Professional Documents

Culture Documents

Each Bit Reset Each Channel

Uploaded by

asdasdasfli.elkinOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Each Bit Reset Each Channel

Uploaded by

asdasdasfli.elkinCopyright:

Available Formats

S912 Datasheet Revision 0.

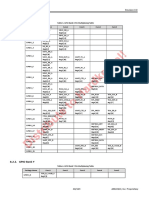

Bit(s) R/W Default Description

19 RW 0 Auto stop count 4 Wr_en

18:16 RW 0 Auto stop count 4

15 RW 0 Auto stop count 3 Wr_en

14:12 RW 0 Auto stop count 3

11 RW 0 Auto stop count 2 Wr_en

10:8 RW 0 Auto stop count 2

7 RW 0 Auto stop count 1 Wr_en

6:4 RW 0 Auto stop count 1

3 RW 0 Auto stop count 0 Wr_en

2:0 RW 0 Auto stop count 0

DEMUX_CHANNEL_RESET_O 0x3d

Bit(s) R/W Default Description

31:0 R 0 Bit 31:0 reset channel status - Each Bit reset each channel

DEMUX_SCRAMBLING_STATE_O 0x3e

Bit(s) R/W Default Description

31:0 R 0 Scrambling state of each channel

DEMUX_CHANNEL_ACTIVITY_O 0x3f

Bit(s) R/W Default Description

31:0 R 0 Channel activity of each channel

DEMUX_STAMP_CTL_O 0x40

Bit(s) R/W Default Description

4 RW 0 video_stamp_use_dts

3 RW 0 audio_stamp_sync_1_en

2 RW 0 audio_stamp_insert_en

1 RW 0 video_stamp_sync_1_en

0 RW 0 video_stamp_insert_en

DEMUX_VIDEO_STAMP_SYNC_0_O 0x41

Bit(s) R/W Default Description

31:0 RW 0 Video stamp sync [63:32]

DEMUX_VIDEO_STAMP_SYNC_1_O 0x42

Bit(s) R/W Default Description

31:0 RW 0 Video stamp sync [31:0]

DEMUX_AUDIO_STAMP_SYNC_0_O 0x43

Bit(s) R/W Default Description

31:0 RW 0 Aideo stamp sync [63:32]

DEMUX_AUDIO_STAMP_SYNC_1_O 0x44

Bit(s) R/W Default Description

31:0 RW 0 Aideo stamp sync [31:0]

DEMUX_SECTION_RESET_O 0x45

131/554 AMLOGIC, Inc. Proprietary

S912 Datasheet Revision 0.1

Bit(s) R/W Default Description

Write : Bit[4:0] secter filter number for reset Read : select according to

output_section_buffer_valid: per bit per section buffer valid status or

31:0 R 0 section_buffer_ignore

DEMUX_INPUT_TIMEOUT_C_O 0x46

Bit(s) R/W Default Description

31:0 RW 0 channel_reset_timeout_disable

DEMUX_INPUT_TIMEOUT_O 0x47

Bit(s) R/W Default Description

31 RW 0 no_match_reset_timeout_disable

30:0 RW 0 input_time_out_int_cnt (0 -- means disable) Wr-setting, Rd-count

DEMUX_PACKET_COUNT_O 0x48

Bit(s) R/W Default Description

31:0 RW 0 channel_packet_count_disable

DEMUX_PACKET_COUNT_C_O0x49

Bit(s) R/W Default Description

31 RW 0 no_match_packet_count_disable

30:0 RW 0 input_packet_count

DEMUX_CHAN_RECORD_EN_O 0x4a

Bit(s) R/W Default Description

31:0 RW 0xffffffff channel_record_enable

DEMUX_CHAN_PROCESS_EN_O 0x4b

Bit(s) R/W Default Description

31:0 RW 0xffffffff channel_process_enable

DEMUX_SMALL_SEC_CTL_O 0x4c

Bit(s) R/W Default Description

31:24 RW 0 small_sec_size ((n+1) * 256 Bytes)

23:16 RW 0 small_sec_rd_ptr

15:8 RW 0 small_sec_wr_ptr

7:2 RW 0 reserved

1 RW 0 small_sec_wr_ptr_wr_enable

0 RW 0 small_section_enable

132/554 AMLOGIC, Inc. Proprietary

S912 Datasheet Revision 0.1

27. Video Output

27.1 Overview

This section describes S912 -module, including RDMA sub-module, HDMI sub-module and the CVBS sub-module.

27.2 VPU

VPU is designed as the interface of the video input module and the video out module. The main function of VPU is to get data

from DDR and deliver it to CVBS or HDMITX based on different format.

VPU Registers

VPU_VIU_VENC_MUX_CTRL 0x271a

Bit(s) R/W Default Description

11-8 R/W 0 VIU_VDIN_SEL_DATA: Select which data to VDI6 path, must clear it first before switching the data.

Select ENCP data to VDI6

7-4 R/W 0 VIU_VDIN_SEL_CLK: Select which clock to VDI6 path, must clear it first before switching the clock.

3-2 R/W 0 VIU2_SEL_VENC: Select which one of the encI/P/T/L that Viu2 connects to.

0: ENCL

1: ENCI

2: ENCP

3: ENCT

1-0 R/W 0 VIU1_SEL_VENC: Select which one of the encI/P/T/L that Viu1 connects to.

0: ENCL

1: ENCI

2: ENCP

3: ENCT

VPU_HDMI_SETTING 0x271b

Bit(s) R/W Default Description

15-12 R/W 0 RD_RATE: Read rate to the async FIFO between VENC and HDMI.

0: One read every rd_clk

1: One read every 2 rd_clk

2: One read every 3 rd_clk

15: One read every 16 rd_clk

11-8 R/W 0 WR_RATE: Write rate to the async FIFO between VENC and HDMI.

0: One write every wr_clk

1: One write every 2 wr_clk

2: One write every 3 wr_clk

15: One write every 16 wr_clk

7-5 R/W 0 DATA_COMP_MAP: Input data is CrYCr(BRG), map the output data to desired format:

0: output CrYCb (BRG)

1: output YCbCr (RGB)

2: output YCrCb (RBG)

3: output CbCrY (GBR)

133/554 AMLOGIC, Inc. Proprietary

S912 Datasheet Revision 0.1

Bit(s) R/W Default Description

4: output CbYCr (GRB)

5: output CrCbY (BGR)

6,7: Reserved

4 R/W 0 INV_DVI_CLK: If true, invert the polarity of clock output to external DVI interface. (NOT internal HDMI).

3 R/W 0 INV_VSYNC: If true, invert the polarity of VSYNC input from VENC

2 R/W 0 INV_HSYNC: If true, invert the polarity of HSYNC input from VENC

1-0 R/W 0 SRC_SEL: Select which HDMI source from between ENCI and ENCP.

data to HDMI

ENCI_INFO_READ 0x271c

Bit(s) R/W Default Description

31-29 R 0 Current ENCI field status.

28-25 R 0 Reserved

24-16 R 0 Current ENCI line counter status.

15-11 R 0 Reserved

10-0 R 0 Current ENCI pixel counter status.

ENCP_INFO_READ 0x271d

Bit(s) R/W Default Description

31-29 R 0 Current ENCP field status.

28-16 R 0 Current ENCP line counter status.

15-13 R 0 Reserved

12-0 R 0 Current ENCP pixel counter status.

ENCT_INFO_READ 0x271e

Bit(s) R/W Default Description

31-29 R 0 Current ENCT field status.

28-16 R 0 Current ENCT line counter status.

15-13 R 0 Reserved

12-0 R 0 Current ENCT pixel counter status.

ENCL_INFO_READ 0x271f

Bit(s) R/W Default Description

31-29 R 0 Current ENCL field status.

28-16 R 0 Current ENCL line counter status.

15-13 R 0 Reserved

12-0 R 0 Current ENCL pixel counter status.

VPU_SW_RESET 0x2720

Bit(s) R/W Default Description

3 R/W 0 vpuarb2_mmc_arb_rst_n

2 R/W 0 vdisp_mmc_arb_rst_n

1 R/W 0 vdin_mmc_arb_rst_n

0 R/W 0 viu_rst_n

VPU_D2D3_MMC_CTRL 0x2721

Bit(s) R/W Default Description

30 R/W 0 d2d3_depr_req_sel, 0:vdisp_pre_arb, 1: vpuarb2_pre_arb

27-22 R/W 0x3f d2d3_depr_brst_num

21-16 R/W 0x2d d2d3_depr_id

14 R/W 0x0 d2d3_depw_req_sel, 0: vdin_pre_arb, 1: vdisp_pre_arb

11-6 R/W 0x3f d2d3_depw_brst_num

5-0 R/W 0x2e d2d3_depw_id

134/554 AMLOGIC, Inc. Proprietary

You might also like

- SD - REG9 - ICTL 0xc1108e24Document3 pagesSD - REG9 - ICTL 0xc1108e24asdasdasfli.elkinNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Ninebot ES Communicaton Protocol: Release Date: 27/09/2019Document19 pagesNinebot ES Communicaton Protocol: Release Date: 27/09/2019Полина АндрееваNo ratings yet

- 14.4. Register Description: 14.4.1. I2C - M - 0 - CONTROL - REG 0x2140Document3 pages14.4. Register Description: 14.4.1. I2C - M - 0 - CONTROL - REG 0x2140asdasdasfli.elkinNo ratings yet

- Rbs 6201 3g 3rd Carrier Site - XMLDocument6 pagesRbs 6201 3g 3rd Carrier Site - XMLsyednooman1No ratings yet

- I-7018 (R) (BL) (P), M-7018 (R) Quick Start GuideDocument4 pagesI-7018 (R) (BL) (P), M-7018 (R) Quick Start GuideData CommunicationNo ratings yet

- Load Cell Input Module: 1 Specifications of FBS-PLC Load Cell Measurement ModulesDocument8 pagesLoad Cell Input Module: 1 Specifications of FBS-PLC Load Cell Measurement ModulesNelson GilNo ratings yet

- Jetter JC Series PLC Delta A. Hmi Factory Settings: Appendix B Communication - Scredit Software User ManualDocument2 pagesJetter JC Series PLC Delta A. Hmi Factory Settings: Appendix B Communication - Scredit Software User ManualryoNo ratings yet

- Adv7619 RegsDocument45 pagesAdv7619 RegsJames DoolinNo ratings yet

- Pic 16 F 628Document20 pagesPic 16 F 628Merényi Oszkár100% (1)

- Tristar MPPT Modbus® Specification: V10.2 5 December 2011Document26 pagesTristar MPPT Modbus® Specification: V10.2 5 December 2011a.anugrahNo ratings yet

- PVI 50/60TL: Modbus CommunicationsDocument34 pagesPVI 50/60TL: Modbus CommunicationsBaggi NNo ratings yet

- 8 Reset PDFDocument20 pages8 Reset PDFnicolas8702No ratings yet

- CAN Bus1Document14 pagesCAN Bus1pirpi_12345No ratings yet

- Microchip CRC ManualDocument22 pagesMicrochip CRC ManualmordehainNo ratings yet

- Dokumen - Tips Prostar MPPT Modbus Specification The Prostar MPPT Supports Rtu Mode Only 16bitDocument31 pagesDokumen - Tips Prostar MPPT Modbus Specification The Prostar MPPT Supports Rtu Mode Only 16bitAlberto Xilotl SolanoNo ratings yet

- ModbusConfig V1 01Document1 pageModbusConfig V1 01pedro pabloNo ratings yet

- SH1101ADocument59 pagesSH1101AchNo ratings yet

- Hust CNC Controller Delta A. Hmi Factory Settings: Appendix B Communication - Scredit Software User ManualDocument1 pageHust CNC Controller Delta A. Hmi Factory Settings: Appendix B Communication - Scredit Software User ManualryoNo ratings yet

- Dem128064o1fgh PWDocument17 pagesDem128064o1fgh PWRadu MititeluNo ratings yet

- MITSUBISHI QJ71 Driver For Q00/Q01 CPU Port: HMI SettingDocument3 pagesMITSUBISHI QJ71 Driver For Q00/Q01 CPU Port: HMI SettingHamid KharazmiNo ratings yet

- Technical Reference Options and Adapters Volume 2 3of3Document243 pagesTechnical Reference Options and Adapters Volume 2 3of3kgrhoadsNo ratings yet

- 89c51 Raining Cou Week1Document33 pages89c51 Raining Cou Week1api-3761333No ratings yet

- LG Master-K Cnet Delta A. Hmi Factory Settings: Appendix B Communication - Scredit Software User ManualDocument2 pagesLG Master-K Cnet Delta A. Hmi Factory Settings: Appendix B Communication - Scredit Software User ManualryoNo ratings yet

- TS-MPPT-600V Modbus Doc Public - Aug-2014Document27 pagesTS-MPPT-600V Modbus Doc Public - Aug-2014Assad Ullah KhanNo ratings yet

- ModbusDocument6 pagesModbusCésar YagüeNo ratings yet

- 8-Bit Microcontroller With 1K Bytes In-System Programmable Flash AT90S1200Document7 pages8-Bit Microcontroller With 1K Bytes In-System Programmable Flash AT90S1200Yerson CrespoNo ratings yet

- SM5160CM/DM: Nippon Precision Circuits IncDocument7 pagesSM5160CM/DM: Nippon Precision Circuits IncLucas Gabriel CasagrandeNo ratings yet

- Cj2m-Cpu3-Cpu1 E1 DSDocument4 pagesCj2m-Cpu3-Cpu1 E1 DSluis miguel huarita castellonNo ratings yet

- CAN BUS Communication Manual For The DNC Series: ContentDocument9 pagesCAN BUS Communication Manual For The DNC Series: Contentstu807No ratings yet

- 24 Device ConfigurationDocument16 pages24 Device Configurationnicolas8702No ratings yet

- Technical Doc Prostar Modbus Specification enDocument29 pagesTechnical Doc Prostar Modbus Specification enRyoma KuugaNo ratings yet

- V1000 DatasheetDocument12 pagesV1000 DatasheetHermanherdiantoNo ratings yet

- Banana Pi: Specification For PCIE-DVR: Root Complex Architecture SpecificationDocument32 pagesBanana Pi: Specification For PCIE-DVR: Root Complex Architecture SpecificationАндрашNo ratings yet

- Ym12864p-Dalian Good Display PDFDocument10 pagesYm12864p-Dalian Good Display PDFEvgeniyNo ratings yet

- Sanyo LCD-32XH7 Noblex 32LC820H Philco PLH3210 JVC LT32R50 Chasis UE6LDocument50 pagesSanyo LCD-32XH7 Noblex 32LC820H Philco PLH3210 JVC LT32R50 Chasis UE6LMP3DEEJAY100% (4)

- DMX-K-DRV-34 Integrated NEMA 34 Step Motor + Driver + Basic Controller ManualDocument21 pagesDMX-K-DRV-34 Integrated NEMA 34 Step Motor + Driver + Basic Controller ManualrafaelNo ratings yet

- Service Manual LCD Television: Model No. LCD-42XF7Document50 pagesService Manual LCD Television: Model No. LCD-42XF7Daniel AvecillaNo ratings yet

- Manual Service 32LC821F PDFDocument50 pagesManual Service 32LC821F PDFies837No ratings yet

- Tristar Modbus Specification Morningstar Corporation V04 6 September 2012Document30 pagesTristar Modbus Specification Morningstar Corporation V04 6 September 2012a.anugrahNo ratings yet

- Setting BRAKE Wiring Digital Output CN1Document5 pagesSetting BRAKE Wiring Digital Output CN1Imam SyaefudinNo ratings yet

- Product Specifications: Displaytech LTDDocument20 pagesProduct Specifications: Displaytech LTDPwter KovacsNo ratings yet

- TS1620 TechstarDocument12 pagesTS1620 TechstarMahdiiiiii83No ratings yet

- Mks Ct150 Delta A. Hmi Factory Settings: Appendix B Communication - Scredit Software User ManualDocument2 pagesMks Ct150 Delta A. Hmi Factory Settings: Appendix B Communication - Scredit Software User ManualryoNo ratings yet

- Mitsubishi A2A/A2AS/A2USH A1SH/A3N/A2ASH (CPU-S1) CPU Port Delta A. HMI Factory SettingsDocument3 pagesMitsubishi A2A/A2AS/A2USH A1SH/A3N/A2ASH (CPU-S1) CPU Port Delta A. HMI Factory SettingsryoNo ratings yet

- Lecture12-Using PIC Micro Controller 16F877ADocument57 pagesLecture12-Using PIC Micro Controller 16F877ADoodee Mohammed100% (4)

- Lab 7 ADCDocument19 pagesLab 7 ADCakkauntdlyaigrichegotoescheNo ratings yet

- Serial Communications: ObjectivesDocument26 pagesSerial Communications: ObjectivesAmy OliverNo ratings yet

- PIC16F/LF1826/27: 14.0 Fixed Voltage Reference (FVR)Document13 pagesPIC16F/LF1826/27: 14.0 Fixed Voltage Reference (FVR)jjebmiNo ratings yet

- Công Suất Phát Rrh 3g Alu Band 900Document12 pagesCông Suất Phát Rrh 3g Alu Band 900cuongNo ratings yet

- 24fj RESETApNoteDocument26 pages24fj RESETApNoteLuis Di PintoNo ratings yet

- Sh1106 Sino WealthDocument49 pagesSh1106 Sino WealthAnonymous Im6zx7xiyNo ratings yet

- Datasheet L272MDocument10 pagesDatasheet L272MJavier JaviNo ratings yet

- Digital To Analog Converters (DAC) : Adam Fleming Mark Hunkele 3/11/2005Document42 pagesDigital To Analog Converters (DAC) : Adam Fleming Mark Hunkele 3/11/2005Dinh Thuc NguyenNo ratings yet

- Manual Fallas 23TL CPSDocument36 pagesManual Fallas 23TL CPSAlexander RamirezNo ratings yet

- Converter & Timing CircuitDocument16 pagesConverter & Timing Circuityoboiiii649No ratings yet

- ARM Experiment ProgrammsDocument52 pagesARM Experiment ProgrammsShweta KulkarniNo ratings yet

- S912 Datasheet Revision 0.1Document6 pagesS912 Datasheet Revision 0.1asdasdasfli.elkinNo ratings yet

- Dasfgderh 57y45Document4 pagesDasfgderh 57y45asdasdasfli.elkinNo ratings yet

- 8.2.1. GPIO Bank X: S805 Datasheet Revision 0.8Document5 pages8.2.1. GPIO Bank X: S805 Datasheet Revision 0.8asdasdasfli.elkinNo ratings yet

- 9.3.7. GPIO 4 7 Pin Select: 0x2622: S805 Datasheet Revision 0.8Document3 pages9.3.7. GPIO 4 7 Pin Select: 0x2622: S805 Datasheet Revision 0.8asdasdasfli.elkinNo ratings yet

- Isa - Timerg CBUS: 0x2666Document3 pagesIsa - Timerg CBUS: 0x2666asdasdasfli.elkinNo ratings yet

- Simplecv: "Exit " "CTRL+ D" "Clear" "Tutorial" "Example" "Forums" "Walkthrough"Document5 pagesSimplecv: "Exit " "CTRL+ D" "Clear" "Tutorial" "Example" "Forums" "Walkthrough"asdasdasfli.elkinNo ratings yet

- R8M DataSheet V02Document14 pagesR8M DataSheet V02asdasdasfli.elkinNo ratings yet

- Func Ti OnsDocument3 pagesFunc Ti Onsasdasdasfli.elkinNo ratings yet

- 001Document3 pages001asdasdasfli.elkinNo ratings yet

- Bioemg Iii: Bioresearch Assoc. IncDocument3 pagesBioemg Iii: Bioresearch Assoc. Incasdasdasfli.elkinNo ratings yet

- Chapter 3 C Language and Arduino Type Ide For Pcduino: Toolchain of The Arduino LibraryDocument3 pagesChapter 3 C Language and Arduino Type Ide For Pcduino: Toolchain of The Arduino Libraryasdasdasfli.elkinNo ratings yet

- Altera MAX II Family IntroductionDocument6 pagesAltera MAX II Family Introductionasdasdasfli.elkinNo ratings yet

- MAX II Device Family DatasheetDocument86 pagesMAX II Device Family Datasheetasdasdasfli.elkinNo ratings yet

- EPM240MAINBOARD Schematic DiagramDocument2 pagesEPM240MAINBOARD Schematic Diagramasdasdasfli.elkinNo ratings yet

- Setting Up A Password System On Fanuc Robots (R-30iB V8.30P)Document7 pagesSetting Up A Password System On Fanuc Robots (R-30iB V8.30P)Amine AbassiNo ratings yet

- UnzipDocument13 pagesUnzipNaga LakshmaiahNo ratings yet

- 14 RCAT - Root Cause Analysis TechniquesDocument3 pages14 RCAT - Root Cause Analysis TechniquesDanny Durham100% (1)

- Ieee 802.11Document13 pagesIeee 802.11jeffy100% (1)

- Oracle Database TestDocument2 pagesOracle Database TestMamboleo MamboleaNo ratings yet

- Software Architecture and Design PatternsDocument16 pagesSoftware Architecture and Design PatternsHameed Hamdan Hameed Mohammed AlashwalNo ratings yet

- Mastersaf Interface Namespace SAP - Guide 1 - Read MeDocument5 pagesMastersaf Interface Namespace SAP - Guide 1 - Read MekalyanNo ratings yet

- Dell SonicWALL E-Class SRA 10.6.2 Admin GuideDocument585 pagesDell SonicWALL E-Class SRA 10.6.2 Admin Guidesayed_41No ratings yet

- UNIX Inter Process Communications (I)Document82 pagesUNIX Inter Process Communications (I)Roopa KumaarNo ratings yet

- HCIA-Transmission V2.5 Exam OutlineDocument3 pagesHCIA-Transmission V2.5 Exam OutlineCharlyn TomayaoNo ratings yet

- Multiprogramming: Concurrency Improves ThroughputDocument38 pagesMultiprogramming: Concurrency Improves ThroughputFiroj AnsariNo ratings yet

- SCIP 2.0 Commmunication ProtocolDocument25 pagesSCIP 2.0 Commmunication ProtocolAnthony DennisNo ratings yet

- 1 NEW Oracle 1z0-533 Practice Exam Questions - Oracle Hyperion Planning 11 Essentials - Exam-LabsDocument110 pages1 NEW Oracle 1z0-533 Practice Exam Questions - Oracle Hyperion Planning 11 Essentials - Exam-LabsAbebeNo ratings yet

- PHP GridDocument40 pagesPHP GridKishor KumarNo ratings yet

- Current LogDocument34 pagesCurrent Logmarcelo abellanedaNo ratings yet

- Oracle Database 11g Release 2 (11.2) - E23094-02 - Developer Guide XML DBDocument956 pagesOracle Database 11g Release 2 (11.2) - E23094-02 - Developer Guide XML DBLuciano Merighetti MarwellNo ratings yet

- Oracle Brochure RevisedDocument4 pagesOracle Brochure RevisedvmkamathNo ratings yet

- PL/SQL Practice Quizzes Exam 2Document6 pagesPL/SQL Practice Quizzes Exam 2meachamrob0% (1)

- Internet Technology PDFDocument3 pagesInternet Technology PDFAshika JayaweeraNo ratings yet

- Interview QuestionsDocument3 pagesInterview QuestionsRay20% (5)

- Customer Interface Error - S3 Error The Address Reference Specified Is Not Valid For This Customer Reference (Doc ID 470164.1)Document2 pagesCustomer Interface Error - S3 Error The Address Reference Specified Is Not Valid For This Customer Reference (Doc ID 470164.1)NgocTBNo ratings yet

- CChapter 3 - C-Sharp Language FuncamentalsDocument52 pagesCChapter 3 - C-Sharp Language FuncamentalsRudresh CMNo ratings yet

- Smart SourcingDocument15 pagesSmart SourcingIshanvi ShuklaNo ratings yet

- Distributed File SystemDocument7 pagesDistributed File SystemMahamud elmogeNo ratings yet

- MS XP MythsDocument31 pagesMS XP MythsSandip GumtyaNo ratings yet

- 8051 MaterialDocument198 pages8051 Materialsupreetp555No ratings yet

- FD Controller Instruction Manual Devicenet Function: 3Rd EditionDocument38 pagesFD Controller Instruction Manual Devicenet Function: 3Rd EditionrmlNo ratings yet

- Historian Databases ChemaDocument1 pageHistorian Databases ChemaDinh VuNo ratings yet

- Intel Ethernet Adapters On HPE PlatformsDocument23 pagesIntel Ethernet Adapters On HPE PlatformsYUUNo ratings yet

- Advanced Computer Architecture 2Document17 pagesAdvanced Computer Architecture 2Pritesh PawarNo ratings yet