Professional Documents

Culture Documents

S912 Datasheet Revision 0.1

Uploaded by

asdasdasfli.elkinOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

S912 Datasheet Revision 0.1

Uploaded by

asdasdasfli.elkinCopyright:

Available Formats

S912 Datasheet Revision 0.

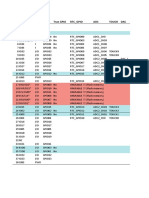

23:16 R/W 0d25 reg_adp_hcti_con_2_gain0 : , default = 25 . unsigned , default = 25

15: 8 R/W 0d60 reg_adp_hcti_con_2_gain1 : , default = 60 . unsigned , default = 60

7: 0 R/W 0d0 reg_adp_hcti_con_2_gain2 : 0;, default = 0 . unsigned , default = 0

SRSHARP1_HCTI_CON_2_GAIN_1 0x32b2

Bit(s) R/W Default Description

31:24 R/W 0d96 reg_adp_hcti_con_2_gain3 : 96;, default = 96 . unsigned , default = 96

23:16 R/W 0d5 reg_adp_hcti_con_2_gain4 : 5;, default = 5 . unsigned , default = 5

15: 8 R/W 0d80 reg_adp_hcti_con_2_gain5 : 80;, default = 80 . unsigned , default = 80

7: 0 R/W 0d20 reg_adp_hcti_con_2_gain6 : 20;, default = 20 . unsigned , default = 20

SRSHARP1_HCTI_OS_MARGIN 0x32b3

Bit(s) R/W Default Description

7: 0 R/W 0d0 reg_adp_hcti_os_margin : : margin for hcti overshoot, default = 0 . unsigned , default = 0

SRSHARP1_HLTI_FLT_CLP_DC 0x32b4

Bit(s) R/W Default Description

28 R/W 0d1 reg_adp_hlti_en : , 0: no cti, 1: new cti, default = 1 . unsigned , default = 1

27:26 R/W 0d2 reg_adp_hlti_vdn_flt : , 0: no lpf; 1:[0,2,4,2,0], 2 : [1 2 2 2 1]/8 3:[1 0 2 0 1]/4, default = 2 . unsigned , default =

2

25:24 R/W 0d2 reg_adp_hlti_hdn_flt : , 0: no lpf; 1:[0, 0, 0, 4, 8, 4, 0, 0, 0], 2:[0, 0, 2, 4, 4, 4, 2, 0, 0], 3: [1, 2, 2, 2, 2, 2, 2, 2, 1],

default = 2. unsigned , default = 2

23:22 R/W 0d2 reg_adp_hlti_ddn_flt : , 0: no lpf; 1:[0,2,4,2,0], 2 : [1 2 2 2 1]/8 3:[1 0 2 0 1]/4, default = 2 . unsigned , default =

2

21:20 R/W 0d2 reg_adp_hlti_lpf0_flt : , 0:no filter; 1:sigma=0.75, 2: sigma = 1.0, 3: sigma = 1.5, default = 2 . unsigned , default

=2

19:18 R/W 0d2 reg_adp_hlti_lpf1_flt : , 0:no filter; 1:sigma= 2.0, 2: sigma = 3.0, 3: sigma = 4.0, default = 2 . unsigned , default

=2

17:16 R/W 0d2 reg_adp_hlti_lpf2_flt : , 0:no filter; 1:sigma=5.0, 2: sigma = 9.0, 3: sigma = 13.0, default = 2 . unsigned , default

=2

15:12 R/W 0d2 reg_adp_hlti_hard_clp_win : , window size, 0~8, default = 2 . unsigned , def

default = 2

11: 8 R/W 0d1 reg_adp_hlti_hard_win_min : , window size, 0~8, default = 1 . unsigned , default = 1

4 R/W 0d0 reg_adp_hlti_clp_mode : , 0: hard clip, 1: adaptive clip, default = 0 . unsigned , default = 0

2: 0 R/W 0d4 reg_adp_hlti_dc_mode : , 0:dn, 1:lpf0, 2:lpf1, 3:lpf2, 4: lpf3: 5: vdn result; 6/7:org, default = 4 . unsigned , default

=4

SRSHARP1_HLTI_BST_GAIN 0x32b5

Bit(s) R/W Default Description

31:24 R/W 0d40 reg_adp_hlti_bst_gain0 : : gain of the bandpass 0 (lpf1

(lpf1-lpf2)- LBP, default = 40 . unsigned , default =

40

23:16 R/W 0d48 reg_adp_hlti_bst_gain1 : : gain of the bandpass 1 (lpf0

(lpf0-lpf1)- BP, default = 48 . unsigned , default =

48

15: 8 R/W 0d32 reg_adp_hlti_bst_gain2 : : gain of the bandpass 2 (hdn-lpf0)- HP, default = 32 . unsigned , default =

32

7: 0 R/W 0d16 reg_adp_hlti_bst_gain3 : : gain of the unsharp band (yuvin-hdn) - US, default = 16 . unsigned , default

= 16

SRSHARP1_HLTI_BST_CORE 0x32b6

Bit(s) R/W Default Description

31:24 R/W 0d5 reg_adp_hlti_bst_core0 : : core of the bandpass 0 (lpf1-lpf2)- LBP, default = 5 . unsigned , default =

5

23:16 R/W 0d5 reg_adp_hlti_bst_core1 : : core of the bandpass 1 (lpf0-lpf1)- BP, default = 5 . unsigned , default =

5

15: 8 R/W 0d5 reg_adp_hlti_bst_core2 : : core of the bandpass 2 (hdn-lpf0)- HP, default = 5 . unsigned , default =

5

7: 0 R/W 0d3 reg_adp_hlti_bst_core3 : : core of the unsharp band (yuvin-hdn) - US, default = 3 . unsigned , default

=3

254/554 AMLOGIC, Inc. Proprietary

S912 Datasheet Revision 0.1

SRSHARP1_HLTI_CON_2_GAIN_0 0x32b7

Bit(s) R/W Default Description

31:29 R/W 0d2 reg_adp_hlti_con_mode : : con mode 0:[0, 0,-1, 1, 0, 0, 0]+[0, 0, 0, 1,-1, 0, 0], 1: [0, 0,-1, 0, 1, 0, 0], 2: [0,-1, 0, 0, 0,

1, 0], 3:[-1, 0, 0, 0, 0, 0, 1], 4: ....., default = 2. unsigned , default = 2

28:26 R/W 0d3 reg_adp_hlti_dx_mode : : dx mode 0: [-1 1 0]; 1~7: [-1 (2x+1)"0" 1], default = 3 . unsigned , default =

3

25:24 R/W 0d1 reg_adp_hlti_con_lpf : : lpf mode of the con: 0: [1 2 1]/4; 1:[1 2 2 2 1]/8, default = 1 . unsigned , default =

1

23:16 R/W 0d25 reg_adp_hlti_con_2_gain0 : 25;, default = 25 . unsigned , default = 25

15: 8 R/W 0d60 reg_adp_hlti_con_2_gain1 : 60;, default = 60 . unsigned , default = 60

7: 0 R/W 0d90 reg_adp_hlti_con_2_gain2 : 0;, default = 90 . unsigned , default = 90

SRSHARP1_HLTI_CON_2_GAIN_1 0x32b8

Bit(s) R/W Default Description

31:24 R/W 0d96 reg_adp_hlti_con_2_gain3 : 96;, default = 96 . unsigned , defa

default = 96

23:16 R/W 0d95 reg_adp_hlti_con_2_gain4 : 5;, default = 95 . unsigned , defa

default = 95

15: 8 R/W 0d80 reg_adp_hlti_con_2_gain5 : 80;, default = 80 . unsigned , default = 80

7: 0 R/W 0d20 reg_adp_hlti_con_2_gain6 : 20;, default = 20 . unsigned , defa

default = 20

SRSHARP1_HLTI_OS_MARGIN 0x32b9

Bit(s) R/W Default Description

7: 0 R/W 0d0 reg_adp_hlti_os_margin : : margin for hlti overshoot, default = 0 . unsigned , defaul

default = 0

SRSHARP1_VLTI_FLT_CON_CLP 0x32ba

Bit(s) R/W Default Description

14 R/W 0d1 reg_adp_vlti_en : : enable bit of vlti, default = 1 . unsigned , default = 1

13:12 R/W 0d3 reg_adp_vlti_hxn_flt : : 0: no dn; 1: [1 2 1]/4; 2 : [1 2 2 2 1]/8 3:[1 0 2 0 1]/4, default = 3 . unsigned , default =

3

11:10 R/W 0d3 reg_adp_vlti_dxn_flt : : 0: no dn; 1: [1 2 1]/4; 2 : [1 2 2 2 1]/8 3:[1 0 2 0 1]/4, default = 3 . unsigned , default =

3

9: 8 R/W 0d3 reg_adp_vlti_han_flt : : 0: no dn; 1: [1 2 1]/4; 2 : [1 2 2 2 1]/8 3:[1 0 2 0 1]/4, default = 3 . unsigned , default =

3

7: 6 R/W 0d3 reg_adp_vlti_dan_flt : : 0: no dn; 1: [1 2 1]/4; 2 : [1 2 2 2 1]/8 3:[1 0 2 0 1]/4, default = 3 . unsigned , default =

3

5: 4 R/W 0d2 reg_adp_vlti_dx_mode : : 0:[0:[-1 1] 1:[-1 0 -1]; 2/3: [-1 0 0 0 -1], default = 2 . unsigned , default = 2

2 R/W 0d1 reg_adp_vlti_con_lpf : : lpf mode of the con: 0: [1 2 1]/4; 1:[1 2 2 2 1]/8, default = 1 . unsigned , default =

1

0 R/W 0d1 reg_adp_vlti_hard_clp_win : : window size; 0: 1x3 window; 1: 1x5 window, default = 1 . unsigned ,

default = 1

SRSHARP1_VLTI_BST_GAIN 0x32bb

Bit(s) R/W Default Description

23:16 R/W 0d32 reg_adp_vlti_bst_gain0 : : gain to boost filter [-1 2 -1];, default = 32 . unsigned , default = 32

15: 8 R/W 0d32 reg_adp_vlti_bst_gain1 : : gain to boost filter [-1 0 2 0 -1];, default = 32 . unsigned , default = 32

7: 0 R/W 0d32 reg_adp_vlti_bst_gain2 : : gain to boost filter usf, default = 32 . unsigned , default = 32

SRSHARP1_VLTI_BST_CORE 0x32bc

Bit(s) R/W Default Description

23:16 R/W 0d5 reg_adp_vlti_bst_core0 : : coring to boost filter [-1 2 -1];, default = 5 . unsigned , default = 5

15: 8 R/W 0d5 reg_adp_vlti_bst_core1 : : coring to boost filter [-1 0 2 0 -1];, default = 5 . unsigned , default = 5

7: 0 R/W 0d3 reg_adp_vlti_bst_core2 : : coring to boost filter usf, default = 3 . unsigned , default = 3

SRSHARP1_VLTI_CON_2_GAIN_0 0x32bd

Bit(s) R/W Default Description

31:24 R/W 0d25 reg_adp_vlti_con_2_gain0 : 25;, default = 25 . unsigned , default = 25

23:16 R/W 0d69 reg_adp_vlti_con_2_gain1 : 60;, default = 69 . unsigned , default = 60

15: 8 R/W 0d90 reg_adp_vlti_con_2_gain2 : 0;, default = 90 . unsigned , default = 90

255/554 AMLOGIC, Inc. Proprietary

S912 Datasheet Revision 0.1

7: 0 R/W 0d96 reg_adp_vlti_con_2_gain3 : 96;, default = 96 . unsigned , default = 96

SRSHARP1_VLTI_CON_2_GAIN_1 0x32be

Bit(s) R/W Default Description

31:24 R/W 0d95 reg_adp_vlti_con_2_gain4 : 5;, default = 95 . unsigned , default = 95

23:16 R/W 0d80 reg_adp_vlti_con_2_gain5 : 80;, default = 80 . unsigned , default = 80

15: 8 R/W 0d20 reg_adp_vlti_con_2_gain6 : 20;, default = 20 . unsigned , default = 20

7: 0 R/W 0d0 reg_adp_vlti_os_margin : : margin for vlti overshoot, default = 0 . unsigned , default = 0

SRSHARP1_VCTI_FLT_CON_CLP 0x32bf

Bit(s) R/W Default Description

14 R/W 0d1 reg_adp_vcti_en : : enable bit of vlti, default = 1 . unsigned , default = 1

13:12 R/W 0d3 reg_adp_vcti_hxn_flt : : 0: no dn; 1: [1 2 1]/4; 2 : [1 2 2 2 1]/8 3:[1 0 2 0 1]/4, default = 3 . unsigned , default =

3

11:10 R/W 0d3 reg_adp_vcti_dxn_flt : : 0: no dn; 1: [1 2 1]/4; 2 : [1 2 2 2 1]/8 3:[1 0 2 0 1]/4,

4, default = 3 . unsigned , default =

3

9: 8 R/W 0d3 reg_adp_vcti_han_flt : : 0: no dn; 1: [1 2 1]/4; 2 : [1 2 2 2 1]/8 3:[1 0 2 0 1]/4, default = 3 . unsigned , default =

3

7: 6 R/W 0d3 reg_adp_vcti_dan_flt : : 0: no dn; 1: [1 2 1]/4; 2 : [1 2 2 2 1]/8 3:[1 0 2 0 1]/4, default = 3 . unsigned , default =

3

5: 4 R/W 0d2 reg_adp_vcti_dx_mode : : 0:[-1 1] 1:[-1 0 -1]; 2/3: [-1 0 0 0 -1],

1], default = 2 . unsigned , default = 2

2 R/W 0d1 reg_adp_vcti_con_lpf : : lpf mode of the con: 0: [1 2 1]/4; 1:[1 2 2 2 1]/8, default = 1 . unsigned , default =

1

0 R/W 0d1 reg_adp_vcti_hard_clp_win : : window size; 0: 1x3 window; 1: 1x5 window, default = 1 . unsigned ,

default = 1

SRSHARP1_VCTI_BST_GAIN 0x32c0

Bit(s) R/W Default Description

23:16 R/W 0d0 reg_adp_vcti_bst_gain0 : : gain to boost filter [[-1 2 -1];, default = 0 . unsigned , default = 0

15: 8 R/W 0d0 reg_adp_vcti_bst_gain1 : : gain to boost filter [[-1 0 2 0 -1];, default = 0 . unsigned , default = 0

7: 0 R/W 0d0 reg_adp_vcti_bst_gain2 : : gain to boost filter usf, default = 0 . unsigned , default = 0

SRSHARP1_VCTI_BST_CORE 0x32c1

Bit(s) R/W Default Description

23:16 R/W 0d0 reg_adp_vcti_bst_core0 : : coring to boost filter [[-1 2 -1];, default = 0 . unsigned , default = 0

15: 8 R/W 0d0 reg_adp_vcti_bst_core1 : : coring to boost filter [[-1 0 2 0 -1];, default = 0 . unsigned , default = 0

7: 0 R/W 0d0 reg_adp_vcti_bst_core2 : : coring to boost filter usf, default = 0 . unsigned , default = 0

SRSHARP1_VCTI_CON_2_GAIN_0 0x32c2

Bit(s) R/W Default Description

31:24 R/W 0d25 reg_adp_vcti_con_2_gain0 : 25;, default = 25 . unsigned , defa

default = 25

23:16 R/W 0d60 reg_adp_vcti_con_2_gain1 : 60;, default = 60 . unsigned , default = 60

15: 8 R/W 0d90 reg_adp_vcti_con_2_gain2 : 0;, default = 90 . unsigned , default = 90

7: 0 R/W 0d96 reg_adp_vcti_con_2_gain3 : 96;, default = 96 . unsigned , default = 96

SRSHARP1_VCTI_CON_2_GAIN_1 0x32c3

Bit(s) R/W Default Description

31:24 R/W 0d95 reg_adp_vcti_con_2_gain4 : 5;, default = 95 . unsigned , default = 95

23:16 R/W 0d80 reg_adp_vcti_con_2_gain5 : 80;, default = 80 . unsigned , default = 80

15: 8 R/W 0d20 reg_adp_vcti_con_2_gain6 : 20;, default = 20 . unsigned , default = 20

7: 0 R/W 0d0 reg_adp_vcti_os_margin : : margin for vcti overshoot, default = 0 . unsigned , default = 0

SRSHARP1_SHARP_3DLIMIT 0x32c4

Bit(s) R/W Default Description

28:16 R/W 0d0 reg_3d_mid_width : ,width of left part of 3d input, dft = half size of input width default = 0 . unsigned , default

= 960

256/554 AMLOGIC, Inc. Proprietary

S912 Datasheet Revision 0.1

12: 0 R/W 0d0 reg_3d_mid_height : ,height of left part of 3d input, dft = half size of input height default = 0 . unsigned , default

= 540

SRSHARP1_DNLP_EN 0x32c5

Bit(s) R/W Default Description

0 R/W 0d1 reg_dnlp_en : . unsigned , default = 1

SRSHARP1_DNLP_00 0x32c6

Bit(s) R/W Default Description

31: 0 R/W 0x08060402 reg_dnlp_ygrid0 : : dnlp00 . unsigned , default = 0x08060402

SRSHARP1_DNLP_01 0x32c7

Bit(s) R/W Default Description

31: 0 R/W 0x100e0c0a reg_dnlp_ygrid1 : : dnlp01 . unsigned , default = 0x100e0c0a

SRSHARP1_DNLP_02 0x32c8

Bit(s) R/W Default Description

31: 0 R/W 0x1a171412 reg_dnlp_ygrid2 : : dnlp02 . unsigned , default = 0x1a171412

SRSHARP1_DNLP_03 0x32c9

Bit(s) R/W Default Description

31: 0 R/W 0x2824201d reg_dnlp_ygrid3 : : dnlp03 . unsigned , default = 0x2824201d

SRSHARP1_DNLP_04 0x32ca

Bit(s) R/W Default Description

31: 0 R/W 0x3834302c reg_dnlp_ygrid4 : : dnlp04 . unsigned , default = 0x3834302c

SRSHARP1_DNLP_05 0x32cb

Bit(s) R/W Default Description

31: 0 R/W 0x4b45403c reg_dnlp_ygrid5 : : dnlp05 . unsigned , default = 0x4b45403c

SRSHARP1_DNLP_06 0x32cc

Bit(s) R/W Default Description

31: 0 R/W 0x605b5550 reg_dnlp_ygrid6 : : dnlp06 . unsigned , default = 0x605b5550

SRSHARP1_DNLP_07 0x32cd

Bit(s) R/W Default Description

31: 0 R/W 0x80787068 reg_dnlp_ygrid7 : : dnlp07 . unsigned , default = 0x80787068

SRSHARP1_DNLP_08 0x32ce

Bit(s) R/W Default Description

31: 0 R/W 0xa0989088 reg_dnlp_ygrid8 : : dnlp08 . unsigned , default = 0xa0989088

SRSHARP1_DNLP_09 0x32cf

Bit(s) R/W Default Description

31: 0 R/W 0xb8b2aca6 reg_dnlp_ygrid9 : : dnlp09 . unsigned , default = 0xb8b2aca6

SRSHARP1_DNLP_10 0x32d0

Bit(s) R/W Default Description

31: 0 R/W 0xc8c4c0bc reg_dnlp_ygrid10 : : dnlp10 . unsigned , default = 0xc8c4c0bc

SRSHARP1_DNLP_11 0x32d1

Bit(s) R/W Default Description

31: 0 R/W 0xd4d2cecb reg_dnlp_ygrid11 : : dnlp11 . unsigned , default = 0xd4d2cecb

257/554 AMLOGIC, Inc. Proprietary

S912 Datasheet Revision 0.1

SRSHARP1_DNLP_12 0x32d2

Bit(s) R/W Default Description

31: 0 R/W 0xdad8d7d6 reg_dnlp_ygrid12 : : dnlp12 . unsigned , default = 0xdad8d7d6

SRSHARP1_DNLP_13 0x32d3

Bit(s) R/W Default Description

31: 0 R/W 0xe2e0dedc reg_dnlp_ygrid13 : : dnlp13 . unsigned , default = 0xe2e0dedc

SRSHARP1_DNLP_14 0x32d4

Bit(s) R/W Default Description

31: 0 R/W 0xf0ece8e4 reg_dnlp_ygrid14 : : dnlp14 . unsigned , default = 0xf0ece8e4

SRSHARP1_DNLP_15 0x32d5

Bit(s) R/W Default Description

31: 0 R/W 0xfffcf8f4 reg_dnlp_ygrid15 : : dnlp15 . unsigned , default = 0xfffcf8f4

SRSHARP1_DEMO_CRTL 0x32d6

Bit(s) R/W Default Description

18:17 R/W 0d2 demo_disp_position : . unsigned , default = 2

16 R/W 0d0 demo_hsvsharp_enable : . unsigned , default = 0

12: 0 R/W 0d360 demo_left_top_screen_width : : . unsigned , de

default = 360

SRSHARP1_SHARP_SR2_CTRL 0x32d7

Bit(s) R/W Default Description

31:25 R/W reserved

24 R/W 0 sr2_dejaggy_en, 1 to enable dejaggy

23:22 R/W reserved

21:16 R/W 24 sr2_pk_la_err_dis_rate, low angle and high angle error should not be no less than nearby_error* rate/64

15: 8 R/W 16 sr2_pk_sad_diag_gain, gain to sad[2] and sad[6], 16 normalized to 1

7 R/W 0 sr2_vert_outphs, vertical output pixel phase, 0: 0 phase; 1: 1/2 phase

6 R/W 0 sr2_horz_outphs, horizontal output pixel phase, 0: 0 phase; 1: 1/2 phase

5 R/W 0 sr2_vert_ratio , vertical scale ratio, 0

0-> 1:1; 1-> 1:2

4 R/W 0 sr2_horz_ratio , horizontal scale ratio, 0

0-> 1:1; 1-> 1:2

3 R/W 1 sr2_ bic_norm , normalization of bicubical: 0: 128; 1: 64

2 R/W 0 sr2_ enable , 1 to enable super scaler

1 R/W 0 sr2_ sharp_prc_lr_hbic,

0 R/W 0 sr2_ sharp_prc_lr, 1: LTI/CTI/NR/Peaking processing using LR grid. 0: on HR grid; 1:on LR grid, horizontally no

upscale, but using simple bic.

SRSHARP1_SHARP_SR2_YBIC_HCOEF0

_SR2_YBIC_HCOEF0 0x32d8

Bit(s) R/W Default Description

31:24 R/W 0 sr2_y_bic_hcoeff03, signed

23:16 R/W 0 sr2_y_bic_hcoeff02, signed

15: 8 R/W 64 sr2_y_bic_hcoeff01, signed

7: 0 R/W 0 sr2_y_bic_hcoeff00, signed

SRSHARP1_SHARP_SR2_YBIC_HCOEF1 0x32d9

Bit(s) R/W Default Description

31:24 R/W -4 sr2_y_bic_hcoeff13 , signed

23:16 R/W 36 sr2_y_bic_hcoeff12 , signed

15: 8 R/W 36 sr2_y_bic_hcoeff11 , signed

7: 0 R/W -4 sr2_y_bic_hcoeff10 , signed

SRSHARP1_SHARP_SR2_CBIC_HCOEF0 0x32da

258/554 AMLOGIC, Inc. Proprietary

S912 Datasheet Revision 0.1

Bit(s) R/W Default Description

31:24 R/W 0 sr2_c_bic_hcoeff03 , signed

23:16 R/W 21 sr2_c_bic_hcoeff02 , signed

15: 8 R/W 22 sr2_c_bic_hcoeff01 , signed

7: 0 R/W 21 sr2_c_bic_hcoeff00 , signed

SRSHARP1_SHARP_SR2_CBIC_HCOEF1 0x32db

Bit(s) R/W Default Description

31:24 R/W -4 sr2_c_bic_hcoeff13 , signed

23:16 R/W 36 sr2_c_bic_hcoeff12 , signed

15: 8 R/W 36 sr2_c_bic_hcoeff11 , signed

7: 0 R/W -4 sr2_c_bic_hcoeff10 , signed

SHARP_SR2_YBIC_VCOEF0 0x32dc

Bit(s) R/W Default Description

31:24 R/W 0 sr2_y_bic_vcoeff03 , signed

23:16 R/W 0 sr2_y_bic_vcoeff02 , signed

15: 8 R/W 64 sr2_y_bic_vcoeff01 , signed

7: 0 R/W 0 sr2_y_bic_vcoeff00 , signed

SRSHARP1_SHARP_SR2_YBIC_VCOEF1 0x32dd

Bit(s) R/W Default Description

31:24 R/W -4 sr2_y_bic_vcoeff13 , signed

23:16 R/W 36 sr2_y_bic_vcoeff12 , signed

15: 8 R/W 36 sr2_y_bic_vcoeff11 , signed

7: 0 R/W -4 sr2_y_bic_vcoeff10 , signed

SRSHARP1_SHARP_SR2_CBIC_VCOEF0 0x32de

Bit(s) R/W Default Description

31:24 R/W 0 sr2_c_bic_vcoeff03 , signed

23:16 R/W 21 sr2_c_bic_vcoeff02 , signed

15: 8 R/W 22 sr2_c_bic_vcoeff01 , signed

7: 0 R/W 21 sr2_c_bic_vcoeff00 , signed

SRSHARP1_SHARP_SR2_CBIC_VCOEF1 0x32df

Bit(s) R/W Default Description

31:24 R/W -4 sr2_c_bic_vcoeff13 , signed

23:16 R/W 36 sr2_c_bic_vcoeff12 , signed

15: 8 R/W 36 sr2_c_bic_vcoeff11 , signed

7: 0 R/W -4

4 sr2_c_bic_vcoeff10 , signed

SRSHARP1_SHARP_SR2_MISC 0x32e0

Bit(s) R/W Default Description

31:2 R/W reserved

1 R/W 0 sr2_cmpmux_bef , 0 : no swap for YUV/RGB; 1: swap for YUV/RGB, YUV/RGB->UVY/GBR

0 R/W 0 sr2_cmpmux_aft , 0 : no swap for YUV/RGB; 1: swap for YUV/RGB, UVY/GBR->YUV/RGB

SRSHARP1_SHARP_DEJ2_PRC 0x32e1

Bit(s) R/W Default Description

31:24 R/W 5 sr2_dejaggy2_hcon_thrd, hcon threshold, only pixels with hcon equal or larger than this value can be detected

as jaggy2

23:16 R/W 30 sr2_dejaggy2_svdif_thrd, abs(sum(vdif[4])) threshold to decide jaggy2.

15: 8 R/W 32 sr2_dejaggy2_svdif_rate, sum(abs(vdif[4])) <= (rate*abs(sum(vdif[4]))/16), rate to decide jaggy2

7: 0 R/W -3 sr2_dejaggy2_vdif_thrd, vdif threshold for same trend decision, these value is the margin for not same trend,

if >0, means need to be same trend, if <0, can be a little bit glitch.

259/554 AMLOGIC, Inc. Proprietary

You might also like

- Z80 - Basic Programming Techniques - Answer of ExercisesDocument9 pagesZ80 - Basic Programming Techniques - Answer of ExercisesHaddouNo ratings yet

- Each Bit Reset Each ChannelDocument4 pagesEach Bit Reset Each Channelasdasdasfli.elkinNo ratings yet

- Car Gear Indicator AbstractDocument5 pagesCar Gear Indicator Abstractapi-3818780No ratings yet

- Design Task 1 Final LabDocument15 pagesDesign Task 1 Final Labrazorblademk2No ratings yet

- Dasfgderh 57y45Document4 pagesDasfgderh 57y45asdasdasfli.elkinNo ratings yet

- Mikroc GLCD Library PDFDocument12 pagesMikroc GLCD Library PDFKenaiNo ratings yet

- Player Prev - LogDocument8 pagesPlayer Prev - LogLuis DokoupilNo ratings yet

- Led On of ConinterrupcionDocument2 pagesLed On of ConinterrupcionManuel sotoNo ratings yet

- Altera Nios II BSP SummaryDocument12 pagesAltera Nios II BSP SummarywwasdNo ratings yet

- ARM Cortex-A9 ARM V7-A A Programmer's PerspectiveDocument22 pagesARM Cortex-A9 ARM V7-A A Programmer's PerspectiveRayane GadelhaNo ratings yet

- Lecture6-Bit AddressabilityDocument27 pagesLecture6-Bit AddressabilityJawad shah SayedNo ratings yet

- Mks Ct150 Delta A. Hmi Factory Settings: Appendix B Communication - Scredit Software User ManualDocument2 pagesMks Ct150 Delta A. Hmi Factory Settings: Appendix B Communication - Scredit Software User ManualryoNo ratings yet

- Gambit MLK MT - A00 - 20180202 - 01Document107 pagesGambit MLK MT - A00 - 20180202 - 01Tin Học Chí CôngNo ratings yet

- Unit 2 - 2Document44 pagesUnit 2 - 2SurajNo ratings yet

- Mitsubishi FX5U: HMI SettingDocument5 pagesMitsubishi FX5U: HMI SettingmbgprsmsNo ratings yet

- Conocimiento Del Software de Desarrollo ATMEL Studio: 1. TemaDocument6 pagesConocimiento Del Software de Desarrollo ATMEL Studio: 1. TemaKhrizzCorreaNo ratings yet

- Supporting Document For Assembly ProgrammingDocument7 pagesSupporting Document For Assembly ProgrammingJoginder YadavNo ratings yet

- 3500/4500 CENCAL: Addr. Hex Size Item Description R/W Min Max DP Def. Meas. UnitDocument5 pages3500/4500 CENCAL: Addr. Hex Size Item Description R/W Min Max DP Def. Meas. UnitmarcoNo ratings yet

- Cnss FW Logs CurrentDocument246 pagesCnss FW Logs CurrentНиколай ЯнчуNo ratings yet

- Bootrst Ivsel Reset Address Interrupt Vectors Start AddressDocument1 pageBootrst Ivsel Reset Address Interrupt Vectors Start AddressnamerNo ratings yet

- 3 Program CodeDocument15 pages3 Program Codergkusumba100% (1)

- Mitsubishi FX5UDocument5 pagesMitsubishi FX5UmarioNo ratings yet

- Lab 7 ADCDocument19 pagesLab 7 ADCakkauntdlyaigrichegotoescheNo ratings yet

- Lab5 - 1 EngDocument13 pagesLab5 - 1 EngMai Huỳnh TháiNo ratings yet

- Data Access Mobility Call DropDocument21 pagesData Access Mobility Call DropArio NugrohoNo ratings yet

- Z80 ProgrammingDocument30 pagesZ80 ProgrammingDusan TrisicNo ratings yet

- Arduino and Stepper MotorDocument5 pagesArduino and Stepper Motorchandramahesh736No ratings yet

- 15140-1 Vostro - 3668 - 3669 - 3268 - 3667 - 3660 - 3267Document107 pages15140-1 Vostro - 3668 - 3669 - 3268 - 3667 - 3660 - 3267Multiservicio DELEDENNo ratings yet

- Timerss PracDocument14 pagesTimerss Prac1967 Darshan GaragattiNo ratings yet

- RS Power Adjustment Template CRDocument10 pagesRS Power Adjustment Template CRHeru PrasetiyoNo ratings yet

- Power List GPIO List: Confidential Sony Ericsson Diagram SchemaDocument11 pagesPower List GPIO List: Confidential Sony Ericsson Diagram Schemateguh2997No ratings yet

- BCM-7602-G01 BLE Transparent Transmission Module: Features General DescriptionDocument4 pagesBCM-7602-G01 BLE Transparent Transmission Module: Features General DescriptionZondaNo ratings yet

- Hardware PinoutDocument5 pagesHardware Pinouthansmru87No ratings yet

- External Dimension: JHD12864EDocument1 pageExternal Dimension: JHD12864EdocumentossethNo ratings yet

- Wh1602b Ygk CPDocument20 pagesWh1602b Ygk CPMoni Gote del OrtusNo ratings yet

- Lc1622 Smlyh6 EtcDocument26 pagesLc1622 Smlyh6 EtcsaumyakanthaNo ratings yet

- AdcDocument1 pageAdcPhilip KononenkoNo ratings yet

- List of programs-CHE S6 and CES6-Revision 2015Document18 pagesList of programs-CHE S6 and CES6-Revision 2015Anna JoseNo ratings yet

- Player LogDocument7 pagesPlayer LogPaulNo ratings yet

- Kylin SATA Arch DraftDocument34 pagesKylin SATA Arch DraftАндрашNo ratings yet

- LED Moving Message Diaply Using PIC16f628 CD4017 and 74LS595Document5 pagesLED Moving Message Diaply Using PIC16f628 CD4017 and 74LS595murugaraj19822100% (1)

- FFTDocument40 pagesFFTsreekuttymsNo ratings yet

- 03-Character LCD DatasheetDocument25 pages03-Character LCD DatasheetmohamedNo ratings yet

- Crash DumpDocument2 pagesCrash DumppapafritaconquesoNo ratings yet

- Experiment No.: 5Document6 pagesExperiment No.: 5Dhrumil ManiyarNo ratings yet

- Orca Share Media1510735460791Document2 pagesOrca Share Media1510735460791jairoNo ratings yet

- Design With Microprocessors: Year III Computer Science 1-st Semester Lecture 2: AVR Registers and InstructionsDocument26 pagesDesign With Microprocessors: Year III Computer Science 1-st Semester Lecture 2: AVR Registers and InstructionsSelmaGogaNo ratings yet

- Sy7208abc C80514Document13 pagesSy7208abc C80514Luis SantosNo ratings yet

- Modbus Protocol Fieldlogger v17x enDocument17 pagesModbus Protocol Fieldlogger v17x enAlexis Javier HernandezNo ratings yet

- ABB ProgrammingDocument2 pagesABB Programmingemilio garavitoNo ratings yet

- FPGA Keyboard Interface - Embedded ThoughtsDocument29 pagesFPGA Keyboard Interface - Embedded ThoughtsAshok kumarNo ratings yet

- Rbs 6201 3g 3rd Carrier Site - XMLDocument6 pagesRbs 6201 3g 3rd Carrier Site - XMLsyednooman1No ratings yet

- Tc1602a 01TDocument18 pagesTc1602a 01Thungdt4No ratings yet

- Digital Systems - Mini AVR 5: Pere Pal' A - Alexis L OpezDocument15 pagesDigital Systems - Mini AVR 5: Pere Pal' A - Alexis L OpezPau Susin AlsinaNo ratings yet

- LPC17xx ARM Cortex M3 Assembly Language ExampleDocument11 pagesLPC17xx ARM Cortex M3 Assembly Language ExampleDaniel Ramos50% (2)

- LPC 17xx ADC: Done byDocument13 pagesLPC 17xx ADC: Done byabu taherNo ratings yet

- HCSR04 Tutorial v2Document8 pagesHCSR04 Tutorial v2El RuniNo ratings yet

- Interfacing The HC05 MCU To A Multichannel Digital-to-Analog Converter Using The MC68HC705C8A and The MC68HC705J1ADocument24 pagesInterfacing The HC05 MCU To A Multichannel Digital-to-Analog Converter Using The MC68HC705C8A and The MC68HC705J1AradaresNo ratings yet

- TS-MPPT-600V Modbus Doc Public - Aug-2014Document27 pagesTS-MPPT-600V Modbus Doc Public - Aug-2014Assad Ullah KhanNo ratings yet

- 9.3.7. GPIO 4 7 Pin Select: 0x2622: S805 Datasheet Revision 0.8Document3 pages9.3.7. GPIO 4 7 Pin Select: 0x2622: S805 Datasheet Revision 0.8asdasdasfli.elkinNo ratings yet

- 14.4. Register Description: 14.4.1. I2C - M - 0 - CONTROL - REG 0x2140Document3 pages14.4. Register Description: 14.4.1. I2C - M - 0 - CONTROL - REG 0x2140asdasdasfli.elkinNo ratings yet

- Isa - Timerg CBUS: 0x2666Document3 pagesIsa - Timerg CBUS: 0x2666asdasdasfli.elkinNo ratings yet

- Func Ti OnsDocument3 pagesFunc Ti Onsasdasdasfli.elkinNo ratings yet

- Simplecv: "Exit " "CTRL+ D" "Clear" "Tutorial" "Example" "Forums" "Walkthrough"Document5 pagesSimplecv: "Exit " "CTRL+ D" "Clear" "Tutorial" "Example" "Forums" "Walkthrough"asdasdasfli.elkinNo ratings yet

- 8.2.1. GPIO Bank X: S805 Datasheet Revision 0.8Document5 pages8.2.1. GPIO Bank X: S805 Datasheet Revision 0.8asdasdasfli.elkinNo ratings yet

- Chapter 3 C Language and Arduino Type Ide For Pcduino: Toolchain of The Arduino LibraryDocument3 pagesChapter 3 C Language and Arduino Type Ide For Pcduino: Toolchain of The Arduino Libraryasdasdasfli.elkinNo ratings yet

- 001Document3 pages001asdasdasfli.elkinNo ratings yet

- EPM240MAINBOARD Schematic DiagramDocument2 pagesEPM240MAINBOARD Schematic Diagramasdasdasfli.elkinNo ratings yet

- Altera MAX II Family IntroductionDocument6 pagesAltera MAX II Family Introductionasdasdasfli.elkinNo ratings yet

- R8M DataSheet V02Document14 pagesR8M DataSheet V02asdasdasfli.elkinNo ratings yet

- Bioemg Iii: Bioresearch Assoc. IncDocument3 pagesBioemg Iii: Bioresearch Assoc. Incasdasdasfli.elkinNo ratings yet

- MAX II Device Family DatasheetDocument86 pagesMAX II Device Family Datasheetasdasdasfli.elkinNo ratings yet

- Tcps 2 Final WebDocument218 pagesTcps 2 Final WebBornaGhannadiNo ratings yet

- Culvert Design Write UpDocument8 pagesCulvert Design Write UpifylasyNo ratings yet

- Gender InequalityDocument9 pagesGender InequalityRhzNo ratings yet

- Cee 2005 - 06Document129 pagesCee 2005 - 06iloveeggxPNo ratings yet

- For Purposeful and Meaningful Technology Integration in The ClassroomDocument19 pagesFor Purposeful and Meaningful Technology Integration in The ClassroomVincent Chris Ellis TumaleNo ratings yet

- SLC 10 ScienceDocument16 pagesSLC 10 SciencePffflyers KurnawanNo ratings yet

- InheretanceDocument8 pagesInheretancefarhan.mukhtiarNo ratings yet

- Spinning CalculationDocument178 pagesSpinning Calculationamboklate69% (16)

- Tips Experiments With MatlabDocument190 pagesTips Experiments With MatlabVishalNo ratings yet

- Business Cognate SBADocument20 pagesBusiness Cognate SBAUncle TravisNo ratings yet

- Mixed Methods Research PDFDocument14 pagesMixed Methods Research PDFChin Ing KhangNo ratings yet

- Manufacturing Technology - Metrology: Dr.B.Ramamoorthy Professor Manufacturing Engg. Section Iitmadras 600 036Document22 pagesManufacturing Technology - Metrology: Dr.B.Ramamoorthy Professor Manufacturing Engg. Section Iitmadras 600 036Ramasubramanian KannanNo ratings yet

- My Publications and Workshops ListDocument4 pagesMy Publications and Workshops Listraviteja tankalaNo ratings yet

- Fendrick Govt 720 Global Problem EssayDocument5 pagesFendrick Govt 720 Global Problem Essayapi-283893191No ratings yet

- Manage Your Nude PhotosDocument14 pagesManage Your Nude PhotosRick80% (5)

- Cambridge IGCSE ™: Co-Ordinated Sciences 0654/61 October/November 2022Document9 pagesCambridge IGCSE ™: Co-Ordinated Sciences 0654/61 October/November 2022wangfeifei620No ratings yet

- MAK Halliday The Language of ScienceDocument268 pagesMAK Halliday The Language of ScienceJeneiGabriellaOfő100% (4)

- Lecture Notes For Transition To Advanced MathematicsDocument115 pagesLecture Notes For Transition To Advanced MathematicsAngela WaltersNo ratings yet

- DBR G+24 Building ProjectDocument28 pagesDBR G+24 Building ProjectShobhit Mohta100% (1)

- Fuzzy Ideals and Fuzzy Quasi-Ideals in Ternary Semirings: J. Kavikumar and Azme Bin KhamisDocument5 pagesFuzzy Ideals and Fuzzy Quasi-Ideals in Ternary Semirings: J. Kavikumar and Azme Bin KhamismsmramansrimathiNo ratings yet

- IRJES 2017 Vol. 1 Special Issue 2 English Full Paper 038Document6 pagesIRJES 2017 Vol. 1 Special Issue 2 English Full Paper 038liew wei keongNo ratings yet

- Shadow Volume in Real-Time Rendering: Abdelmouméne Zerari Mohamed Chaouki BabaheniniDocument6 pagesShadow Volume in Real-Time Rendering: Abdelmouméne Zerari Mohamed Chaouki BabaheniniRizqiy Bryan McfaddenNo ratings yet

- Pal and Lisa Senior Secondary School Senior Five End of Term Two ExaminationsDocument3 pagesPal and Lisa Senior Secondary School Senior Five End of Term Two ExaminationsAthiyo MartinNo ratings yet

- Mmims5elesson BiomesDocument3 pagesMmims5elesson Biomesapi-490524730100% (1)

- Vertical Axis Wind Turbine ProjDocument2 pagesVertical Axis Wind Turbine Projmacsan sanchezNo ratings yet

- Disneyland (Manish N Suraj)Document27 pagesDisneyland (Manish N Suraj)Suraj Kedia0% (1)

- VGB-R 105 e ContentDocument7 pagesVGB-R 105 e Contentramnadh8031810% (2)

- Physics For EngineersDocument5 pagesPhysics For EngineersKonstantinos FilippakosNo ratings yet

- Why Balance Your HomeDocument11 pagesWhy Balance Your HomeWalkinLANo ratings yet

- Design BasisDocument9 pagesDesign BasisSamiksha RajdevNo ratings yet