Professional Documents

Culture Documents

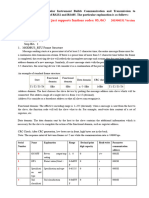

FCRIS Register (See Page 507)

Uploaded by

Mustafa Demir0 ratings0% found this document useful (0 votes)

6 views1 pageThis document describes the bit/field names, types, reset values, and descriptions of status and clear registers. It includes fields for invalid data masked interrupt status and clear (INVDMISC), voltage masked interrupt status and clear (VOLTMISC), and EEPROM masked interrupt status and clear (EMISC). Each field reads as 0 when the interrupt has not occurred and 1 when the interrupt has occurred and been unmasked. Writing a 1 clears both the specific field and a corresponding bit in another register.

Original Description:

Original Title

vm 4

Copyright

© © All Rights Reserved

Available Formats

DOC, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentThis document describes the bit/field names, types, reset values, and descriptions of status and clear registers. It includes fields for invalid data masked interrupt status and clear (INVDMISC), voltage masked interrupt status and clear (VOLTMISC), and EEPROM masked interrupt status and clear (EMISC). Each field reads as 0 when the interrupt has not occurred and 1 when the interrupt has occurred and been unmasked. Writing a 1 clears both the specific field and a corresponding bit in another register.

Copyright:

© All Rights Reserved

Available Formats

Download as DOC, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

6 views1 pageFCRIS Register (See Page 507)

Uploaded by

Mustafa DemirThis document describes the bit/field names, types, reset values, and descriptions of status and clear registers. It includes fields for invalid data masked interrupt status and clear (INVDMISC), voltage masked interrupt status and clear (VOLTMISC), and EEPROM masked interrupt status and clear (EMISC). Each field reads as 0 when the interrupt has not occurred and 1 when the interrupt has occurred and been unmasked. Writing a 1 clears both the specific field and a corresponding bit in another register.

Copyright:

© All Rights Reserved

Available Formats

Download as DOC, PDF, TXT or read online from Scribd

You are on page 1of 1

Bit/Field Name Type Reset Description

Invalid Data Masked Interrupt Status and Clear

Value Description

When read, a 0 indicates that an interrupt has not occurred.

A write of 0 has no effect on the state of this bit.

0

When read, a 1 indicates that an unmasked interrupt was

signaled.

Writing a 1 to this bit clears INVDMISC and also the INVDRIS

bit in the FCRIS register (see page 507).

1

10 INVDMISC R/W1C 0

VOLT Masked Interrupt Status and Clear

Value Description

When read, a 0 indicates that an interrupt has not occurred.

A write of 0 has no effect on the state of this bit.

0

When read, a 1 indicates that an unmasked interrupt was

signaled.

Writing a 1 to this bit clears VOLTMISC and also the VOLTRIS

bit in the FCRIS register (see page 507).

1

9 VOLTMISC R/W1C 0

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

8:3 reserved RO 0

EEPROM Masked Interrupt Status and Clear

Value Description

When read, a 0 indicates that an interrupt has not occurred.

A write of 0 has no effect on the state of this bit.

0

When read, a 1 indicates that an unmasked interrupt was

signaled.

Writing a 1 to this bit clears EMISC and also the ERIS bit in the

FCRIS register (see page 507).

1

2 EMISC R/W1C 0

Programming Masked Interrupt Status and Clear

Value Description

When read, a 0 indicates that a programming cycle complete

interrupt has not occurred.

A write of 0 has no effect on the state of this bit.

0

When read, a 1 indicates that an unmasked interrupt was

signaled because a programming cycle completed.

Writing a 1 to this bit clears PMISC

You might also like

- FCRIS Register (See Page 507)Document1 pageFCRIS Register (See Page 507)Mustafa DemirNo ratings yet

- FCRIS Register (See Page 507)Document1 pageFCRIS Register (See Page 507)Mustafa DemirNo ratings yet

- FCRIS Register (See Page 507)Document1 pageFCRIS Register (See Page 507)Mustafa DemirNo ratings yet

- FCRIS Register (See Page 507)Document1 pageFCRIS Register (See Page 507)Mustafa DemirNo ratings yet

- 508 January 19, 2013 Texas Instruments-Advance Information Internal MemoryDocument1 page508 January 19, 2013 Texas Instruments-Advance Information Internal MemoryMustafa DemirNo ratings yet

- KM 5Document1 pageKM 5Mustafa DemirNo ratings yet

- Asset Identification Eeprom AT24RF08C: FeaturesDocument21 pagesAsset Identification Eeprom AT24RF08C: Featuresmarkstevens9No ratings yet

- Avr NotesDocument20 pagesAvr Noteschandrakant chaudhariNo ratings yet

- 24fj IOApNoteDocument36 pages24fj IOApNoteLuis Di PintoNo ratings yet

- LPC2148 Interrupt TutorialDocument13 pagesLPC2148 Interrupt TutorialSomil N SwarnaNo ratings yet

- Section 10. I - O PortsDocument24 pagesSection 10. I - O PortsVlad MizeffNo ratings yet

- Hi3521D V100 H.265 Codec Processor Data SheetDocument1,017 pagesHi3521D V100 H.265 Codec Processor Data SheetNguyễn Hữu NamNo ratings yet

- Short Notes Chapter 8 (Lecture 22-23) :: Why Interrupts Must Be Asynchronous?Document4 pagesShort Notes Chapter 8 (Lecture 22-23) :: Why Interrupts Must Be Asynchronous?The best maxNo ratings yet

- 24fj PPSApNoteDocument26 pages24fj PPSApNoteLuis Di PintoNo ratings yet

- Logicore Ip Fast Simplex Link (FSL) V20 Bus (V2.11C) : Ffs Block RamsDocument9 pagesLogicore Ip Fast Simplex Link (FSL) V20 Bus (V2.11C) : Ffs Block RamswachutunaiNo ratings yet

- msp430 Users GuideDocument414 pagesmsp430 Users GuideYang CeNo ratings yet

- Internal Registers in Pic MicroctrlDocument4 pagesInternal Registers in Pic MicroctrljaimefpolisNo ratings yet

- Electronic Load-SCPI ProtocolDocument41 pagesElectronic Load-SCPI Protocolrogeriocorrea601No ratings yet

- Read Modify WriteDocument2 pagesRead Modify WriteMisbah UrRehman100% (1)

- F2010 552 Project DescriptionDocument6 pagesF2010 552 Project DescriptionJamil_fawadNo ratings yet

- Embedded SystemsDocument9 pagesEmbedded SystemsqasdfghjklwertyNo ratings yet

- Atmel AT24RF08C EEPROM Data SheetDocument21 pagesAtmel AT24RF08C EEPROM Data SheetJames HowardNo ratings yet

- User's GuideDocument512 pagesUser's Guideapi-3744762No ratings yet

- ModbusDocument6 pagesModbusCésar YagüeNo ratings yet

- The 8086 Interrupt Mechanism: The 8259A PICDocument14 pagesThe 8086 Interrupt Mechanism: The 8259A PICSatishNo ratings yet

- Asset Identification Eeprom AT24RF08C: FeaturesDocument22 pagesAsset Identification Eeprom AT24RF08C: FeaturesG & GNo ratings yet

- Merricks WeigherDocument4 pagesMerricks WeigheripunggNo ratings yet

- Serial Ata Ahci Tech Proposal Rev1 3 1Document22 pagesSerial Ata Ahci Tech Proposal Rev1 3 1Kuani LeeNo ratings yet

- UART (Universal Asynchronous Receiver/Transmitter) TUTORIAL Using Edk in Ml403 BoardDocument8 pagesUART (Universal Asynchronous Receiver/Transmitter) TUTORIAL Using Edk in Ml403 BoardphanieceNo ratings yet

- 8085 Microprocessor Architecture and Programming-1Document92 pages8085 Microprocessor Architecture and Programming-1ShubhamNo ratings yet

- Recommended Usage of Microchip SPI Serial EEPROM Devices: Author: Chris Parris Microchip Technology IncDocument8 pagesRecommended Usage of Microchip SPI Serial EEPROM Devices: Author: Chris Parris Microchip Technology IncHenrique VianaNo ratings yet

- UART (Universal Asynchronous Receiver/Transmitter) TUTORIAL Using Edk in Ml403 Board Part 2: InterruptionsDocument8 pagesUART (Universal Asynchronous Receiver/Transmitter) TUTORIAL Using Edk in Ml403 Board Part 2: InterruptionsKrishnakumar SomanpillaiNo ratings yet

- Asynchronous FIFODocument7 pagesAsynchronous FIFOshivakumar v gadedNo ratings yet

- ABCIP Communication DriverDocument49 pagesABCIP Communication DriverGrébneva AlënaNo ratings yet

- PIC16F87XA: 3.7 Protection Against Spurious Write 3.8 Operation During Code-ProtectDocument5 pagesPIC16F87XA: 3.7 Protection Against Spurious Write 3.8 Operation During Code-Protectvitor valeNo ratings yet

- Architecture Body: 2. As A Set of Concurrent Assignment 3. As A Set of Sequential Assignment 4. AnyDocument34 pagesArchitecture Body: 2. As A Set of Concurrent Assignment 3. As A Set of Sequential Assignment 4. AnyJeevan BhatNo ratings yet

- Preliminary Specifications LE25FV101T 1M (128k Words × 8bits) Serial Flash EEPROMDocument10 pagesPreliminary Specifications LE25FV101T 1M (128k Words × 8bits) Serial Flash EEPROMsasNo ratings yet

- PIO and Interrupt StudentsDocument12 pagesPIO and Interrupt StudentsLê Đình TiếnNo ratings yet

- Lecture 05 PIC Microcontroller Interrupts and EEPROM Data MemoryDocument7 pagesLecture 05 PIC Microcontroller Interrupts and EEPROM Data MemoryJpricarioNo ratings yet

- Beco2200 m3311Document66 pagesBeco2200 m3311Victor Jose Romero FernandezNo ratings yet

- Scripts 14 16 2Document3 pagesScripts 14 16 2Feri FeriNo ratings yet

- CPR04 Modbus Protocol 2v01Document21 pagesCPR04 Modbus Protocol 2v01ing.lunarNo ratings yet

- BC-5000&5150 HL7 Communication Protocol V1.0 enDocument25 pagesBC-5000&5150 HL7 Communication Protocol V1.0 enQamar MunirNo ratings yet

- Microprpcessor 8086Document29 pagesMicroprpcessor 8086amanNo ratings yet

- Lab 10Document8 pagesLab 10zeeshan AkramNo ratings yet

- Technical Reference Options and Adapters Volume 2 3of3Document243 pagesTechnical Reference Options and Adapters Volume 2 3of3kgrhoadsNo ratings yet

- 02 The PIC16F877 Memory Map and ProgramingDocument15 pages02 The PIC16F877 Memory Map and ProgramingAllen AlaskaNo ratings yet

- 05 Condition Codes PDFDocument14 pages05 Condition Codes PDFAnandu KumarNo ratings yet

- Discontinued: Synchronous FIFO 5.0Document10 pagesDiscontinued: Synchronous FIFO 5.0Prathap NsNo ratings yet

- Intel 8253 - Programmable Interval Timer: Difference Between 8253 and 8254Document24 pagesIntel 8253 - Programmable Interval Timer: Difference Between 8253 and 8254Varun YadavNo ratings yet

- ATmega8 RegisterInfo v0 2Document12 pagesATmega8 RegisterInfo v0 2api-3699101No ratings yet

- How To Read or Write A Single Parameter Using FB287Document7 pagesHow To Read or Write A Single Parameter Using FB287MiguelGonzalezNo ratings yet

- Instruções LadderDocument142 pagesInstruções Ladderjurgen.kdiasNo ratings yet

- Mani Es ch2Document34 pagesMani Es ch2Dinesh PrabhuNo ratings yet

- Technical Manual Modbus (Recloser-Map-S) Etr300-R & Evrc2a-Nt Ver1.01 201807Document28 pagesTechnical Manual Modbus (Recloser-Map-S) Etr300-R & Evrc2a-Nt Ver1.01 201807danh vo100% (1)

- 5131 13 46 PDocument10 pages5131 13 46 PAneeshNo ratings yet

- Agc 150 Modbus Server Tables 4189341212 UkDocument601 pagesAgc 150 Modbus Server Tables 4189341212 UkShokunbi OyedeleNo ratings yet

- WAN TECHNOLOGY FRAME-RELAY: An Expert's Handbook of Navigating Frame Relay NetworksFrom EverandWAN TECHNOLOGY FRAME-RELAY: An Expert's Handbook of Navigating Frame Relay NetworksNo ratings yet

- PIC Projects and Applications using C: A Project-based ApproachFrom EverandPIC Projects and Applications using C: A Project-based ApproachRating: 4 out of 5 stars4/5 (2)

- MV 4Document1 pageMV 4Mustafa DemirNo ratings yet

- Den 4Document2 pagesDen 4Mustafa DemirNo ratings yet

- Channel If The Corresponding EOCIE or JEOCIE Bit Is SetDocument1 pageChannel If The Corresponding EOCIE or JEOCIE Bit Is SetMustafa DemirNo ratings yet

- Channel If The Corresponding EOCIE or JEOCIE Bit Is SetDocument1 pageChannel If The Corresponding EOCIE or JEOCIE Bit Is SetMustafa DemirNo ratings yet

- Channel If The Corresponding EOCIE or JEOCIE Bit Is SetDocument1 pageChannel If The Corresponding EOCIE or JEOCIE Bit Is SetMustafa DemirNo ratings yet

- Channel If The Corresponding EOCIE or JEOCIE Bit Is SetDocument1 pageChannel If The Corresponding EOCIE or JEOCIE Bit Is SetMustafa DemirNo ratings yet

- Channel If The Corresponding EOCIE or JEOCIE Bit Is SetDocument1 pageChannel If The Corresponding EOCIE or JEOCIE Bit Is SetMustafa DemirNo ratings yet