0% found this document useful (0 votes)

282 views17 pages8086 System Architecture Overview

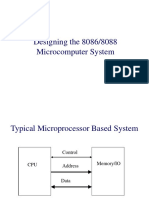

The document discusses the operating modes and control signals of the Intel 8288 bus controller chip. It describes the I/O bus mode where I/O command lines are always enabled and no waiting is required to access the I/O bus. It also describes the system bus mode where both memory and I/O commands must wait for bus arbitration. The document outlines the control outputs of the 8288 including Data Enable, Data Transmit/Receive, and Master Cascade Enable/Peripheral Data Enable. It also discusses the maximum-mode memory read and write cycles of the 8086 system and memory interfacing in maximum mode.

Uploaded by

Aditya KumarCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

282 views17 pages8086 System Architecture Overview

The document discusses the operating modes and control signals of the Intel 8288 bus controller chip. It describes the I/O bus mode where I/O command lines are always enabled and no waiting is required to access the I/O bus. It also describes the system bus mode where both memory and I/O commands must wait for bus arbitration. The document outlines the control outputs of the 8288 including Data Enable, Data Transmit/Receive, and Master Cascade Enable/Peripheral Data Enable. It also discusses the maximum-mode memory read and write cycles of the 8086 system and memory interfacing in maximum mode.

Uploaded by

Aditya KumarCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd