Professional Documents

Culture Documents

Counter Ics: Digital Logic Design Laboratory

Uploaded by

Trương Quang Tường0 ratings0% found this document useful (0 votes)

19 views7 pagesOriginal Title

Lab7_Spring2022 (2)

Copyright

© © All Rights Reserved

Available Formats

DOCX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

19 views7 pagesCounter Ics: Digital Logic Design Laboratory

Uploaded by

Trương Quang TườngCopyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

You are on page 1of 7

INTERNATIONAL UNIVERSITY

SCHOOL OF ELECTRICAL ENGINEERING

Digital Logic Design Laboratory

Lab 7

Counter ICs

Full name: …………………………………………….

Student number: ………………………………….

Class: ……………………………………………….......

Date: …………………………………………………....

Digital Logic Design Laboratory 1-7

INTERNATIONAL UNIVERSITY

SCHOOL OF ELECTRICAL ENGINEERING

I. Objectives

In this laboratory, students will study:

- Understand the operation of Counter of IC

- Use a Counter of IC and design/implement a circuit.

II. Procedure

1. Design and implement a synchronous counter by the given state diagram

Design and implement a synchronous 3-bit counter shown in the given diagram as

shown in Figure 1 using D Flip Flops

Figure 1. State diagram

Transition Table

Present State Next State

Q2 Q1 Q0 D2 D1 D0 Q2 Q1 Q0

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

Digital Logic Design Laboratory 2-7

INTERNATIONAL UNIVERSITY

SCHOOL OF ELECTRICAL ENGINEERING

D0 = ………………….. D1 = ………………….. D2 = …………………..

Implement the circuit via simulation software and paste the result in here

Make comment on the results

2. Decade counter 74XX90

a. Investigate decade counter 74XX90

IC 74XX90 contains a divide-by-two counter and a divide-by-five counter as shown in

Figure 2. The truth table for the counter 74XX90 is shown in Table 1.

Connect Clock signal to CPO

Connect Q0 to CP 1

Connect MS1, MS2, MR1, MR2 to switches for controlling operations

Connect outputs (Q0, Q1, Q2, Q3) to BCD to 7-segment display block

Figure 2. IC 74XX90

Digital Logic Design Laboratory 3-7

INTERNATIONAL UNIVERSITY

SCHOOL OF ELECTRICAL ENGINEERING

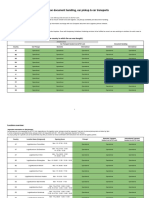

Table 1. Truth table for 74XX90

Implement the circuit (Figure 2) via simulation software and paste the result in here

Make comment on the results

b. Adjust the circuit to make a MOD-7 counter (counting from 0 to 6)

Implement the circuit via simulation software and paste the result in here

Digital Logic Design Laboratory 4-7

INTERNATIONAL UNIVERSITY

SCHOOL OF ELECTRICAL ENGINEERING

Make comment on the results (show the way to implement)

3. Decade counter 74HC390

a. Investigate Dual 4-Bit Decade Counter

IC 74HC390 includes 2 decimal counters

Ra, Rb: Clear (high level active)

QA, QB, QC and QD: outputs of the MOD-10 counter

Figure 3. 74HC390 Counter having M=100

- The outputs QA, QB, QC and QD are connected to BCD TO 7-SEGMENT

DISPLAY

- The Ra, Rb inputs are connected to switches to control the circuit operation.

Implement the circuit (Figure 3) via simulation software and paste the result in here

Digital Logic Design Laboratory 5-7

INTERNATIONAL UNIVERSITY

SCHOOL OF ELECTRICAL ENGINEERING

Make comment on the results

b. Design 74HC390 as a MOD-60 counter (counting from 0 to 59)

Implement the circuit via simulation software and paste the result in here

Make comment on the results (show the way to implement)

Digital Logic Design Laboratory 6-7

INTERNATIONAL UNIVERSITY

SCHOOL OF ELECTRICAL ENGINEERING

Digital Logic Design Laboratory 7-7

You might also like

- Demultiplexers: Digital Logic Design LaboratoryDocument8 pagesDemultiplexers: Digital Logic Design LaboratoryTrương Quang TườngNo ratings yet

- Lab 3Document10 pagesLab 3tuan phanNo ratings yet

- 1 2 7 P Understandingdigitaldesign RNG UnfinishedDocument5 pages1 2 7 P Understandingdigitaldesign RNG Unfinishedapi-287488627No ratings yet

- 1 2 7 Ak Understandingdigitaldesign RNGDocument5 pages1 2 7 Ak Understandingdigitaldesign RNGapi-290804719No ratings yet

- DSDDocument45 pagesDSDnama varapuNo ratings yet

- Digital Electronics Lab ManualDocument75 pagesDigital Electronics Lab ManualLikithaReddy YenumulaNo ratings yet

- 1 2 7 P Understandingdigitaldesign RNG (Finished)Document7 pages1 2 7 P Understandingdigitaldesign RNG (Finished)api-287657167100% (1)

- Flip Flops and Counters: Digital Logic Design LaboratoryDocument16 pagesFlip Flops and Counters: Digital Logic Design LaboratoryTrương Quang TườngNo ratings yet

- ENGR2105 - Laboratory 3 - Seven Segment LED Stop Clock in Assembly and CDocument6 pagesENGR2105 - Laboratory 3 - Seven Segment LED Stop Clock in Assembly and CReeseNo ratings yet

- CE 264 Lab Project: Design of a Digital Circuit for Multiplication and Display of ResultDocument9 pagesCE 264 Lab Project: Design of a Digital Circuit for Multiplication and Display of ResultCalvin SaldanhaNo ratings yet

- Lab 2 - Flip Flops and CountersDocument27 pagesLab 2 - Flip Flops and CountersHoang Dung SonNo ratings yet

- Lab ManualDocument173 pagesLab ManualSahil PatelNo ratings yet

- DEC Manual-2017Document52 pagesDEC Manual-2017Gopalakrishna Murthy C RNo ratings yet

- Digital Logic Design Lab ReportDocument16 pagesDigital Logic Design Lab ReportTrương Quang Tường100% (1)

- Linear Control Systems Lab (EE-3302) : Experiment No: 2Document9 pagesLinear Control Systems Lab (EE-3302) : Experiment No: 2Syed Shehryar Ali NaqviNo ratings yet

- Lab Manual 02Document5 pagesLab Manual 02Muhammad AmirNo ratings yet

- Lab 6Document9 pagesLab 6tuan phanNo ratings yet

- Multiplexers: Digital Logic Design LaboratoryDocument8 pagesMultiplexers: Digital Logic Design LaboratoryTrương Quang TườngNo ratings yet

- Lab1(1)Document15 pagesLab1(1)Nguyễn Hải ThanhNo ratings yet

- DSD Lab ManualDocument49 pagesDSD Lab Manualshailygoyal50% (2)

- BH TBNi Vna TCNJ QKM 972Document12 pagesBH TBNi Vna TCNJ QKM 972Saudamini MahajanNo ratings yet

- Half Adder & Full Adder Experimaent 3: Digital Logic Design Lab ManualDocument4 pagesHalf Adder & Full Adder Experimaent 3: Digital Logic Design Lab ManualRana jamshaid Rana jamshaidNo ratings yet

- 1 2 7 Understanding Digital Design-2Document8 pages1 2 7 Understanding Digital Design-2api-287488010100% (1)

- Experiment 1 - Leds and 7-Segment Display (Part 1) : A. Learning OutcomesDocument10 pagesExperiment 1 - Leds and 7-Segment Display (Part 1) : A. Learning OutcomesBianca ReyNo ratings yet

- Lab 5 Counters and Shift RegistersDocument8 pagesLab 5 Counters and Shift RegistersAhmed Razi UllahNo ratings yet

- DLD Lab 1 - Logic GatesDocument8 pagesDLD Lab 1 - Logic GatesTenkuu No AbarebouNo ratings yet

- Laboratory Design Projects For A Freshman Digital Electronics CourseDocument8 pagesLaboratory Design Projects For A Freshman Digital Electronics CourseRamshaNo ratings yet

- Laboratory Manual: Computer Graphics Laboratory With Mini Project 15CSL68Document88 pagesLaboratory Manual: Computer Graphics Laboratory With Mini Project 15CSL68RanjaniNo ratings yet

- DLD E8 1Document10 pagesDLD E8 1Jahnavi NallapareddyNo ratings yet

- 1 2 7 P Understandingdigitaldesign RNG (1) FinishedDocument8 pages1 2 7 P Understandingdigitaldesign RNG (1) Finishedapi-287488627No ratings yet

- Laboratory Exercise 2: Basic Logic GatesDocument5 pagesLaboratory Exercise 2: Basic Logic GatesSantiago EspitiaNo ratings yet

- Electrical Engineering Department Academic SessionDocument12 pagesElectrical Engineering Department Academic Sessionmuhd aslamNo ratings yet

- Half Subtractor and Full Subtractor Experimaent 4: Lab Manual 3 SemesterDocument5 pagesHalf Subtractor and Full Subtractor Experimaent 4: Lab Manual 3 SemesterRana jamshaid Rana jamshaidNo ratings yet

- Laboratory Exercise 5 PDFDocument5 pagesLaboratory Exercise 5 PDFCristian Felipe Rangel TrianaNo ratings yet

- DLDforFall2017 18Document58 pagesDLDforFall2017 18Ramzan AliNo ratings yet

- Lab Activity #1:: University of The EastDocument7 pagesLab Activity #1:: University of The Eastdawj jdwijNo ratings yet

- Traffic LightDocument19 pagesTraffic LightDianne ParNo ratings yet

- Lab12 Design of A Combinational Circuit (BCD To 7-Segment Decoder) ND Voting Machine DesignDocument7 pagesLab12 Design of A Combinational Circuit (BCD To 7-Segment Decoder) ND Voting Machine DesignAli HassanNo ratings yet

- University of North Carolina at Charlotte Department of Electrical and Computer Engineering Experiment No. 2 - BCD To Seven Segment Display OverviewDocument7 pagesUniversity of North Carolina at Charlotte Department of Electrical and Computer Engineering Experiment No. 2 - BCD To Seven Segment Display Overview9096998222No ratings yet

- Lab8 2-Bit Binary Adder-SubtractorDocument11 pagesLab8 2-Bit Binary Adder-SubtractorAhmed Razi UllahNo ratings yet

- Laboratory Exercise 2Document5 pagesLaboratory Exercise 2BriNyanNo ratings yet

- Lcdxultrasonic Lab Act 060106Document7 pagesLcdxultrasonic Lab Act 060106juanzxc acgNo ratings yet

- FPGA Lab 07Document14 pagesFPGA Lab 07Zain AlamgirNo ratings yet

- It-Dl Instructor Manual 17 18 Mdk1Document85 pagesIt-Dl Instructor Manual 17 18 Mdk1Likhith ReddyNo ratings yet

- Test Digital ICs Quickly with Programmable CircuitDocument46 pagesTest Digital ICs Quickly with Programmable Circuitsajid_mllNo ratings yet

- Analog Integrated Circuits Lab SyllabusDocument3 pagesAnalog Integrated Circuits Lab SyllabusVilayil jestinNo ratings yet

- De - Lab ExperimentsDocument62 pagesDe - Lab ExperimentssaipraneethpNo ratings yet

- Digital ManualDocument38 pagesDigital Manualdivyang_pNo ratings yet

- Screenshot 2022-04-18 at 1.25.40 PMDocument72 pagesScreenshot 2022-04-18 at 1.25.40 PMZxsl FNo ratings yet

- Daffodil International University: Department of Computer Science & EngineeringDocument26 pagesDaffodil International University: Department of Computer Science & Engineeringmdshawonkhan513No ratings yet

- Digital Design I: Laboratory ExperimentsDocument9 pagesDigital Design I: Laboratory ExperimentsDoğa GüvenNo ratings yet

- De CepDocument19 pagesDe CepFrosty2 LeafNo ratings yet

- Design Lab Final YearDocument18 pagesDesign Lab Final YearSourav DebnathNo ratings yet

- ReportDocument84 pagesReportAmit PatilNo ratings yet

- ECE401 Lab 7: Introduction to Logic GatesDocument3 pagesECE401 Lab 7: Introduction to Logic GatesbingNo ratings yet

- Logic DesignDocument65 pagesLogic DesignChaudhary WaseemNo ratings yet

- Task # 5Document2 pagesTask # 5Ejju AbdalraheemNo ratings yet

- 6c7f5ec8 1643863161253Document38 pages6c7f5ec8 1643863161253Akshay GuptaNo ratings yet

- Suggested Outline Question Type: Do You Agree or Disagree ?Document1 pageSuggested Outline Question Type: Do You Agree or Disagree ?Trương Quang TườngNo ratings yet

- Homework: Entropy and the Second LawDocument20 pagesHomework: Entropy and the Second LawTrương Quang TườngNo ratings yet

- Academic Language For Introduction-Literature Review SectionsDocument6 pagesAcademic Language For Introduction-Literature Review SectionsTrương Quang TườngNo ratings yet

- Danh sách cấm thi - G1Document1 pageDanh sách cấm thi - G1Trương Quang TườngNo ratings yet

- Week 12 - Speech Writing TechniquesDocument26 pagesWeek 12 - Speech Writing TechniquesTrương Quang TườngNo ratings yet

- C/C++ Lab 6 IntroductionDocument4 pagesC/C++ Lab 6 IntroductionTrương Quang TườngNo ratings yet

- Final Examination: Subject: Digital Logic Design Laboratory Date: Monday, May 30, 2022. Duration: 75 MinutesDocument4 pagesFinal Examination: Subject: Digital Logic Design Laboratory Date: Monday, May 30, 2022. Duration: 75 MinutesTrương Quang TườngNo ratings yet

- Truong Quang Tuong ITITIU20130 Lab 2 CDocument6 pagesTruong Quang Tuong ITITIU20130 Lab 2 CTrương Quang TườngNo ratings yet

- The Rapid Development of Information Technology Has Touched Every Aspect of Our Daily Life and Influenced Our Consumption Habits and Buying DecisionsDocument6 pagesThe Rapid Development of Information Technology Has Touched Every Aspect of Our Daily Life and Influenced Our Consumption Habits and Buying DecisionsTrương Quang TườngNo ratings yet

- Template For Final Exam ScriptDocument2 pagesTemplate For Final Exam ScriptTrương Quang TườngNo ratings yet

- Your Name: Trương Quang Tư NG Your ID: ITITIU20130: Lab 7 - Introduction To C/C++ ProgrammingDocument7 pagesYour Name: Trương Quang Tư NG Your ID: ITITIU20130: Lab 7 - Introduction To C/C++ ProgrammingTrương Quang TườngNo ratings yet

- Digital Logic Design Laboratory Course Id: It099IuDocument13 pagesDigital Logic Design Laboratory Course Id: It099IuTrương Quang TườngNo ratings yet

- Your Name: Your ID:: Lab 4 - Introduction To C/C++ ProgrammingDocument5 pagesYour Name: Your ID:: Lab 4 - Introduction To C/C++ ProgrammingTrương Quang TườngNo ratings yet

- The Influence of Social Media On Buy Decision-MakiDocument5 pagesThe Influence of Social Media On Buy Decision-MakiTrương Quang TườngNo ratings yet

- Your Name: Lê Nguyễn Bảo Long Your ID: ITITIU20138: Lab 3 - Introduction to C/C++ ProgrammingDocument6 pagesYour Name: Lê Nguyễn Bảo Long Your ID: ITITIU20138: Lab 3 - Introduction to C/C++ ProgrammingTrương Quang TườngNo ratings yet

- Flip Flops and Counters: Digital Logic Design LaboratoryDocument16 pagesFlip Flops and Counters: Digital Logic Design LaboratoryTrương Quang TườngNo ratings yet

- Lesson 5 - Designing SlidesDocument57 pagesLesson 5 - Designing SlidesTrương Quang TườngNo ratings yet

- Multiplexers: Digital Logic Design LaboratoryDocument8 pagesMultiplexers: Digital Logic Design LaboratoryTrương Quang TườngNo ratings yet

- Digital Logic Design Lab ReportDocument16 pagesDigital Logic Design Lab ReportTrương Quang Tường100% (1)

- Lesson 2 - IntroductionDocument21 pagesLesson 2 - IntroductionTrương Quang TườngNo ratings yet

- Your Name: Your ID:: Lab 5 - Introduction To C/C++ ProgrammingDocument3 pagesYour Name: Your ID:: Lab 5 - Introduction To C/C++ ProgrammingTrương Quang TườngNo ratings yet

- Final Examination: SUBJECT: C/C++ Programming in UNIXDocument5 pagesFinal Examination: SUBJECT: C/C++ Programming in UNIXTrương Quang TườngNo ratings yet

- 250+ C Programs For Practice PDFDocument13 pages250+ C Programs For Practice PDFrazi100% (1)

- Simulation of 2.4Ghz Microstrip Patch Antenna Using Ebg StructureDocument5 pagesSimulation of 2.4Ghz Microstrip Patch Antenna Using Ebg StructureSanjeev KumarNo ratings yet

- Control Unit ProgrammingDocument6 pagesControl Unit ProgrammingShafii SigeraNo ratings yet

- Informix 4GL Environment GuideDocument28 pagesInformix 4GL Environment GuideRodolfo J. PeñaNo ratings yet

- 03 Gas TurbineDocument56 pages03 Gas TurbineJessray RepunteNo ratings yet

- Namatreasure Playing Programming Uv PDFDocument129 pagesNamatreasure Playing Programming Uv PDFNikos IoannouNo ratings yet

- Decision Tree To Guide SWIFT Users To Determine Their CSP Architecture TypeDocument35 pagesDecision Tree To Guide SWIFT Users To Determine Their CSP Architecture Typeফয়সাল হোসেন100% (1)

- Jenbacher Type-6 EngineDocument24 pagesJenbacher Type-6 EngineAb Hannan chowdhury100% (1)

- Online EarningDocument3 pagesOnline Earningwordwork373No ratings yet

- NCM 110 Lec Act.1 Prelim VirayDocument4 pagesNCM 110 Lec Act.1 Prelim VirayJezzy VeeNo ratings yet

- ChecklistDocument1 pageChecklistYahir andres Luna lopezNo ratings yet

- SP0510ver4-Earth System Site Injection TestDocument14 pagesSP0510ver4-Earth System Site Injection TestvipinrajNo ratings yet

- Process Simulate On Teamcenter: TecnomatixDocument2 pagesProcess Simulate On Teamcenter: TecnomatixjanardhanaNo ratings yet

- Module 3 Post TestDocument5 pagesModule 3 Post TestCleórbete Santos100% (1)

- Wifi SecurityDocument17 pagesWifi Securityviniskykumar100% (2)

- Smart Retailing and The Challenges of AI Ethics A Systematic Literature Review-2-33Document32 pagesSmart Retailing and The Challenges of AI Ethics A Systematic Literature Review-2-33Edem Kofi BoniNo ratings yet

- Satcon 500 KW Inverter SpecDocument4 pagesSatcon 500 KW Inverter SpecSagar SinghNo ratings yet

- THE DEMOLITION INDUSTRY APPROVED CCDO SMART CARD SCHEMEDocument21 pagesTHE DEMOLITION INDUSTRY APPROVED CCDO SMART CARD SCHEMEDg FernandezNo ratings yet

- CV MonirDocument3 pagesCV MonirMIslamMonirNo ratings yet

- AUTO1.com European car transport statusDocument10 pagesAUTO1.com European car transport statusCholi Cortiñas LeonNo ratings yet

- Installation Guide - R8 V8 V10 ExhaustDocument22 pagesInstallation Guide - R8 V8 V10 ExhaustNishan HunsrajNo ratings yet

- Burn ISO Images Natively in Windows 7Document8 pagesBurn ISO Images Natively in Windows 7Meghana JainNo ratings yet

- D - MNL0D750M Control de Portones ElectricosDocument0 pagesD - MNL0D750M Control de Portones ElectricosbernalgutierrezNo ratings yet

- Unity Conn Password RecoveryDocument3 pagesUnity Conn Password RecoveryciscolifeguardNo ratings yet

- SDX Developer GuideDocument11 pagesSDX Developer GuideS Surya DharmaNo ratings yet

- Use of Source MAC Address Field in SpannDocument6 pagesUse of Source MAC Address Field in SpannPraveen RaiNo ratings yet

- ISA100Document37 pagesISA100Victor Rubilar BobadillaNo ratings yet

- MGT 513 Technology Forecasting and Assessment Fall 2014Document14 pagesMGT 513 Technology Forecasting and Assessment Fall 2014Arun VenkatesanNo ratings yet

- ADMS USer ManualDocument42 pagesADMS USer Manualindra astNo ratings yet

- A Study On The Impact of Artificial Intelligence Techniques in Enhancing Electronic Public Procurement SystemDocument7 pagesA Study On The Impact of Artificial Intelligence Techniques in Enhancing Electronic Public Procurement SystemInternational Journal of Innovative Science and Research TechnologyNo ratings yet

- Electronic Cash Register User ManualDocument134 pagesElectronic Cash Register User ManualRobert MendozaNo ratings yet