Professional Documents

Culture Documents

2 OF 4 2 OF 4 3 OF 4 3 OF 4: Misc Misc

Uploaded by

EgeOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

2 OF 4 2 OF 4 3 OF 4 3 OF 4: Misc Misc

Uploaded by

EgeCopyright:

Available Formats

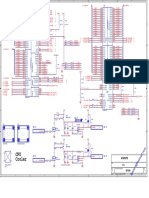

5 4 3 2 1

WWW.AliSaler.Com

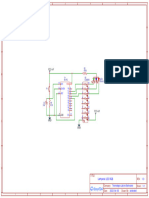

7 H_D#[0..63] VCC_CORE_S0 VCC_CORE_S0

U62B 2 OF 4 U62C

3 OF 4

H_D#0 E22 Y22 H_D#32

H_D#1 D0# D32# H_D#33

F24 D1# D33# AB24 A7 VCC VCC AB20

H_D#2 E26 V24 H_D#34 A9 AB7

H_D#3 D2# D34# H_D#35 VCC VCC

G22 D3# D35# V26 A10 VCC VCC AC7

H_D#4 F23 V23 H_D#36 A12 AC9

D4# D36# VCC VCC

D D

DATA GRP0

DATA GRP2

H_D#5 G25 T22 H_D#37 A13 AC12

H_D#6 D5# D37# H_D#38 VCC VCC

E25 D6# D38# U25 A15 VCC VCC AC13

H_D#7 E23 U23 H_D#39 A17 AC15

H_D#8 D7# D39# H_D#40 VCC VCC

K24 D8# D40# Y25 A18 VCC VCC AC17

H_D#9 G24 W22 H_D#41 A20 AC18

H_D#10 D9# D41# H_D#42 VCC VCC

J24 D10# D42# Y23 B7 VCC VCC AD7

H_D#11 J23 W24 H_D#43 B9 AD9

H_D#12 D11# D43# H_D#44 VCC VCC

H22 D12# D44# W25 B10 VCC VCC AD10

H_D#13 F26 AA23 H_D#45 B12 AD12

H_D#14 D13# D45# H_D#46 VCC VCC

K22 D14# D46# AA24 B14 VCC VCC AD14

H_D#15 H23 AB25 H_D#47 B15 AD15

H_DSTBN#0 D15# D47# H_DSTBN#2 VCC VCC

7 H_DSTBN#0 J26 DSTBN0# DSTBN2# Y26 H_DSTBN#2 7 B17 VCC VCC AD17

H_DSTBP#0 H26 AA26 H_DSTBP#2 B18 AD18

7 H_DSTBP#0 DSTBP0# DSTBP2# H_DSTBP#2 7 VCC VCC

H_DINV#0 H25 U22 H_DINV#2 B20 AE9

7 H_DINV#0 DINV0# DINV2# H_DINV#2 7 VCC VCC

C9 VCC VCC AE10

C10 VCC VCC AE12

H_D#16 N22 AE24 H_D#48 C12 AE13

H_D#17 D16# D48# H_D#49 VCC VCC

K25 D17# D49# AD24 C13 VCC VCC AE15

H_D#18 P26 AA21 H_D#50 C15 AE17

H_D#19 D18# D50# H_D#51 VCC VCC

R23 D19# D51# AB22 C17 VCC VCC AE18

H_D#20 L23 AB21 H_D#52 C18 AE20

H_D#21 D20# D52# H_D#53 VCC VCC

M24 D21# D53# AC26 D9 VCC VCC AF9

DATA GRP1

DATA GRP3

H_D#22 L22 AD20 H_D#54 D10 AF10

H_D#23 D22# D54# H_D#55 VCC VCC

M23 D23# D55# AE22 D12 VCC VCC AF12

H_D#24 P25 AF23 H_D#56 D14 AF14

H_D#25 D24# D56# H_D#57 VCC VCC

P23 D25# D57# AC25 D15 VCC VCC AF15

H_D#26 P22 AE21 H_D#58 D17 AF17

H_D#27 D26# D58# H_D#59 VCC VCC

T24 D27# D59# AD21 D18 VCC VCC AF18

H_D#28 R24 AC22 H_D#60 E7 AF20 1D05V_S0

D28# D60# VCC VCC

C H_D#29

H_D#30

L25

T25

D29# D61# AD23

AF22

H_D#61

H_D#62

E9

E10

VCC

G21 R155 1 2

C

H_D#31 D30# D62# H_D#63 VCC VCCP R146 1

N25 D31# D63# AC23 E12 VCC VCCP V6 2 0R2J-2-GP

H_DSTBN#1 L26 AE25 H_DSTBN#3 E13 J6 0R2J-2-GP TC7

7 H_DSTBN#1 DSTBN1# DSTBN3# H_DSTBN#3 7 VCC VCCP

H_DSTBP#1 M26 AF24 H_DSTBP#3 E15 K6

7 H_DSTBP#1 DSTBP1# DSTBP3# H_DSTBP#3 7 VCC VCCP

SE330U2VDM-6-GP

H_DINV#1 N24 AC20 H_DINV#3 E17 M6

7 H_DINV#1 DINV1# DINV3# H_DINV#3 7 VCC VCCP

E18 VCC VCCP J21

1

V_CPU_GTLREF AD26 R26 COMP0 1 2 E20 K21

TPAD28 TP19 TEST1 GTLREF COMP0 COMP1 R171 VCC VCCP

C23 TEST1 MISC COMP1 U26 1 2 27D4R2F-L1-GP F7 VCC VCCP M21

SCD1U16V2KX-3GP TPAD28 TP22 TEST2 D25 AA1 COMP2 R172 1 2 54D9R2F-L1-GP F9 N21 DY

2

TPAD28 TP20 TEST3 TEST2 COMP2 COMP3 R132 VCC VCCP

C24 TEST3 COMP3 Y1 1 2 27D4R2F-L1-GP F10 VCC VCCP N6

1 2 C296 TEST4 AF26 TEST4

R131 54D9R2F-L1-GP F12 VCC VCCP R21

TPAD28 TP3 TEST5 AF1 E5 H_DPRSTP# F14 R6

TEST5 DPRSTP# H_DPRSTP# 7,19 VCC VCCP

TPAD28 TP21 TEST6 A26 B5 H_DPSLP# F15 T21

DY TEST6 DPSLP#

D24 H_DPWR#

H_DPSLP# 19

F17

VCC VCCP

T6

DPWR# H_DPWR# 7 VCC VCCP

CPU_BSEL0 B22 D6 H_PWRGOOD F18 V21

3 CPU_BSEL0 BSEL0 PWRGOOD H_PWRGOOD 19 VCC VCCP 1D5V_S0

CPU_BSEL1 B23 D7 H_CPUSLP# F20 W21 layout note:

3 CPU_BSEL1 BSEL1 SLP# H_CPUSLP# 7 VCC VCCP

CPU_BSEL2 C21 AE6 PSI# AA7

3 CPU_BSEL2 BSEL2 PSI# PSI# 35

AA9

VCC

B26 C298 place C3 near

VCC VCCA

R145 AA10 VCC VCCA C26 PIN B26

1

SCD01U16V2KX-3GP

AA12 VCC CPU_VID[0..6] 35

BGA479-SKT6-GPU3 1 2 AA13 AD6 CPU_VID0 C303

H_PWRGOOD_R 4 VCC VID0 CPU_VID1 SC10U10V5ZY-1GP

AA15 AF5

2

VCC VID1 CPU_VID2

PLACE C173 close to the TEST4 PIN, 1KR2J-1-GP AA17 VCC VID2 AE5

AA18 AF4 CPU_VID3

make sure TEST3,TEST4,TEST5 trace AA20

VCC VID3

AE3 CPU_VID4

VCC VID4 CPU_VID5

routing is reference to GND and AB9 VCC VID5 AF3

AC10 AE2 CPU_VID6

away other noisy signals AB10

VCC VID6

VCC

B AB12 VCC Length match within B

Resistor Placed AB14 AF7 VCC_SENSE

AB15

VCC VCCSENSE VCC_SENSE 35 25 mils . The trace

within 0.5" of CPU AB17

VCC

width/space/other is

VCC VSS_SENSE

pin. Trace should AB18 VCC VSSSENSE AE7 VSS_SENSE 35 20/7/25 .

CPU_BSEL CPU_BSEL2 CPU_BSEL1 CPU_BSEL0 be at least 25 mils

away from any other

BGA479-SKT6-GPU3 VCC_SENSE 1 2 VCC_CORE_S0

166 0 1 1 toggling signal . R143 100R2F-L1-GP-U

COMP[0,2] trace

VSS_SENSE 1 2

width is 18 mils. R142 100R2F-L1-GP-U

200 0 1 0

COMP[1,3] trace

width is 4 mils .

Close to CPU pin

within 500mils

1D05V_S0

2

Close to CPU

R422

pin AD26 1KR2F-3-GP

<Core Design>

Z0=55 ohm

A A

SCD01U16V2KX-3GP

with in

1 1

V_CPU_GTLREF C602

500mils . Wistron Corporation

1

R423 21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

2KR2F-3-GP

2

Title

2

Meron(2/3)-AGTL+/PWR

Size Document Number Rev

WWW.AliSaler.Com

A3

Pamirs-Discrete SC

Date: Tuesday, December 19, 2006 Sheet 5 of 47

You might also like

- HP Probook 450 g3 Quanta x63 Da0x63mb6h1 R1aDocument67 pagesHP Probook 450 g3 Quanta x63 Da0x63mb6h1 R1aNeven PiscutiNo ratings yet

- HonorDishonorProcess - Victoria Joy-1 PDFDocument126 pagesHonorDishonorProcess - Victoria Joy-1 PDFarjay1266100% (3)

- Surge arrester protects electrical equipmentDocument25 pagesSurge arrester protects electrical equipmentSyed Ahsan Ali Sherazi100% (3)

- 1-2 COGS Vs SALESDocument3 pages1-2 COGS Vs SALESRenato GilbonioNo ratings yet

- Dev OpsDocument28 pagesDev Opsdeb galangNo ratings yet

- Finding The Answers To The Research Questions (Qualitative) : Quarter 4 - Module 5Document39 pagesFinding The Answers To The Research Questions (Qualitative) : Quarter 4 - Module 5Jernel Raymundo80% (5)

- G7-UNIT - I. (Module - 1 (Week 1 - 3 (Microscopy & Levels of Org.)Document8 pagesG7-UNIT - I. (Module - 1 (Week 1 - 3 (Microscopy & Levels of Org.)Margie Gabo Janoras - DaitolNo ratings yet

- SchematicDocument1 pageSchematicpranddNo ratings yet

- Asus Eee PC 900 - Rev 1.2Document21 pagesAsus Eee PC 900 - Rev 1.2dinnhowNo ratings yet

- 344 Mach Chuyen Doi Rs232 To Rs485 Cho PC, Board (Nguyen Gia Minh Thao)Document1 page344 Mach Chuyen Doi Rs232 To Rs485 Cho PC, Board (Nguyen Gia Minh Thao)Quang Linh Lê100% (1)

- Power supply and microcontroller circuit diagramDocument1 pagePower supply and microcontroller circuit diagramsagar21pNo ratings yet

- PIC Led SwitchDocument1 pagePIC Led Switchlayeabdoulaye344No ratings yet

- ACKU040 SOM SchematicDocument22 pagesACKU040 SOM SchematicSalim HajjiNo ratings yet

- LAUNCH& LED BOARD SB 0609Document1 pageLAUNCH& LED BOARD SB 0609maris.grisulisNo ratings yet

- USB Programmer SchematicDocument1 pageUSB Programmer Schematicnguyen thuan100% (1)

- XT2133-x - (Lisbon) - MB - Schematics - L3 - Repair Central Do TécnicoDocument47 pagesXT2133-x - (Lisbon) - MB - Schematics - L3 - Repair Central Do Técnicoedward blancoNo ratings yet

- Symbol 2Document1 pageSymbol 2fredtranNo ratings yet

- 3V3Document1 page3V3ERNANIPARNOWNo ratings yet

- Starlord Sensor - Schematic - A00 - 20160226Document2 pagesStarlord Sensor - Schematic - A00 - 20160226Eliu MaldonadoNo ratings yet

- Schematic - RC Car Receiver Circuit - 2024-01-09Document1 pageSchematic - RC Car Receiver Circuit - 2024-01-09Priyanshu SilNo ratings yet

- Up2 Motor Fan SensDocument1 pageUp2 Motor Fan SensnoctuaryNo ratings yet

- Ac7050 - SDM - Xc7s50-1fgga484iDocument10 pagesAc7050 - SDM - Xc7s50-1fgga484imahimithran16No ratings yet

- Tatmainnah Ainun Haq - MH 17.054: D8 D9 D10 D11 D12 D13 VCC Aref GND A0 A1 A2 A3 A4 A5Document1 pageTatmainnah Ainun Haq - MH 17.054: D8 D9 D10 D11 D12 D13 VCC Aref GND A0 A1 A2 A3 A4 A5tatmainnahainunhaqNo ratings yet

- Hf-Lpt200-Evk V1.0-SCHDocument1 pageHf-Lpt200-Evk V1.0-SCHLarry LawrenceNo ratings yet

- Kendryte Test Board V0 2Document13 pagesKendryte Test Board V0 2Abel DavidNo ratings yet

- stm32 Gem3m SCHDocument3 pagesstm32 Gem3m SCHQuan Tran QuangNo ratings yet

- Schematic - DIY Three Phase Rectifier Circuit - Sheet - 1 - 20190926091525 PDFDocument1 pageSchematic - DIY Three Phase Rectifier Circuit - Sheet - 1 - 20190926091525 PDFcriman45No ratings yet

- Schematic - DIY Three Phase Rectifier Circuit - Sheet - 1 - 20190926091525Document1 pageSchematic - DIY Three Phase Rectifier Circuit - Sheet - 1 - 20190926091525criman45No ratings yet

- Schematic DIY Three Phase Rectifier Circuit Sheet 1 20190926091525Document1 pageSchematic DIY Three Phase Rectifier Circuit Sheet 1 20190926091525Manolo PerezNo ratings yet

- Athlon64 Power Good & Enables Circuit System Power Reference Source VDDA - 25 PowerDocument2 pagesAthlon64 Power Good & Enables Circuit System Power Reference Source VDDA - 25 PowerGeovanny SanJuanNo ratings yet

- Grand Escape - Weathering With You Tenki No Ko OstDocument6 pagesGrand Escape - Weathering With You Tenki No Ko Ost이주영No ratings yet

- Weathering with You soundtrackDocument6 pagesWeathering with You soundtrackArianne AguadoNo ratings yet

- Grand Escape: Weathering With You (Tenki No Ko) OST Arranged by Steve HansenDocument6 pagesGrand Escape: Weathering With You (Tenki No Ko) OST Arranged by Steve HansenJustin OliverNo ratings yet

- ESP32-S2-Kaluga-1 V1 3 SCH 20200526ADocument4 pagesESP32-S2-Kaluga-1 V1 3 SCH 20200526A黄健No ratings yet

- TUBEPRE Power Supply SchematicDocument5 pagesTUBEPRE Power Supply SchematicJJ MMNo ratings yet

- LCD connection to 8051 microcontrollerDocument1 pageLCD connection to 8051 microcontrollerGarvitt BhatnagarNo ratings yet

- MACH NAP ACQUY 24VDocument1 pageMACH NAP ACQUY 24VtayantrungquochpNo ratings yet

- Pipistrello v2 Schematic PDFDocument5 pagesPipistrello v2 Schematic PDFjackabrahamNo ratings yet

- Seeed Studio EdgeBox-ESP-100 Schematic PDFDocument15 pagesSeeed Studio EdgeBox-ESP-100 Schematic PDFhidden MaskNo ratings yet

- CY4502 EZ PD CCG2 Development Schematic PDFDocument3 pagesCY4502 EZ PD CCG2 Development Schematic PDFG.MarieNo ratings yet

- SCH Image SensorDocument1 pageSCH Image SensorAnal E SNo ratings yet

- LFTXDocument1 pageLFTXxieharNo ratings yet

- Training Esp32 2022 2023Document1 pageTraining Esp32 2022 2023Fernando Alexander GTNo ratings yet

- Uart LDO 3.3VDocument2 pagesUart LDO 3.3VMas SamNo ratings yet

- Max 232Document1 pageMax 232MNorace GosaiNo ratings yet

- Acer Aspire 4810 5810 - WISTRON JM41 - MINI BOARDS - REV - 1 IIDocument7 pagesAcer Aspire 4810 5810 - WISTRON JM41 - MINI BOARDS - REV - 1 IISilvio RodriguesNo ratings yet

- Khoi Cong Suat: Khoi Bam Xung Cho Dong CoDocument1 pageKhoi Cong Suat: Khoi Bam Xung Cho Dong CoDuong NghiaNo ratings yet

- FDR AnalogDocument13 pagesFDR AnalogSree VBroNo ratings yet

- Schematic - 4017 Kademeli Led - 2021-12-29Document1 pageSchematic - 4017 Kademeli Led - 2021-12-29Luis Eduardo RibeiroNo ratings yet

- 3 - MemoryDocument1 page3 - MemoryHungNo ratings yet

- TM1650Document1 pageTM1650mingrenttyyNo ratings yet

- Esquematico Icaro LPTDocument1 pageEsquematico Icaro LPTElías Damián Martínez TerénNo ratings yet

- Auto Incredible MultiplexorDocument3 pagesAuto Incredible MultiplexorJuan AguilarNo ratings yet

- Foreword: ADDITIONAL COMBINED SCIENCE ................................................................................. 1Document2 pagesForeword: ADDITIONAL COMBINED SCIENCE ................................................................................. 1rodel.verzosaNo ratings yet

- Title:: File: Arduino - LDR - KICAD - SCH SheetDocument1 pageTitle:: File: Arduino - LDR - KICAD - SCH SheetakNo ratings yet

- Módulo Conversor A/DDocument1 pageMódulo Conversor A/DcharlyNo ratings yet

- DNP IOT Irrigation Wemos - 2022-11-28Document1 pageDNP IOT Irrigation Wemos - 2022-11-28Aditya ConsultancyNo ratings yet

- MachDocument1 pageMachhamsterkhinNo ratings yet

- Vestel 17MB63DDocument7 pagesVestel 17MB63DLuis RodriguezNo ratings yet

- Schematic - Schemat Rfid - 2021-04-25 - 20-26-26Document1 pageSchematic - Schemat Rfid - 2021-04-25 - 20-26-26totylkojaNo ratings yet

- Tang Nano 9k 3672 SchematicDocument5 pagesTang Nano 9k 3672 SchematicJohnNo ratings yet

- Korad Ka3005p Interface-BoardDocument1 pageKorad Ka3005p Interface-Boardcesar14diaz100% (1)

- SIM7000XDocument5 pagesSIM7000XEDI WIYONO100% (1)

- R evN o R e v i s io n n o t eDocument1 pageR evN o R e v i s io n n o t eAbdelfatah MohamedNo ratings yet

- Schematic - Lampara RGB - 2022-05-02Document1 pageSchematic - Lampara RGB - 2022-05-02Pablo GarciaNo ratings yet

- Mercury Poisoning Symptoms and TreatmentsDocument1 pageMercury Poisoning Symptoms and TreatmentsRakheeb BashaNo ratings yet

- Classification of AnimalsDocument6 pagesClassification of Animalsapi-282695651No ratings yet

- CAFA Open House HighlightsDocument1 pageCAFA Open House HighlightsDaniel LaiNo ratings yet

- CB4 BBC Interviews EXTRA UnitDocument1 pageCB4 BBC Interviews EXTRA UnitCristianNo ratings yet

- Desk PiDocument21 pagesDesk PiThan LwinNo ratings yet

- 02 1 Cohen Sutherland PDFDocument3 pages02 1 Cohen Sutherland PDFSarra AnitaNo ratings yet

- Orion C.M. HVAC Case Study-07.25.23Document25 pagesOrion C.M. HVAC Case Study-07.25.23ledmabaya23No ratings yet

- Internship Report Zannatul Ferdousi Alam YameemDocument51 pagesInternship Report Zannatul Ferdousi Alam YameemZannatul Ferdousi Alam YameemNo ratings yet

- M.Sc. Agriculture (Agronomy)Document23 pagesM.Sc. Agriculture (Agronomy)Abhishek MauryaNo ratings yet

- SolidWorks2018 PDFDocument1 pageSolidWorks2018 PDFAwan D'almightyNo ratings yet

- HEC-HMS Tutorials and Guides-V3-20210529 - 140315Document756 pagesHEC-HMS Tutorials and Guides-V3-20210529 - 140315Ervin PumaNo ratings yet

- MOW Procurement Management Plan - TemplateDocument7 pagesMOW Procurement Management Plan - TemplateDeepak RajanNo ratings yet

- INSYS - EBW Serie EbookDocument4 pagesINSYS - EBW Serie EbookJorge_Andril_5370No ratings yet

- Natural GasDocument86 pagesNatural GasNikhil TiwariNo ratings yet

- JKSTREGIESDocument59 pagesJKSTREGIESmss_singh_sikarwarNo ratings yet

- Senior High School Tracks: Free Powerpoint Templates Free Powerpoint TemplatesDocument11 pagesSenior High School Tracks: Free Powerpoint Templates Free Powerpoint TemplatesGeraldineNo ratings yet

- B.Ed Syllabus NEW 2015-16 PDFDocument170 pagesB.Ed Syllabus NEW 2015-16 PDFVikas KuthadiNo ratings yet

- Heather Bianco 2016 Resume Revised PDFDocument3 pagesHeather Bianco 2016 Resume Revised PDFapi-316610725No ratings yet

- Research on Comparisons between Sabah and Diesel CyclesDocument8 pagesResearch on Comparisons between Sabah and Diesel CyclesjorgeNo ratings yet

- Theory and Practice of Crown and Bridge Prosthodontics 4nbsped CompressDocument1,076 pagesTheory and Practice of Crown and Bridge Prosthodontics 4nbsped CompressYuganya SriNo ratings yet

- Concurrent AuditorDocument67 pagesConcurrent AuditorAjoydeep DasNo ratings yet

- Material Safety Data Sheet Surfacecool© Roof CoatingDocument3 pagesMaterial Safety Data Sheet Surfacecool© Roof CoatingPremfeb27No ratings yet

- Compare The Political System of Kazakhstan, USA, UK PresentationDocument19 pagesCompare The Political System of Kazakhstan, USA, UK PresentationAiganym OmiraliNo ratings yet

- Textbook of Heat Transfer Sukhatme S PDocument122 pagesTextbook of Heat Transfer Sukhatme S PSamer HouzaynNo ratings yet