Professional Documents

Culture Documents

Datasheet - Arquitectura y Organización de Memoria

Datasheet - Arquitectura y Organización de Memoria

Uploaded by

Alan EllembergOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Datasheet - Arquitectura y Organización de Memoria

Datasheet - Arquitectura y Organización de Memoria

Uploaded by

Alan EllembergCopyright:

Available Formats

PIC16F627A/628A/648A

FIGURE 3-1: BLOCK DIAGRAM

13 Data Bus 8

Program Counter

Flash

Program

Memory RAM

8-Level Stack

File

(13-bit) Registers

Program 14

Bus RAM Addr (1) 9 PORTA

Addr MUX RA0/AN0

Instruction Reg

RA1/AN1

Direct Addr 7 Indirect RA2/AN2/VREF

8 Addr

RA3/AN3/CMP1

FSR Reg RA4/T0CK1/CMP2

RA5/MCLR/VPP

Status Reg RA6/OSC2/CLKOUT

8 RA7/OSC1/CLKIN

3 MUX PORTB

Power-up

Timer RB0/INT

RB1/RX/DT

Instruction Oscillator

Decode & Start-up Timer RB2/TX/CK

ALU RB3/CCP1

Control

Power-on RB4/PGM

Reset 8

RB5

Timing Watchdog RB6/T1OSO/T1CKI/PGC

Generation Timer W Reg

RB7/T1OSI/PGD

OSC1/CLKIN Brown-out

OSC2/CLKOUT Reset

Low-Voltage

Programming

MCLR VDD, VSS

Comparator Timer0 Timer1 Timer2

VREF CCP1 USART Data EEPROM

Note 1: Higher order bits are from the Status register.

DS40044F-page 10 © 2007 Microchip Technology Inc.

PIC16F627A/628A/648A

4.0 MEMORY ORGANIZATION 4.2 Data Memory Organization

The data memory (Figure 4-2 and Figure 4-3) is

4.1 Program Memory Organization partitioned into four banks, which contain the General

The PIC16F627A/628A/648A has a 13-bit program Purpose Registers (GPRs) and the Special Function

counter capable of addressing an 8K x 14 program Registers (SFRs). The SFRs are located in the first 32

memory space. Only the first 1K x 14 (0000h-03FFh) locations of each bank. There are General Purpose

for the PIC16F627A, 2K x 14 (0000h-07FFh) for the Registers implemented as static RAM in each bank.

PIC16F628A and 4K x 14 (0000h-0FFFh) for the Table 4-1 lists the General Purpose Register available

PIC16F648A are physically implemented. Accessing a in each of the four banks.

location above these boundaries will cause a wrap-

around within the first 1K x 14 space (PIC16F627A), TABLE 4-1: GENERAL PURPOSE STATIC

2K x 14 space (PIC16F628A) or 4K x 14 space RAM REGISTERS

(PIC16F648A). The Reset vector is at 0000h and the PIC16F627A/628A PIC16F648A

interrupt vector is at 0004h (Figure 4-1).

Bank0 20-7Fh 20-7Fh

FIGURE 4-1: PROGRAM MEMORY MAP Bank1 A0h-FF A0h-FF

AND STACK Bank2 120h-14Fh, 170h-17Fh 120h-17Fh

PC<12:0> Bank3 1F0h-1FFh 1F0h-1FFh

CALL, RETURN 13 Addresses F0h-FFh, 170h-17Fh and 1F0h-1FFh are

RETFIE, RETLW implemented as common RAM and mapped back to

addresses 70h-7Fh.

Stack Level 1

Stack Level 2 Table 4-2 lists how to access the four banks of registers

via the Status register bits RP1 and RP0.

Stack Level 8 TABLE 4-2: ACCESS TO BANKS OF

REGISTERS

Reset Vector 000h Bank RP1 RP0

0 0 0

1 0 1

Interrupt Vector 0004 2 1 0

On-chip Program 0005

3 1 1

Memory

PIC16F627A, 4.2.1 GENERAL PURPOSE REGISTER

PIC16F628A and FILE

PIC16F648A

The register file is organized as 224 x 8 in the

03FFh

PIC16F627A/628A and 256 x 8 in the PIC16F648A.

Each is accessed either directly or indirectly through

On-chip Program

Memory the File Select Register (FSR), See Section 4.4

“Indirect Addressing, INDF and FSR Registers”.

PIC16F628A and

PIC16F648A

07FFh

On-chip Program

Memory

PIC16F648A only

0FFFh

1FFFh

© 2007 Microchip Technology Inc. DS40044F-page 15

PIC16F627A/628A/648A

FIGURE 4-2: DATA MEMORY MAP OF THE PIC16F627A AND PIC16F628A

File

Address

Indirect addr.(1) 00h Indirect addr.(1) 80h Indirect addr.(1) 100h Indirect addr.(1) 180h

TMR0 01h OPTION 81h TMR0 101h OPTION 181h

PCL 02h PCL 82h PCL 102h PCL 182h

STATUS 03h STATUS 83h STATUS 103h STATUS 183h

FSR 04h FSR 84h FSR 104h FSR 184h

PORTA 05h TRISA 85h 105h 185h

PORTB 06h TRISB 86h PORTB 106h TRISB 186h

07h 87h 107h 187h

08h 88h 108h 188h

09h 89h 109h 189h

PCLATH 0Ah PCLATH 8Ah PCLATH 10Ah PCLATH 18Ah

INTCON 0Bh INTCON 8Bh INTCON 10Bh INTCON 18Bh

PIR1 0Ch PIE1 8Ch 10Ch 18Ch

0Dh 8Dh 10Dh 18Dh

TMR1L 0Eh PCON 8Eh 10Eh 18Eh

TMR1H 0Fh 8Fh 10Fh 18Fh

T1CON 10h 90h

TMR2 11h 91h

T2CON 12h PR2 92h

13h 93h

14h 94h

CCPR1L 15h 95h

CCPR1H 16h 96h

CCP1CON 17h 97h

RCSTA 18h TXSTA 98h

TXREG 19h SPBRG 99h

RCREG 1Ah EEDATA 9Ah

1Bh EEADR 9Bh

1Ch EECON1 9Ch

1Dh EECON2(1) 9Dh

1Eh 9Eh

CMCON 1Fh VRCON 9Fh 11Fh

20h General 120h

A0h Purpose

General General Register

Purpose Purpose 48 Bytes 14Fh

Register Register

150h

80 Bytes

80 Bytes

6Fh EFh 16Fh 1EFh

70h F0h 170h 1F0h

accesses accesses accesses

16 Bytes

70h-7Fh 70h-7Fh 70h-7Fh

7Fh FFh 17Fh 1FFh

Bank 0 Bank 1 Bank 2 Bank 3

Unimplemented data memory locations, read as ‘0’.

Note 1: Not a physical register.

DS40044F-page 16 © 2007 Microchip Technology Inc.

PIC16F627A/628A/648A

FIGURE 4-3: DATA MEMORY MAP OF THE PIC16F648A

File

Address

Indirect addr.(1) 00h Indirect addr.(1) 80h Indirect addr.(1) 100h Indirect addr.(1) 180h

TMR0 01h OPTION 81h TMR0 101h OPTION 181h

PCL 02h PCL 82h PCL 102h PCL 182h

STATUS 03h STATUS 83h STATUS 103h STATUS 183h

FSR 04h FSR 84h FSR 104h FSR 184h

PORTA 05h TRISA 85h 105h 185h

PORTB 06h TRISB 86h PORTB 106h TRISB 186h

07h 87h 107h 187h

08h 88h 108h 188h

09h 89h 109h 189h

PCLATH 0Ah PCLATH 8Ah PCLATH 10Ah PCLATH 18Ah

INTCON 0Bh INTCON 8Bh INTCON 10Bh INTCON 18Bh

PIR1 0Ch PIE1 8Ch 10Ch 18Ch

0Dh 8Dh 10Dh 18Dh

TMR1L 0Eh PCON 8Eh 10Eh 18Eh

TMR1H 0Fh 8Fh 10Fh 18Fh

T1CON 10h 90h

TMR2 11h 91h

T2CON 12h PR2 92h

13h 93h

14h 94h

CCPR1L 15h 95h

CCPR1H 16h 96h

CCP1CON 17h 97h

RCSTA 18h TXSTA 98h

TXREG 19h SPBRG 99h

RCREG 1Ah EEDATA 9Ah

1Bh EEADR 9Bh

1Ch EECON1 9Ch

1Dh EECON2(1) 9Dh

1Eh 9Eh

CMCON 1Fh VRCON 9Fh 11Fh

20h 120h

A0h

General General General

Purpose Purpose Purpose

Register Register Register

80 Bytes 80 Bytes

80 Bytes

6Fh EFh 16Fh 1EFh

70h F0h 170h 1F0h

accesses accesses accesses

16 Bytes

70h-7Fh 70h-7Fh 70h-7Fh

7Fh FFh 17Fh 1FFh

Bank 0 Bank 1 Bank 2 Bank 3

Unimplemented data memory locations, read as ‘0’.

Note 1: Not a physical register.

© 2007 Microchip Technology Inc. DS40044F-page 17

PIC16F627A/628A/648A

4.2.2.1 Status Register For example, CLRF STATUS will clear the upper-three

bits and set the Z bit. This leaves the Status register

The Status register, shown in Register 4-1, contains the

as “000uu1uu” (where u = unchanged).

arithmetic status of the ALU; the Reset status and the

bank select bits for data memory (SRAM). It is recommended, therefore, that only BCF, BSF,

SWAPF and MOVWF instructions are used to alter the

The Status register can be the destination for any

Status register because these instructions do not affect

instruction, like any other register. If the Status register

any Status bit. For other instructions, not affecting any

is the destination for an instruction that affects the Z,

Status bits, see the “Instruction Set Summary”.

DC or C bits, then the write to these three bits is

disabled. These bits are set or cleared according to the Note: The C and DC bits operate as a Borrow

device logic. Furthermore, the TO and PD bits are non- and Digit Borrow out bit, respectively, in

writable. Therefore, the result of an instruction with the subtraction. See the SUBLW and SUBWF

Status register as destination may be different than instructions for examples.

intended.

REGISTER 4-1: STATUS – STATUS REGISTER (ADDRESS: 03h, 83h, 103h, 183h)

R/W-0 R/W-0 R/W-0 R-1 R-1 R/W-x R/W-x R/W-x

IRP RP1 RP0 TO PD Z DC C

bit 7 bit 0

bit 7 IRP: Register Bank Select bit (used for indirect addressing)

1 = Bank 2, 3 (100h-1FFh)

0 = Bank 0, 1 (00h-FFh)

bit 6-5 RP<1:0>: Register Bank Select bits (used for direct addressing)

00 = Bank 0 (00h-7Fh)

01 = Bank 1 (80h-FFh)

10 = Bank 2 (100h-17Fh)

11 = Bank 3 (180h-1FFh)

bit 4 TO: Time Out bit

1 = After power-up, CLRWDT instruction or SLEEP instruction

0 = A WDT time out occurred

bit 3 PD: Power-down bit

1 = After power-up or by the CLRWDT instruction

0 = By execution of the SLEEP instruction

bit 2 Z: Zero bit

1 = The result of an arithmetic or logic operation is zero

0 = The result of an arithmetic or logic operation is not zero

bit 1 DC: Digit Carry/Borrow bit (ADDWF, ADDLW,SUBLW,SUBWF instructions) (for Borrow the polarity

is reversed)

1 = A carry-out from the 4th low order bit of the result occurred

0 = No carry-out from the 4th low order bit of the result

bit 0 C: Carry/Borrow bit (ADDWF, ADDLW,SUBLW,SUBWF instructions)

1 = A carry-out from the Most Significant bit of the result occurred

0 = No carry-out from the Most Significant bit of the result occurred

Note: For Borrow, the polarity is reversed. A subtraction is executed by adding the two’s

complement of the second operand. For rotate (RRF, RLF) instructions, this bit is

loaded with either the high or low order bit of the source register.

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

-n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

DS40044F-page 22 © 2007 Microchip Technology Inc.

PIC16F627A/628A/648A

4.2.2.2 OPTION Register

Note: To achieve a 1:1 prescaler assignment for

The Option register is a readable and writable register,

TMR0, assign the prescaler to the WDT

which contains various control bits to configure the

(PSA = 1). See Section 6.3.1 “Switching

TMR0/WDT prescaler, the external RB0/INT interrupt,

Prescaler Assignment”.

TMR0 and the weak pull-ups on PORTB.

REGISTER 4-2: OPTION_REG – OPTION REGISTER (ADDRESS: 81h, 181h)

R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1

RBPU INTEDG T0CS T0SE PSA PS2 PS1 PS0

bit 7 bit 0

bit 7 RBPU: PORTB Pull-up Enable bit

1 = PORTB pull-ups are disabled

0 = PORTB pull-ups are enabled by individual port latch values

bit 6 INTEDG: Interrupt Edge Select bit

1 = Interrupt on rising edge of RB0/INT pin

0 = Interrupt on falling edge of RB0/INT pin

bit 5 T0CS: TMR0 Clock Source Select bit

1 = Transition on RA4/T0CKI/CMP2 pin

0 = Internal instruction cycle clock (CLKOUT)

bit 4 T0SE: TMR0 Source Edge Select bit

1 = Increment on high-to-low transition on RA4/T0CKI/CMP2 pin

0 = Increment on low-to-high transition on RA4/T0CKI/CMP2 pin

bit 3 PSA: Prescaler Assignment bit

1 = Prescaler is assigned to the WDT

0 = Prescaler is assigned to the Timer0 module

bit 2-0 PS<2:0>: Prescaler Rate Select bits

Bit Value TMR0 Rate WDT Rate

000 1:2 1:1

001 1:4 1:2

010 1:8 1:4

011 1 : 16 1:8

100 1 : 32 1 : 16

101 1 : 64 1 : 32

110 1 : 128 1 : 64

111 1 : 256 1 : 128

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

-n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

© 2007 Microchip Technology Inc. DS40044F-page 23

PIC16F627A/628A/648A

4.2.2.3 INTCON Register

Note: Interrupt flag bits get set when an interrupt

The INTCON register is a readable and writable

condition occurs regardless of the state of

register, which contains the various enable and flag bits

its corresponding enable bit or the global

for all interrupt sources except the comparator module.

enable bit, GIE (INTCON<7>).

See Section 4.2.2.4 “PIE1 Register” and

Section 4.2.2.5 “PIR1 Register” for a description of

the comparator enable and flag bits.

REGISTER 4-3: INTCON – INTERRUPT CONTROL REGISTER (ADDRESS: 0Bh, 8Bh, 10Bh, 18Bh)

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-x

GIE PEIE T0IE INTE RBIE T0IF INTF RBIF

bit 7 bit 0

bit 7 GIE: Global Interrupt Enable bit

1 = Enables all un-masked interrupts

0 = Disables all interrupts

bit 6 PEIE: Peripheral Interrupt Enable bit

1 = Enables all un-masked peripheral interrupts

0 = Disables all peripheral interrupts

bit 5 T0IE: TMR0 Overflow Interrupt Enable bit

1 = Enables the TMR0 interrupt

0 = Disables the TMR0 interrupt

bit 4 INTE: RB0/INT External Interrupt Enable bit

1 = Enables the RB0/INT external interrupt

0 = Disables the RB0/INT external interrupt

bit 3 RBIE: RB Port Change Interrupt Enable bit

1 = Enables the RB port change interrupt

0 = Disables the RB port change interrupt

bit 2 T0IF: TMR0 Overflow Interrupt Flag bit

1 = TMR0 register has overflowed (must be cleared in software)

0 = TMR0 register did not overflow

bit 1 INTF: RB0/INT External Interrupt Flag bit

1 = The RB0/INT external interrupt occurred (must be cleared in software)

0 = The RB0/INT external interrupt did not occur

bit 0 RBIF: RB Port Change Interrupt Flag bit

1 = When at least one of the RB<7:4> pins changes state (must be cleared in software)

0 = None of the RB<7:4> pins have changed state

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

-n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

DS40044F-page 24 © 2007 Microchip Technology Inc.

PIC16F627A/628A/648A

4.3 PCL and PCLATH The stack operates as a circular buffer. This means that

after the stack has been PUSHed eight times, the ninth

The Program Counter (PC) is 13-bits wide. The low PUSH overwrites the value that was stored from the

byte comes from the PCL register, which is a readable first PUSH. The tenth PUSH overwrites the second

and writable register. The high byte (PC<12:8>) is not PUSH (and so on).

directly readable or writable and comes from PCLATH.

On any Reset, the PC is cleared. Figure 4-4 shows the Note 1: There are no Status bits to indicate stack

two situations for loading the PC. The upper example overflow or stack underflow conditions.

in Figure 4-4 shows how the PC is loaded on a write to 2: There are no instructions/mnemonics

PCL (PCLATH<4:0> → PCH). The lower example in called PUSH or POP. These are actions

Figure 4-4 shows how the PC is loaded during a CALL that occur from the execution of the

or GOTO instruction (PCLATH<4:3> → PCH). CALL, RETURN, RETLW and RETFIE

instructions, or the vectoring to an

FIGURE 4-4: LOADING OF PC IN interrupt address.

DIFFERENT SITUATIONS

4.4 Indirect Addressing, INDF and

PCH PCL FSR Registers

12 8 7 0 Instruction with The INDF register is not a physical register. Addressing

PC PCL as

Destination the INDF register will cause indirect addressing.

PCLATH<4:0> 8

5 ALU result Indirect addressing is possible by using the INDF

register. Any instruction using the INDF register

PCLATH

actually accesses data pointed to by the File Select

Register (FSR). Reading INDF itself indirectly will

PCH PCL produce 00h. Writing to the INDF register indirectly

12 11 10 8 7 0 results in a no-operation (although Status bits may be

PC GOTO, CALL affected). An effective 9-bit address is obtained by

concatenating the 8-bit FSR register and the IRP bit

PCLATH<4:3> 11

2 Opcode <10:0>

(STATUS<7>), as shown in Figure 4-5.

A simple program to clear RAM location 20h-2Fh using

PCLATH indirect addressing is shown in Example 4-1.

EXAMPLE 4-1: INDIRECT ADDRESSING

4.3.1 COMPUTED GOTO MOVLW 0x20 ;initialize pointer

MOVWF FSR ;to RAM

A computed GOTO is accomplished by adding an offset

NEXT CLRF INDF ;clear INDF register

to the program counter (ADDWF PCL). When doing a INCF FSR ;inc pointer

table read using a computed GOTO method, care BTFSS FSR,4 ;all done?

should be exercised if the table location crosses a PCL GOTO NEXT ;no clear next

memory boundary (each 256-byte block). Refer to the ;yes continue

Application Note AN556 “Implementing a Table Read”

(DS00556).

4.3.2 STACK

The PIC16F627A/628A/648A family has an 8-level

deep x 13-bit wide hardware stack (Figure 4-1). The

stack space is not part of either program or data space

and the Stack Pointer is not readable or writable. The

PC is PUSHed onto the stack when a CALL instruction

is executed or an interrupt causes a branch. The stack

is POPed in the event of a RETURN, RETLW or a

RETFIE instruction execution. PCLATH is not affected

by a PUSH or POP operation.

DS40044F-page 28 © 2007 Microchip Technology Inc.

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5814)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1092)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (844)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (540)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (348)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (822)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Fauji Fertilizer Company Limited FFC: Ans) ADocument8 pagesFauji Fertilizer Company Limited FFC: Ans) AFarhan Azhar KhattakNo ratings yet

- Cloudsim 3.0.3 ManualDocument90 pagesCloudsim 3.0.3 ManualBathini NipunNo ratings yet

- Sie20034 Sie20031Document1 pageSie20034 Sie20031vikilukito 2210No ratings yet

- Noise ChapterDocument32 pagesNoise ChapterShyam RajapuramNo ratings yet

- Technical Note TN - 166 FTDI Example IC PCB FootprintsDocument46 pagesTechnical Note TN - 166 FTDI Example IC PCB FootprintsSteve SmithNo ratings yet

- Department of Electronics & Communication HKE's S.L.N College of Engineering Assignment BankDocument2 pagesDepartment of Electronics & Communication HKE's S.L.N College of Engineering Assignment Bankvijayarani.katkamNo ratings yet

- M2tex1000lt10ns 1Document59 pagesM2tex1000lt10ns 1Manuel AlvaradoNo ratings yet

- LXI980+LXC6110 E Installation Configuration InstructionsDocument10 pagesLXI980+LXC6110 E Installation Configuration InstructionsGeneral Projects and Electric, C.A GEPECANo ratings yet

- Digital Systems III Practical Manual - Ver1.2Document44 pagesDigital Systems III Practical Manual - Ver1.2sifisodlungwanaNo ratings yet

- SM4378NSKP: Pin Description FeaturesDocument11 pagesSM4378NSKP: Pin Description FeaturesChami NdaNo ratings yet

- Test - Chapter 8 - Wireless, Mobile Computing, and Mobile Commerce - Quizlet PDFDocument6 pagesTest - Chapter 8 - Wireless, Mobile Computing, and Mobile Commerce - Quizlet PDFNoor ThamerNo ratings yet

- Globaltechstream Software Installation Procedure: 5Th EditionDocument27 pagesGlobaltechstream Software Installation Procedure: 5Th EditionMaxisys AutelNo ratings yet

- Single-Channel: 6N137, Hcpl-2601, Hcpl-2611 Dual-Channel: Hcpl-2630, Hcpl-2631 High Speed-10 Mbit/S Logic Gate OptocouplersDocument12 pagesSingle-Channel: 6N137, Hcpl-2601, Hcpl-2611 Dual-Channel: Hcpl-2630, Hcpl-2631 High Speed-10 Mbit/S Logic Gate Optocouplersgem1144aaNo ratings yet

- FM Catalog2017 FinalDocument68 pagesFM Catalog2017 FinalNerdyNo ratings yet

- ISAT - NPO - 3 - 1 - 2 - 7 - 1 - 1 - Indosat - Radio - Network - Layering - Strategy - Guideline - v2 2 - Four Carriers-UpdatedDocument18 pagesISAT - NPO - 3 - 1 - 2 - 7 - 1 - 1 - Indosat - Radio - Network - Layering - Strategy - Guideline - v2 2 - Four Carriers-Updatedโดราเอม่อน คัก คัก100% (1)

- Fabrication and Testing of Headlight Reminder CircuitDocument14 pagesFabrication and Testing of Headlight Reminder CircuitJimmy ReeceNo ratings yet

- Annex I List of Major Equipments 2019Document2 pagesAnnex I List of Major Equipments 2019Eunica April Catahan FloresNo ratings yet

- Chapter1 - CLO1Document28 pagesChapter1 - CLO1melvynNo ratings yet

- Best Collection of Mouse Types - Hafeez Center Online StoreDocument3 pagesBest Collection of Mouse Types - Hafeez Center Online StoreRichardNo ratings yet

- Sequence Generation LTEDocument39 pagesSequence Generation LTEsubbaNo ratings yet

- 8051 Timer and CounterDocument11 pages8051 Timer and CountermahavishnuNo ratings yet

- Foxboro™ SCADA SCD6000 RTU Architectural Overview - 41h8g7Document18 pagesFoxboro™ SCADA SCD6000 RTU Architectural Overview - 41h8g7Muhd Nu'man HNo ratings yet

- Unit E28093 6 - File HandlingDocument46 pagesUnit E28093 6 - File HandlingKeshav GarvalNo ratings yet

- Wireless Communications and Cellular Network FundamentalsDocument24 pagesWireless Communications and Cellular Network FundamentalsMahesh A BirariNo ratings yet

- Border Security - IOT - Raspberry OiDocument3 pagesBorder Security - IOT - Raspberry OiRudresh RakeshNo ratings yet

- New Product Announcement: Diodes, Inc. Announces Surface Mount 1.0W Zener DiodeDocument2 pagesNew Product Announcement: Diodes, Inc. Announces Surface Mount 1.0W Zener DiodeWagner RibeiroNo ratings yet

- ControllerMate and Automatic FingersDocument2 pagesControllerMate and Automatic FingersRhea Blny MñgNo ratings yet

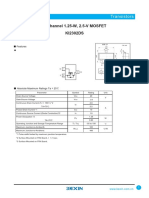

- SMD Type Transistors: N-Channel 1.25-W, 2.5-V MOSFET KI2302DSDocument2 pagesSMD Type Transistors: N-Channel 1.25-W, 2.5-V MOSFET KI2302DSСергей БрегедаNo ratings yet

- Top 10 Flexible Printed Circuit Board ManufacturersDocument15 pagesTop 10 Flexible Printed Circuit Board ManufacturersjackNo ratings yet

- The University of Auckland: Summer Semester, 2012 Campus: CityDocument24 pagesThe University of Auckland: Summer Semester, 2012 Campus: CityorhanaliuNo ratings yet