Professional Documents

Culture Documents

Ref10 06259481

Uploaded by

Rajendra ChikkanagoudaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Ref10 06259481

Uploaded by

Rajendra ChikkanagoudaCopyright:

Available Formats

A 75.5-to-120.

5-GHz, High-gain CMOS Low-Noise Amplifier

De-Ren Lu, Yu-Chung Hsu, Jui-Chih Kao, Jhe-Jia Kuo, Dow-Chih Niu*, and Kun-You Lin

Department of Electrical Engineering and Graduate Institute of Communication Engineering, National

Taiwan University, Taipei 10617, Taiwan

*Chung-Shan Institute of Science and Technology (CSIST), Taoyuan 325, Taiwan

Abstract — In this paper, a high-gain and wideband low-noise

amplifier using 65-nm CMOS process is proposed. A four-stage 30

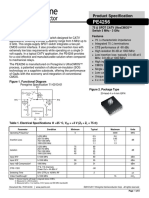

Gmax (4 fingers) NFmin (4 fingers)

8

cascode configuration is adopted to achieve the high gain and

wideband performance. With 24-mA dc current and 2-V supply Gmax (8 fingers) NFmin (8 fingers)

25 7

voltage, the LNA not only provides gain higher than 20 dB from Gmax (12 fingers) NFmin (12 fingers)

75.5 GHz to 120.5 GHz, but also has a measured noise figure

between 6 and 8.3 dB from 87 to 100 GHz. The output 1-dB 20 6

MSG/MAG (dB)

compression power (OP1dB) is -3 dBm at 110 GHz, and the chip

NFmin (dB)

size is 0.55 × 0.45 mm2. 15 5

Index Terms — W-band, low noise amplifier, MMIC, CMOS.

10 4

I. INTRODUCTION

5 3

There are several applications including astronomy

telescope, imaging, and radar systems in the W-band regime. 0 2

In the past, most of the W-band amplifiers are realized by III- 70 80 90 100 110 120 130 140 150

V technologies such as GaAs and InP pHEMT processes. Frequency (GHz)

Recently, thanks to the great progress of the CMOS Fig. 1. Simulated MSG/MAG and NFmin of the cascode configuration

technologies, more and more W-band LNAs are implemented with unit gate width of 2 μm.

by advanced CMOS processes [1]-[7]. By using 90-nm CMOS

technologies, a 104-GHz three-stage common-source (CS)

LNA is proposed with 9.34 dB gain in a narrow bandwidth [1],

and a three-stage cascode LNA achieves a wideband

performance from 86 to 108 GHz with a peak gain of 17.4 dB

[2]. Several LNAs implemented in 65-nm CMOS are

presented with gain lower than 15 dB [3]-[6]. A high-gain

LNA with a peak gain of 27 dB is demonstrated by five-stage

cascode configuration [7].

In this paper, a W-band LNA adopting four-stage cascode

configuration in 65-nm CMOS process is presented. This

design achieves a measured small-signal gain which is higher

than 20 dB from 75.5 to 120.5 GHz. The noise figure from 87

GHz to 100 GHz is 6-8.3 dB. With the wideband, high-gain

and low-noise characteristics, the LNA is suitable for the

wideband applications in W-band.

Fig. 2. Circuit schematic of the proposed W-band LNA.

II. CIRCUIT DESIGN Simulated maximum stable gain (MSG)/maximum available

This circuit is fabricated in TSMC 65-nm CMOS process. gain (MAG) and NFmin of cascode configuration under various

The process provides one poly layer for the gates of CMOS finger numbers with 2-μm unit finger width are shown in Fig.

transistors, nine metal layers with ultra-thick top metal (metal 1. It shows that using smaller device results in lower NFmin.

9) of 3.4 μm for interconnections, and metal-insulator-metal However, the transition frequency of MSG and MAG

(MIM) capacitors between metal 8 and metal 7. Based on the increases when a 4-finger transistor is selected for the cascode

model provided by foundry, the NMOS device in common- configuration. This means the cascode device is more unstable

source configuration has a maximum oscillation frequency in the desired band. Finally, the device with 8 fingers and total

(fmax) of about 220 GHz under 1-V drain-to-source voltage. gate width of 16 μm is selected in this design due to the trade-

In order to achieve high gain performance and minimize the off between gain and noise performance. The cascode device

chip size, cascode configuration is selected for this design. has 12-dB simulated MSG at 130 GHz and demonstrates 3.4-

978-1-4673-1088-8/12/$31.00 ©2012 IEEE

50

25 100

T

TLp=0 μm

TLp=200 μm

10 80 GHz 250

80

0 GHz

Γ*out@TLP=0 μm

Γ*out@TLP=50 μm

10 25 50 100 250

Γ*out@TLP=100 μm

Γ*out@TLP=150 μm

-10

Γ*out@TLP=200 μm -250 Fig. 5. Chip photograph of the widebannd LNA with the area of 0.55

x 0.45 mm2.

ΓL 30

25

-25 -100

20

-50 15

Fig. 3. Simulated Γ*out at different TLp and ΓL.

S parameters (dB)

10 Sim. |S

S11| Meas. |S11|

24 Sim. |S

S21| Meas. |S21|

TL

Lp=0 μm 5

22 Sim. |S

S22| Meas. |S22|

TL

Lp=50 μm 0

20

TL

Lp=100 μm -5

18 TL

Lp=150 μm -10

16 TL

Lp=200 μm

MSG/MAG (dB)

14 -15

12 -20

10 -25

65 70 75 80 85 90 95 100 105 110 115 120 125

8

6

Frequency (GHz)

4

Fig. 6. Simulated and measured S param

meters of the wideband LNA.

2

four-stage amplifier with the new final stage device. When the

0

40 50 60 70 80 90 100 110 120 130 140 150 length of TLp increases from 0 μm to 200 μm, Γ*out decreases

Frequency (GHz) correspondingly and makes the wideband impedance matching

Fig. 4. Simulated MSG/MAG of the cascode devicee with different easier. However, the transition freq quency of MSG and MAG

lengths of TLp. decreases with increasing length of o TLp, as shown in Fig. 4.

This shows a trade-off between the gain and the bandwidth of

5.4 dB NFmin from 80 GHz to 120 GHz whhile 2 V/6 mA is output return loss. Finally, a 190 0-μm TLp is selected. The

consumed. output matching network is simillar to the input matching

To implement a LNA with a gain better thaan 20 dB from 80 network and is consisted of series lines, a short stub and an

to 120 GHz, the four-stage design is adopted.. Fig. 2 shows the open stub. The reflection coefficieent of the output matching

complete schematic of the proposed widebband LNA. The network (ΓL) is shown in Fig. 3. It is close to the Γ*out of the

matching networks are realized by thin-film m microstrip lines four-stage amplifier with the final cascode device which has

(TFMS). The ultra-thick top metal is used as signal line of the 190 μm TLp. The die microphotograph is shown in Fig. 5. The

TFMS, and the ground plane is implemented by metal 1 and 2 2

chip size which includes all the totaal pads is 0.55 x 0.45 mm .

to meet the requirement of density rules. In thhe first stage, the

source feedback is adopted, and the input mattching network is

consisted of series transmission lines, an openn stub and a short III. MEASUREMENT

T RESULTS

stub to achieve wideband noise matching. The inter-stage The proposed LNA is measured d by on-wafer probing. To

matching networks are realized by series trransmission lines implement wideband S parameterss measurement, the vector

and short stubs. network analyzer (VNA), Anritsu 37397D, is used for the

Although the cascode configuration proviides a high gain measurement from 65 to 110 GH Hz, and the VNA, Agilent

characteristic, the output impedance is too hhigh to achieve a E8361C, is used for the measurem

ment from 110 to 125 GHz.

wideband impedance matching at the outpuut port. To solve This LNA consumes 48-mW dc power from 2-V supply

this problem, an extra transmission line (TLp), as shown in Fig. voltage. Fig. 6 shows the sim mulated and measured S

2, is placed between the CS and common-gatee (CG) transistors parameters of the proposed wideb band LNA. The measured

of the cascode device at the final stage. F Fig. 3 shows the peak gain is 25.3 dB at 117.5 GHzz, and the measured gain is

simulated conjugate output reflection coefficiient (Γ*out) of the higher than 20 dB from 75.5 GHzz to 120.5 GHz. The input

978-1-4673-1088-8/12/$31.00 ©2012 IEEE

TABLE I

COMPARISON WITH PREVIOUSLY REPORTED W-BAND CMOS LNAS.

Ref. CMOS DC Power Chip Size

Topology Peak Gain (dB) Gain (dB) NF (dB)

Process (mW) (mm2)

[1] 90 nm 3-stage CS 9.34 @103.8 GHz - - 22@1 V 0.36

[2] 90 nm 3-stage cascode 17.4 @ 91 GHz > 14.4 (86-108 GHz) - 54@2.5 V 0.42

[3] 65 nm 6-stage CS 12 > 9 (75-81 GHz) 9-10.5 (75-81 GHz) 32.4@1.2 V 0.24

[4] 65 nm 4-stage CS 14.8 @ 90 GHz > 11.8 (82-103 GHz) 7.5-9 (82-100 GHz) 86.4@1.2 V 0.33

[5] 65 nm 5-stage CS 15 @ 86 GHz > 12 (81-92 GHz) 7-9 (85-95 GHz) 42@1.2 V -

[6] 65 nm 3-stage cascode 13.5 @ 81 GHz > 10.5 (72-92 GHz) 6.4-8.4 (75-88.5 GHz) 36.3@1.5 V -

[7] 65 nm 5-stage cascode 27 @ 88 GHz > 24 (83-93 GHz) 6.8-10 (75-89 GHz) 36@1.2 V -

This Work 65 nm 4-stage cascode 25.3 @ 117.5 GHz > 20 (75.5-120.5 GHz) 6-8.3 (87-100 GHz) 48@2 V 0.25

10

Simulated NF from 87 to 100 GHz. The OP1dB of -3 dBm is obtained at 110

Measured NF GHz. This circuit accomplishes wide bandwidth

8 characteristics with high-gain and low-noise performance by

using 65-nm CMOS technology.

6

NF (dB)

ACKNOWLEDGEMENT

4

The authors would like to thank Prof. Huei Wang and Dr.

Zuo-Min Tsai of National Taiwan University for their

2

valuable suggestions. This work is supported in part by the

National Science Council of Taiwan, under Grant NSC 100-

0 2219-E-002-005, Excellent Research Projects of National

85 90 95 100

Taiwan University, under 10R80919-3, 10R80300 and the

Frequency (GHz)

Fig. 7. Simulated and measured noise figure of the wideband LNA. University Shuttle Program of Taiwan Semiconductor

Manufacturing Company (TSMC), Hsin-chu, Taiwan.

and output return losses are both better than 5 dB from 75.5 to

120.5 GHz. The measured results agree to the simulated REFERENCES

results reasonably. Fig. 7 shows the simulated and measured

noise figure, and the measured noise figure is 6-8.3 dB from [1] B. Heydari, M. Bohsali, E. Adabi, and A. Niknejad, “Low-

power mm-wave components up to 104 GHz in 90 nm

87 to 100 GHz. Output power versus input power is also CMOS,” in IEEE ISSCC Dig. Tech. Papers, 2007, pp. 200–

measured. The OP1dB are -5, -6 and -3 dBm, while the 597.

saturated output power (Psat) are -2.5, -3 and 0.5 dBm at 78, 94 [2] Y.-S. Jiang, Z.-M. Tsai, J.-H. Tsai, H.-T. Chen, and H. Wang,

and 110 GHz, respectively. “A 86 to 108 GHz amplifier in 90 nm CMOS,” IEEE Microw.

TABLE I summarizes the comparison with the previously Wireless Compon. Lett., vol. 18, no. 2, pp. 124–126, Feb.

2008.

reported W-band CMOS LNAs. The proposed LNA [3] Ning Zhang, Chih-Ming Hung, Kenneth, K. O., “80-GHz

demonstrates high gain, low noise figure and wideband Tuned Amplifier in Bulk CMOS,” IEEE Microw. Wireless

performance in a miniature size. Compon. Lett., vol. 18, no. 2, pp. 121-123, Feb. 2008.

[4] D. Sandstrom, M. Varonen, M. Karkkainen, K. Halonen, “W-

band CMOS amplifiers achieving +10dBm saturated output

VII. CONCLUSION power and 7.5dB NF,” in IEEE ISSCC Dig. Tech. Papers,

2009, pp. 486 - 487.

A W-band LNA using TSMC 65-nm CMOS technology has [5] L. Zhou, C.-C. Wang, Z. Chen, P. Heydari, “A W-band CMOS

been designed, fabricated and measured. The circuit achieves receiver chipset for millimeter-Wave radiometer systems,”

high gain and wideband performance. The four-stage cascode IEEE J. Solid-State Circuits, vol. 46, no. 2, pp. 378–391, Feb.

circuit topology is used to obtain a high gain performance, and 2011.

[6] M. Khanpour, K. W. Tang, P. Garcia, and S. P. Voinigescu,

a transmission line between the CS and CG transistors of the “A wideband W-band receiver front-end in 65-nm CMOS,”

cascode device for the final stage is added to achieve IEEE J. Solid-State Circuits, vol. 43, no. 8, pp. 1717–1730,

wideband output matching. This design demonstrates a Aug. 2008.

measured small signal gain which is better than 20 dB from [7] A. Tomkins, P. Garcia, S. P. Voinigescu, “A Passive W-Band

75.5 to 120.5 GHz. The measured noise figure is 6-8.3 dB imaging receiver in 65-nm bulk CMOS,” IEEE J. Solid-State

Circuits, vol. 45, no. 10, pp. 1981–1991, Feb. 2010.

978-1-4673-1088-8/12/$31.00 ©2012 IEEE

You might also like

- Understanding FiberOpticsDocument1 pageUnderstanding FiberOpticsInformaticaTemple100% (1)

- Satellite CommunicationsDocument84 pagesSatellite CommunicationsniczNo ratings yet

- An Introduction To Logic Circuit TestingDocument111 pagesAn Introduction To Logic Circuit Testingmedo2005100% (6)

- CMOS Integrated Circuits For Millimeter-Wave Applications Millimeter-Wave ApplicationsDocument45 pagesCMOS Integrated Circuits For Millimeter-Wave Applications Millimeter-Wave ApplicationswalkmemberNo ratings yet

- VsatDocument31 pagesVsatapichanNo ratings yet

- Understanding Fiber Optics Po Fop TM AeDocument1 pageUnderstanding Fiber Optics Po Fop TM AeAghna Tiyas MandalNo ratings yet

- Introduction To Optical Networking: From Wavelength Division Multiplexing To Passive Optical NetworkingDocument39 pagesIntroduction To Optical Networking: From Wavelength Division Multiplexing To Passive Optical NetworkingAllen JoelNo ratings yet

- Introduction To Optical NetworkingDocument39 pagesIntroduction To Optical NetworkingshahabniaziNo ratings yet

- MBF 40 Series - EMEA APAC - Rev D PDFDocument2 pagesMBF 40 Series - EMEA APAC - Rev D PDFnadim_khan_12569No ratings yet

- Alxxf Mp400: Wireless Ethernet SolutionDocument2 pagesAlxxf Mp400: Wireless Ethernet SolutionpgrNo ratings yet

- OPGW SpecDocument28 pagesOPGW SpecvikasmikkuNo ratings yet

- An Innovative Ultra Low Voltage Sub-32nm SRAM Voltage Sense Amplifier in DG-SOI TechnologyDocument4 pagesAn Innovative Ultra Low Voltage Sub-32nm SRAM Voltage Sense Amplifier in DG-SOI Technologyapi-19668941No ratings yet

- A 77 GHZ Cmos Low Noise Amplifier For Automotive Radar ReceiverDocument3 pagesA 77 GHZ Cmos Low Noise Amplifier For Automotive Radar ReceiverJeong-geun KimNo ratings yet

- 86 Gbit S Sige Receiver Module With High Sensitivity For 160 86 Gbit S DWDM SystemDocument2 pages86 Gbit S Sige Receiver Module With High Sensitivity For 160 86 Gbit S DWDM SystemSoumitra BhowmickNo ratings yet

- Msa 1105 TR1 PDFDocument4 pagesMsa 1105 TR1 PDFAlisson VahlNo ratings yet

- Microstrip Patch Antenna (3.5 GHZ) : Ansari Fahad Bilal ZaheeruddinDocument5 pagesMicrostrip Patch Antenna (3.5 GHZ) : Ansari Fahad Bilal Zaheeruddinkadambari shindeNo ratings yet

- 10 Christian Schillab-FlukeDocument35 pages10 Christian Schillab-FlukeberrezegNo ratings yet

- Rfic 06 TyaoDocument4 pagesRfic 06 TyaoGanagadhar CHNo ratings yet

- White Paper - STP-UTP - E - 2011Document12 pagesWhite Paper - STP-UTP - E - 2011Stjepan CrnkovićNo ratings yet

- Introduction To Optical Networking: From Wavelength Division Multiplexing To Passive Optical NetworkingDocument39 pagesIntroduction To Optical Networking: From Wavelength Division Multiplexing To Passive Optical NetworkingNeha VermaNo ratings yet

- Fk-202F Transducer: SpecificationsDocument2 pagesFk-202F Transducer: Specifications莊淯淞No ratings yet

- Fiber Specifications 4-13Document2 pagesFiber Specifications 4-13lazybookwarmNo ratings yet

- 250 GHZ Sige-Bicmos Cascaded Single-Stage Distributed AmplifierDocument4 pages250 GHZ Sige-Bicmos Cascaded Single-Stage Distributed AmplifierAli HattabNo ratings yet

- Alcatel 9600LSYDocument2 pagesAlcatel 9600LSYsamiNo ratings yet

- Q28QD080C0YF - QSFP28 Dual Fibre: 1310nm / 80km / 100GBASE-ZR4Document5 pagesQ28QD080C0YF - QSFP28 Dual Fibre: 1310nm / 80km / 100GBASE-ZR4Jose JaramilloNo ratings yet

- Tranceriver PDFDocument12 pagesTranceriver PDFvffabioNo ratings yet

- TS Technical Specification For OPGW Fibre Optic CableDocument10 pagesTS Technical Specification For OPGW Fibre Optic CableabhishekNo ratings yet

- Manual Amplificador Mobile Signal BoosterDocument22 pagesManual Amplificador Mobile Signal BoosterJorge MoralesNo ratings yet

- A Cmos Switching Mode Amplifier With 3 V Output Swing For Continuous-Wave Frequencies Up To 4 GHZDocument3 pagesA Cmos Switching Mode Amplifier With 3 V Output Swing For Continuous-Wave Frequencies Up To 4 GHZwbnetNo ratings yet

- Unit7 WDM Concept and ComponentsDocument45 pagesUnit7 WDM Concept and ComponentspavithraNo ratings yet

- Fisa Tehnica Cablu FTP Cu Sufa CAT6Document1 pageFisa Tehnica Cablu FTP Cu Sufa CAT6Eugen CreastaNo ratings yet

- CPG25 - 5in1 - V8-CFD195-5.2M - 17' - SMA SPEC (2) - 1Document22 pagesCPG25 - 5in1 - V8-CFD195-5.2M - 17' - SMA SPEC (2) - 1Airul MutaqinNo ratings yet

- New Generation of Fiber OpticDocument45 pagesNew Generation of Fiber OpticfriendamigoNo ratings yet

- Product Technical Data: 418Mhz Am Miniature Transmitter Module (Micro TX) Nv08JDocument4 pagesProduct Technical Data: 418Mhz Am Miniature Transmitter Module (Micro TX) Nv08Jinsomnium86No ratings yet

- Microwave ODU: F e A T U R e SDocument2 pagesMicrowave ODU: F e A T U R e Sopeda normanNo ratings yet

- 1 8 GHZ Gallium Nitride Distributed Power Amplifier Mmic Utilizing Trifilar TransformerDocument4 pages1 8 GHZ Gallium Nitride Distributed Power Amplifier Mmic Utilizing Trifilar Transformeraiffer jasonNo ratings yet

- NS3000 Modem BD 2Document2 pagesNS3000 Modem BD 2Andy ChanNo ratings yet

- VCSEL Gigabit EthernetDocument2 pagesVCSEL Gigabit EthernetVictor Alfonso Gomez MatallanaNo ratings yet

- w3dzz Antenna Iss 1 31 PDFDocument4 pagesw3dzz Antenna Iss 1 31 PDFcokeclNo ratings yet

- MBF-40 Series: Single, Dual, Tri and Quad Band For BrazilDocument3 pagesMBF-40 Series: Single, Dual, Tri and Quad Band For BrazilClaudia MendesNo ratings yet

- Tsop 2338Document7 pagesTsop 2338stari692002No ratings yet

- SAGEM LINK F - Brochure PDFDocument2 pagesSAGEM LINK F - Brochure PDFMaz MoektiNo ratings yet

- Elber Datasheets Mobile Systems - SPM - (Mt-Mr-Line) (En)Document2 pagesElber Datasheets Mobile Systems - SPM - (Mt-Mr-Line) (En)Techne PhobosNo ratings yet

- A 77 GHZ Controllable Gain Low Noise AmplifierDocument4 pagesA 77 GHZ Controllable Gain Low Noise AmplifierMehrdad FahimniaNo ratings yet

- Mmic Sot 343 Marking CodeDocument4 pagesMmic Sot 343 Marking Codeckean_ngNo ratings yet

- Receptor IR TSOP4836Document7 pagesReceptor IR TSOP4836damijoseNo ratings yet

- Samsung SCH I535Document169 pagesSamsung SCH I535shlomi sellmecellNo ratings yet

- Cascadable Silicon Bipolar MMIC Amplifiers: Technical DataDocument4 pagesCascadable Silicon Bipolar MMIC Amplifiers: Technical DataGabriel RacovskyNo ratings yet

- 5 WattsDocument4 pages5 WattsRabbia SalmanNo ratings yet

- Category 6 250Mhz Gel Filled Outdoor Lan CableDocument2 pagesCategory 6 250Mhz Gel Filled Outdoor Lan Cablesoulkidnyc4920No ratings yet

- Low Noise Amplifier Design Using 0.35 Μm Sige Bicmos Technology For Wlan/Wimax ApplicationsDocument5 pagesLow Noise Amplifier Design Using 0.35 Μm Sige Bicmos Technology For Wlan/Wimax ApplicationssunilsheelavantNo ratings yet

- Astel Digital RG179Document3 pagesAstel Digital RG179Faiz BajwaNo ratings yet

- Optical MultiplexerDocument15 pagesOptical Multiplexereabhishek22250% (2)

- Using DSM For High EfficiencyDocument16 pagesUsing DSM For High EfficiencyAnisNo ratings yet

- Panduit - Testing 10Gbps WPDocument12 pagesPanduit - Testing 10Gbps WPpmoreno64No ratings yet

- EE240 Term Project SPRING 2001: OutlineDocument22 pagesEE240 Term Project SPRING 2001: OutlineArnab Jyoti BaruahNo ratings yet

- Design of Square - Ring Microstrip AntennaDocument8 pagesDesign of Square - Ring Microstrip Antennasutariahardik_bvm66No ratings yet

- Data Sheet: MGA-425P8Document15 pagesData Sheet: MGA-425P8Aparna BhardwajNo ratings yet

- Wireless 3g InstallationDocument4 pagesWireless 3g Installationasaad_81No ratings yet

- Product SpecificationDocument8 pagesProduct SpecificationEivar IndependenciaNo ratings yet

- Radio Frequency Identification and Sensors: From RFID to Chipless RFIDFrom EverandRadio Frequency Identification and Sensors: From RFID to Chipless RFIDNo ratings yet

- High-Performance D/A-Converters: Application to Digital TransceiversFrom EverandHigh-Performance D/A-Converters: Application to Digital TransceiversNo ratings yet

- Ref3 HCL 60GHzDocument15 pagesRef3 HCL 60GHzRajendra ChikkanagoudaNo ratings yet

- Ref14 CurrentReuse CGLnaDocument8 pagesRef14 CurrentReuse CGLnaRajendra ChikkanagoudaNo ratings yet

- Ref13 - LNA - Ultra Low Power 60 GHZ LNA - CSTopologyDocument3 pagesRef13 - LNA - Ultra Low Power 60 GHZ LNA - CSTopologyRajendra ChikkanagoudaNo ratings yet

- Intel® HM77 Express ChipsetDocument988 pagesIntel® HM77 Express ChipsetShivbraham Singh RajawatNo ratings yet

- 24aguideline For Pre of PHD ThesisDocument3 pages24aguideline For Pre of PHD ThesisAshutosh SadalgeNo ratings yet

- World Academy of Science, Engineering and TechnologyDocument4 pagesWorld Academy of Science, Engineering and Technologywhxlinan1222No ratings yet

- Jagjyothi Basavanna's VachanasDocument52 pagesJagjyothi Basavanna's VachanasRajendra ChikkanagoudaNo ratings yet

- UGC List of Journals PDFDocument1,046 pagesUGC List of Journals PDFRajendra Chikkanagouda100% (1)

- A W-Band CMOS Receiver Chipset For Milli PDFDocument14 pagesA W-Band CMOS Receiver Chipset For Milli PDFRajendra ChikkanagoudaNo ratings yet

- Rama Raksha Stotram in KannadaDocument5 pagesRama Raksha Stotram in KannadaRajendra Chikkanagouda100% (1)

- CarsDocument2 pagesCarsRajendra ChikkanagoudaNo ratings yet

- Seed Germination Expirement For School KidsDocument8 pagesSeed Germination Expirement For School KidsRajendra ChikkanagoudaNo ratings yet

- Save Forest For School KidsDocument7 pagesSave Forest For School KidsRajendra ChikkanagoudaNo ratings yet

- Mixed Mode Vlsi Sylabus For EC 6semDocument2 pagesMixed Mode Vlsi Sylabus For EC 6semabualsNo ratings yet

- Chart ComicSansNewDocument7 pagesChart ComicSansNewRajendra ChikkanagoudaNo ratings yet

- CMOS-VLSI-Mtech - Anil Nand+punith Gowda MBDocument19 pagesCMOS-VLSI-Mtech - Anil Nand+punith Gowda MBPunith Gowda M BNo ratings yet

- CellVine Repeater 50W - PCS1900Document2 pagesCellVine Repeater 50W - PCS1900Danny SassinNo ratings yet

- Mmic Power Amplifier ThesisDocument8 pagesMmic Power Amplifier ThesisWriteMyApaPaperUK100% (2)

- W. Tomasi - PPDocument15 pagesW. Tomasi - PPapi-26783388100% (2)

- A 17.5-26 GHZ Low-Noise Amplifier With Over 8 KV Esd Protection in 65 NM CmosDocument3 pagesA 17.5-26 GHZ Low-Noise Amplifier With Over 8 KV Esd Protection in 65 NM CmosBisuNo ratings yet

- Optimization of Cmos 018 M Low Noise Amplifier Usi PDFDocument14 pagesOptimization of Cmos 018 M Low Noise Amplifier Usi PDFRiyaz ShaikNo ratings yet

- LNA Lab TutorialDocument17 pagesLNA Lab TutorialMohamed MegahedNo ratings yet

- 2012 Eeysc 947Document74 pages2012 Eeysc 947Nabil DakhliNo ratings yet

- EC8651 TLW R2017 2 MarksDocument11 pagesEC8651 TLW R2017 2 Marksdhanaraj100% (2)

- Audio Video Systems (2151101) : Laboratory Manual (AY 2019-20)Document18 pagesAudio Video Systems (2151101) : Laboratory Manual (AY 2019-20)kamlesh chauhanNo ratings yet

- Design and Analysis of Low Noise AmplifierDocument11 pagesDesign and Analysis of Low Noise AmplifierDr. P Akhendra KumarNo ratings yet

- Choke RingDocument2 pagesChoke RingTrenton Astley IslaNo ratings yet

- Sensors 19 01273 PDFDocument16 pagesSensors 19 01273 PDFRitesh SadwikNo ratings yet

- Impact of Noise Figure On A Satellite Link PerformanceDocument3 pagesImpact of Noise Figure On A Satellite Link PerformanceMuhammad Umar AbbasiNo ratings yet

- LNA TutorialDocument112 pagesLNA TutorialCorol LanNo ratings yet

- CNAV - C-Nav286 AntennaDocument2 pagesCNAV - C-Nav286 AntennatheoNo ratings yet

- Spectre SimulationsDocument9 pagesSpectre SimulationsicdaneNo ratings yet

- EE314 Stanford Lectures On RFDocument19 pagesEE314 Stanford Lectures On RFapi-3804019100% (3)

- 2.4 GHZ LNA Filter DesingDocument4 pages2.4 GHZ LNA Filter DesingNikhilAKothariNo ratings yet

- Apx1000-2000-4000 Service Manual 68012004061 f-8Document100 pagesApx1000-2000-4000 Service Manual 68012004061 f-8buenodrNo ratings yet

- ECE370b - 2014 - LAB-4 - MIXERDocument13 pagesECE370b - 2014 - LAB-4 - MIXERKiran U NNo ratings yet

- Lna ReportDocument28 pagesLna ReportPranjal JalanNo ratings yet

- A System To Measure Out-of-Band Noise of IEEE 802.11b/g/a/n/ac Transmitter Signals in Cellular Frequency Bands With Noise CalibrationDocument6 pagesA System To Measure Out-of-Band Noise of IEEE 802.11b/g/a/n/ac Transmitter Signals in Cellular Frequency Bands With Noise CalibrationSudarsh Suresh MallayaNo ratings yet

- Amplifier ManualDocument5 pagesAmplifier ManualSamparka SanyalNo ratings yet

- The Technical Working of Low Noise AmplifierDocument11 pagesThe Technical Working of Low Noise AmplifierjackNo ratings yet

- ICOM AG-2400 2.4 GHZ Down Converter WWDocument4 pagesICOM AG-2400 2.4 GHZ Down Converter WW10sd156No ratings yet

- Service ManualDocument30 pagesService ManualcenyagorbunkovNo ratings yet

- GPS, LNA, Sensitivity, Jamming, Cohabitation, TTFF: Global Position System Low Noise AmplifierDocument5 pagesGPS, LNA, Sensitivity, Jamming, Cohabitation, TTFF: Global Position System Low Noise AmplifiergarunkumargNo ratings yet

- Unit Ii Space Segment and Satellite Link Design: Spacecraft Technology-StructureDocument28 pagesUnit Ii Space Segment and Satellite Link Design: Spacecraft Technology-StructureSoundararajan RajagopalanNo ratings yet