Professional Documents

Culture Documents

NTNU Exam in Integrated Circuit Design

Uploaded by

enekoOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

NTNU Exam in Integrated Circuit Design

Uploaded by

enekoCopyright:

Available Formats

NTNU

Norwegian University of Department of Electronics and

Science and Technology Telecommunications

Exam in the subject TFE4151 Design of Integrated Circuits

Date: 15th of December 2012

Hours: 09:00 - 13:00

Remedy: D No printed and hand written remedies are allowed. A specified

simple calculator is allowed.

The examination results: 15th of January 2013

Contact during the exam: Professor Snorre Aunet; 73594316, 90013264.

Research fellow Iason Filippopoulos; 41187244

TFE4151 – Design of integrated circuits 15th of December 2012 Page 1 / 21

General information:

This is a multiple choice exam. All tasks have 4 alternative answers. There is also the alternative I

don’t know. All tasks must be answered. If you do not answer it is counted as a wrong answer. You

are allowed to hedge.

A correct answer is 3 points. A wrong answer is -1 point. I don’t know is 0 points. By hedging, the

points for the answers are counted together. There is 1 correct answer for each task.

Fill in your answers in the three forms at the end of this set. Hand in the two last forms as your

answer to this exam with the necessary information added. You may keep the first form for yourself

as a copy. If there are any discrepancies between the marks on your copy and the forms that are

submitted, the marking on the form “Teachers copy” is regarded as your answer.

Good luck!

The tasks:

1. The figure below shows a MOSFET characteristic. Indicate which region it is operating for

different letters mentioned in figure with direction of VGS.

A. A Short channel, B Triode, C Active and VGS upward

B. A Triode, B Active, C Short channel VGS upward

C. A Triode, B Active, C Short channel VGS downward

D. A Active, B Triode, C Short Channel VGS upward

E. I don’t know

TFE4151 – Design of integrated circuits 15th of December 2012 Page 2 / 21

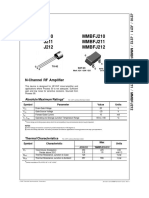

2. An NMOS transistor in 45 nm CMOS, having parameters that are enclosed with this exam set,

has a gate length of 50 nm, a width of 65 nm and VGS = 1.55 V. Assume infinite output resistance for

your calculations. What will be the drain current for this device, given these conditions?

(Given: iD = 0.5µnCoxW(VGS - Vtn)2/L)

A. 188.2 µA

B. 220.2 µA

C. 244.7 µA

D. 130.3 µA

E. I don’t know.

3. A layout of an amplifier is shown in figure 1, what type of amplifier? (Hint: Draw equivalent

circuit)

A. Common gate amplifier

B. Differential amplifier

C. Cascode amplifier

D. Cascade amplifier

E. I don’t know

Fig. 1.

4. The figure below shows the cross section of a CMOS-circuit that is produced on a weakly doped

p-type substrate. What circuit is it?

A. NMOS source-follower with diode-coupled NMOS load

B. PMOS source-follower with diode-coupled PMOS load

C. PMOS current mirror

D. NMOS current mirror

E. I don’t know

TFE4151 – Design of integrated circuits 15th of December 2012 Page 3 / 21

5. Figure 2 shows a PMOS current mirror. The circuit has two transistors: M1 with gate width W1

and gate length L1, and M2 with gate width W2 and gate length L2.

M1 M2

Iout

Iref

Fig. 2.

You want to scale the transistor geometries such that Iout = 4* Iref and the output impedance gets

as large as possible. Which alternative is the best?

A. W1= 10 m, L1 = 1 m, W2 = 40 m, og L2 = 1 m

B. W1= 40 m, L1 = 1 m, W2 = 10 m, og L2 = 1 m

C. W1 = 40 m, L1 = 4 m, W2 = 10 m, og L2 = 4 m

D. W1 = 10 m, L1 = 2 m, W2 = 40 m, og L2 = 2 m

E. I don’t know

6. The amplifier shown has a total instantaneous gate-to-source input voltage, with the input signal,

vgs, of vGS = VGS + vgs. This results in a total instantaneous drain-current, iD, consisting of three

components, c1, c2 and c3. c1 = (µnCoxW/2L)(VGS – Vt)2. c2 = (µnCoxW/L)(VGS – Vt)vgs. c3 =

(µnCoxW/2L)vgs2. Which component, or which components, are in most cases undesirable?

TFE4151 – Design of integrated circuits 15th of December 2012 Page 4 / 21

A. c1

B. c2 and c3

C. c2

D. c3

E. I don’t know.

7. The common-source amplifier above, has an NMOS transistor with a transconductance of “gm”

and a small signal resistance from drain to source, “rds”. The transistor is operating in the active

region. What is the small signal voltage gain of the amplifier?

A. - gm(rds || RD)

B. - gm(rds)

C. - gm RD

D. - gm(rds x RD)

E. I don’t know.

8. A common source amplifier is given in the figure below. What is the voltage gain of the

amplifier?

Given: All MOSFET have W/L= 50 µm / 0.8 µm. µnCox= 90 µA/V2, µpCox=30 µA/V2,

Ibias= 100 µA, rds-n() = 8000 L(µm)/ID (mA) and rds-p() = 10000 L(µm)/ID (mA).

A. -37.7

B. -75.4

C. 7.54

D. 150.8

E. I don’t know

TFE4151 – Design of integrated circuits 15th of December 2012 Page 5 / 21

9. Variations in transistor parameters, supply voltage and temperature (PVT) variations can be

problematic to analog designers trying to reliably meet specific performance criteria. Let’s consider

the case of having a current mirror as seen in the figure, with two identically drawn transistors with

W1 = W2 = 2 µm, and L1 = L2 = 0.5 µm Which transistor dimensions would you suggest to improve

the current matching of the current mirror by a factor of 2?

A. W1 = W2 = 2 µm, and L1 = L2 =

1.0 µm

B. W1 = 2 µm, W2 = 4 µm and L1 = M1 M2

L2 = 0.5 µm

C. W1 = 2 µm, W2 = 2 µm and L1 =

L2 = 2 µm Iout

D. W1 = 4 µm, W2 = 4 µm and L1 = Iref

L2 = 2 µm

E. I don’t know.

10. Which alternative below contains one or more false statements about matching in CMOS?

A. Matching is generally very important for analog CMOS. Matching of transistors may be

improved by connecting several unit-sized transistors in parallel.

B. Matched devices should ideally have the same boundary conditions, which may be

accomplished by adding dummy components.

C. For transistors with the same VGS we have to quadruple the device area if we are going to

improve the current matching by a factor of 2.

D. Vt mismatch seldom has to be taken into account by analog designers.

E. I don’t know.

11. What is the least number of transistors needed to implement F = A·B + A·C·D in CMOS ( not

exploiting a technique like for example pseudoNMOS )?

A. 8

B. 10

C. 16

D. 20

E. I don’t know

12. Which statement about power consumption in a CMOS inverter with capacitive load is not true?

A. The power consumption may be divided in one static (DC) and one dynamic component.

B. The dynamic power dissipation is proportional to the signal frequency.

C. Reducing the supply voltage is a very effective way of reducing the overall power

Consumption since it has a quadratic impact on the power consumption.

D. The static power consumption is proportional to the load capacitance.

E. I don’t know

TFE4151 – Design of integrated circuits 15th of December 2012 Page 6 / 21

13. What is correct for a large load?

A. CMOS drivers may may drive a larger current than equally sized bipolar drivers.

B. Bipolar drivers may drive a larger current than equally sized CMOS drivers.

C. With bipolar drivers there will be an overshoot on the output voltage beyond VDD and VSS.

D. All the above statements are wrong.

E. I don’t know

14. A CMOS transistor has been produced, and parts of the result, are shown below. How does it

influence the operation of the gate?

A. The transistor is always off. (May not be turned on).

B. The transistor is always on. (May not be turned off).

C. It’s nothing wrong with this transistor.

D. The gate is extended too far to the right, short circuiting the gate to the nWell.

E. I don’t know.

15. Which statement below is generally not true for an NMOS transistor operating in the active

region?

A. The small signal output resistance, rds, increases when the gate length increases.

B. Increasing the voltage level of the bulk node decreases the current between drain and source.

C. Increasing Veff = VGS - Vtn increases the current between drain and source.

D. Increasing Veff = VGS - Vtn decreases the small signal output resistance, rds.

E. I don’t know.

16. The signal delay on an interconnect length of 10 µm is 2.5 ps. If the line is increased to 40 µm,

what would be the delay of the complete, extended, line?

A. 10 ps

B. 40 ps

TFE4151 – Design of integrated circuits 15th of December 2012 Page 7 / 21

C. 39,0625 ps

D. 30 ps

E. I don’t know.

17. You shall design an edge triggered D-register with synchronous set and reset. Set and Reset are

active HIGH. Which code is correct?

A. always@(clk)

if (1 == reset)

out = 0;

else if (1==set)

out = 1;

else

out = d_in;

B. always@(posedge(clk))

if (1 == set)

out = 0;

else if (1 == eset)

out = 1;

else

out = d_in;

C. always@(posedge clk) or posedge(reset) or posedge(set))

if (1 == reset)

out = 0;

else if (1==set)

out = 1;

else

out = d_in;

D. always@(posedge clk)

if (1 == reset)

out = 0;

else if (1==set)

out = 1;

else

out = d_in;

E. I don’t know

18. The Verilog code below describes:

always @(b)

A. One-bit full adder case (b)

2’b00: a = 1’b0;

B. One-bit half adder

2’b01: a = 1’b0;

C. One-bit comparator 2’b10: a = 1’b0;

D. 2-input and 2’b11: a = 1’b1;

E. I don’t know endcase

TFE4151 – Design of integrated circuits 15th of December 2012 Page 8 / 21

19. You are designing a clock-generator by a ring oscillator. This Verilog code is a part of your

code. What is the clock period for this clock generator?

A. 18 ps `timescale 1 ps/1 fs

B. 27 ps …

C. 36 ps

not #(2, 2)

D. 54 ps I1 (s[3], s[2]),

E. I don’t know I2 (s[4], s[3]),

I3 (s[5], s[4]),

I4 (s[6], s[5]),

I5 (s[7], s[6]),

I6 (s[8], s[7]),

I7 (s[9], s[8]),

I8 (s[1], s[9]);

nor #(2, 2)

N1 (s[2], s[1], reset);

assign clk = s[1];

20. The plot shows the output voltage from an inverter when it changes from HIGH to LOW value.

What is the fall-time tf, for the signal?

A. tf = t4 – t3 Vut

B. tf = t4 – t2

C. tf = t3 – t2

D. tf = t5 – t1

E. I don’t know

t1 t2 t3 t4 t5 tid

TFE4151 – Design of integrated circuits 15th of December 2012 Page 9 / 21

21. The VTC curve for an inverter is shown below. VM is Vdd/2, so that a dc voltage of Vdd/2 at the

input results in the same value at the output. At the end of the problem set you find MOSFET

parameters representative of various CMOS technologies. Given that the VTC curve below is valid

for the 180 nm technology, which statement below would be valid when implementing the same

inverter in 45 nm technology (not changing the MOSFET aspect ratios)?

A. The VTC curve would remain the same.

B. The VTC curve would be shifted slightly to the left (meaning that the area under the VTC curve

would decrease).

C. The VTC curve would be shifted slightly to the right (meaning that the area under the VTC

curve would increase)..

D. The midpoint, VM, would stay the same, but the voltage gain would increase.

E. I don’t know.

22. A standard CMOS inverter is implemented in an nWell process. The input voltage level is Vdd.

The transistor placed in the nWell has it’s “B” node decreased from one dc voltage level to another

dc voltage level. May this change in the voltage level impact the drain current through the devices?

A. This change leads to an increase in the drain-currents of both transistors.

B. This change does not lead to a change in the drain-currents of any transistor.

C. The change leads to an increased drain-current in the PMOS only.

D. The change leads to an increased drain-current in the NMOS only.

E. I don’t know.

23. How many transistors is it usually in CMOS AND and OR gates having N inputs?

A. N

B. N+1

C. 2N

D. 2N+2

E. I don’t know.

24. How may transistors is it in a simple pseudo nMOS gate having N inputs?

A. N

B. N+1

C. 2N

D. N2

E. I don’t know.

TFE4151 – Design of integrated circuits 15th of December 2012 Page 10 / 21

25. What is the false statement with respect to state machines?

A. Registers for state machines are m bits wide and can be built using flip-flops, which may

result in machines with 2m states.

B. D-flip-flops are often used when implementing state machines, due to their simplicity and

good performance, compared to several other types of flip-flops.

C. The overall speed of a state machine is seldom determined by any limitations imposed by

the clocking.

D. State machines are used in VLSI chips of a wide range of different types.

E. I don’t know.

26. With the NOR-gate to the right, the test vector {AB} = {01} is applied. Which faults are detected

by this test? (A-SA1 is input A Stuck-at-1.)

A. A-SA1, F-SA1

B. A-SA1, F-SA0

C. B-SA0, F-SA0

D. B-SA0, F-SA1

E. I don’t know

27. We have the combinatorial network given below. The B inputs are Stuck-at-0. Which test vector,

{A,B,C,D}, detects this fault? ( Path sensitization is one possible means of finding a test vector.)

A. {1,1,1,1}

B. {1,0,0,1}

C. {0,1,0,1}

D. {0,1,1,1}

E. I don’t know

28. What is correct about CMOS-gates?

A. The delay through a CMOS-gate is only defined by the gate itself.

B. The delay through a CMOS-gate is only defined by the load.

C. The delay through a CMOS-gate is independent of by the load and the gate itself.

D. The delay through a CMOS-gate is defined by the load (conductors and gates) and the gate

itself

E. I don’t know.

29. The figure is taken from “Introduction to VLSI Circuits and Systems, by John P. Uyemura and

shows an inverter cascade. A least possible delay through the chain is desired. Suppose that we want

to drive a load capacitance of value CL = 10 pF (where 1 pF = 10-12 F). The input stage is defined

with C1 = 20 fF (1 fF = 10-15 F). What is the proper number of scaled inverters that should be used?

TFE4151 – Design of integrated circuits 15th of December 2012 Page 11 / 21

A. 1

B. 6

C. 7

D. 9

E. I don’t know

30. Parts of a layout is shown below (from the book by J. P. Uyemura). What is the corresponding

circuit functionality?

A. A tri-state inverter

B. A D-latch with nFET pass gates

C. A 1-bit DRAM cell

D. An SRAM cell

E. I don’t know

31. With the given data, what is the value of in the conductor?

R□ = 0,05 /□

C = 0,05 fF/m2

= 0,25 m

A. 1,56 fs W=2

B. 0,625 fs

L = 100

C. 2,50 fs

D. 6,25 fs

E. I don’t know

TFE4151 – Design of integrated circuits 15th of December 2012 Page 12 / 21

32. What does it mean that a CMOS transistor is bidirectional?

A. The pn-junction between the well and the bulk may have current in both directions.

B. The transistors are placed on the circuit by “simulated annealing”.

C. The Gate electrode is used as a part of the mask set for the transistor.

D. The Source and the Drain electrodes are equivalent. The current in the channel may flow in

both directions.

E. I don’t know.

33. What does this net list model?

A. or-and-invert .subckt ukjent 1 2 3 4 5 6 7 8

m1 3 2 1 1 pmos l=1u w=3u

B. and-or-invert m2 5 4 3 1 pmos l=1u w=3u

C. or m3 7 6 5 1 pmos l=1u w=3u

D. nor m4 9 7 1 1 pmos l=1u w=3u

m5 9 7 8 8 nmos l=1u w=1u

E. I don’t know m6 7 2 8 8 nmos l=1u w=1u

m7 7 4 8 8 nmos l=1u w=1u

m8 7 6 8 8 nmos l=1u w=1u

.ends

34. Which statement is not true for 64-bits adder circuits?

A. A Ripple-Carry Adder is smaller than a Carry Look-Ahead Adder.

B. A Carry-Look-Ahead Adder has higher power consumption than a Ripple-Carry-Adder.

C. The 64 bit Ripple-Carry Adder requires 64 Full Adders.

D. There is no connection between the power consumption and the speed for an adder.

E. I don’t know.

35. What does this netlist model?

A. or-and-invert .subckt unknown 1 2 3 4 5 6 7 8

m1 7 6 5 1 pmos l=1u w=3u

B. and-or-invert m2 5 4 3 1 pmos l=1u w=3u

C. nor m3 3 2 1 1 pmos l=1u w=3u

D. or m5 7 2 8 8 nmos l=1u w=1u

m6 7 4 8 8 nmos l=1u w=1u

E. I don’t know m7 7 6 8 8 nmos l=1u w=1u

.ends

TFE4151 – Design of integrated circuits 15th of December 2012 Page 13 / 21

36. The netlist below represent different circuits. Which one corresponds to F = A NAND B?

A. .subckt NAND2A 1 2 3 4 5 6

m1 1 3 5 1 pmos l=1u w=1u

m2 5 4 1 1 pmos l=1u w=1u

m3 5 3 2 2 nmos l=1u w=1u

m4 2 4 5 2 nmos l=1u w=1u

.ends

B. .subckt NAND2B 1 2 3 4 5 6

m1 4 2 1 1 pmos l=1u w=1u

m2 4 3 1 1 pmos l=1u w=1u

m3 4 2 5 6 nmos l=1u w=1u

m4 5 3 6 6 nmos l=1u w=1u

.ends

C. .subckt NAND2C 1 2 3 4 5 6

m1 1 3 6 1 pmos l=1u w=1u

m2 6 4 5 1 pmos l=1u w=1u

m3 5 3 2 2 nmos l=1u w=1u

m4 5 4 2 2 nmos l=1u w=1u

.ends

D. .subckt NAND2D 1 2 3 4 5 6

m1 1 2 3 1 pmos l=1u w=1u

m2 6 4 5 1 pmos l=1u w=1u

m3 5 4 6 2 nmos l=1u w=1u

m4 3 2 1 2 nmos l=1u w=1u

.ends

E. I don’t know.

37. A CMOS gate has the P-net in the figure. Which function is this? Remember that 1’ = 0, 0’ = 1

A. This is not a digital function.

B. Out = (C·D+B·E+A)’ VDD

C. Out = [(B+C)·(A+D+E)]’

D. Out = [(A·D·E)+(B·C)]’ D

E. I don’t know

C E

B A

Out

TFE4151 – Design of integrated circuits 15th of December 2012 Page 14 / 21

38. A transistor diagram is given below. What is the corresponding function?

A. This is not a digital function.

B. A tri-state output

C. A non-inverting buffer

D. A mirrored implementation of a

2-input NAND

E. I don’t know

39. A transistor diagram is given below. What is the corresponding function?

A. This is not a digital function.

B. Out = AB + CD

C. Out = (AB+CD)’

D. Out = [(A+B)(C+D)]’

E. I don’t know

40. A transistor diagram is shown below. What is this?

A. OUT = (A XOR B) XOR C

B. OUT = ((A XOR B) XOR C)’

C. OUT=A’B’+A’C’+B’C’

D. This will not work.

E. I don’t know

TFE4151 – Design of integrated circuits 15th of December 2012 Page 15 / 21

TFE4151 – Design of integrated circuits 15th of December 2012 Page 16 / 21

TFE4151 – Design of integrated circuits 15th of December 2012 Page 17 / 21

TFE4151 – Design of integrated circuits 15th of December 2012 Page 18 / 21

TFE4151 – Design of integrated circuits 15th of December 2012 Page 19 / 21

Submittal form for the exam for subject Studentnr: ..........................

TFE4151 Design of integrated circuits Studieprogram:...................

(Student copy)

You may use this form to make a copy of what you

submit. Submit the form on the last page.

If there is a discrepancy between the marks on the copy and the submitted form, the submitted

form is the one valid.

Fill in your Student number and Studieprogram.

Task A B C D E Task A B C D E

1 21

2 22

3 23

4 24

5 25

6 26

7 27

8 28

9 29

10 30

11 31

12 32

13 33

14 34

15 35

16 36

17 37

18 38

19 39

20 40

TFE4151 – Design of integrated circuits 15th of December 2012 Page 20 / 21

Submittal form for the exam for subject

Studentnr: ..........................

TFE4151 Design of Integrated Circuits

Fill in this form and submit it as your answer to the exam. Studieprogram: ...................

You may use the form on a previous page as a copy for

yourself. Do not submit any calculations.

If there is a discrepancy between the marks on the copy and the submitted form, the submitted

form is the one valid. If there is a discrepancy between the marks on the external examiner

copy and this submitted form, this submitted form is the one valid.

Fill in your Student number and Studieprogram..

Task A B C D E Task A B C D E

1 21

2 22

3 23

4 24

5 25

6 26

7 27

8 28

9 29

10 30

11 31

12 32

13 33

14 34

15 35

16 36

17 37

18 38

19 39

20 40

TFE4151 – Design of integrated circuits 15th of December 2012 Page 21 / 21

You might also like

- Electronic Devices and Circuits Fifth Edition by David A. BellDocument48 pagesElectronic Devices and Circuits Fifth Edition by David A. BellVIGNESH T A50% (34)

- Homework 2Document8 pagesHomework 2A.A.RON33% (3)

- 2011 Final MECH 368Document14 pages2011 Final MECH 368Akmal FarhanNo ratings yet

- Frequency Response of BJT and MOFETDocument54 pagesFrequency Response of BJT and MOFETshubhankar palNo ratings yet

- Ee141 HW5 2Document3 pagesEe141 HW5 2Vidhya DsNo ratings yet

- VLSI Quiz QuestionsDocument17 pagesVLSI Quiz Questionsjitu_40% (1)

- Homework 1 EE 240b Advanced Analog CircuitsDocument2 pagesHomework 1 EE 240b Advanced Analog Circuitsb98154No ratings yet

- DAC AnalysisDocument19 pagesDAC Analysisమురళీధర్ ఆది ఆంధ్రుడుNo ratings yet

- MOSFET Amplifier Design and Current Mirror CircuitsDocument30 pagesMOSFET Amplifier Design and Current Mirror CircuitssreevatsakurudiNo ratings yet

- EE 2.3: Semiconductor Modelling in SPICE Course Homepage:: SPICE Diode and BJT ModelsDocument34 pagesEE 2.3: Semiconductor Modelling in SPICE Course Homepage:: SPICE Diode and BJT ModelsKathir ChandraboseNo ratings yet

- MOSFET design and operationDocument44 pagesMOSFET design and operationAbdul KhaliqNo ratings yet

- Ece 331 Lab Manual Spring 2021Document86 pagesEce 331 Lab Manual Spring 2021haiderNo ratings yet

- Measuring InstrDocument4 pagesMeasuring InstrG ParidaNo ratings yet

- Exercise 3 - Summer Semester 2019Document8 pagesExercise 3 - Summer Semester 2019Mario PajaNo ratings yet

- General Instructions To The CandidateDocument4 pagesGeneral Instructions To The Candidateapurv shuklaNo ratings yet

- 6.012 Electronic Devices and Circuits: Final ExaminationDocument13 pages6.012 Electronic Devices and Circuits: Final ExaminationhelpsatyaNo ratings yet

- Euler's PathDocument10 pagesEuler's PathSatish Kumar0% (1)

- Ee141 HW2 3 PDFDocument5 pagesEe141 HW2 3 PDFVidhya DsNo ratings yet

- Two-stage CMOS op amp design and analysis in 150nm techDocument6 pagesTwo-stage CMOS op amp design and analysis in 150nm techsohailasghar_tNo ratings yet

- Steber An LMS Impedance BridgeDocument7 pagesSteber An LMS Impedance BridgebigpriapNo ratings yet

- CMOS Logic Schematic and Layout LabDocument2 pagesCMOS Logic Schematic and Layout LabSiam HasanNo ratings yet

- Chapter 4 - JFET PDFDocument13 pagesChapter 4 - JFET PDFnelsonjnelsonjNo ratings yet

- JFET transistor guideDocument17 pagesJFET transistor guideChen Chee JungNo ratings yet

- Exam 1 ECE 410 Fall 2002Document5 pagesExam 1 ECE 410 Fall 2002Bereket LemmaNo ratings yet

- CMOS fundamentals and design techniquesDocument5 pagesCMOS fundamentals and design techniquesShreyas S RNo ratings yet

- Ee141 HW3Document4 pagesEe141 HW3Vidhya DsNo ratings yet

- Answer: Q1Document46 pagesAnswer: Q1amar2k904100% (3)

- EE 240B Homework: Analog Design Problems For Electrical EngineersDocument3 pagesEE 240B Homework: Analog Design Problems For Electrical Engineersb98154No ratings yet

- CMOS Answers: 1. What Is Intrinsic and Extrinsic Semiconductor?Document4 pagesCMOS Answers: 1. What Is Intrinsic and Extrinsic Semiconductor?veerugc89No ratings yet

- Four-input NAND gate design using two-input NAND gatesDocument14 pagesFour-input NAND gate design using two-input NAND gatesarammartNo ratings yet

- Ade QuestionDocument11 pagesAde QuestionClone CloneNo ratings yet

- Bwire Ans AssgDocument5 pagesBwire Ans AssgEria NalwasaNo ratings yet

- Technologies for Digital Media Midterm AssessmentDocument7 pagesTechnologies for Digital Media Midterm AssessmentDima TahaNo ratings yet

- Physical DesignDocument45 pagesPhysical DesignSameer Badachi100% (10)

- EDN Design Ideas 2006Document142 pagesEDN Design Ideas 2006chag1956100% (1)

- EE331 Lab 1 v2Document13 pagesEE331 Lab 1 v2Áo ĐenNo ratings yet

- Lab#11 EEDocument16 pagesLab#11 EEJunaid KhalidNo ratings yet

- N LMS Impedance BridgeDocument7 pagesN LMS Impedance BridgeCazzKazikNo ratings yet

- CMOS Question FN-3Document3 pagesCMOS Question FN-3alokjadhavNo ratings yet

- SANDISKDocument3 pagesSANDISKrAM100% (3)

- Lab 7 - Voltage MultiplierDocument2 pagesLab 7 - Voltage Multiplieregaupc2123No ratings yet

- Microwave - Experiment 5 - Coupler DesignDocument27 pagesMicrowave - Experiment 5 - Coupler DesignbangntsuNo ratings yet

- Physical DesignDocument45 pagesPhysical DesignMalka RavikrishnaNo ratings yet

- Questions On Signals and AmplifiersDocument30 pagesQuestions On Signals and Amplifierskibrom atsbhaNo ratings yet

- CMOS Integrated Circuits Layout Design (ELEC212Document15 pagesCMOS Integrated Circuits Layout Design (ELEC212khan aliNo ratings yet

- EE 330 Exam 2 Spring 2015 PDFDocument10 pagesEE 330 Exam 2 Spring 2015 PDFeng2011techNo ratings yet

- Subject Name: Basic Electrical and Electronics Engineering / Ge 2151Document3 pagesSubject Name: Basic Electrical and Electronics Engineering / Ge 2151Gokul ChandrasekaranNo ratings yet

- Flash ADC Design Challenges and MethodologyDocument15 pagesFlash ADC Design Challenges and MethodologyJagadeep KumarNo ratings yet

- Midterm 07Document10 pagesMidterm 07ubertomeNo ratings yet

- Expt Write-UpDocument37 pagesExpt Write-UpTushar PatwaNo ratings yet

- Lecture - MOS & MOSFET-1Document21 pagesLecture - MOS & MOSFET-1Kartika MunirNo ratings yet

- Design of Fully Integrated Digitally Controlled CMOS Voltage AmplifierDocument10 pagesDesign of Fully Integrated Digitally Controlled CMOS Voltage AmplifierHarsh GuptaNo ratings yet

- Vlsi 2-Marks With AnswerDocument23 pagesVlsi 2-Marks With Answerk poornimaNo ratings yet

- A Low-Cost Impedance Meter Using a PC Sound CardDocument4 pagesA Low-Cost Impedance Meter Using a PC Sound Carddavorko_tNo ratings yet

- Wyatt Na Ddg12Document6 pagesWyatt Na Ddg12Antonio BergnoliNo ratings yet

- MOS Integrated Circuit DesignFrom EverandMOS Integrated Circuit DesignE. WolfendaleNo ratings yet

- Easy(er) Electrical Principles for General Class Ham License (2015-2019)From EverandEasy(er) Electrical Principles for General Class Ham License (2015-2019)Rating: 5 out of 5 stars5/5 (1)

- Easy(er) Electrical Principles for General Class Ham License (2019-2023)From EverandEasy(er) Electrical Principles for General Class Ham License (2019-2023)No ratings yet

- Stem: Science, Technology, Engineering and Maths Principles Teachers Pack V11From EverandStem: Science, Technology, Engineering and Maths Principles Teachers Pack V11No ratings yet

- Stem: Science, Technology, Engineering and Maths Principles V11From EverandStem: Science, Technology, Engineering and Maths Principles V11No ratings yet

- Active LoadDocument69 pagesActive LoadVijay P. LabdeNo ratings yet

- BF511Document7 pagesBF511madooNo ratings yet

- ECE315 / ECE515: - Common Source Amplifier - MOSFET Amplifier DistortionDocument27 pagesECE315 / ECE515: - Common Source Amplifier - MOSFET Amplifier DistortionSHAIK MUSTHAFANo ratings yet

- 3 Analog Electronics Lab PDFDocument4 pages3 Analog Electronics Lab PDFjeyepuvevNo ratings yet

- EC8361 - Analog and Digital Circuits Laboratory Manual - by LearnEngineering - inDocument82 pagesEC8361 - Analog and Digital Circuits Laboratory Manual - by LearnEngineering - inPavithra PrakashNo ratings yet

- Chapter 9Document27 pagesChapter 9hessa 2001No ratings yet

- Single-Stage Amplifiers: EE215A B. Razavi Fall 14 HO #2 EE215A B. Razavi Fall 14 HO #2Document6 pagesSingle-Stage Amplifiers: EE215A B. Razavi Fall 14 HO #2 EE215A B. Razavi Fall 14 HO #2SiddharthJainNo ratings yet

- TK13A65U: Switching Regulator ApplicationsDocument6 pagesTK13A65U: Switching Regulator ApplicationsBruno SoutoNo ratings yet

- DEE 20023 SEMICONDUCTOR DEVICES SESI II 2021/2022 FET AMPLIFIERDocument14 pagesDEE 20023 SEMICONDUCTOR DEVICES SESI II 2021/2022 FET AMPLIFIERmbagavan 0712No ratings yet

- 21EEL305-ASP-Lab ManualDocument51 pages21EEL305-ASP-Lab ManualShivakumar 2108No ratings yet

- Electronics Circuit Lab ManualDocument50 pagesElectronics Circuit Lab ManualkrajenderreddyNo ratings yet

- AP7201Document8 pagesAP7201Anala MNo ratings yet

- Laboratory Manual Cadence Tste80 07Document26 pagesLaboratory Manual Cadence Tste80 07chetan_bec2834No ratings yet

- Discrete MOSFET AmplifiersDocument43 pagesDiscrete MOSFET Amplifiersmaddineni vagdeviNo ratings yet

- Osmania University BE 2/4 Electronic Devices Lab ManualDocument88 pagesOsmania University BE 2/4 Electronic Devices Lab ManualAbdulShehzadNo ratings yet

- High Speed N-Channel Dual JFET for Differential Amplifiers (SST440/441Document2 pagesHigh Speed N-Channel Dual JFET for Differential Amplifiers (SST440/441汤强No ratings yet

- The MOSFET AmplifierDocument135 pagesThe MOSFET AmplifierRodrigo WilliamsNo ratings yet

- Csa PDFDocument79 pagesCsa PDFAniruddh SharmaNo ratings yet

- BEEE 2333 - Lab 3 Common Source JFET AmplifierDocument9 pagesBEEE 2333 - Lab 3 Common Source JFET AmplifierDammahom LuriahkNo ratings yet

- Analog Circuit Design NotesDocument16 pagesAnalog Circuit Design NotesitsnirosNo ratings yet

- MPF102Document9 pagesMPF102radioscribdNo ratings yet

- Bf245a B C - 2Document12 pagesBf245a B C - 2Marius MircescuNo ratings yet

- 2.4 GHZ LNA Filter DesingDocument4 pages2.4 GHZ LNA Filter DesingNikhilAKothariNo ratings yet

- Silicon Junction FET characteristicsDocument1 pageSilicon Junction FET characteristicsjoelpalzaNo ratings yet

- J212 PDFDocument7 pagesJ212 PDFRicky CoxNo ratings yet

- RFIC Notes PDFDocument145 pagesRFIC Notes PDFramanjulun100% (1)

- 6.012 DP: CMOS Integrated Differential Amplifier: Tony Hyun KimDocument9 pages6.012 DP: CMOS Integrated Differential Amplifier: Tony Hyun Kimanil kumarNo ratings yet

- Electronics Circuits MOSFET and Its AnalysisDocument31 pagesElectronics Circuits MOSFET and Its AnalysisSiddhasen PatilNo ratings yet