Professional Documents

Culture Documents

July 2008

Uploaded by

Sathisha0 ratings0% found this document useful (0 votes)

7 views1 pageQp3

Original Title

july-2008

Copyright

© © All Rights Reserved

Available Formats

PDF or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentQp3

Copyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

0 ratings0% found this document useful (0 votes)

7 views1 pageJuly 2008

Uploaded by

SathishaQp3

Copyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

You are on page 1of 1

Save trees use e-Question Paper Go green

DOWNLOAD THIS FREE AT www.vturesource.com

usN” | ong;

‘Third Semester B.E. Degree Examinat

Logic Design

in, June / July 0:

iene: 3 hee Max.

Note: Answer any FIVE full questions, choosing atteast wo frgiiPeacWRGA.

1a. What are universal gates? Implement the following function using univeti gate) only

(A+B twrks)

b. Simplify the following using K — mapP(A.B,C.D)= ATIC + AD RD + Cg aC + AB

(os Maris)

©. What are the drawbacks of Kemap? Simplify the folk pression using

Quine ~ Me Clusky Method. F(A, B,C,D) = 2(1,2,8,9,10,12,13,14). (40 Marks)

2a Show that using a 3 — to ~ 8 decoder and multi ~input O} flowing Boolean

expressions ean be realized.

F,(A.B,C)= Em(0,4,6),

*3(A,B,C) = Em(0,5), Fy ) = SA(1,23,7). (04 marks)

b. Design Decimal - to ~ BCD encoder? (os marks)

©. What are the different types of PLD’s and impleme; segment decoder usin PLA?

‘08 Maris)

d. Write a verilog code for 4: 1 multiplexer using case st {04 Marks)

“15 in 2°s complement.

3 a. i) Perform 8 ~ bit addition of the decimal num!

8 and + 65 in 2's complement

(06 Marks)

b._ i) Find the binary addition of (7510),0 andl bit numbers,

ii) Find the binary subtraction of (200),o 1 sing 8— bit numbers. (10 Marks)

« the binary Adder ~ subtractes example. (04 Marks)

4a Schmitt trigger? Explain S sfer characteristic. co marks)

>. Explain the different types of flip yvith their truth table. Also explain the race ~

around condition in a flip flop.

¢. Differentiate between combi 3d sequential circuit (10 Marks)

5a. a in detail and give its timing diagram. (10 Marks)

b y oa fr using JK flip flop. (10 Maris)

6 a Explain Moore model thesis table and also obtain the cigcuit diagram for

Moore model. <10 Marks)

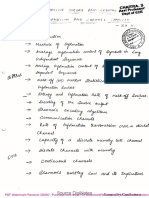

b. Desig an asynebrono ial logic circuit for state warsition diagram shown in Fig.

60),

ee

Fig. Q 6(b) a0 Marks)

7 ie laddez? Explain the binary ladder with a digital input of 1000. (10 Marks)

= bit simultaneous A/D converter. 10 Marks)

8 a circuit diagram, explain the operation of the CMOS NAND gate. (10 Maris)

EDIBIe 2 2— input NAND gate TTL with Totem — pole output witha neat diagram, |

‘a Man

BRANCHES | ALL SEMESTERS | NOTES | QUESTON PAPERS | LAB MANUALS

A Vturesource Go Green initiative

You might also like

- July 2011Document2 pagesJuly 2011SathishaNo ratings yet

- Module 4Document27 pagesModule 4SathishaNo ratings yet

- Unit 3photoshopDocument23 pagesUnit 3photoshopSathishaNo ratings yet

- Module 2BDocument31 pagesModule 2BSathishaNo ratings yet

- Module 3BDocument21 pagesModule 3BSathishaNo ratings yet

- Basic Electronics & Communication Engineering: JBOS 18.10.2021 / EC 30.10.2021Document5 pagesBasic Electronics & Communication Engineering: JBOS 18.10.2021 / EC 30.10.2021SathishaNo ratings yet

- First Semester - BE - Degree Examination Subject Title: Basic Electrical EngineeringDocument3 pagesFirst Semester - BE - Degree Examination Subject Title: Basic Electrical EngineeringSathishaNo ratings yet

- V Sem BCA QBDocument42 pagesV Sem BCA QBSathishaNo ratings yet

- Toyota Technical Training Institute: Entrance Examination: Sample Question PaperDocument4 pagesToyota Technical Training Institute: Entrance Examination: Sample Question PaperSathishaNo ratings yet

- Subject Title - Basic Electrical Engineering: First Semester BE Degree ExaminationDocument3 pagesSubject Title - Basic Electrical Engineering: First Semester BE Degree ExaminationSathishaNo ratings yet

- Cover Page: Template For The Unisys Innovation Program Student Technical Contest-Preliminary Project Plan and AbstractDocument3 pagesCover Page: Template For The Unisys Innovation Program Student Technical Contest-Preliminary Project Plan and AbstractSathishaNo ratings yet

- Half Yearly (First) Progress Report of Ph.D. Candidate.: As Detailed Given BelowDocument2 pagesHalf Yearly (First) Progress Report of Ph.D. Candidate.: As Detailed Given BelowSathishaNo ratings yet

- Itc 1 PDFDocument65 pagesItc 1 PDFSathishaNo ratings yet

- STTP June20 PDFDocument1 pageSTTP June20 PDFSathishaNo ratings yet

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)