Professional Documents

Culture Documents

Untitled

Untitled

Uploaded by

Victor Richard0 ratings0% found this document useful (0 votes)

10 views16 pagesCopyright

© © All Rights Reserved

Available Formats

PDF or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

0 ratings0% found this document useful (0 votes)

10 views16 pagesUntitled

Untitled

Uploaded by

Victor RichardCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

You are on page 1of 16

6

os)

a

oO

ey

(2

(3)

(60)

United States Patent

Casady et al.

SELF-AL

NED TRANSISTOR AND DIODE,

IES IN SILICON CARBIDE

OF SELECTIV!

CTIVE IMPLANTATION

Inventors: Jeffrey B. Casady,

(US); Geoffrey B. Carter, Sahllo, MS

(US); Yaroslav Koshk, Starkville, MS

(US); Michael S. Mazzola, Starkville,

MS (US); Igor Sankin, Starkville, MS

(vs)

Starkville, MS

Assignee: Mississippt State Unlversity-Researeh

and Technology Corporation (RTO),

Us

Mississippi State, MS

Notice: Subject to any disclaimer, the term ofthis

patent is extended or adjusted under 35

USC. I54tb) by O days

Appl. No.

Filed:

10/193,108

Jul. 12, 2002

Prior Publication Data

US 2003041195 AL Feb, 20,2008,

Related U.S. Application Data

Provisional application No. 607304423, filed on Jul. 12,

‘US00676778382

US 6,767,783 B2

(10) Patent No.

(5) Date of Patent: Jul. 27, 2004

G1) Int HOLL 21/8239

(2) US.CL “438/234; 438/235; 438,256;

438/237, 438/238

(58) Fleld of Search 438/285-238

6s References Cited

US. PATENT BOCUMENTS

Soom A” 4200 Se

asset bt ame2 Aaa

* cited by examiner

Primary Esaminer—Loog, Phase

(74) Attorney, Agent, or Firm—Piper Rudnick L.LLPs

even B. Kelber

6 ABSTRACT

‘A method of making vertical diodes and transistors in SiC is

provided. The method avcording to the invention uses a

‘mask (et, 2 mask that has been previously used for etching

Features into the device) for selective epitaxial growth or

selective ion implantation. In this manner, the gate and base

regions of sale induction tansisors and bipolar junction

{ransistors can be formed ina sell-aligned process. Ametod

of making planar diodes and planar edge termination struc

tures (eg. guard rings) i aso provided.

27 Claims, 8 Drawing Sheets

CLLLLLLL LLL LLL LLL LTT LLL LL

U.S. Patent Jul. 27, 2004 Sheet 1 of 8 US 6,767,783 B2

Ge] ies] 18 |

FIG.1A

0 2

FIG.1C

U.S. Patent Jul. 27, 2004 Sheet 2 of 8 US 6,767,783 B2

U.S. Patent Jul. 27, 2004 Sheet 3 of 8 US 6,767,783 B2

wf =] (pf

{

i

SS. a

3 F if

fa at A

2B

FIG.3B

q "7

FIG.3C

U.S. Patent Jul. 27, 2004 Sheet 4 of 8 US 6,767,783 B2

FIG.4C

U.S. Patent Jul. 27, 2004 Sheet 5 of 8 US 6,767,783 B2

U.S. Patent Jul. 27, 2004 Sheet 6 of 8 US 6,767,783 B2

g

18

is

EJ

FIG.6A

a | 88 ® | 86 2 EJ

a

FIG.6B

iC

C

Ta

U.S. Patent Jul. 27, 2004 Sheet 7 of 8 US 6,767,783 B2

108 108

Yio# | wm | tot)

102

Po

FIG.7A

FIG.7B

FIG.7C

US 6,767,783 B2

Sheet 8 of 8

Jul. 27, 2004

US. Patent

6'9l4

<7 LUI II

Vee

Sfb On

Ov Onl Ov Om

CLR RRR RRR

zt:

LCR

KOs, Da WW

el $ gel

SN

US 6,767,783 B2

1

SELF-ALIGNED TRANSISTOR AND DIODE

TOPOLOGIES IN SILICON CARBIDE

THROUGH THE USE OF SELECTIVE

EPITAXY OR SELECTIVE IMPLANTATION

(CROSS-REFERENCE TO RELATED

"APPLICATIONS,

‘This application claims priority from US. Provisional

Application Serial No. 60/304,423 fled Jul 12, 2001. The

entirety of tha provisional application is incorporated her

by reference,

BACKGROUND OF THE INVENTION

1. Field of the Invention

This invention applies to advanced SiC deviees for high-

speed, high-power applications such as compact efficient

power amplifiers im radar transmitters in airborne and

‘ground-based radar systems and high-power density switeh-

‘ng applications such as high-vollage DC-DC converters and

2, Background of the Technology

‘Two of the most common types of vertical SiC poswer

teunsistors are the Static Haduetion Transistor (SIT) and the

Bipolar Junction Transistor (BIT). These devices are

described in more detail below.

‘The SIT is a vertical MESFET or JFET type device

‘wherein the gates ae close together resulting in space charge

limited curent conduction. The device characteristics look

much like triode rather than a conventional FET. The

advantages of using an SIT area result of its high vollage

fain and good impedance characteristics, which reslt in &

high power gain. In SiC, the device performance is further

‘enhanced by the high savration velocity (e 8. 1.5-2x that of

Si) and high electri field breakdewa siength (6. 10 thal

‘of Si), Based on SiC’s high thermal conductivity and suit

ability for use at high-emperatures, a silicon carbide SIT

‘device should produce substantial improvements over Si

technology.

‘An SIT can have either PN or Schottky gates

Aadlitionally, current in an SIT is controlled by the electric

field applied to the dean and gate regions. Most SITs in SiC

have used Schottky metal gates. Se, for example, U.S. Pat.

Nos. 5,945,701; 5,903,020, 5,807,773; and 5,0123547. See

also Henning et al, “A Novel Self Aligned Fabrication

Process for Microwave Static Induction Transistors in Sili-

‘con Carbide” Electton Device Letters, 21, 578-580 (

Using a Schottky gate in an SIT or MESFET will typically

Timit the junction temperature 10 about 250° C. because

leakage cirents exponentially increase through the Schot-

tky gate with ineeasing temperatuce,

‘Mach of the early work on the SIT in SiC focused on

‘developing highly uniform, highly controlled epitaxy layers

forthe drift and channel regions, The early successes of the

device were direct result of improved epitaxy vniformity

through the wse of wafer rotation and a better understanding

‘of epitaxial growth mechanisms.

‘Most of the fabrication difculies cureenly being expe=

rienced in low-cost volume manufacturing ean be traced

level processing steps. Fis, the eurrent-

iy ofthe SIT is highly sensitive tothe width

‘of the channel regions, which i se by patterned reactive ion

‘etching (RIE). However, after RIE, itis usally necessary to

perform theemal oxidation in order to form a high

You might also like

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (842)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5807)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1091)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Iit2006 0175 4Document3 pagesIit2006 0175 4Victor RichardNo ratings yet

- JP 35 92 395Document4 pagesJP 35 92 395Victor RichardNo ratings yet

- IIT2002 Tabil IonDocument3 pagesIIT2002 Tabil IonVictor RichardNo ratings yet

- PCGA200T65NF8Document1 pagePCGA200T65NF8Victor RichardNo ratings yet

- Conference Program PCIM Europe 2022: Tuesday, 10 May 2022Document35 pagesConference Program PCIM Europe 2022: Tuesday, 10 May 2022Victor RichardNo ratings yet

- ElectronicsDocument18 pagesElectronicsVictor RichardNo ratings yet

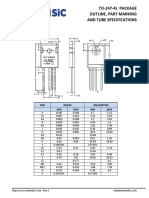

- TO-247-4L Outline, Marking and Tube SpecificationsDocument2 pagesTO-247-4L Outline, Marking and Tube SpecificationsVictor RichardNo ratings yet

- Stgya 50 H 120 DF 2Document15 pagesStgya 50 H 120 DF 2Victor RichardNo ratings yet

- Generic FPCN22966XVDocument3 pagesGeneric FPCN22966XVVictor RichardNo ratings yet

- NXH450N65L4Q2Document1 pageNXH450N65L4Q2Victor RichardNo ratings yet