Professional Documents

Culture Documents

Ic 555 Astable Circuit: Theory

Uploaded by

SYEDMOOSA RAZAOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Ic 555 Astable Circuit: Theory

Uploaded by

SYEDMOOSA RAZACopyright:

Available Formats

IC 555 ASTABLE CIRCUIT

THEORY

IC 555 timer is an analog IC used for generating accurate time delay or oscillations. The

entire circuit is usually housed in an 8-pin package as specified in figures 1 & 2 below. A series

connection of three resistors inside the IC sets the reference voltage levels to the two

2 1

comparators at V and V , the output of these comparators setting or resetting the flip-

3 CC 3 CC

flop unit. The output of the flip-flop circuit is then brought out through an output buffer stage.

In the stable state the 𝑄¯ output of the flip-flop is high (ie Q low). This makes the output (pin 3)

low because of the buffer which basically is an inverter.The flip-flop circuit also operates a

transistor inside the IC, the transistor collector usually being driven low to discharge a timing

capacitor connected at pin 7. The description of each pin s described below,

Pin 1: (Ground): Supply ground is connected to this pin.

Pin 2: (Trigger): This pin is used to give the trigger input in monostable multivibrator.

When trigger of amplitude greater than (1/3)Vcc is applied to this terminal

circuit switches to quasi-stable state.

Pin 3: (Output)

Pin 4 (Reset): This pin is used to reset the output irrespective of input. A logic low

at this pin will reset output. For normal operation pin 4 is connected to Vcc.

Pin 5 (Control): Voltage applied to this terminal will control the instant at which the

comparator switches, hence the pulse width of the output. When this pin is not

used it is bypassed to ground using a 0.01μF capacitor.

Pin 6 (Threshold): If the voltage

applied to threshold terminal is

greater than (2/3)VCC, upper

comparator switches to +Vsat

and flip-flop gets reset.

Pin 7: (Discharge): When the output is

low, the external capacitor is

discharged through this pin

Figure 2: IC 555 pin diagram

Pin 8 (VCC): The power supply pin

Figure 1: IC 555 Functional block diagram

MULTIVIBRATOR

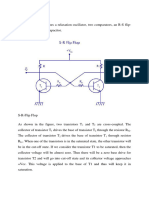

One popular application of the 555 timer IC is as an astable multivibrator or clock

Circuit. Figure 3 shows an astable circuit built using 2 external resistors and a capacitor to set

the timing interval of the output signal. Capacitor C charges toward VCC through external

2

resistors RA and RB. Referring to figure, the capacitor voltage rises until it goes above V .

3 CC

This voltage is the threshold voltage at pin 6, which drives comparator 1 to trigger the flip-

flop(𝑄 low 𝑄¯ high) so that the output at pin 3 goes low. In addition, the discharge transistor is

driven on, causing the output at pin 7 to discharge the capacitor through resistor RB. The

1

capacitor voltage then decreases until it drops below the trigger level V . The flipflop is

3 CC

triggered so that the output goes back high and the discharge transistor is turned off, so that the

capacitor can again charge through resistors RA and RB towards VCC.

CIRCUIT DIAGRAM

Figure 3 Astable multivibrator circuit using IC 555

BREADBOARD CIRCUIT

MULTISIM CIRCUIT

You might also like

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- 555 Timer IC-Block Diagram-Working-Pin Out Configuration-Data SheetDocument13 pages555 Timer IC-Block Diagram-Working-Pin Out Configuration-Data SheetΔημητριος ΣταθηςNo ratings yet

- Experiment No: 14 Astable Multivibrator Using Ic 555Document3 pagesExperiment No: 14 Astable Multivibrator Using Ic 555AmalAugustineNo ratings yet

- Multi VibratorDocument6 pagesMulti VibratorAhie CherianNo ratings yet

- IC555 TimerDocument8 pagesIC555 TimerRaflysyah PutraNo ratings yet

- 555 TimerDocument3 pages555 TimerchandrakanthNo ratings yet

- Multivibrator CircuitsDocument11 pagesMultivibrator CircuitsSatyaki ChowdhuryNo ratings yet

- University of Engineering and Technology, Lahore Department of Electrical EngineeringDocument5 pagesUniversity of Engineering and Technology, Lahore Department of Electrical EngineeringMuhammad SameerNo ratings yet

- University of Engineering and Technology, Lahore Department of Electrical EngineeringDocument5 pagesUniversity of Engineering and Technology, Lahore Department of Electrical EngineeringMuhammad SameerNo ratings yet

- Multivibrador Com Ci 555Document11 pagesMultivibrador Com Ci 555joselito1juniorNo ratings yet

- Lab#10: Design and Study of IC 555 Multivibrator Circuits (2 Turns)Document11 pagesLab#10: Design and Study of IC 555 Multivibrator Circuits (2 Turns)Ayushman ChoudharyNo ratings yet

- 555 Timer: by D.V.Kamat, Faculty Department of E&C Engg., MITDocument21 pages555 Timer: by D.V.Kamat, Faculty Department of E&C Engg., MITRupsa SahaNo ratings yet

- Lic Eec-501 Notes Unit5 Iftm UniversityDocument14 pagesLic Eec-501 Notes Unit5 Iftm UniversitySougata GhoshNo ratings yet

- IC-Applications U4Document21 pagesIC-Applications U4kavithavenkatesanNo ratings yet

- The Important Features of The 555 Timer AreDocument7 pagesThe Important Features of The 555 Timer ArePathella SudhakarNo ratings yet

- 555 Timer As Monostable MultivibratorDocument5 pages555 Timer As Monostable MultivibratorDarshan BhansaliNo ratings yet

- 3.1555 TIMER:: Schematic SymbolDocument10 pages3.1555 TIMER:: Schematic SymbolnagpradasNo ratings yet

- A Mono Stable Multi Vibrato 1Document4 pagesA Mono Stable Multi Vibrato 1Noemi CaluzaNo ratings yet

- Experiment No.4: FM Using 555 IcDocument3 pagesExperiment No.4: FM Using 555 IcSree DhanyaNo ratings yet

- LIC Mod 2Document15 pagesLIC Mod 2Sona PrakashNo ratings yet

- List The Features of 555 TimersDocument3 pagesList The Features of 555 TimersDivyesh DivakarNo ratings yet

- IC 555 Multivibrator CircuitsDocument11 pagesIC 555 Multivibrator CircuitsKaran YadavNo ratings yet

- 555 Timer Integrated CircuitDocument8 pages555 Timer Integrated CircuitTalha WaqarNo ratings yet

- UNIT-4 Special Ics The 555 Timer IcDocument10 pagesUNIT-4 Special Ics The 555 Timer IcVerloves LoveNo ratings yet

- SE/NE 555 Timer. It Is Basically A Monolithic Timing Circuit That Produces Accurate and Highly Stable Time Delays orDocument12 pagesSE/NE 555 Timer. It Is Basically A Monolithic Timing Circuit That Produces Accurate and Highly Stable Time Delays orEFraim Manzano FranciscoNo ratings yet

- Integratedelectronics (Unit2) 555 TIMER ASTABLE MONOSTABLE MVDocument5 pagesIntegratedelectronics (Unit2) 555 TIMER ASTABLE MONOSTABLE MVYogeshwaranNo ratings yet

- Core JavaDocument11 pagesCore JavaGangadharNo ratings yet

- IC 555 TimerDocument6 pagesIC 555 Timeraditya pandeyNo ratings yet

- 555 Timer IC: The Important Features of The 555 Timer AreDocument5 pages555 Timer IC: The Important Features of The 555 Timer AreChara GalaNo ratings yet

- Operation 555 Timer/OscillatorDocument7 pagesOperation 555 Timer/OscillatoryuvakiraniNo ratings yet

- Theory:The 555 Timer Configured For Monostable OperationDocument3 pagesTheory:The 555 Timer Configured For Monostable OperationkumararguruNo ratings yet

- Timers PDFDocument43 pagesTimers PDFDeepak S SNo ratings yet

- ME 455/555 - Lab 2 - 555 TimersDocument10 pagesME 455/555 - Lab 2 - 555 TimersGustavo KernNo ratings yet

- Timer 555 - ManualDocument20 pagesTimer 555 - ManualXen XeonNo ratings yet

- Ic Applications Lab NewDocument12 pagesIc Applications Lab NewSandy RonaldoNo ratings yet

- Monostable MutlivibratorDocument4 pagesMonostable MutlivibratorHarshal Paymode100% (1)

- Introduction To IC 555 TimerDocument66 pagesIntroduction To IC 555 TimermuraliNo ratings yet

- Opamp Applicationpart30Document31 pagesOpamp Applicationpart30KUNTALA DASNo ratings yet

- Lab 10555 TimerDocument10 pagesLab 10555 Timermanaj_mohapatra2041No ratings yet

- Monostable MultivibratorDocument4 pagesMonostable MultivibratorSakshi GosaviNo ratings yet

- Principles Applications ICL7660Document10 pagesPrinciples Applications ICL7660Juan F. RamosNo ratings yet

- 555 Timer Operation With Internal CircuitDocument9 pages555 Timer Operation With Internal Circuitjanakiram473No ratings yet

- Operational AmplifierDocument10 pagesOperational AmplifierSalman AliNo ratings yet

- Astable Multivibrator Using 555 TimerDocument12 pagesAstable Multivibrator Using 555 TimerΔημητριος ΣταθηςNo ratings yet

- ODL Lab7 2018EE69Document7 pagesODL Lab7 2018EE69Ali MohsinNo ratings yet

- 555 TimerDocument28 pages555 TimerNisha Kotyan G RNo ratings yet

- 555 TimerDocument76 pages555 TimerSai Krishna KodaliNo ratings yet

- Chapter 4 TimerDocument33 pagesChapter 4 TimerLian Ai ChenNo ratings yet

- Abhijit H Jadhav (Roll No 02) (Roll No 58)Document15 pagesAbhijit H Jadhav (Roll No 02) (Roll No 58)ksooryakrishna1No ratings yet

- Design of Smart Automatic Street Light SystemDocument5 pagesDesign of Smart Automatic Street Light SystemSatkar AgrawalNo ratings yet

- 555 Timer PDFDocument76 pages555 Timer PDFronaldo19940% (1)

- 6.1 IC555 TIMER: Circuit ComponentsDocument8 pages6.1 IC555 TIMER: Circuit ComponentsManish PradhanNo ratings yet

- 555-Timer Class NotesDocument1 page555-Timer Class NotesPraveen KumarNo ratings yet

- 555 TimerDocument11 pages555 Timersenpaixd0110No ratings yet

- 1 Ic 555Document6 pages1 Ic 555Harish PatilNo ratings yet

- AstableDocument4 pagesAstableezhil 1No ratings yet

- Integrated Circuits:) of Flip-Flop ThroughDocument13 pagesIntegrated Circuits:) of Flip-Flop ThroughShubh MishraNo ratings yet

- MonostableDocument3 pagesMonostableezhil 1No ratings yet

- 555 Integrated Circuit (Timer Operation)Document5 pages555 Integrated Circuit (Timer Operation)Geet SehgalNo ratings yet

- Chapter-1 Objective: 1.1 Objective of The ProjectDocument23 pagesChapter-1 Objective: 1.1 Objective of The ProjectPrashanth CooldudeNo ratings yet

- Yamaha Ysp 2700 Ysp Cu2700Document129 pagesYamaha Ysp 2700 Ysp Cu2700boroda2410100% (1)

- PVIV Test Solution: Typical I-V Test Configuration With Optional Equipment Shown. Solar Simulator Is Sold SeparatelyDocument4 pagesPVIV Test Solution: Typical I-V Test Configuration With Optional Equipment Shown. Solar Simulator Is Sold Separatelyluciano_gularteNo ratings yet

- THARMAC GMBH INFOFOLDER CELLSPIN I+II CYTOCENTRIFUGES ENGLISCH 2019 - UnlockedDocument8 pagesTHARMAC GMBH INFOFOLDER CELLSPIN I+II CYTOCENTRIFUGES ENGLISCH 2019 - UnlockedrafaelNo ratings yet

- Speery Marine NAVIKNOT Speed Log 600Document148 pagesSpeery Marine NAVIKNOT Speed Log 600Parul MehtaNo ratings yet

- RGPV Syllabus 3rd Sem Biomedical EngineeringDocument10 pagesRGPV Syllabus 3rd Sem Biomedical Engineeringoliver senNo ratings yet

- 42LF20FRDocument28 pages42LF20FRkanakNo ratings yet

- Thesis Doc v01Document34 pagesThesis Doc v01Dummy FuzzyNo ratings yet

- Irs2092 Product InfoDocument17 pagesIrs2092 Product InfoAnderson LuizNo ratings yet

- Series DS2 Compact Valve - G1/2 FeaturesDocument9 pagesSeries DS2 Compact Valve - G1/2 FeaturesBiswanath LenkaNo ratings yet

- EM2 Lab 1Document6 pagesEM2 Lab 1Amit ChowdhuryNo ratings yet

- Network TheoremsDocument30 pagesNetwork TheoremsMohammadNo ratings yet

- 5 - Fișă Tehnică Releu de Protecţie - Ziehl - UFR1001E PDFDocument2 pages5 - Fișă Tehnică Releu de Protecţie - Ziehl - UFR1001E PDFAlexandru SuciuNo ratings yet

- شيتات محطات كهربية PDFDocument8 pagesشيتات محطات كهربية PDFhazem saeidNo ratings yet

- Electrical Circuits: Electromotive Force & Terminal Potential DifferenceDocument5 pagesElectrical Circuits: Electromotive Force & Terminal Potential DifferencePhilip MooreNo ratings yet

- Jadual Spesifikasi Ujian Peperiksaan Akhir (Teori) Kod Kursus: Ete 7014 Nama Kursus: Low Voltage Pre-Testing Semester: 3 Semester: 3Document1 pageJadual Spesifikasi Ujian Peperiksaan Akhir (Teori) Kod Kursus: Ete 7014 Nama Kursus: Low Voltage Pre-Testing Semester: 3 Semester: 3Roger JohnNo ratings yet

- Complementary Power Transistors: 4H11G (NPN) 5H11G (PNP)Document6 pagesComplementary Power Transistors: 4H11G (NPN) 5H11G (PNP)gemnsterNo ratings yet

- Led Beam 300Document12 pagesLed Beam 300Jeroen udbNo ratings yet

- Philips+40PFL3706-F7+Chassis+PL11 1Document55 pagesPhilips+40PFL3706-F7+Chassis+PL11 1Jeffer VieiraNo ratings yet

- M & I Exam Eee 207 - 201819Document4 pagesM & I Exam Eee 207 - 201819Naija RonaldoNo ratings yet

- Syntax:: Familiarization of Infinite Impulse Response (IIR) and Pole-Zero Response FiltersDocument13 pagesSyntax:: Familiarization of Infinite Impulse Response (IIR) and Pole-Zero Response FiltersNico LomaNo ratings yet

- FOTBDocument38 pagesFOTBnice hossainNo ratings yet

- Agora Doha External Pylon With LCDDocument1 pageAgora Doha External Pylon With LCDScywrenz ManaloNo ratings yet

- Manual Equipo Gd6000aDocument21 pagesManual Equipo Gd6000aGiovanni TorresNo ratings yet

- Transistor (NPN) : 1. Base 2. Emitter 3. CollectorDocument2 pagesTransistor (NPN) : 1. Base 2. Emitter 3. CollectorMyFullNo ratings yet

- A 7-21 GHZ Dual-Polarized Planar Ultrawideband Modular Antenna (Puma) ArrayDocument12 pagesA 7-21 GHZ Dual-Polarized Planar Ultrawideband Modular Antenna (Puma) ArraymaheedharNo ratings yet

- DJ-MD5 User Manual 180731Document24 pagesDJ-MD5 User Manual 180731Shin Hyun KangNo ratings yet

- Study of Resonant Microstrip Antennas On Artificial Neural NetworksDocument6 pagesStudy of Resonant Microstrip Antennas On Artificial Neural NetworksresearchparksNo ratings yet

- Article About Electronic FieldDocument4 pagesArticle About Electronic FieldMalika BellounisNo ratings yet

- High Capacity 298Wh Rechargeable Li-Ion Battery With SmbusDocument1 pageHigh Capacity 298Wh Rechargeable Li-Ion Battery With SmbusMostafa MoghariNo ratings yet

- Appendix - Antenna PROCOM-CXL-70-3LWDocument3 pagesAppendix - Antenna PROCOM-CXL-70-3LWjanNo ratings yet