Professional Documents

Culture Documents

UCC28070 300-W Interleaved PFC Pre-Regulator Design Review: Application Report

Uploaded by

Jean-Yves LAPORTEOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

UCC28070 300-W Interleaved PFC Pre-Regulator Design Review: Application Report

Uploaded by

Jean-Yves LAPORTECopyright:

Available Formats

Application Report

SLUA479B – August 2008 – Revised July 2010

UCC28070 300-W Interleaved PFC Pre-Regulator Design

Review

MIchael O'Loughlin ........................................................................ PMP - Power Supply Control Products

ABSTRACT

In higher power applications to utilize the full line power and reduce line current harmonics PFC

Pre-regulators are generally required. In these high power applications interleaving PFC stages can

reduce inductor volume and reduce input and output capacitor ripple current. This results in smaller overall

magnetic volume and filter capacitor volume increasing the converters overall power density. This is made

possible through distributing the power over two interleaved boost converters and the inductor ripple

current cancellation that occurs with interleaving, reference [5]. This application note will review the design

of a 300W two-phase interleaved power factor corrected (PFC) pre-regulator. This power converter

achieves PFC with the use of the UCC28070 interleaved PFC controller, reference [7].

1 Design Goals

The specifications for this design were chosen based on the power requirements of a medium power LCD

TV.

Table 1. Design Specifications

PARAMETER MIN TYP MAX UNITS

85 265

VIN RMS input voltage

(VIN_MIN) (VIN_MAX) V

VOUT Output voltage 390

47 Hz

Line frequency 63 Hz

(fLINE)

PF Power factor at maximum load 0.90

POUT Output power 300 W

h Full load efficiency 90%

fs Individual phase switching frequency 200 kHz

SLUA479B – August 2008 – Revised July 2010 UCC28070 300-W Interleaved PFC Pre-Regulator —Design Review 1

Copyright © 2008–2010, Texas Instruments Incorporated

Schematic www.ti.com

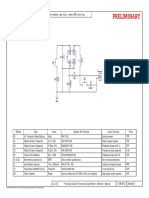

2 Schematic

UCC28070 PFC controller in a two-phase average current mode control interleaved PFC pre-regulator.

DB

L1

Vin IIN IL1 D1 VOUT

– +

DPA2

DRA

RFA

COUT

T1

1k

CFA RSA CRR RR T1

220pF

GDA ROA

RTA

DRB

RFB Q1

VCC=13V 4.7pF

DPA1

CTA 1k

CFB RSB CRR RR T2

ROB

220pF

4.7pF L2

DPB2

RA1 D2

CTB

UCC28070

RTB

1 CDR DMAX 20

IL2

2 RDM RT 19

DPB1

T2

3 VAO SS 18

RA2

4 VSENSE GDB 17

GDB

5 VINAC GND 16

12V to 21V Q2 CB4

6 IMO VCC 15

RB2

7 RSYNTH GDA 14 1.2nF

8 CSB VREF 13

CCDR

9 CSA CAOA 12

RB1

10 PKLMT CAOB 11

CZV

RIMO RZCB RZCA

RPK1

CB1 CPV CPCB CPCA

CB2 CB3 CSS RRT RDMX

RRDM

1.2nF RSYN

0.1uF 0.1uF CZCB CZCA

RZV RPK2

Figure 1. Typical Average Current Mode Interleaved PFC Pre-Regulator

2 UCC28070 300-W Interleaved PFC Pre-Regulator —Design Review SLUA479B – August 2008 – Revised July 2010

Copyright © 2008–2010, Texas Instruments Incorporated

www.ti.com Inductor Selection

3 Inductor Selection

One of the benefits of interleaved PFC boost pre-regulators is inductor ripple current reduction that is seen

at the input of the converter. The following equations and Figure 2 show the ratio of input ripple current

(ΔIIN) to individual inductor ripple current (ΔIL1) in a two-phase interleaved PFC as a function of duty cycle

(D). Because of this inductor ripple current cancellation, the designer can allow each inductor to have

more inductor ripple current than in a single stage design.

DIIN

K(D) =

DIL1

(1)

1- 2D

K(D) = if D is < 05 = 0.5

1- D

(2)

2D - 1

K(D) = if D is > 0.5

D

(3)

K(D)=DIIN/DIL1

D - Duty Cycle

Figure 2. Input Inductor Ripple Current Cancellation

The boost inductors (L1 and L2) are selected based on the maximum allowable input ripple current. In

universal applications (e.g., 85 V to 265 V RMS input) the maximum input ripple current occurs at the

peak of low line and for this design the maximum input ripple current was set to 30% of the peak nominal

input current at low line.

SLUA479B – August 2008 – Revised July 2010 UCC28070 300-W Interleaved PFC Pre-Regulator —Design Review 3

Copyright © 2008–2010, Texas Instruments Incorporated

Inductor Selection www.ti.com

The following calculations are used to select the appropriate inductance for L1 and L2. Where, variable

DPLL is the converter’s duty cycle at the peak of low line operation. Variable K(DPLL) is the ratio of input

current to inductor ripple current at the peak of low line operation. ∆IL is the boost inductor ripple current

at the peak of low line based on the converters input ripple current requirements.

VOUT - VIN_MIN 2 390V - 85V 2

DPLL = = » 0.69

VOUT 390 V

(4)

2 ´ 0.69 - 1

K(DPLL ) = = 0.55

0.69

POUT ´ 2 × 0.3 300W ´ 2 ´ 0.3

DIL = = » 3.0 A

VIN_MIN ´ h ´ K(DPLL ) 85V ´ 0.90 ´ 0.55

VIN_MIN ´ 2 ´ DPLL 85V ´ 2 ´ 0.69

L1 = L2 = = » 140 uH

DIL × f s 2.96A ´ 200 kHz

(5)

The following equation can be used to calculate total inductor RMS current (IL1_RMS and IL2_RMS).

2

2 æ VIN_MIN 2sin(q ) VOUT - VIN_MIN 2sin(q ) ö

æ POUT ö ç ´ ÷

ç 2 ÷ ç 1p L1 ´ f s VOUT ÷

IL1_RMS = IL2_RMS = ç ÷ +ç ò ÷

çç VIN_MIN ´h ÷÷ ç p 0 12 ÷

è ø ç ÷

è ø

(6)

2

2

æ 300W ö æç 85V 2sin(q ) 390V - 85V 2sin(q ) ö

÷

ç ÷ p ´

2 1 140uH ´ 200kHz 390V

IL1_RMS = IL2_RMS = ç ÷ +ç ò ÷ » 2A

çç 85V ´ 0.90 ÷÷ çç p 0 12 ÷

è ø èç ÷÷

ø

(7)

A 140-mH boost inductor from Cooper Electronic Technologies part number CTX16-18060 was chosen for

the design. The inductance during normal operation will swing from 140mH to 350mH.

L1MIN = L2MIN = 140 uH

(8)

L1MAX = L2MAX = 350 uH

(9)

The average inductance is calculated for current loop compensation purposes. This will be used in the

current loop compensation section of the application note:

L1MIN + L1MAX 140 uH + 350 uH

L1AVG = L2AVG = = = 245 uH

2 2

(10)

4 UCC28070 300-W Interleaved PFC Pre-Regulator —Design Review SLUA479B – August 2008 – Revised July 2010

Copyright © 2008–2010, Texas Instruments Incorporated

www.ti.com Output Capacitor Selection

4 Output Capacitor Selection

The output capacitor (COUT) is selected based on holdup requirements.

2 ´ POUT 2 ´ 300W

COUT ³

fLINE

= 47 Hz » 192 uF

VOUT 2 - (VOUT ´ 0.75)2 2

(390V) - (292.5V )

2

(11)

Two 100-mF capacitors were used in parallel for the output capacitor.

COUT = 200 μF

(12)

For this size capacitor the output peak to peak voltage ripple (VRIPPLE) is:

2 ´ 300W

2 ´ POUT 1 0.90

VRIPPLE = = » 14.5V

h VOUT ´ 2p ´ 2fLINE ´ COUT 390V ´ 2π ´ 2 ´ 47Hz ´ 200 μF

(13)

In addition to holdup requirements, a capacitor must be selected so that it can withstand both the

low-frequency RMS current (ICOUT_LF) and the high-frequency RMS current (ICOUT_HF). High-voltage

electrolytic capacitors generally have both low frequency (100 Hz to 120 Hz) and high frequency RMS

current ratings on their data sheets.

POUT 300W

ICOUT_LF = = » 0.604A

h VOUT 2 0.90 ´ 390V ´ 2

(14)

2

æ P 16 ´ VOUT ö 2

2

ICOUT_HF = ç OUT

ç h VOUT 6p ´ VIN_MIN 2 ÷

(

- h ÷ - ICOUT_LF )

è ø

(15)

2

æ 300W 16 ´ 390V ö 2

ICOUT_HF = ç - (0.90)2 ÷ - (0.604 ) » 1.0A

ç 0.90 ´ 390V 6p ´ 85V 2 ÷

è ø

(16)

SLUA479B – August 2008 – Revised July 2010 UCC28070 300-W Interleaved PFC Pre-Regulator —Design Review 5

Copyright © 2008–2010, Texas Instruments Incorporated

Power Semiconductor Selection (Q1, Q2, D1, D2) www.ti.com

5 Power Semiconductor Selection (Q1, Q2, D1, D2)

The selection of Q1, Q2, D1, and D2 are based on the power requirements of the design. Application note

(SLUA369), UCC28528 350-W Two Phase Interleaved PFC Pre-regulator, explains how to select power

semiconductor components for interleaved PFC pre-regulators using average current mode control

techniques, reference [4]. To meet the power requirements of this design IRFB11N50A N channel FETs

from IR were chosen for Q1 and Q2. To reduce reverse recovery losses SiC diodes CSD10060G from

CREE were chosen for the design.

Boost Diode (D1, D2) and FET (Q1, Q2) peak current (IPEAK) calculation:

A factor of 1.2 was added to the equation for added design margin.

æ POUT ´ 2 DI ö æ 300W ´ 2 2.97A ö

IPEAK = ç + L1 ÷ 1.2 = çç + ÷ 1.2 » 5.1A

ç 2 ´ VIN_MIN ´ h

è 2 ÷ø è 2 × 85V ´ 0.90 2 ÷ø

(17)

Q1 and Q2 RMS current (IDS) calculation:

POUT 300W

η 16 ´ VIN_MIN 2 0.90 16 ´ 85V 2

IDS = 2 - = 2- » 1.685A

2 ´ VIN_MIN 2 3 ´ p ´ VOUT 2 ´ 85V 2 3 ´ p ´ 390V

(18)

D1 and D2’s average current calculation (ID):

POUT 300W

ID = = » 0.39A

VOUT 2 ´ 390V

(19)

6 UCC28070 300-W Interleaved PFC Pre-Regulator —Design Review SLUA479B – August 2008 – Revised July 2010

Copyright © 2008–2010, Texas Instruments Incorporated

www.ti.com Current Sense Transformers Setup and Selection (T1, T2, DRA, DRB)

6 Current Sense Transformers Setup and Selection (T1, T2, DRA, DRB)

The current sense transformer is selected to handle IPEAK and have a peak current sense signal (IRS) of

roughly 100 mA.

NS I 5.1A

NCT = ³ PEAK = = 51

NP IRS 0.1A

(20)

For this design a current sense transformer with a turns ratio (NCT) of 50 was chosen for the design.

NCT = 50

(21)

The magnetizing inductance (LM) of the current sense transformer should be selected or designed so the

magnetizing current is less than 2% of the maximum current sense signal. The following equation

calculates the minimum LM where VS is the maximum current sense signal voltage. For this design a

current sense transformer was designed by Cooper Electronic Technologies (CTX16-18294) with a

magnetizing inductance of 8.25 mH.

VS VOUT - VIN_MIN 2 3.7V 390V - 85V 2

LM ³ ´ = ´ » 6.24mH

IPEAK VOUT 5.1A 390V

´ 0.02 ´ f s ´ 0.02 ´ 200kHz

NCT 50

(22)

LM = 8.25 mH

(23)

Selection of the current sense resistors (RSA and RSB ) is based on the peak current limit signal (VS) and

the peak current on the secondary side of the current sense transformer. A factor of 0.9 was multiplied by

the current sense signal to leave room for the 10% PWM ramp that is used to make this design more

noise immune at lighter loads.

0.9 ´ VS 0.9 ´ 3.7V ´ 50

RSA = RSB = = » 32.5 W

IPEAK 0.102A

NCT

(24)

Select a standard resistor for the design:

RS = 33.2 W

(25)

Resistor RR is used to reset the current sense transformer:

RS ´ DMAX 33.2 W × 0.97

RR ³ = ; 1 kW

1 - DMAX 1 - 0.97

(26)

Current sense transformer’s rectifying diodes (DR) need to be designed to withstand the current sense

transformers reset voltage (VR):

NP 5.1A ´ 1 kW

VR = IPEAK ´ ´ RR = ³ 103V

NS 50

(27)

SLUA479B – August 2008 – Revised July 2010 UCC28070 300-W Interleaved PFC Pre-Regulator —Design Review 7

Copyright © 2008–2010, Texas Instruments Incorporated

Current Sense Transformers Setup and Selection (T1, T2, DRA, DRB) www.ti.com

To improve noise immunity at extremely light loads, a PWM ramp with a dc offset is recommended to be

added to the current sense signals. Electrical components RTA, RTB, CTA, CTB, DPA1, DPA2, DPB1, and DPB2

form a PWM ramp that is activated and deactivated by the gate drive outputs of the UCC28070. Resistor

ROA and ROB add a DC offset to the CS resistors (RSA and RSB).

When the inductor current becomes discontinuous the boost inductors ring with the parasitic capacitances

in the boost stages. This inductor current rings through the CTs causing a false current sense signal.

Refer to the following graphical representation of what the current sense signal looks like when the

inductor current goes discontinuous. Note that the inductor current and VRSA may vary from this graphical

representation depending on how much inductor ringing is in the design when the unit goes discontinuous.

GDA

IL1

0A

VRSA

VOFF

0V

Discontinues Current Causes False Current Sense Signal

Figure 3. False Current Sense Signal

8 UCC28070 300-W Interleaved PFC Pre-Regulator —Design Review SLUA479B – August 2008 – Revised July 2010

Copyright © 2008–2010, Texas Instruments Incorporated

www.ti.com Current Sense Transformers Setup and Selection (T1, T2, DRA, DRB)

To properly select the offset (VOFF) just requires adjusting resistors ROA and ROB to add a dc offset to the

current sense resistors, that is high enough to block DRA and DRB from conducting when a false current

sense signals is present. This occurs when the inductors are operating with discontinuous inductor current

and was described above in detail. Setting the offset to 200 mV is a good starting point and may need to

be adjusted based on individual design criteria and the amount of noise and parasitic elements present in

the system.

VOFF = 0.2 V

(28)

(VVCC - VOFF )RSA (13V - 0.2V ) ´ 33.2

ROA = ROB = = » 2.1 kW

VOFF 0.2V

(29)

Select a standard resistor for the design:

ROA = 2.05 kW

(30)

(VVCC - (Vs ´ 0.1- VOFF +VDPA2 )RSA (13V - (3.7V ´ 0.1- 0.2V)+0.6V )´ 33.2

RTA =RTB = = » 2.62 kW

Vs ´ 0.1- VOFF 3.7V ´ 0.1- 0.2V

(31)

Chose a standard resistor for the design:

RTA = RTB = 2.49 kW

(32)

1

CTA = CTB = » 50 nF

RSA ´ fS ´ 3

(33)

A standard capacitor needs to be chosen for the design:

CTA = 47 nF

(34)

SLUA479B – August 2008 – Revised July 2010 UCC28070 300-W Interleaved PFC Pre-Regulator —Design Review 9

Copyright © 2008–2010, Texas Instruments Incorporated

Setting Up Peak Current Limiting (RPK1, RPK2) www.ti.com

7 Setting Up Peak Current Limiting (RPK1, RPK2)

The UCC28070 has an adjustable peak current limit comparator that can be set up by selecting RPK1 and

calculating the required RPK2. For this design to keep the reset voltage of the current sense transformer

manageable the peak current sense signal (VS) was set to 3.7 V.

VS ´ RPK1 3.7V ´ 3.65 kΩ

RPK2 = = » 5.9 kW

VREF - VS 6V - 3.7V

(35)

Converter Timing and Maximum Duty Cycle Clamp

Resistor RRT and RDMX set up converter timing and the maximum PWM duty cycle clamp:

7.5 ´ 109 W ´ Hz 7.5 ´ 109 W ´ Hz

RRT = = = 37.5 kW

fs 200 kHz

(36)

A standard resistor was selected for the design:

RRT = 37.4 kW

(37)

Resistor RDMX was selected to set the maximum duty cycle clamp (DMAX) to 0.97:

RDMX = RRT (2 ´ DMAX - 1) = 37.4 kΩ (2 ´ 0.97 - 1) = 35 k W

(38)

Chose a standard resistor for the design:

RDMX = 34.8 kW

(39)

8 Programming VOUT

Resistor RA is selected to minimize the error due to VSENSE input bias current and to minimize loading on

the power line when the PFC is disabled. Construct resistor RA from two or more resistors in series to

meet high voltage requirements. Resistor RB is sized to program the converters output voltage (VOUT).

RA = 3M W

(40)

VREF

´ RA

2 3V ´ 3MΩ

RB = = » 23.3 kW

VREF 390V - 3V

VOUT -

2

(41)

A standard resistor was chosen for the design.

RB = 23.2 kW

(42)

The resistor divider formed by RA and RB from the output voltage to the VSENSE pin also sets the over

voltage protection threshold (VOVP).

R A + RB 3MW + 23.2 kW

VOVP = 3.18V = 3.18V » 414V

RB 23.2 kW

(43)

10 UCC28070 300-W Interleaved PFC Pre-Regulator —Design Review SLUA479B – August 2008 – Revised July 2010

Copyright © 2008–2010, Texas Instruments Incorporated

www.ti.com VINAC Divider Setup

9 VINAC Divider Setup

The UCC28070 also requires sensing the line input for proper operation. This requires a divider from the

rectified line voltage to the VINAC pin of the UCC28070. For simplicity the UCC28070 was designed to

use the same resistor divider values as the VSENSE pin. Resistors RA and RB need to be the same ratio

for the VINAC voltage divider as thouse in the VSENSE voltage divider to ensure the UCC28070 controller

operates correctly. Please refer to the applications schematic for proper component placement.

10 Voltage Loop Configuration

The methodology used to compensate the voltage loop is based on the compensation methodology

developed by Lloyd Dixon. A detailed explanation of this compensation scheme written by Mr. Dixon can

be found in the 1990 Unitrode Power Supply Design SEM700, High Power Factor Switching Pre-regulator

Design Optimization, Topic 7, reference [2].

Capacitor CPV is sized to attenuate low frequency ripple to less than 3% of the voltage amplifier output

range. This will ensure good power factor and low input current harmonic distortion.

Voltage Amplifier Transconductance Amplifier gain:

gmV = 70 m S

(44)

Voltage Divider Feedback Gain:

VVREF 3V

H= = » 0.0077

VOUT 390V

(45)

Output impedance (ZO) is required to attenuate the low frequency boost capacitor output ripple (VRIPPLE) to

less than 3% of the effective voltage amplifier output range (ΔVAO). This impedance is set by properly

selecting feedback capacitor CPV:

DVAO ´ 0.03 3.2V ´ 0.03

ZO = = » 12.3 kW

VRIPPLE ´ H ´ gmV 14.5V ´ 0.0077 ´ 70 m S

(46)

1 1

CPV = = » 138nF

2p ´ 2 ´ fLINE ´ Zo 2p ´ 2 ´ 47Hz ´ 12.3kW

(47)

Choose as standard capacitor for the design:

CPV = 150 nF

(48)

SLUA479B – August 2008 – Revised July 2010 UCC28070 300-W Interleaved PFC Pre-Regulator —Design Review 11

Copyright © 2008–2010, Texas Instruments Incorporated

Voltage Loop Configuration www.ti.com

For the highest possible power factor the voltage loop crossover frequency (fCV) needs to be set based on

the following equation:

DVAO = 3.2 V

(49)

POUT 1

η j ´ 2p ´ COUT 1

fCV = H ´ gmV ´ ´ ´

DVAO VOUT 2 ´ p ´ CPV

(50)

300W

1 1

fCV = 0.0077 ´ 70m S ´ 0.90 ´ ´ » 11Hz

3.2V 2 ´ p ´ 200mF ´ 390V 2 ´ p ´ 150nF

(51)

Voltage compensation resistor RZV is then sized to put a pole at the converter’s voltage loop crossover

frequency:

1 1

R ZV = = » 96.4 kW

2p ´ fCV ´ CPV 2p ´ 10.6Hz ´ 150nF

(52)

Select a standard resistor for the design:

R ZV = 100 kW

(53)

Voltage compensation capacitor CZV is used to increase the dc gain of the voltage loop and gives some

added phase margin before crossover. The zero added to the voltage loop needs to be set at 1/10th the

crossover frequency.

1 1

CZV = = » 1.5 mF

fCV 11Hz

2p ´ ´ R ZV 2p ´ ´ 100 kW

10 10

(54)

12 UCC28070 300-W Interleaved PFC Pre-Regulator —Design Review SLUA479B – August 2008 – Revised July 2010

Copyright © 2008–2010, Texas Instruments Incorporated

www.ti.com Voltage Loop Configuration

The following equations can be used to estimate voltage compensation network gain, voltage loop power

stage gain and voltage loop gain. These equations can also be used to graphically check loop stability.

Voltage Compensation Network Gain (GCV(f)) as function of frequency:

DVVAO j ´ 2p ´ f ´ R ZV ´ CZV +1

GCV (f ) = = H ´ gmV ´

DVOUT æ ´ CZV ´ CPV ö

(j ´ 2p ´ f ´ (CZV + CPV ))ç j ´ 2p ´ f ´C RZV +1÷

è ZV +CPV ø

(55)

Voltage Loop Power Stage Gain (GPSV(f)) as function of frequency:

POUT æ 1 ö

ç ÷

DVOUT η è j ´ 2p ´ f ´ COUT ø

GPSV (f ) = = ´

DVVAO DVAO VOUT

(56)

Voltage Loop Gain in dB (TvdB(f)) as function of frequency:

TvdB( f ) = 20log (GPSV ( f ) ´ GCV ( f ) )

(57)

Figure 4 shows the theoretical loop gain (TvdB(f)) as a function of frequency and Figure 5 shows the

theoretical loop phase (qv(f)) as a function of frequency. From these figures it can be observed that the

voltage loop crossed over at roughly 9 Hz with a phase margin of 60 degrees. Compensating the voltage

loop is not an exact science and should be checked with a network analyzer and adjusted if necessary.

90 90

90 90

60

75

30

60

TvdB ( f) 0

qv( f)45

30

30

60

- 90 15

90 3

1 10 100 1 .10 0

1 f 3 0 3

1´10 1 10 100 1 .10

1 f 3

1´10

Figure 4. Theoretical Voltage Loop Gain (TvdB(f)) Figure 5. Theoretical Voltage Loop Phase (qv(f))

SLUA479B – August 2008 – Revised July 2010 UCC28070 300-W Interleaved PFC Pre-Regulator —Design Review 13

Copyright © 2008–2010, Texas Instruments Incorporated

Current Loop Compensation www.ti.com

11 Current Loop Compensation

Setting up the current synthesizer is accomplished by correctly selecting RSYN:

The inductor used in this design example swings from 350 mH to 140 mH from no load to maximum load.

When calculating RSYN the highest inductance value (L1MAX) should be used.

RB 23.2 kW

NCT ´ L1MAX 50 ´ 350 mH ´

R A + RB 3 MW + 23.2 kW » 40.5 kW

RSYN = =

RS ´ 0.1 nF 33.2W ´ 0.1nF

(58)

Chose a standard resistor:

RSYN = 38.3 kW

(59)

The IMO resistor needs to be set with the following equation to center the digitized multiplier for universal

line applications:

17 ´ 10-6 A ´ VINAC (VVAOMAX - 1V ) 17 ´ 10-6 A ´ 0.76V (5V - 1V )

IMO = = » 130 m A

K VFF 0.398V 2

(60)

0.76V ´ (R A + RB ) 0.76V ´ (3MW + 23.2kW)

VI = = » 70V

RB ´ 2 23.2kW ´ 2

(61)

1.1´ POUT ´ 2 1 1.1 300W 2 1

V2 = ´ ´ RS = ´ ´ ´ 33.2W » 2.458V

2 ´h ´V 1 NCT 2 0.92 ´ 72V 50

(62)

V2 2.458 V

RIMO = = » 18.9kW

IMO 130 m A

(63)

Choose a standard resistor close to the calculated value:

RIMO = 19.6 kW

(64)

th th

The current loop in a PFC converter is generally designed to crossover at between 1/10 and 1/6 the

converter’s switching frequency. The current loop in this design example is going to be designed to

crossover at 1/10th of the single stage’s switching frequency. In order to properly compensate the current

loop it is required to calculate the current loop's power stage gain (GPS) at the current loop's crossover and

properly select passive components RZC1/2, CZC1/2 and CPC1/2:

1 1

VOUT ´ RS ´ 390 V ´ 33.2W ´

NCT 50

GPSC = = » 2.1

fs 200 kHz

2p ´ ´ L1AVG ´ VRAMP 2p ´ ´ 245 mH ´ 4.0V

10 10

(65)

14 UCC28070 300-W Interleaved PFC Pre-Regulator —Design Review SLUA479B – August 2008 – Revised July 2010

Copyright © 2008–2010, Texas Instruments Incorporated

www.ti.com Current Loop Compensation

Variable gmC is the current amplifier Transconductance Current Amplifier Gain.

gmC = 100 m S

(66)

1 1

R ZC1 = R ZC2 = = = 4.8 kW

gmC ´ GPSC 100 m S ´ 2.1

(67)

1 1

CZC1 = CZC2 = = » 1.7nF

fs 200 kHz

2p × R ZC 2p ´ 4.8 kW

10 10

(68)

1 1

CPC1 = CPC2 = = » 333 pF

fs 200 kHz

2p ´ R ZC 2p ´ 4.8 kW

2 2

(69)

Standard components close to the calculated values are chosen for the current loop compensation:

R ZC1 = 4.02 kW, CZC1 = 2.2 nF, CPC1 = 330 pF

(70)

Graphically Check Theoretical Current Loop Gain (TcdB(f)) and loop phase (qc(f)): From the plots in

Figure 6 and Figure 7 it can be observed that the theoretical loop gain crossed over at roughly 20 kHz

with a phase margin of roughly 39 degrees.

æ N ö

ç VOUT ´ Rs ´ P ÷

ç NS j ´ 2p ´ f ´ R ZC ´ CZC +1 ÷

TcdB(f ) = 20log ç ´ gmC ´ ÷

j ´ 2p ´ f ´ L1´ DVRAMP æ j ´ 2 p ´ f ´ R ´ C ´ C ö

ç

ç

(j ´ 2p ´ f ´ (CZC +CPC ))ç ZC ZC PC

+1÷ ÷

è è CZC +CPC ø ÷ø

(71)

200 180

200 180

133.33

150

66.67

120

TcdB( f) 0

qc( f) 90

66.67

60

133.33

- 200 30

200

3 4 5 6

1 10 100 1 .10 1 .10 1 .10 1 .10

6

0

1 f 1´10 0

3 4 5 6

1 10 100 1 .10 1 .10 1 .10 1 .10

1 f 6

1´10

Figure 6. Current Loop Gain (TdB(f)) Figure 7. Current Loop Phase (qc(f))

SLUA479B – August 2008 – Revised July 2010 UCC28070 300-W Interleaved PFC Pre-Regulator —Design Review 15

Copyright © 2008–2010, Texas Instruments Incorporated

Soft Start www.ti.com

12 Soft Start

To have a controlled soft start the CSS capacitor needs to be set to at least the same value as the CZV

capacitor or larger. This means the design has a minimum soft start time based on the CZV capacitor

2.25 V ´ CZV 2.25V ´ 1.5 mF

t SSMIN = = » 338 ms

10 m A 10 m A

(72)

CSS ³ CZV

(73)

The soft-start timing can be set with timing capacitor CSS once the amount of soft start time (tSS) has been

determined. Our original design requirement was to have 200 ms of soft-start time. The calculated

capacitance needed for this soft-start time is less than the minimum required capacitance.

10 m A ´ t ss 10 m A ´ 200 ms

Css = = » 0.889 mF

2.25V 2.25 V

(74)

A CSS capacitor value equal to the CZV capacitor was chosen for the design.

Css = 1.5 mF

(75)

13 Spread Spectrum Reduces EMI

It has been shown that dithering the converter’s switching frequency can reduce EMI. Resistor RRDM and

CCDR program the frequency dithering magnitude and rate. For this design the frequency dither magnitude

(fDM) was set to 30 kHz and the frequency dither rate (fDR) was set to 10 kHz. The frequency will dither

around the typical frequency programmed by resistor RRT. In this example the frequency will dither from

roughly 185 kHz to 215 kHz at a 10 kHz rate.

fDM = 30 kHz

(76)

fDR = 10kHz

(77)

6 6

937.5 ´ 10 W 937.5 ´ 10 W

RRDM = = = 31.13 kW

fDM 30 kHz

(78)

0.0667 ´ 10-9F ´ RRDM 0.0667 ´ 10-9F ´ 31.13 kW

CCDR = = = 208 pF

fRD 10 kHz

(79)

A standard resistor and capacitor are chosen for the design:

RRDM = 31.6 kW

(80)

CCDR = 220 pF

(81)

16 UCC28070 300-W Interleaved PFC Pre-Regulator —Design Review SLUA479B – August 2008 – Revised July 2010

Copyright © 2008–2010, Texas Instruments Incorporated

www.ti.com Recommended PCB Device Layout

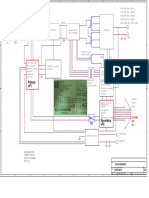

14 Recommended PCB Device Layout

Interleaved PFC techniques dramatically reduce input and output ripple current caused by the PFC boost

inductor, which allows the circuit to use smaller and less expensive filters. To maximize the benefits of

interleaving, the output filter capacitor should be located after the two phases allowing the current of each

phase to be combined together before entering the boost capacitor. Similar to other power management

devices, when laying out the PCB it is important to use star grounding techniques and to keep filter and

high frequency bypass capacitors as close to the device pins and ground pin as possible. To minimize the

interference caused by magnetic coupling from the boost inductor, the device should be located at least

one inch away from the boost inductor. It is also recommended that the device not be placed underneath

magnetic elements. To verify the application a 300-W interleaved prototype was constructed and

evaluated. This prototype consisted of mother board that was the power stage and a daughter board that

consisted of the control circuitry. Refer to Figure 8 through Figure 13 for schematics and a recommended

layout. The daughter board controller has two jumpers JP1 and JP2. If these jumpers are open the

evaluation module is running with frequency dithering. If these jumpers are shorted frequency dither is

disabled and the EVM can be synchronized through the sync input.

Figure 8. 300-W Prototype Daughter Board Controller Schematic

SLUA479B – August 2008 – Revised July 2010 UCC28070 300-W Interleaved PFC Pre-Regulator —Design Review 17

Copyright © 2008–2010, Texas Instruments Incorporated

Recommended PCB Device Layout www.ti.com

U1

UCC27324D

+ +

Figure 9. 300-W Prototype Mother Board Power Stage

18 UCC28070 300-W Interleaved PFC Pre-Regulator —Design Review SLUA479B – August 2008 – Revised July 2010

Copyright © 2008–2010, Texas Instruments Incorporated

www.ti.com Recommended PCB Device Layout

Figure 10. Daughter Board Layout Front

Figure 11. Daughter Board Layout Back

SLUA479B – August 2008 – Revised July 2010 UCC28070 300-W Interleaved PFC Pre-Regulator —Design Review 19

Copyright © 2008–2010, Texas Instruments Incorporated

Recommended PCB Device Layout www.ti.com

VOUT RETURN

C5

HS1

C2

L1 L2

C6 C7

.

D5 T1 . T2

D6

C2

RT1

J1

VAR1 Q1 Q1

F1

HS3 HS2

C11

J2 SYNC

AC LINE AC NEUTRAL VCC

GND

Figure 12. Mother Board Layout Front

RETURN VOUT

JP2

D1

JP2

D3

D9 D2

R19

R5

R9 R10

R18 R8

U1

C8

C12

R14 C10 D12

D11 R16

R13 R1

C4 D8

D7 R6

D13

C9 C3

R15

R3

R4

D10 D4

J1 R12 R7

R11

R17

R2

AC NEUTRAL AC LINE

Figure 13. Mother Board Bottom

20 UCC28070 300-W Interleaved PFC Pre-Regulator —Design Review SLUA479B – August 2008 – Revised July 2010

Copyright © 2008–2010, Texas Instruments Incorporated

www.ti.com Efficiency Curves

15 Efficiency Curves

A 300-W prototype was built based on the design information presented in this application note. The

following graphs show the performance of this EVM.

15.1 Prototype Efficiency

Efficiency Efficiency

100% 100%

98% 98%

96% 96%

94% 94%

% Efficiency

92% 92%

% Efficiency

90% 90%

88% 88%

86% 86%

Efficency at Vin 85V RMS Efficiency at VIN = 115V

84% 84%

82% Efficiency at VIN = 230V

82% Efficency at Vin = 265V RMS

80%

80%

10% 20% 30% 40% 50% 60% 70% 80% 90% 100% 10% 20% 30% 40% 50% 60% 70% 80% 90% 100%

% Output Power % Output Power

Figure 14. Figure 15.

Current Harmonics V IN = 230V, POUT = 300W

1.41473

1.17894

0.94316

EN61000-3-2 Class D Specifications

Amplitude (A)

0.70737

0.47159

0.23580

0.00001

1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39

Harmonic

Figure 16. Prototype Harmonic Content at VIN = 230 V, POUT = 300 W

SLUA479B – August 2008 – Revised July 2010 UCC28070 300-W Interleaved PFC Pre-Regulator —Design Review 21

Copyright © 2008–2010, Texas Instruments Incorporated

Efficiency Curves www.ti.com

15.2 Prototype Power Factor

Pow er Factor Pow er Factor

1.000 1.000

0.990 0.990

0.980 0.980

0.970 0.970

0.960 0.960

PF

0.950

PF

0.950

PF VIN = 85V 0.940 PF VIN = 115V

0.940

PF VIN = 265V PF VIN = 230V

0.930 0.930

0.920 0.920

0.910 0.910

0.900 0.900

20% 30% 40% 50% 60% 70% 80% 90% 100% 20% 30% 40% 50% 60% 70% 80% 90% 100%

% Output Pow er % Output Pow er

Figure 17. Figure 18. Input Current and Output Ripple Voltage at

Maximum Output Power

Ch2 = IIN, CH2 = VOUT

Figure 19. VIN = 85 V RMS Figure 20. VIN = 265 V RMS

22 UCC28070 300-W Interleaved PFC Pre-Regulator —Design Review SLUA479B – August 2008 – Revised July 2010

Copyright © 2008–2010, Texas Instruments Incorporated

www.ti.com Efficiency Curves

15.3 Inductor Ripple Current Cancellation, CH2=IL1, CH3=IL2, M1=IL1+IL2

Figure 21. VIN = 85 V RMS, Peak of Line Figure 22. VIN = 265V RMS, Peak of Line

Figure 23. VIN = 265V RMS, Line Voltage at Half the Figure 24. VIN = 85 V, POUT = 300 W

Output Voltage

SLUA479B – August 2008 – Revised July 2010 UCC28070 300-W Interleaved PFC Pre-Regulator —Design Review 23

Copyright © 2008–2010, Texas Instruments Incorporated

Efficiency Curves www.ti.com

Figure 25. VIN = 265 V, POUT = 300 W

24 UCC28070 300-W Interleaved PFC Pre-Regulator —Design Review SLUA479B – August 2008 – Revised July 2010

Copyright © 2008–2010, Texas Instruments Incorporated

www.ti.com Efficiency Curves

15.4 Recovery from Line Dropout, CH1= Rectified Line Voltage, CH2=IL1, CH3=IL2, CH4 =

VOUT

Figure 26. Brownout at VIN = 115V, POUT = 300 W

15.5 Startup, CH2 = IL1, CH3 = IL2, CH4 = VOUT

Figure 27. VIN = 85 V, POUT = 300 W Figure 28. VIN = 265 V, POUT = 300 W

SLUA479B – August 2008 – Revised July 2010 UCC28070 300-W Interleaved PFC Pre-Regulator —Design Review 25

Copyright © 2008–2010, Texas Instruments Incorporated

References www.ti.com

15.6 EMI Measurements

When dithering was applied to the EVM a 4.35dBuV reduction in the Quasi Peak (QP) measurement was

observed. Note a filter was added to the front end of the EVM to clean up some of the noise to take EMI

data. Depending on the filter the amount of EMI will vary. Also, this filter was not setup to pass EMI

requirements but to show frequency dither reduced EMI.

Figure 29. EMI Quasi Peak (QP) Measurement with out Frequency Dithering, No EMI Filter Present

Figure 30. EMI Quasi Peak (QP) Measurement with Frequency Dithering, No EMI filter Present

16 References

1. Lazlo Balogh and Richard Redi, Power Factor Correction with Interleaved Boost, APEC 1993, pp.

168-174

2. Lloyd Dixon, High Power Factor Switching Pre-regulator Design Optimization, Unitrode Power Supply

Design Seminar SEM-700, 1990, Topic 7

3. Brett Miwa, David Otten, Martin F. Schlecht, High Efficiency Power Factor Correction Using Interleaved

Techniques IEEE 1992, pp. 557 to 568

4. Michael O’Loughlin, 350W, Two Phase Interleaved PFC Pre-regulator Design Review, Texas

Instrument Literature Number SLUA369, 2006

5. Michael O’Louglin, An Interleaving PFC Pre-Regulator for High-Power Converters Unitrode/TI Power

Supply Design Seminar SEM-1700, Topic 5

6. P. Zumel, O. Garcia, J. A. Cobos, J. Uceda, EMI Reduction by Interleaving of Power Converters

Presentation, APEC 2004

7. UCC28070 Data Sheet, Texas Instruments Literature Number SLUS794,

http://focus.ti.com/lit/ds/symlink/ucc28070.pdf

26 UCC28070 300-W Interleaved PFC Pre-Regulator —Design Review SLUA479B – August 2008 – Revised July 2010

Copyright © 2008–2010, Texas Instruments Incorporated

IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements,

and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should

obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are

sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard

warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where

mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and

applications using TI components. To minimize the risks associated with customer products and applications, customers should provide

adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right,

or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information

published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a

warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual

property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied

by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive

business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional

restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all

express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not

responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably

be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing

such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and

acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products

and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be

provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in

such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are

specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military

specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at

the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are

designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated

products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

Products Applications

Amplifiers amplifier.ti.com Audio www.ti.com/audio

Data Converters dataconverter.ti.com Automotive www.ti.com/automotive

DLP® Products www.dlp.com Communications and www.ti.com/communications

Telecom

DSP dsp.ti.com Computers and www.ti.com/computers

Peripherals

Clocks and Timers www.ti.com/clocks Consumer Electronics www.ti.com/consumer-apps

Interface interface.ti.com Energy www.ti.com/energy

Logic logic.ti.com Industrial www.ti.com/industrial

Power Mgmt power.ti.com Medical www.ti.com/medical

Microcontrollers microcontroller.ti.com Security www.ti.com/security

RFID www.ti-rfid.com Space, Avionics & www.ti.com/space-avionics-defense

Defense

RF/IF and ZigBee® Solutions www.ti.com/lprf Video and Imaging www.ti.com/video

Wireless www.ti.com/wireless-apps

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2010, Texas Instruments Incorporated

You might also like

- UCC28070 300-W Interleaved PFC Pre-Regulator Design Review: Application ReportDocument41 pagesUCC28070 300-W Interleaved PFC Pre-Regulator Design Review: Application ReportKiên NguyễnNo ratings yet

- AP1510 SchematicDocument9 pagesAP1510 SchematicteniNo ratings yet

- Sboa 287Document5 pagesSboa 287Khaian LaybinitzNo ratings yet

- AP1539 DiodesIncorporatedDocument13 pagesAP1539 DiodesIncorporatedalexmihai_scribdNo ratings yet

- FSQ0170RNA, FSQ0270RNA Green Mode Fairchild Power Switch (FPS™)Document17 pagesFSQ0170RNA, FSQ0270RNA Green Mode Fairchild Power Switch (FPS™)mircea mozoleaNo ratings yet

- AN149f PDFDocument22 pagesAN149f PDFranjitheee1292No ratings yet

- Onsemi FSCQ0765RTYDTU DatasheetDocument33 pagesOnsemi FSCQ0765RTYDTU DatasheetsamynnxpNo ratings yet

- 230V SinglephaseDocument1 page230V SinglephasePaul CansinoNo ratings yet

- F DatasheetDocument16 pagesF DatasheetTerelia Kinan GallenNo ratings yet

- CatalogueDocument29 pagesCatalogueAnonymous CPmZqMNo ratings yet

- Ap1534 59433Document10 pagesAp1534 59433YachnaNo ratings yet

- AOZ1268QI 01 AlphaOmegaSemiconductorsDocument15 pagesAOZ1268QI 01 AlphaOmegaSemiconductorsrcgruwanNo ratings yet

- Service BulletinDocument34 pagesService BulletinSilomo-saka MambaNo ratings yet

- Design For A Discrete Charge Pump: Application ReportDocument8 pagesDesign For A Discrete Charge Pump: Application ReportDrTeethNo ratings yet

- FSCQ1565RT: Green Mode Fairchild Power Switch (FPS) For Quasi-Resonant Switching ConverterDocument25 pagesFSCQ1565RT: Green Mode Fairchild Power Switch (FPS) For Quasi-Resonant Switching ConverterPaulo Roberto s freireNo ratings yet

- Design and Analysis of A New GaN-based AC DC Topology For Battery Charging ApplicationDocument6 pagesDesign and Analysis of A New GaN-based AC DC Topology For Battery Charging Applicationshibijith.m24No ratings yet

- Circuito en Fuente TV LCD Mustek N3856VGDocument13 pagesCircuito en Fuente TV LCD Mustek N3856VGAntonio ChavezNo ratings yet

- TQC v2.2.2Document1 pageTQC v2.2.2IratiNo ratings yet

- Tps 54040Document53 pagesTps 54040l.siqueiraNo ratings yet

- TPS54040 0.5-A, 42-V Step Down DC/DC Converter With Eco-Mode™Document53 pagesTPS54040 0.5-A, 42-V Step Down DC/DC Converter With Eco-Mode™SofyanNo ratings yet

- RF-382A Remote ControllerDocument8 pagesRF-382A Remote ControllerΒΕΗΣ ΣΤΕΛΙΟΣ Veis SteliosNo ratings yet

- LTJournal V25N1 06 Di LT3999 DawsonHuangDocument5 pagesLTJournal V25N1 06 Di LT3999 DawsonHuangEdoardoNo ratings yet

- Tea 5170Document9 pagesTea 5170Erasmo Franco SNo ratings yet

- FSCQ0765RT PDFDocument25 pagesFSCQ0765RT PDFGreivin GonzálezNo ratings yet

- Email Ke Pak Budi - Electrical Work DM1W+B R2 Final 1Document6 pagesEmail Ke Pak Budi - Electrical Work DM1W+B R2 Final 1Serdadu LebahNo ratings yet

- Alinco DR-138 Serv PDFDocument42 pagesAlinco DR-138 Serv PDFHarris AdrianNo ratings yet

- P 6 KexxDocument4 pagesP 6 KexxEmigert HimaNo ratings yet

- 500-kHz Half-Bridge DC-DC ConverterDocument17 pages500-kHz Half-Bridge DC-DC Converteratkxyz777100% (1)

- An 1173Document21 pagesAn 1173M. T.No ratings yet

- An 1173 PDFDocument21 pagesAn 1173 PDFM. T.No ratings yet

- Growatt 12000TL3-S/13000TL3-S 15000TL3-S: Leading - Edge TechnologyDocument2 pagesGrowatt 12000TL3-S/13000TL3-S 15000TL3-S: Leading - Edge TechnologyVaibhav Shandilya0% (1)

- FSQ510, FSQ510H - Green Mode Fairchild Power Switch (FPS) For Quasi-Resonant ConverterDocument15 pagesFSQ510, FSQ510H - Green Mode Fairchild Power Switch (FPS) For Quasi-Resonant ConverterEletronica TecnotronicaNo ratings yet

- tps54560 q1 PDFDocument43 pagestps54560 q1 PDFgjsmoNo ratings yet

- Features Descriptio: LTC1624 High Efficiency SO-8 N-Channel Switching Regulator ControllerDocument28 pagesFeatures Descriptio: LTC1624 High Efficiency SO-8 N-Channel Switching Regulator ControllervetchboyNo ratings yet

- InterfacingDocument46 pagesInterfacingdundi_kumarNo ratings yet

- Datasheet Growatt 12000-15000 tl3-s PDFDocument2 pagesDatasheet Growatt 12000-15000 tl3-s PDFTelecomMasterNo ratings yet

- LT 8711Document38 pagesLT 8711MallikarjunBhiradeNo ratings yet

- Ucc28950 600 W Phase Shifted Full Bridge App Report TI Slua560b PDFDocument30 pagesUcc28950 600 W Phase Shifted Full Bridge App Report TI Slua560b PDFvinsenNo ratings yet

- ALINCO DR 130 (Manual Tecnico)Document42 pagesALINCO DR 130 (Manual Tecnico)Ramon Suarez FleitasNo ratings yet

- Tps 54140Document52 pagesTps 54140niceautomation8831No ratings yet

- Jim Williams An04Document8 pagesJim Williams An04MartinNo ratings yet

- Primary Up1: Pandemonium Power Supply Block Diagram REV.X3Document11 pagesPrimary Up1: Pandemonium Power Supply Block Diagram REV.X3Alex LuzNo ratings yet

- HP - HSTNS PL11 - PS 2122 1CDocument11 pagesHP - HSTNS PL11 - PS 2122 1CStephen SoosaiNo ratings yet

- Instruction Manual: Installation Operation MaintenanceDocument7 pagesInstruction Manual: Installation Operation MaintenanceEslam SadekNo ratings yet

- AozDocument16 pagesAozAndreNo ratings yet

- Features DescriptionDocument24 pagesFeatures DescriptionAhmad SubkhanNo ratings yet

- Description Features: APU3037 / APU3037ADocument18 pagesDescription Features: APU3037 / APU3037ALeonardoNo ratings yet

- Design Guidelines For Quasi-Resonant Flyback DesignDocument21 pagesDesign Guidelines For Quasi-Resonant Flyback DesignTarelli RiccardoNo ratings yet

- Pfc-Control-Ic-Fa1a60n 58 PowerDocument7 pagesPfc-Control-Ic-Fa1a60n 58 PowerTDFRIOGRANDE100% (1)

- Tps 54240Document48 pagesTps 54240Maria KhanNo ratings yet

- FSQ100 Green Mode Fairchild Power Switch (FPS™) : Features DescriptionDocument13 pagesFSQ100 Green Mode Fairchild Power Switch (FPS™) : Features Descriptionايهاب فوزيNo ratings yet

- LM25085A 42V Constant On-Time PFET Buck Switching Controller With 0.9V ReferenceDocument31 pagesLM25085A 42V Constant On-Time PFET Buck Switching Controller With 0.9V ReferenceStuxnetNo ratings yet

- Fcp190N60 / Fcpf190N60: N-Channel Superfet Ii MosfetDocument10 pagesFcp190N60 / Fcpf190N60: N-Channel Superfet Ii Mosfetarness22No ratings yet

- Growatt 15000TL3-SL/ 20000TL3-SL/22000TL3-SL: Leading - Edge TechnologyDocument2 pagesGrowatt 15000TL3-SL/ 20000TL3-SL/22000TL3-SL: Leading - Edge TechnologyJohnny Alberto GaleanoNo ratings yet

- Data SheetDocument28 pagesData SheetCarlos CxsNo ratings yet

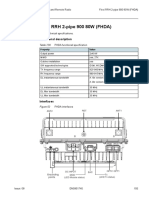

- 30 Flexi RRH 2-Pipe 900 80W (FHDA) : Functional DescriptionDocument5 pages30 Flexi RRH 2-Pipe 900 80W (FHDA) : Functional DescriptionАндрей СвининNo ratings yet

- Switch Mode Power Supplies Muito BomDocument20 pagesSwitch Mode Power Supplies Muito BomHamedKoneNo ratings yet

- FAX30 Service Manual B3 12-15-10Document34 pagesFAX30 Service Manual B3 12-15-10Leovard69No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- V1 001 PDFDocument20 pagesV1 001 PDFG100% (2)

- Elasticity of Solid, Liquid and Modulus of MaterialsDocument3 pagesElasticity of Solid, Liquid and Modulus of MaterialsHinata CosaNo ratings yet

- Installation and Removal of High MastDocument3 pagesInstallation and Removal of High MastMohd Hafiz Muhamed100% (1)

- en 30 - Sub Supplier - ManagementDocument2 pagesen 30 - Sub Supplier - ManagementAMB SpainNo ratings yet

- Vickers Hardness TestDocument9 pagesVickers Hardness TestMazlin AzuraNo ratings yet

- David Brown Engineering LTDDocument2 pagesDavid Brown Engineering LTD'-MubashirBaigNo ratings yet

- VSD 50 HZ 201.21-NM2 167-1Document1 pageVSD 50 HZ 201.21-NM2 167-1Asanka RodrigoNo ratings yet

- Website Design Contest-6!9!2023Document1 pageWebsite Design Contest-6!9!2023maha sowmeNo ratings yet

- Management Visit Report 31 October 2023Document3 pagesManagement Visit Report 31 October 2023John Renz Caling RetiroNo ratings yet

- Wooden PanelingDocument47 pagesWooden PanelingRashim SharmaNo ratings yet

- Alignment Report (Kolar-Chikkaballapura)Document38 pagesAlignment Report (Kolar-Chikkaballapura)Kiran R Gowda100% (2)

- PCB Design TutorialDocument25 pagesPCB Design TutorialMadhu Mangal KumarNo ratings yet

- Comparing The Mechanical Properties of Cyanate Ester Modified Epoxy /glass LaminatesDocument7 pagesComparing The Mechanical Properties of Cyanate Ester Modified Epoxy /glass LaminatesAndrew NallayanNo ratings yet

- Plantation Tree ProjectsDocument15 pagesPlantation Tree Projectsmahnoor cheemaNo ratings yet

- Access - Catalog.805b.color - DP&Casing Tools-50Document1 pageAccess - Catalog.805b.color - DP&Casing Tools-50RICHARDNo ratings yet

- Ariel Corporation - Arielcorp - Com15Document1 pageAriel Corporation - Arielcorp - Com15Anwar Sadat100% (1)

- Fortigate Logging ReportingDocument68 pagesFortigate Logging Reportingzulhelmi2010No ratings yet

- UpsDocument22 pagesUpsroshani007No ratings yet

- DSE9701 & DSE9702: Vertical 5 Amp Battery ChargersDocument2 pagesDSE9701 & DSE9702: Vertical 5 Amp Battery Chargersasuhuane100% (1)

- CPP Tutorial0Document581 pagesCPP Tutorial0abdoNo ratings yet

- QC Hemato Mei 2014 NormalDocument29 pagesQC Hemato Mei 2014 Normalsri wahyuniafif2425No ratings yet

- M and J Slab Gate ValveDocument12 pagesM and J Slab Gate Valvetxlucky80No ratings yet

- Despiece SUSP. DEL 930EDocument2 pagesDespiece SUSP. DEL 930EAndersson Campos VásquezNo ratings yet

- Regulatory Documentation PDFDocument21 pagesRegulatory Documentation PDFJohn Mark BordeosNo ratings yet

- 4grinding Polishing Flexible ToolsDocument113 pages4grinding Polishing Flexible ToolsGabriel DobrescuNo ratings yet

- KS 103 1984Document39 pagesKS 103 1984Carlos A GonzaNo ratings yet

- Lawal Habeeb Babatunde: A Seminar Report OnDocument21 pagesLawal Habeeb Babatunde: A Seminar Report OnAyinde AbiodunNo ratings yet

- Sendai Mediatheque - Data, Photos & Plans - WikiArquitectura PDFDocument7 pagesSendai Mediatheque - Data, Photos & Plans - WikiArquitectura PDFhariNo ratings yet

- Post Launch Report For Apollo Mission A-102Document331 pagesPost Launch Report For Apollo Mission A-102Bob AndrepontNo ratings yet

- Instruction: Write The Step by Step Procedures in InstallingDocument7 pagesInstruction: Write The Step by Step Procedures in InstallingJovilen Rose MarmesNo ratings yet