Professional Documents

Culture Documents

Exp 8-10 Dld. Lab

Uploaded by

Mohit YadavOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Exp 8-10 Dld. Lab

Uploaded by

Mohit YadavCopyright:

Available Formats

BML MUN JAL

.. UNIVERStTY

•l'•oM: ~•·•r ,o rwt .-o,ua

Fundamentals of Digital logic Lab

EXPERIMEN T N O.8

Objective: Verification of Counter circuit.

1. ~eration of a 4-Bit Binary counter using ICs 7493

2. Ring counter using ICs 7495.

3. Johnson Ring counter using !Cs 7495.

Apparatus: IC 7495, IC 7404, Patch Cords & IC Trainer Kit.

Theory: A counter is a register capable of counting number of clock pulse arriving at its clock

input. Counter represents the number of clock pulses arrived. Ring counter is a basic register

with direct feedback such that the contents of the register simply circulate around the register

when the clock is running. Here the last output that is QD in a shift register is connected back to

the serial input. A basic ring counter can be slightly modified to produce another type of shift

register counter called Johnson counter. Here complement of last output is connect:d back to

the not gate input and not gate output is connected back to serial input. A four btt Johnson

counter gives 8 state output.

PROCEDURE:

• Check all the components for their working.

• Insert the appropriate IC into the IC base.

• Make connections as shown in the circuit diagram.

• Apply clock to pin number 9 and observe the output

,,.~v

s

v,,

'~ A

8

IC

7f9!5

,o

t:,,J

Department of Electronics and Communication Engineering, SOET

BML MUNJAL UNIVERSITY

-

BML MUN JAL

UN IVERSlTV

FHN IOIU , . ,Ml WO•lo

CLK

0

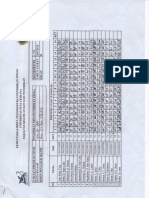

OA OB oc OD

Fundamentals of Digital logic Lab

0 0 0 0

1 0 0 0 1

2 0 0 I 0

3 0 0 I l

4 0 1 0 0

5 0 1 0 1

6 0 1 I 0

7 0 1 I I

8 I 0 0 0

9 1 0 0 1

10 l 0 1 0

11 l 0 1 1

12 l 1 0 0

13 1 1 0 1

14 l 1 1 0

'15 l 1 l 1

b) Ring counter circuit- Truth Table

- .. , . - .. .

-- -·

.. ...

ad Q, Q,

u~-u 1r1r, --e-

• 0 l

Cl!

0 0 0

0

1 - - ..0 1 0

!

,

0

,,.

0 1.. o···

re ,an .... , . · o·· ·----

0

·---··· ..

0. 1

,. ..

--J·-1_f 0

·-·

0 .

..

,r

S - 0.

I 0 0

- ····-

0 0... l --- ---- 0

'I

1

...

n

I

.. -·--

..

0.

0

.

0

0

l

0

•---

Department of Electronics and Communication Engineering, SOET

BML MUNJAL UNIVERSITY

-

BMLMUN JAL

UNIVERSITY

faDM Hl•I TO Tlfll l!Hlttll

c) Johnson Ring Counter-

Fundamentals of Digital logic Lab

Truth Table

Ooct Qa Qc Qo

'I ii~ 0A - -

0 0 Q

0 0

14 12 1110 9 ,. I 0 0 0

2 l J 0 0

IC lUS

l 1 t 0

's

= -

4 1

0

l

1

I

l

l

l

0 0 1 I

'

7

I

0

0

0

0

0

0

I

0 '

Result-

Department of Electronics and Communication Engineering, SOET

BML MUNJAL UNIVERSITY

8

BML MUN JAL

UNIVERSITY

F•ON HC•C' ro lttl. wO•LD

Fundamentals of Digital logic Lab

EXPERIMENT N0.9

Objecdve: Construction ofFlip- Flops and verification of its operation.

Apparatus: Digital trainer kit, IC 7400, 741 0 Connecting wires.

Theory: A Multi vibrator is a regenerative circuit with two active devices designed so that one

device conducts while the other is cut off. Multi vibrator can store binary numbers. So it can

perform essen~al ~ctions like counting of pulses, synchronizing arithmetic Operations etc.

Such type of ctrcwt ts known as FLIP-FLOP circuits. Here we are going to study all types of

FLIP-FLOPs:

I. R-S Latch

2. R-S Flip-Flop

3. D Flip-Flop

4. J-K Flip-Flop

5. T Flip-Flop

Procedure:

I. Connect the trainer kit to A.C power supply.

2. Construct an R-S latch by connecting two NANO gates as per logic diagram.

3. Connect logic sources to R, S inputs and outputs Q, Q' to logic indicators.

4. Apply various R-S combinations and observe Q, Q' outputs.

5. Verify the truth table.

6. Switch off the ac power supply.

S.R Latch- S-R (Set, Reset) latch is a digital storage device. lt can store one bit at time. lts

output depends upon the combination of inputs and previously stored bit.

An S-R latch can be constructed by using two cross couples NAND/ NOR gates. We will use

NOR gates and construct aii active high S-R latch.

Working-

!. S=O, R=O: this is the rest state of the NOR latch. This input has no effect on the output

state. Outputs (Q, Q') will remain in whatever state they were prior to the occurrence of

this input combination.

2. S=l, R=O: this will always set the latch (Q=l, Q'=0), it will remain in this state even

after S returns to 0.

3. S=O, R=l: this will always reset the latch (Q=O, Q'=l), it will remain in this state even

after R returns to 0.

4. S=l, R=l: this condition tries to set and reset the latch at the same time and produces

Q=O, Q'=0. If inputs are returned to 0 at same time, the resulting output state is

unpredictable. This input condition should not be used.

Department of Electronics and Communication Engineering, SOET

BML MUNJAL UNIVERSITY

(.)

BML MUNJAL

UNIVERSITY

j f•OW Hf•~ lO HO IIJO•LO

Fundamentals of Digital logic Lab

S.R Latch Circuit Truth Table-

9

1

S R Q Q'

1 O 0 1

1 '1 O 1 °t~.aftsr 5=1 ,-R=O)

0 1 1 0

1 o_

I0-"6--Q - .1 1

I_;

1 f ;

Clocked S.R Flip Flop- Truth Table-

P.J.iq:P. .$T~:

'T

· :No. 1>rmous ;

:¢.1iange . -·

. f_,,,

orbjdde

·,-r-,,r,

'.I!.

Department of Electronics and Communication Engineering, SOET

BML MUNJAL UNIVERSITY

~- '-'

.j

,,

-~ 0

<!

...... ,0

r

,,

BML MUN JAL

UN IVERSITY

,aoM HUl •o ,.,. no•Le

Fundamentals of Digital logic Lab

D Flip Flop using N AN O Gate. Truth Table

• 1

t =p--r-------....1..ft

' ----1· 0

D Flip flop- D flip-flop is shown in figure. This Flip-Flop is constructed from R-S Flip-Flop.

The S Input ofR-S Flip-Flop is kept as it is and R input is shorted with S input through a NOT

gate. D flip flop is also known as Delay flip flop since it generated the same output as input

when the clock pulse arrives. D flip flop is used in the construction of shift registers, counte.rs

and various other applications.

Working:

D input is 0, the output is 0.

DWhen D input is I, the output is I.

Hence, D Flip-Flop gives the same output as the input and therefore D stands for DATA.

Department of Electronics and Communication Engineering, SOET

BML MUNJAL UNIVERSITY

BMlMUN JAl

UNIVERSITY Fundamentals of Digital logic Lab

l'llJIN )(pt TO 1111 W611LD

T Flip flop using N AN D Gate.

Truth Table-

Clock T

1 1

1 0

T- Flip flop- T flip-flop is the flip-flop that satisfies only the first two and the last two

condition of the JK flip-flop. As flip-flop is called toggle flip-flop by virtue of its property that

the state stored 'toggles' on receiving a clock pulse (when T=l) goes to the opposite state. A JK

flip-flop can easily be converted into a T flip-flop by connecting its two inputs together. T flip-

flop finds applications in digital counters.

Working:

T=O=>Q(t+l)=Q

T=l =>Q(t+l)=Q'

Department of Electronics and Communication Engineering, SOET

BML MUNJAL UNIVERSITY

,: - I t}

- .o ;:f

-

BML MUNJAL

~•o.,UNIVERSITY

ftl&l •o 11,t wou 11

Fundamenlals of Digital logic Lab

,,

J.K Flip Flop using NAND Gate. Truth Table

CK

Ku-___,

Inputs Outputs

Comments

E J K Q._, Q.,:

1 0 0 Q

-Q. No change

1 0 1 0 1 Rset

1 1 0 1 0 Set

1 1 1 Q. Q. Toggle

J.K Flip flop- J-K flip-flop can be used to build a counter that counts the number of positive or

negative clock edges driving its clock input. For the purpose of counting, the J-K flip-flop is the

ideal element to use. The circuit diagram of J-K flip-flop is as shown.

Working:

When J & K both are at low state, both AND gate are disabled and so clock pulse has no

Effect i.e. Q retains its last value. When J=O & K=l upper gate is disabled so there is no way to

set the flip-flop. The only possibility is RESET. When Q is high, the power gate passes a

RESET triggers as soon as the riext positive clock edge arrives. This forces Q to become low.

When J=l & K=O, lower gate is disable so it is impossible to RESET the flip-flop. We can SET

the flip-flop, when Q is low DQ is high. Therefore the upper gate passes a SET trigger on the

next positive clock edge. This drives Q in to high state i.e. Q= 1.

Department of Electronics and Communication Engineering, SOET

BML MUNJAL UNIVERSITY

BML MUNJAL

UNIVERSITY

(IOM NOl to HU, W'OQla

Fundamentals of Digital logic Lab

Pin configuration ofIC 7410.

GNO

7

7410 Triple 3 Input NANO

Result:

Department of Electronics and Communication Engineering, SOET

BML MUNJAL UNIVERSITY

-

BML MUNJAl

UNIVERSITY

, .JIii kfil l'O l"I ltO'-LD

EXPERIMEN T N O.IO

Fundamentals of Digital logic Lab

Objective: _Construction of 4 bit SISO, SIPO, PlSO, PIPO Shift Registers and verification of

their operation.

Apparatus: Digital Trainer kit, ICs 7495, connecting wires.

Theory: A Flip-Flop can store only one bit of data. If we want to store a group of bits, a series

of flip- ~ops ~e ~ter-connected in cascade. This cascaded group of flip-flop as a whole. is

called a Register . The fundamental operations, which make a register very useful, are its

"Shift right" and "Shift left'' operation. There are two methods for shifting binary infonnation

into a register.

1. shifting the information into a register one bit at a time in a series fashion and leads to the

development of a serial shift register.

2. Shifting all the bits into the register at a same time and leads to the development of a

Parallel shift register.

There are basically 4 types of shift registers:

1. Serial-in, serial-out shift register

2. Serial-in, parallel-out shift register

3. Parallel-in, serial-out shift register

4. Parallel-in, parallel-out shift register

Serial-in, serial-out shift register can be of 2 types:

(i) Serial-in, serial-out shift right register

(ii) Serial-in, serial-out shift left register

Also there are 2 shift registers available:

1. Bidirectional shift register

2. Universal shift register

Application:Shift register is used to move the data. To move data, it must be stored. So shift

register actually stores data and moves it to left, right as per signal given to it.

Serial In: Output of one flip flop is input of another. Data is seriatly given i.e. only first flip

flop receives data; it is shifted to next flip flops.

Serial Out: Data is taken out from last flip flop

Parallel In: All flip flops are loaded simultaneously

Parallel Out: data is taken parallel by taking outputs from all flip flops at same time.

This shift register bas four distinct modes of operation.

Department of Electronics and Communication Engineering, SOET

BML MUNJAL UNIVERSITY

BML MUNJAL

UN IVERSITY

ow Ht•t ,.-o , Ht •o•Let . b

ra • . Fundamentals of Digital logic La

I. parall~I Shift Mod_e: Applymg the four bits of data and talcing both mode control input~, SO

and SI high, accomplish synchronous parallel loading. The data are loaded into the assoc1a~ed

flip-flops and appears at the outputs after the positive transition of the clock input. Dunng

loading, serial data flow is inhibited.

2. Shift Right Mod~: S~ift right is accomplished synchronously with the rising edg~ of_ the

clock pulse when SO 1s high and SI is low. Serial data for this mode is entered at the shift nght

data input.

3. Shift Left Mode: When SO is low and SI is high, 1 bit data shifts one position to the left

synchronously and new data is entered at the serial-left serial input at every clock pulse.

4. Inhibiting Mode: Clocking of the flip-flops is inhibited when both mode control inputs are

low.

Procedure:

I. Connect flip flops (ICs 7495) as per given diagram on the bread board.

2. Prepare circuitry using connecting wires. .

3. Apply different level logic combinations to the inputs and observe the correspondmg

Outputs.

4. Note down observed output level in corresponding observation table.

5. Switch off supply.

Circuit diagram for shift left to right/ right to left (Bi dierctional) shift.

'

t

Department of Electronics and Communication Engineering, SOET

BML MUNJAL UNIVERSITY

-

aML MUNJAL

UNIVERSITY

, .... 111 ,u ~O llU _,O.lll

Truth Table-

Fundamentals of Digital logic Lab

Mode ' Clock Shift SerialLeft To Mode Clock Shift serial Right To left

Right -+

+-

M==O CLK- QA QB QC QD M=l CLK- QA QB QC QD

1 2

0 1 I I 1 1

0 2 I 1 I 2 I I

0 3 1 1 1 1 3 1 I 1

0 4 1 1 1 1 1 4 I 1 I 1

1) Serial in Parallel Out (SIPO) Right Shift

Logic Diagram of SIPO Right Shift

"'

'.,;,: ;:=.; • '\

. .

L

,I

- ,. 'ii!

. q ( I,.

Department of Electronics and Communication Engineering, SOET

BML MUNJAL UNIVERSITY

r•O"

•

BML MUNJAL

UN IVERSITY

Truth Table

1'0 'tWI._ WOtll.L.D

Fundamentals of Digital logic Lab

Mode Clock Serial lnnut

M=O CLK-1 1

OA OB oc OD

0 I

0

,0 0 I

1

,0 1 0 1

2) Seri al in Serial Out (SISO~ 1 1 0 1

Serial ,c: l

SDI (l.A.

(lB

.A. QC

& QD

C

D 749~

Clock 1/P 0

He - _ __;e~J··cu(1

::.,.. 1 __. 'v'CC

·- C: L~=;::;:

.. _.__ ~-- 6

, ....... d e ~ · - · t,_-,o DE GUD

Logic Diagram of Serial In Serail Out (S1S0)-

Data in Data out

Clock....--Mll:..

Clear_ _ _ _..__ _ _ _ _ ____._ _ __

Department of Electronics and Communication Engineering, SOET

BML MUN .JAL UNIVERSITY

r

SML MUNJAL

UNIVERSITY

, .0 ., ,.,., to ••t -••a

rruth Table for 4 bit output- Fundamentals ofDigital logic Lab

Mode Clock Serial Input

M=O CLK-1 I

OA OB oc OD

0 2 I

0 3

I -+ I

0 4

1 I -+I

0 I I I -+I

I 0

0 0

2

0 0 -+0

3

0 0 0 -+0

4

0 0 0 -+0

rruth Table for single output

Mode Clock Serial Input

M=O - - - OD

CLK-1 1 I

0 2

-+I

0 3

-+I

0 4 ---+ I

3) Parallel in Serial out (PISO)

NC,,. 1

SOI QA

(· 2 QB

Parallel ,;. 3 .A. QC

IIP Data '~ 4

B QO

,..., 5 C

D 7~5

g

NCC 8 ;CLK1 1 -.>VCC

Clock 1/P (: · CLK2 ·vi::c

,•, 6

~bde (M) MODE GNO

Department of Electronics and Communication Engineering, SOET

BML MUNJAL UNIVERSITY

e.

IAL t,lUNJAL

,.or~r41Vffl'l:'0110

.,

·.o Serial Out (PISO) Fundamentals of Digital logic Lab

4) I

gUFI'/Dl=O

Parallel-in/ serial-out shift register showing parallel load paih

rruth Table-

Mode Clock A B C D QA OB oc OD

M-1 CLK-2 1 0 0 0 1 0 0 0

0 CLK-1 1 0 0 0 1 0 0 0

0 1 X ---+ 1 0 0

0 2 X ·x ---+ I 0

0 3 X X X ---+ I

5) Parallel In Parallel Out (PIPO)

N C,,...1

SDI QA

.~ 2 QB

Parallel J A QC

1/P Data ·::: 4 B ClD

[ C

:~ 5 D 749~

9

N C <:>-- -8 - .· CLK1 1 ~·VCC

Clock 1/P <: . CLl<:2 \ICC

.,.. 6 7

fubde (M) . MODE GND

Department of Electronics and Communication Engineering, SOET

BML MUNJAL UNIVERSITY

-

r,4L MUNJAL

i ,,11 . ,.,.

B

t1NI VERSITV

C TO 11<L WitllLD

tb fable- Fundatn

ff11 entals of Digital logic Lab

'

Mode . Clock A B

M==J CLK-2 l 0

l 1

1 2

1 l

l

0

0

D

l

I

I 3 l 0

I

4 0

I 0 0 I

I

't}

' ., ,'~

·~ -- ..

'

'

&csul

Department of Electronics and Communication Engineering, SOET

BML MUNJAL UNIVERSITY

You might also like

- ITP For EDGDocument6 pagesITP For EDGmuraliNo ratings yet

- Atlas-1 PDFDocument31 pagesAtlas-1 PDFR.SubramanianNo ratings yet

- A267541 Off TopicDocument99 pagesA267541 Off TopicratnatejreddyNo ratings yet

- BelowTenMetersTheManualOfUltra Short Wave Radio PDFDocument72 pagesBelowTenMetersTheManualOfUltra Short Wave Radio PDF_lucky_No ratings yet

- Experiment 3Document3 pagesExperiment 3AAAAALLENNNo ratings yet

- Capitulo07 Pensamento Complexo Interdisciplinaridade 1654727102 PDFDocument16 pagesCapitulo07 Pensamento Complexo Interdisciplinaridade 1654727102 PDFDouglas BarrosNo ratings yet

- FinanceDocument5 pagesFinancevaofiuxlrqpepscxwqNo ratings yet

- LuxemburgoDocument30 pagesLuxemburgoBeatriz C. MeloNo ratings yet

- Autocad KeyboardDocument1 pageAutocad Keyboardmiron alNo ratings yet

- Ian Shanahan - 31-Note Music by Bill Coates OCRDocument6 pagesIan Shanahan - 31-Note Music by Bill Coates OCRIan ShanahanNo ratings yet

- Digital Lec 14Document25 pagesDigital Lec 14Sankalp PadhiNo ratings yet

- 4 Pra Reg ADocument1 page4 Pra Reg Adewi aprilianiNo ratings yet

- 2.6.5. B. 1. RPK TahunanDocument61 pages2.6.5. B. 1. RPK TahunancicipndarniNo ratings yet

- 13Document2 pages13mamidivinay kumarNo ratings yet

- Eduardo Garcia Maynez - Introducción A La Lógica Jurídica (1951)Document128 pagesEduardo Garcia Maynez - Introducción A La Lógica Jurídica (1951)Santiago Maldonado AquinoNo ratings yet

- 2019 Second HandNostalgiaDocument20 pages2019 Second HandNostalgiaOakley FielderNo ratings yet

- Secant Pile LayoutDocument1 pageSecant Pile LayoutSantha Raman R RNo ratings yet

- Lampiran Perawat Terampil Permenpan 25 2014Document11 pagesLampiran Perawat Terampil Permenpan 25 2014Rendra Na PradyatamaNo ratings yet

- Manual ACM 80 - Part 1 (English)Document20 pagesManual ACM 80 - Part 1 (English)JACK GREENHALGH100% (1)

- 1941 BarDocument210 pages1941 Barraj vadNo ratings yet

- KK 016Document1 pageKK 016Choky FhNo ratings yet

- Plano CUMMINS 6CT - 3919937 - MuestraDocument1 pagePlano CUMMINS 6CT - 3919937 - MuestraGUSTAVO LEZANONo ratings yet

- Adobe Scan 06-Oct-2021Document1 pageAdobe Scan 06-Oct-2021Gunika RazdanNo ratings yet

- S:a - .S O: - 3 C:o C:o C:o C:o Ci Ci Ci Ci ...... C:oDocument2 pagesS:a - .S O: - 3 C:o C:o C:o C:o Ci Ci Ci Ci ...... C:oMarsi BaniNo ratings yet

- ICE4010 Run Out The Guns! - Written in Blood (1998)Document67 pagesICE4010 Run Out The Guns! - Written in Blood (1998)Javi NigranNo ratings yet

- حل كويز ١Document16 pagesحل كويز ١Abdelaziz ElsherbinyNo ratings yet

- حل كويز ١Document16 pagesحل كويز ١Abdelaziz ElsherbinyNo ratings yet

- Mapa de FlujosDocument1 pageMapa de FlujosEylen Johana Garcia LopezNo ratings yet

- Hawkins Gerald S. - Stonehenge Decoded PDFDocument120 pagesHawkins Gerald S. - Stonehenge Decoded PDFJames Martin100% (6)

- 1960 02 6969683 Marlboro N JDocument5 pages1960 02 6969683 Marlboro N JOsmanNo ratings yet

- London Bridge Is Falling Down: Grade - BeginnerDocument1 pageLondon Bridge Is Falling Down: Grade - BeginnerastatineNo ratings yet

- London Bridge Is Falling Down: Grade - BeginnerDocument1 pageLondon Bridge Is Falling Down: Grade - Beginneruke.lelèNo ratings yet

- Adhid Suganda 211010045 Quiz LH PDFDocument2 pagesAdhid Suganda 211010045 Quiz LH PDFAdhid SugandaNo ratings yet

- T) 1ect: Vyrm Fy1Document3 pagesT) 1ect: Vyrm Fy1Ichal ZuhdyNo ratings yet

- Liza Lim (Ed. Ian Shanahan) - Lullaby (1988) OCRDocument3 pagesLiza Lim (Ed. Ian Shanahan) - Lullaby (1988) OCRIan ShanahanNo ratings yet

- RECongress 1980 Registration GuidebookDocument44 pagesRECongress 1980 Registration GuidebookLos Angeles Religious Education CongressNo ratings yet

- Hobsbawm-O Fazer-Se Da Classe Operria 1870-1914 Mundos Do Trabalho 279-304Document18 pagesHobsbawm-O Fazer-Se Da Classe Operria 1870-1914 Mundos Do Trabalho 279-304Ana Julia SchuenckNo ratings yet

- Gerson - The Little Enema BookDocument36 pagesGerson - The Little Enema BookBruno GonçalvesNo ratings yet

- สัตวานุกรมวิธานพร้อมตัวอย่างการศึกษาของไรDocument104 pagesสัตวานุกรมวิธานพร้อมตัวอย่างการศึกษาของไรOrmphipod WongkamhaengNo ratings yet

- Pace Survey Pp1 10Document10 pagesPace Survey Pp1 10Chris RowanNo ratings yet

- Loewenstein, K 1979 Teoría de La Constitución 2da Ed BarcelonaDocument312 pagesLoewenstein, K 1979 Teoría de La Constitución 2da Ed BarcelonapolicarpoxitlalyhernqndezNo ratings yet

- UntitledDocument236 pagesUntitledFelipe Bueno CrispimNo ratings yet

- REICH, W. As Origens Da Moral Sexual PDFDocument94 pagesREICH, W. As Origens Da Moral Sexual PDFRafaelSá100% (1)

- Mundos Do Trabalho Eric J. Hobsbawm Cap 11Document236 pagesMundos Do Trabalho Eric J. Hobsbawm Cap 11Nicolly ValleNo ratings yet

- Multiple Choice Practice Test PDFDocument104 pagesMultiple Choice Practice Test PDFKristopher CharlesNo ratings yet

- Roundel 1964-12 Vol 16 No 10Document35 pagesRoundel 1964-12 Vol 16 No 10TateNo ratings yet

- Zns-Preparation-Pdf 29-Oct-2022 09-41-19Document5 pagesZns-Preparation-Pdf 29-Oct-2022 09-41-19Cristians VivasNo ratings yet

- 36 04-05-70809631 SIEMENS-Certificados de Calidad-000Document13 pages36 04-05-70809631 SIEMENS-Certificados de Calidad-000Ing. Ricardo CeballosNo ratings yet

- DM-27 Part3Document14 pagesDM-27 Part3Adrian CantaragiuNo ratings yet

- Rahmani30 - OMR2018 - FilledDocument1 pageRahmani30 - OMR2018 - FilledAbdurraheem JamaliNo ratings yet

- Pages From Dorman Longs - Handbook For Constructional Engineers - 1906-118Document1 pagePages From Dorman Longs - Handbook For Constructional Engineers - 1906-118Fornvald TamasNo ratings yet

- Adobe Scan Dec 13, 2020Document8 pagesAdobe Scan Dec 13, 2020Ian SomerhalderNo ratings yet

- Obara 18 Pulgar ArpegioDocument2 pagesObara 18 Pulgar ArpegioShaRo TorrellesNo ratings yet

- ProjectBlueBook RB47 July17 1957Document57 pagesProjectBlueBook RB47 July17 1957ScriptKillerNo ratings yet

- Leader Test Instruments: Signal Genera TorDocument2 pagesLeader Test Instruments: Signal Genera TorFrancisco GarridoNo ratings yet

- Accord - Exacta - HLDocument23 pagesAccord - Exacta - HLPeter TurnšekNo ratings yet

- Accord - Exacta - E985 - ED825Document16 pagesAccord - Exacta - E985 - ED825Peter TurnšekNo ratings yet

- TPG Insulator FIADocument8 pagesTPG Insulator FIAApongNo ratings yet

- Panduan Tatacara Disiplin Sekolah Untuk GB Dan GuruDocument161 pagesPanduan Tatacara Disiplin Sekolah Untuk GB Dan GurusaraNo ratings yet

- 6000 Most Common Korean Words - For All TOPIK Levels PDFDocument232 pages6000 Most Common Korean Words - For All TOPIK Levels PDFZac67% (3)

- LogDocument67 pagesLogRudhi Al GhaisanNo ratings yet

- PienaDocument1 pagePienaMika Flores PedroNo ratings yet

- Nokia 2690 RM-635 Service ManualDocument18 pagesNokia 2690 RM-635 Service ManualEdgar Jose Aranguibel MorilloNo ratings yet

- Exposition Text Exercise ZenowskyDocument8 pagesExposition Text Exercise ZenowskyZenowsky Wira Efrata SianturiNo ratings yet

- Advanced Laser Al170: Instruction ManualDocument35 pagesAdvanced Laser Al170: Instruction ManualJuan Camilo100% (1)

- Grade 8 - EnglishDocument2 pagesGrade 8 - EnglishTCHR KIMNo ratings yet

- Cable Systems For High and Extra-High Voltage: Development, Manufacture, Testing, Installation and Operation of Cables and Their AccessoriesDocument1 pageCable Systems For High and Extra-High Voltage: Development, Manufacture, Testing, Installation and Operation of Cables and Their AccessorieseddisonfhNo ratings yet

- Union Metal SemiconductorDocument4 pagesUnion Metal SemiconductorskinhugoNo ratings yet

- Evolution of Media INDUSTRIAL ERADocument16 pagesEvolution of Media INDUSTRIAL ERAAlec Ruht MasulaNo ratings yet

- Evolis User ManualDocument28 pagesEvolis User ManualIonmadalin1000No ratings yet

- Review. Applications of Ecogeography and Geographic Information Systems in Conservation and Utilization of Plant Genetic ResourcesDocument11 pagesReview. Applications of Ecogeography and Geographic Information Systems in Conservation and Utilization of Plant Genetic ResourcesEmilio Patané SpataroNo ratings yet

- Ideal Vs Real OttoDocument5 pagesIdeal Vs Real Ottoa7med SoulimanNo ratings yet

- Communicative English Lab Manual 1643268175Document24 pagesCommunicative English Lab Manual 1643268175Dimple BhatiNo ratings yet

- 1.rle Rubrics For Case PresentationDocument2 pages1.rle Rubrics For Case PresentationKhristine EstosoNo ratings yet

- SOL-Logarithm, Surds and IndicesDocument12 pagesSOL-Logarithm, Surds and Indicesdevli falduNo ratings yet

- Of Personality Traits of Only and Sibling School Children in BeijingDocument14 pagesOf Personality Traits of Only and Sibling School Children in BeijingMuhammad Hamza AsgharNo ratings yet

- Bike Share ReportDocument16 pagesBike Share Reportsanjay975100% (1)

- Pitch Analysis PaperDocument7 pagesPitch Analysis PaperMunib MunirNo ratings yet

- BFISDocument1 pageBFISEverestNo ratings yet

- Om en A: F in Ite D Iffe Ren Ce-B Ase DN Um Eri Ca L M Eth Od SDocument426 pagesOm en A: F in Ite D Iffe Ren Ce-B Ase DN Um Eri Ca L M Eth Od SPrateek Kumar PandeyNo ratings yet

- Robots Part Two, The Illusion of Life (Week Three)Document34 pagesRobots Part Two, The Illusion of Life (Week Three)Vitor MacedoNo ratings yet

- Statistical MethodsDocument77 pagesStatistical MethodsGuruKPO100% (1)

- Introduction To Rhetorical Analysis: Week 1Document16 pagesIntroduction To Rhetorical Analysis: Week 1Will KurlinkusNo ratings yet

- BM Stake Holders Case Study 1st November 2023Document2 pagesBM Stake Holders Case Study 1st November 2023Arsath malik ArsathNo ratings yet

- Original Research PapersDocument13 pagesOriginal Research Papersrikaseo rikaNo ratings yet

- Focus On Teaching - Jim KnightDocument213 pagesFocus On Teaching - Jim KnightFernando TeixeiraNo ratings yet

- Submission Letter To LBUDocument46 pagesSubmission Letter To LBUramesh bajracharyaNo ratings yet

- Olympiad Problem 2Document3 pagesOlympiad Problem 2Đạt Nguyễn BáNo ratings yet

- Framework For A Digital Twin in Manufacturing Scope and RequirementsDocument3 pagesFramework For A Digital Twin in Manufacturing Scope and RequirementsJoão Vitor100% (1)