Professional Documents

Culture Documents

Rohini 55318033145

Uploaded by

arunbavaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Rohini 55318033145

Uploaded by

arunbavaCopyright:

Available Formats

ROHINI COLLEGE OF ENGINEERING & TECHNOLOGY

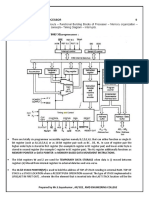

1.4 MEMORY STRUCTURE IN 8085 PROCESSOR

Memory Structure and Its Requirements:

Read/Write memory is a group of registers to store binary information. Fig 1.4.1

shows a typical R/W memory chip; it has “2n = M” registers (where n= no. of

address lines) and each can store N no. of bits.

It has N no. of bidirectional (or separate input-output) data lines.

It also has one Chip select (CS), and two control lines Read (RD) to enable the

output buffer and Write (WR) to enable the input buffer.

Figure. 1.4.1 shows the logic diagram of typical EPROM (Erasable Programmable

Read Only memory) Memory with “2n = M” registers (where n= no. of address

lines).

It has “n” no. of address lines, one Chip select (CS) and one Read (RD).

This memory chip must be programmed before it can be used as Read-Only

memory.

Figure 1.4.1 logic diagram of typical EPROM

[Source: “Microprocessor Architecture Programming and Application” by R.S. Gaonkar, page-91]

EE8551 MICROPROCESSOR AND MICROCONTROLLER

ROHINI COLLEGE OF ENGINEERING & TECHNOLOGY

The 8085 microprocessor uses a16-bit wide address bus for addressing memories

and I/O devices. Using 16-bit wide address bus it can access 216 = 64K bytes of memory

and I/O devices. The 64K addresses are to be assigned to memories and I/O devices for

their addressing. There are two schemes for the allocation of addresses to memories and

input / output devices:

1. Memory mapped I/O scheme.

2. I/O mapped I/O scheme.

Memory mapped I/O scheme:

In memory mapped I/O scheme there is only one address space.

Address space is defined as the set of all possible addresses that microprocessor

can generate.

Some addresses are assigned to memories and some addresses to I/O devices.

An I/O device is also treated as memory location and one address is assign to it.

Suppose that memory locations are assigned the addresses 2000 H to 24FF H then

each one address is assign to each memory location. The addresses for I/O devices

are different from the addresses which have been assigned to memories.

The addresses which have not been assigned to memories can be assigned to each

I/O device.

In this scheme all the data transfer instructions of the microprocessor can be valid

for data transfer from the memory location or I/O device whose address is in H-L

pair.

I/O mapped I/O scheme:

In this scheme the addresses assigned to memory location can also be assigned to

I/O devices.

Since the same address may be assigned to memory location or an I/O device, the

microprocessor must issue a signal to distinguish whether the address on the

address bus is for a memory location or an I/O device.

The 8085 issues an IO/M signal for this purpose.

Two extra instructions IN and OUT are used to address I/O devices.

EE8551 MICROPROCESSOR AND MICROCONTROLLER

ROHINI COLLEGE OF ENGINEERING & TECHNOLOGY

T1 T2 T3 T4

CLK

AD0

ALE

Figure 1.4.2 Timing Diagram: Transfer of Byte from Memory to Microprocessor

[Source: “Microprocessor Architecture Programming and Application” by R.S. Gaonkar, page-66]

Figure 1.4.2 shows the timing diagram of how a data byte is transferred from

memory to the microprocessor from which the need for demultiplexing the bus

AD0-AD7 becomes easier to understand.

This figure shows that the address on the high order bus (20H) remains on the bus

for three clock periods.

However, the low order address (05H) is lost after the first clock period.

This address needs to be latched and used for identifying the memory address.

If the bus AD7-AD0 is used to identify the memory location (2005H), the address

will change to 204FH after the first clock period.

Figure. 1.4.2 shows a schematic that uses a latch and the ALE signal to demultiplex

the bus. The bus AD7-AD0 is connected as input to latch 74LS373.

The ALE signal is connected to Enable (G) pin of the Latch, and the Output control

(OC) signal of the latch is grounded.

Figure 1.4.2 shows that the ALE goes high during T1. When the ALE is high, the

latch is transparent; that means output changes according to the input data.

During T1 output of the latch is 05H.

When ALE goes low, the data byte 05H is latched until the next ALE, and the

output of the latch represents the low-order address bus A7-A0 after the latching

operation.

EE8551 MICROPROCESSOR AND MICROCONTROLLER

ROHINI COLLEGE OF ENGINEERING & TECHNOLOGY

Figure 1.4.3 Schematic of Latching Low-Order Address Bus

[Source: “Microprocessor Architecture Programming and Application” by R.S. Gaonkar, page-82]

Generating Control Signals:

Figure 1.4.3 shows the RD (Read) as a control signal. Because this signal is used

both for reading memory and for reading an input device, it is necessary to generate

two different Read signals: one for memory and another for input. Similarly, two

separate Write signals must be generated.

This signal is Indeed with RD and WR signals by using the 74LS32 quadruple two-

input OR gates, as shown in Figure 1.4.3.

When both the input goes low , the outputs of the gates go low and generate MEMR

(memory Read) and MEMW (memory Write) control Signals.

EE8551 MICROPROCESSOR AND MICROCONTROLLER

ROHINI COLLEGE OF ENGINEERING & TECHNOLOGY

When IO/M goes high, it indicates the peripheral I/O operation. The table shows

that this signal is complemented and ANDed with RD and WR signals to generate

IOR (I/O Read) and IOW (I/O Write) control Signals.

IO/M RD WR Control Signal

0 0 1 Memory read

0 1 0 Memory write

1 0 1 I/O read

1 1 0 I/O write

Address Decoding:

The address of a memory location is sent out by the microprocessor. The

corresponding memory chip or I/O device is selected by a decoding circuit.

The decoding task can be performed by a decoder, a comparator, a bipolar PROM

or PLA (Programmed logic array).

For memory interfacing we can use Decoder IC 74LS138 which has G1, G2A and

G2B enable signals.

To enable 74LS138, G1 should be high, and G2A and G2B should be low. Also,

74LS138 has three select lines A, B & C. By applying proper logic to select ines

any one of the output cab be selected.

Where, 74LS138 has Y0, Y1, …. Y7 output lines. An output lines goes low when

it is selected. Other output lines remain high. Thus as shown in Table1.1 (Truth

table for 74LS138), when G1 is low or G2A is high or G2B is high, all output lines

become high.

Thus 74LS138 acts as decoder only when G1 is high, and G2A and G2B are low.

EE8551 MICROPROCESSOR AND MICROCONTROLLER

ROHINI COLLEGE OF ENGINEERING & TECHNOLOGY

INPUTS

OUTPUTS

ENABLE SELECT

G1 G2A G2B C B A Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7

X H H X X X H H H H H H H H

L X X X X X H H H H H H H H

H L L L L L L H H H H H H H

H L L L L H H L H H H H H H

H L L L H L H H L H H H H H

H L L L H H H H H L H H H H

H L L H L L H H H H L H H H

H L L H L H H H H H H L H H

H L L H H L H H H H H H L H

H L L H H H H H H H H H H L

Following fig shows the simple interfacing of 8K memory with 8085

Figure 1.4.4 simple interfacing of 8K memory with 8085

[Source: “Microprocessor Architecture Programming and Application” by R.S. Gaonkar, page-82]

EE8551 MICROPROCESSOR AND MICROCONTROLLER

You might also like

- 8085 PRJ Schematic 1Document44 pages8085 PRJ Schematic 1Jani ServiniNo ratings yet

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationFrom EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNo ratings yet

- 8085 Microprocessor Architecture and Programming-1Document92 pages8085 Microprocessor Architecture and Programming-1ShubhamNo ratings yet

- 68HC11Document5 pages68HC11Mohammad SalmanNo ratings yet

- 74ALS138 - DemultiplexerDocument6 pages74ALS138 - DemultiplexerDwp BhaskaranNo ratings yet

- Introduction To 8085 Microprocessor - Dr.P.YogeshDocument48 pagesIntroduction To 8085 Microprocessor - Dr.P.YogeshmailmeasddNo ratings yet

- Unit 3Document49 pagesUnit 3Durgesh GandiNo ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- EE309 MP Mod1 Ktunotes - inDocument17 pagesEE309 MP Mod1 Ktunotes - inDivya KrishnanNo ratings yet

- 8085 Note-3Document21 pages8085 Note-3Anonymous dxqddDNo ratings yet

- Interfacing With The ISA BusDocument12 pagesInterfacing With The ISA BusseyfiNo ratings yet

- UNIT-4: 8085 MicroprocessorDocument28 pagesUNIT-4: 8085 MicroprocessorMuthuvel MNo ratings yet

- 8085 MicroprocessorDocument38 pages8085 MicroprocessorPrateek PandeyNo ratings yet

- Hardware Architecture and Registers of the 8085 MicroprocessorDocument16 pagesHardware Architecture and Registers of the 8085 MicroprocessorCsNo ratings yet

- IO InterfacingDocument13 pagesIO InterfacingKrishna SaladiNo ratings yet

- Unit Ii Hardware Interfacing With Intel 8085Document44 pagesUnit Ii Hardware Interfacing With Intel 8085Basheer V.PNo ratings yet

- Unit 2 PDFDocument44 pagesUnit 2 PDFprashantvlsiNo ratings yet

- V K Mehta, Rohit Mehta - Principles of Power System (0, Schand Publisching)Document40 pagesV K Mehta, Rohit Mehta - Principles of Power System (0, Schand Publisching)Jaswanth KadaNo ratings yet

- Ee8551 8085 NotesDocument31 pagesEe8551 8085 NotesKUMARANSCRNo ratings yet

- Unit IDocument22 pagesUnit Iaravinth69601No ratings yet

- Mpi 11002Document21 pagesMpi 11002alkesh.eng0% (1)

- Unit 6 2Document25 pagesUnit 6 2Venkatesh RachaNo ratings yet

- 8086 Input/Output Interface ExplainedDocument17 pages8086 Input/Output Interface ExplainedMohammed MohsinNo ratings yet

- Assembly Language Lecture 5Document20 pagesAssembly Language Lecture 5Ayush SinghNo ratings yet

- Microprocessor 8085 NotesDocument48 pagesMicroprocessor 8085 NotesDewal ChaturvediNo ratings yet

- An Introduction to the Intel 8085 MicroprocessorDocument38 pagesAn Introduction to the Intel 8085 MicroprocessorDebashis ChakrabrtyNo ratings yet

- NEC 022 External Paper SolutionDocument13 pagesNEC 022 External Paper SolutionSachin PalNo ratings yet

- Lecture1423722820 PDFDocument101 pagesLecture1423722820 PDFdavNo ratings yet

- Architecture and Instruction Set of the 8-bit Microprocessor 8085Document80 pagesArchitecture and Instruction Set of the 8-bit Microprocessor 8085vsalaiselvamNo ratings yet

- Global Technical Campus: B. Tech II Year, IVSEM, Branch CSE I Mid Term Examination Microprocessors (4-Cs-1A)Document47 pagesGlobal Technical Campus: B. Tech II Year, IVSEM, Branch CSE I Mid Term Examination Microprocessors (4-Cs-1A)Anonymous xN4Z5QJU100% (1)

- Microprocessor PDFDocument30 pagesMicroprocessor PDFAmy OliverNo ratings yet

- Training ReportDocument18 pagesTraining Reportpiyushji125No ratings yet

- Efficient C Coding For AVRDocument15 pagesEfficient C Coding For AVRapi-3740925No ratings yet

- Introduction to Intel 8085 MicroprocessorDocument35 pagesIntroduction to Intel 8085 MicroprocessorVasudev Rao KonjetiNo ratings yet

- Unit 2Document15 pagesUnit 2Rajasekaran RNo ratings yet

- 8-bit Parallel I/O Device 8255 Programmable InterfaceDocument32 pages8-bit Parallel I/O Device 8255 Programmable Interfacesulekha saxenaNo ratings yet

- Presentation 1Document23 pagesPresentation 1khushalee.chavadaNo ratings yet

- Interfacing I/O Devices and PeripheralsDocument14 pagesInterfacing I/O Devices and PeripheralsHardikNo ratings yet

- Automatic Night Lamp With Morning AlarmDocument16 pagesAutomatic Night Lamp With Morning Alarms.reeganNo ratings yet

- EE8551-Mpmc Two MarksDocument23 pagesEE8551-Mpmc Two MarksmenakadevieceNo ratings yet

- 16-Bit Comparator Using 4-Bit ComparatorsDocument64 pages16-Bit Comparator Using 4-Bit Comparatorsssptc MagazineNo ratings yet

- Question Bank 1Document18 pagesQuestion Bank 1heligolwala1No ratings yet

- Intel 8085 Microprocessor Architecture GuideDocument18 pagesIntel 8085 Microprocessor Architecture GuideGautamNo ratings yet

- 8086 I/O Interfacing & Programming - Part I: Vtu - Edusat ProgrammeDocument19 pages8086 I/O Interfacing & Programming - Part I: Vtu - Edusat ProgrammeChethanNo ratings yet

- 8085 MicroprocessorDocument42 pages8085 MicroprocessorSameerNo ratings yet

- Mpi 11Document15 pagesMpi 11pparvapeterson11No ratings yet

- Basic IoDocument10 pagesBasic IoHoney GuptaNo ratings yet

- The 8086 INPUT/OUTPUT INTERFACEDocument17 pagesThe 8086 INPUT/OUTPUT INTERFACETejan T. KhalilNo ratings yet

- System BusDocument20 pagesSystem BusshyamNo ratings yet

- of Unit-1: Introduction To Microprocessor and Microprocessor 8085Document22 pagesof Unit-1: Introduction To Microprocessor and Microprocessor 8085abahynNo ratings yet

- Eec 503 PDFDocument22 pagesEec 503 PDFmohitNo ratings yet

- Features of 8051Document21 pagesFeatures of 8051Basheer V.PNo ratings yet

- 8085 PDocument31 pages8085 PAnish ChibNo ratings yet

- 13&15 Marks MP&MCDocument6 pages13&15 Marks MP&MCFranklin AlexNo ratings yet

- Select Fine Texture - 4878Document2 pagesSelect Fine Texture - 4878arunbavaNo ratings yet

- The Instantaneous Power Theory Team 2Document35 pagesThe Instantaneous Power Theory Team 2arunbavaNo ratings yet

- Kerala Public Service Commission: 29-04-2023 (Saturday) From 01:30 PM To 03:15 PMDocument3 pagesKerala Public Service Commission: 29-04-2023 (Saturday) From 01:30 PM To 03:15 PMJabir M AmeenNo ratings yet

- HV EarthingDocument3 pagesHV EarthingarunbavaNo ratings yet

- SEMIKRON - SKiiP - 11NAB126V1 - Drive RexrothDocument4 pagesSEMIKRON - SKiiP - 11NAB126V1 - Drive RexrothSergio MuriloNo ratings yet

- Field Monitoring and Automation Using Iot in AgricultureDocument114 pagesField Monitoring and Automation Using Iot in AgriculturedileeppatraNo ratings yet

- 05 - Electrical Part ListDocument6 pages05 - Electrical Part ListbernalgutierrezNo ratings yet

- Max 30102 Acc Ev KitDocument14 pagesMax 30102 Acc Ev Kitdgsn_88No ratings yet

- AUDIO VIDEO Sony Home Sistem Tavl1 Ver 10 200607Document210 pagesAUDIO VIDEO Sony Home Sistem Tavl1 Ver 10 200607Félix Takey KobataNo ratings yet

- ITW Cored Wire Catalogue ENG PDFDocument70 pagesITW Cored Wire Catalogue ENG PDFPhạm Văn ĐảngNo ratings yet

- NTE7420 Dual 4-Input Positive NAND Gate DatasheetDocument3 pagesNTE7420 Dual 4-Input Positive NAND Gate DatasheetRUSTAM YUWONONo ratings yet

- Physics Investigatory ProjectDocument19 pagesPhysics Investigatory ProjectYeshrun prakash Minz100% (3)

- Zelio Logic SR3B261BDDocument7 pagesZelio Logic SR3B261BDZoran SaricNo ratings yet

- BF244A BF244B BF244C: N-Channel RF AmplifierDocument6 pagesBF244A BF244B BF244C: N-Channel RF AmplifierMoisés MartínNo ratings yet

- Bandgap ReferencesDocument15 pagesBandgap ReferencesAyaz Masud SezanNo ratings yet

- Modeling & Simulation of DSTATCOM For Power Quality ImprovementDocument8 pagesModeling & Simulation of DSTATCOM For Power Quality ImprovementIJERDNo ratings yet

- Progress in Materials Science: I. Verboven, W. DefermeDocument31 pagesProgress in Materials Science: I. Verboven, W. DefermeMehar MajidNo ratings yet

- Band Theory1Document136 pagesBand Theory1Bhagyashree PaniNo ratings yet

- Cemento Conductor PDFDocument8 pagesCemento Conductor PDFLiz GutierrezNo ratings yet

- Planmeca: Power ConditionersDocument6 pagesPlanmeca: Power ConditionersAlexis A. Abreu A.No ratings yet

- SRAMDocument7 pagesSRAMRuqaiya KhanamNo ratings yet

- Mosfet Irfz44Document8 pagesMosfet Irfz44huynhsang1979No ratings yet

- Multisim Software Familiarization LabDocument11 pagesMultisim Software Familiarization LabsharedNo ratings yet

- Precision Thermocouple Measurement With The ADS1118: TI Precision Designs: Verified DesignDocument26 pagesPrecision Thermocouple Measurement With The ADS1118: TI Precision Designs: Verified DesignusuariofreeNo ratings yet

- T KM 366 Final Exam 2007Document3 pagesT KM 366 Final Exam 2007sebelasmetergmailcomNo ratings yet

- Low Cement Dense Castables / Calcestruzzi Densi A Basso Cemento / Betons Denses A Basse Teneur en Ciment / Dichte Lc-BetoneDocument2 pagesLow Cement Dense Castables / Calcestruzzi Densi A Basso Cemento / Betons Denses A Basse Teneur en Ciment / Dichte Lc-Betoneasad razaNo ratings yet

- Tga4516 TSDocument10 pagesTga4516 TScurzNo ratings yet

- 40 Makki Rev1Document10 pages40 Makki Rev1Akhil JNo ratings yet

- PVsyst Training Part IDocument96 pagesPVsyst Training Part IBarun BiswasNo ratings yet

- Communication Engineering Lab ManualDocument53 pagesCommunication Engineering Lab Manualtharunkumarreddy100% (1)

- Manualesco de Como Sobreviver Sem Agua e Sem Comida Por Tres Meses e MeioDocument10 pagesManualesco de Como Sobreviver Sem Agua e Sem Comida Por Tres Meses e MeiohugoeleuterioNo ratings yet

- 1.9.1.2-ALCRO - Arc Sprayed Iron-Chrome-Aluminum WireDocument4 pages1.9.1.2-ALCRO - Arc Sprayed Iron-Chrome-Aluminum WirechonubobbyNo ratings yet

- Tài liệu về PLC Liyan, Liyan PLC Manual.Document20 pagesTài liệu về PLC Liyan, Liyan PLC Manual.Nguyễn Văn Dũng100% (1)

- Nonlinear Peltier Effect in Semiconductors.Document4 pagesNonlinear Peltier Effect in Semiconductors.danielglezaNo ratings yet

- Hacking With Linux 2020:A Complete Beginners Guide to the World of Hacking Using Linux - Explore the Methods and Tools of Ethical Hacking with LinuxFrom EverandHacking With Linux 2020:A Complete Beginners Guide to the World of Hacking Using Linux - Explore the Methods and Tools of Ethical Hacking with LinuxNo ratings yet

- CompTIA Security+ All-in-One Exam Guide, Sixth Edition (Exam SY0-601)From EverandCompTIA Security+ All-in-One Exam Guide, Sixth Edition (Exam SY0-601)Rating: 5 out of 5 stars5/5 (1)

- Chip War: The Quest to Dominate the World's Most Critical TechnologyFrom EverandChip War: The Quest to Dominate the World's Most Critical TechnologyRating: 4.5 out of 5 stars4.5/5 (227)

- CompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002From EverandCompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002Rating: 5 out of 5 stars5/5 (1)

- Computer Science: A Concise IntroductionFrom EverandComputer Science: A Concise IntroductionRating: 4.5 out of 5 stars4.5/5 (14)

- CompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102From EverandCompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Rating: 5 out of 5 stars5/5 (2)

- Amazon Web Services (AWS) Interview Questions and AnswersFrom EverandAmazon Web Services (AWS) Interview Questions and AnswersRating: 4.5 out of 5 stars4.5/5 (3)

- Chip War: The Fight for the World's Most Critical TechnologyFrom EverandChip War: The Fight for the World's Most Critical TechnologyRating: 4.5 out of 5 stars4.5/5 (82)

- CompTIA A+ Certification All-in-One Exam Guide, Eleventh Edition (Exams 220-1101 & 220-1102)From EverandCompTIA A+ Certification All-in-One Exam Guide, Eleventh Edition (Exams 220-1101 & 220-1102)Rating: 5 out of 5 stars5/5 (2)

- Cancer and EMF Radiation: How to Protect Yourself from the Silent Carcinogen of ElectropollutionFrom EverandCancer and EMF Radiation: How to Protect Yourself from the Silent Carcinogen of ElectropollutionRating: 5 out of 5 stars5/5 (2)

- Dancing with Qubits: How quantum computing works and how it can change the worldFrom EverandDancing with Qubits: How quantum computing works and how it can change the worldRating: 5 out of 5 stars5/5 (1)

- Model-based System and Architecture Engineering with the Arcadia MethodFrom EverandModel-based System and Architecture Engineering with the Arcadia MethodNo ratings yet

- Samsung Galaxy S20 Learners Guide: A Comprehensive Manual to Help You Master Your Samsung Galaxy S20 and S20 Series like a ProFrom EverandSamsung Galaxy S20 Learners Guide: A Comprehensive Manual to Help You Master Your Samsung Galaxy S20 and S20 Series like a ProNo ratings yet

- Raspberry Pi | 101: The Beginner’s Guide with Basics on Hardware, Software, Programming & ProjecFrom EverandRaspberry Pi | 101: The Beginner’s Guide with Basics on Hardware, Software, Programming & ProjecNo ratings yet

- Samsung Galaxy S22 Ultra User Guide For Beginners: The Complete User Manual For Getting Started And Mastering The Galaxy S22 Ultra Android PhoneFrom EverandSamsung Galaxy S22 Ultra User Guide For Beginners: The Complete User Manual For Getting Started And Mastering The Galaxy S22 Ultra Android PhoneNo ratings yet

- Patterns in the Machine: A Software Engineering Guide to Embedded DevelopmentFrom EverandPatterns in the Machine: A Software Engineering Guide to Embedded DevelopmentRating: 5 out of 5 stars5/5 (1)

- Kindle Fire Owner's Manual: The ultimate Kindle Fire guide to getting started, advanced user tips, and finding unlimited free books, videos and apps on Amazon and beyondFrom EverandKindle Fire Owner's Manual: The ultimate Kindle Fire guide to getting started, advanced user tips, and finding unlimited free books, videos and apps on Amazon and beyondRating: 4.5 out of 5 stars4.5/5 (4)