Professional Documents

Culture Documents

AOZ3015PI

Uploaded by

Ban NeoCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

AOZ3015PI

Uploaded by

Ban NeoCopyright:

Available Formats

AOZ3015PI

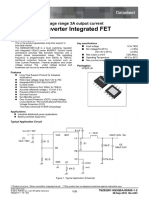

EZBuck™ 3 A Synchronous Buck Regulator

Not Recommended For New Designs

General Description Features

The AOZ3015PI is a high efficiency, easy to use, 3 A 4.5 V to 18 V operating input voltage range

synchronous buck regulator. The AOZ3015PI works from Synchronous Buck: 85 mΩ internal high-side switch

4.5 V to 18 V input voltage range, and provides up to 3 A and 50 mΩ internal low-side switch (at 12 V)

of continuous output current with an output voltage

PEM (pulse energy mode) enables >85% efficiency

s

adjustable down to 0.8 V.

with IOUT = 10 mA (VIN = 12 V, VOUT = 5 V)

n

ig

The AOZ3015PI comes in an exposed pad SO-8 350 µA supply current under typical application

package and is rated over a -40 °C to +85 °C operating Up to 95 % efficiency

es

ambient temperature range.

Internal soft-start

Output voltage adjustable to 0.8 V

D

Replacement Parts: 3 A continuous output current

ew

500 kHz PWM operation

AOZ6663DI

Cycle-by-cycle current limit

AOZ6683CI

N

Pre-bias start-up

Short-circuit protection

r Thermal shutdown

Fo

Exposed pad SO-8 package

d

Applications

de

Point of load DC/DC converters

LCD TV

en

Set top boxes

DVD and Blu-ray players/recorders

m

Cable modems

om

ec

Typical Application

R

VIN Efficiency (VIN = 12V) vs. Load Current

100

C1 CCC

ot

10µF

VIN VCC 90

VOUT

N

EN

AOZ3015PI LX

VOUT

Efficiency (%)

80

L1

R1

COMP C2, C3 5V OUTPUT

FB 22µF 70

3.3V OUTPUT

RC 2.5V OUTPUT

AGND PGND R2 1.8V OUTPUT

CC 60

50

0.01 0.1 1 10

Load Current (A)

Figure 1. 3 A Synchronous Buck Regulator, Fs = 500 kHz

Rev. 2.0 July 2013 www.aosmd.com Page 1 of 13

AOZ3015PI

Ordering Information

Part Number Ambient Temperature Range Package Environmental

AOZ3015PI -40 °C to +85 °C EPAD SO-8 Green Product

AOS Green Products use reduced levels of Halogens, and are also RoHS compliant.

Please visit www.aosmd.com/media/AOSGreenPolicy.pdf for additional information.

Pin Configuration

n s

PGND 1 8 VOUT

ig

es

VIN 2 7 EN

PAD

(LX)

D

AGND 3 6 COMP

VCC 4 5 FB

ew

Exposed Pad SO-8

N

(Top View)

r

Fo

Pin Description

d

de

Pin Number Pin Name Pin Function

1 PGND Power ground. PGND needs to be electrically connected to AGND.

en

2 VIN Supply voltage input. When VIN rises above the UVLO threshold and EN is logic high,

the device starts up.

m

3 AGND Analog ground. AGND is the reference point for controller section. AGND needs to be

electrically connected to PGND.

om

4 VCC Internal LDO output.

5 FB Feedback input. The FB pin is used to set the output voltage via a resistive voltage divider

ec

between the output and AGND.

6 COMP External loop compensation pin. Connect a RC network between COMP and AGND to

R

compensate the control loop.

7 EN Enable pin. Pull EN to logic high to enable the device. Pull EN to logic low to disable the

ot

device. If on/off control in not needed, connect EN to VIN and do not leave it open.

8 VOUT VOUT sense pin for protection purposes.

N

Exposed pad LX Switching node. LX is the drain of the internal power FETs. LX is used as the thermal pad

of the power stage.

Rev. 2.0 July 2013 www.aosmd.com Page 2 of 13

AOZ3015PI

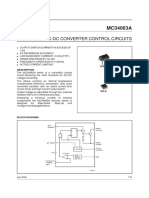

Block Diagram

VCC VIN

EN UVLO LDO OTP

& POR Regulator

Reference ISen

Softstart –

& Bias

Q1

ILimit

n s

ig

+

+ PWM

PWM Level

es

EAmp – Control

FB – Comp Shifter

Logic

+ + LX

FET

D

Output Q2

VOUT Sense

Driver

ew

COMP

500kHz

Oscillator

r N

Fo

PEM Control

Vref Logic

PWM/PEM Iinfo

d

Master Control

de

Iinfo

en

AGND PGND

m

om

Absolute Maximum Ratings Recommended Operating Conditions

Exceeding the Absolute Maximum Ratings may damage the The device is not guaranteed to operate beyond the Maximum

device. Recommended Operating Conditions.

ec

Parameter Rating Parameter Rating

Supply Voltage (VIN) 20 V Supply Voltage (VIN) 4.5 V to 18 V

R

LX to AGND -0.7 V to VIN +0.3 V Output Voltage Range 0.8 V to 0.85*VIN

ot

LX to AGND (<20 ns) -5 V to 22 V Ambient Temperature (TA) -40 °C to +85 °C

EN, VOUT to AGND -0.3 V to VIN +0.3 V Package Thermal Resistance

N

VCC, FB, COMP to AGND -0.3 V to 6.0 V Exposed Pad SO-8 (JA)(2) 50 °C/W

PGND to AGND -0.3 V to +0.3 V Note:

2. The value of JA is measured with the device mounted on a 1-in2

Junction Temperature (TJ) +150 °C

FR-4 board with 2 oz. Copper, in a still air environment with

Storage Temperature (TS) -65 °C to +150 °C TA = 25 °C. The value in any given application depends on the

ESD Rating(1) 2.0 kV user’s specific board design.

Note:

1. Devices are inherently ESD sensitive, handling precautions are

required. Human body model rating: 1.5 kΩ in series with 100 pF.

Rev. 2.0 July 2013 www.aosmd.com Page 3 of 13

AOZ3015PI

Electrical Characteristics

TA = 25 °C, VIN = VEN = 12 V, VOUT = 5 V unless otherwise specified(3)

Symbol Parameter Conditions Min. Typ. Max. Units

VIN Supply Voltage 4.5 18 V

VUVLO Input Under-Voltage Lockout VIN Rising 4

Threshold V

VIN Falling 3.7

IIN Supply Current (Quiescent) VIN = 12 V, VOUT = 5 V, IOUT = 0 A 350 500 µA

IOFF Shutdown Supply Current VEN = 0 V 1 2 µA

VFB Feedback Voltage TA = 25 °C 0.788 0.8 0.812 V

s

Load Regulation 0.5 %

n

Line Regulation 1 %

ig

IFB Feedback Voltage Input Current 200 nA

es

VEN EN Input Threshold Off Threshold 0.6

V

On Threshold 2

D

VHYS EN Input Hysteresis 200 mV

EN Leakage Current µA

ew

1

SS Time 5 ms

MODULATOR

N

fO Frequency IOUT = 2 A 400 500 600 kHz

DMAX Maximum Duty Cycle r 85 %

Fo

TMIN Controllable Minimum On Time IOUT = 2 A 200 ns

Current Sense Transconductance(4) 8 A/ V

d

Error Amplifier Transconductance 200 µA / V

de

PROTECTION

ILIM Current Limit 3.5 4 A

en

Over-Temperature Shutdown Limit TJ Rising 150

°C

TJ Falling 100

m

VOVP Over-Voltage Protection Off Threshold 960

mV

On Threshold 860

om

OUTPUT STAGE

High-Side Switch On-Resistance VIN = 12 V 85 mΩ

ec

Low-Side Switch On-Resistance VIN = 12 V 50 mΩ

R

Note:

3. Specification in BOLD indicate an ambient temperature range of -40 °C to +85 °C. These specifications are not guaranteed to operate beyond the

Maximum Operating ratings.

ot

4. These specifications are guaranteed by design.

N

Rev. 2.0 July 2013 www.aosmd.com Page 4 of 13

AOZ3015PI

Typical Performance Characteristics

Circuit of Figure 1. TA = 25 °C, VIN = VEN = 12 V, VOUT = 3.3 V unless otherwise specified.

Light Load to Heavy Load Operation Heavy Load to Light Load

VLX VLX

10V/div 10V/div

Vo

Vo

s

0.2V/div

0.2V/div

n

ig

IL

IL 1A/div

es

1A/div

D

20µs/div 20µs/div

ew

Short Circuit Protection Short Circuit Recovery

N

VLX

10V/div VLX

r 10V/div

Fo

Vo

2V/div

Vo

d

2V/div

de

IL

2A/div IL

en

2A/div

m

20ms/div 20ms/div

om

Start Up to Full Load 50 % to 100 % Load Transient

ec

Vin

R

5V/div

ot

Vo

2V/div

N

Vo

0.2V/div

Io

2A/div Io

2A/div

5ms/div 100µs/div

Rev. 2.0 July 2013 www.aosmd.com Page 5 of 13

AOZ3015PI

Detailed Description The inductor current flows from the input through the

inductor to the output. When the current signal exceeds

The AOZ3015PI is a current-mode step down regulator

the error voltage, the high-side switch is off. The inductor

with an integrated high-side PMOS switch and a low-side

current is freewheeling through the internal low-side

NMOS switch. The AOZ3015PI operates from a 4.5 V to

N-MOSFET switch to output. The internal adaptive FET

18 V input voltage range and supplies up to 3 A of load

driver guarantees no turn on overlap of both the

current. Features include enable control, power-on reset,

high-side and the low-side switch.

input under voltage lockout, output over voltage

protection, internal soft-start and thermal shut down. Compared with regulators using freewheeling Schottky

diodes, the AOZ3015PI uses a freewheeling NMOSFET

The AOZ3015PI is available in an exposed pad SO-8

to realize synchronous rectification. This greatly

package.

improves the converter efficiency and reduces power

s

loss in the low-side switch.

n

Enable and Soft Start

ig

The AOZ3015PI has an internal soft-start feature to limit The AOZ3015PI uses a P-Channel MOSFET as the

in-rush current and ensure the output voltage ramps up high-side switch. This saves the bootstrap capacitor

es

smoothly to regulation voltage. The soft start process normally seen in a circuit using an NMOS switch.

begins when the input voltage rises to 4 V and voltage on

D

the EN pin is HIGH. In the soft start process, the Output Voltage Programming

output voltage is typically ramped to regulation voltage in Output voltage can be set by feeding back the output to

ew

5 ms. The 5 ms soft-start pin time is set internally. the FB pin using a resistor divider network as shown in

Figure 1. The resistor divider network includes R1 and

The EN pin of the AOZ3015PI is active high. Connect the

R2. Usually, a design is started by picking a fixed R2

N

EN pin to VIN if the enable function is not used. Pulling

value and calculating the required R1 with the equation

EN to ground will disable the AOZ3015PI. Do not leave

below:

EN open. The voltage on the EN pin must be above 2 V r

Fo

to enable the AOZ3015PI. When the EN pin voltage falls R 1

below 0.6 V, the AOZ3015PI is disabled. V O = 0.8 1 + -------

R 2

d

Light Load and PWM Operation

de

Under low output current settings, the AOZ3015PI will Some standard value of R1 and R2 for the most common

operate with pulse energy mode to obtain high efficiency. output voltages are listed in Table 1.

In pulse energy mode, the PWM will not turn off until the

en

inductor current reaches to 800 mA and the current Table 1.

signal exceeds the error voltage.

R1 (kΩ) R2 (kΩ)

m

VO (V)

Steady-State Operation 0.8 1.0 Open

om

Under heavy load steady-state conditions, the converter 1.2 4.99 10

operates in fixed frequency and Continuous-Conduction

1.5 10 11.5

Mode (CCM).

ec

1.8 12.7 10.2

The AOZ3015PI integrates an internal P-MOSFET as the 2.5 21.5 10

R

high-side switch. Inductor current is sensed by amplifying

3.3 31.1 10

the voltage drop across the drain to source of the high

ot

side power MOSFET. Output voltage is divided down by 5.0 52.3 10

the external voltage divider at the FB pin. The difference

N

of the FB pin voltage and reference voltage is amplified The combination of R1 and R2 should be large enough to

by the internal transconductance error amplifier. The avoid drawing excessive current from the output, which

error voltage, which shows on the COMP pin, is will cause power loss.

compared against the current signal, which is the sum of

inductor current signal and ramp compensation signal, at

the PWM comparator input. If the current signal is less

than the error voltage, the internal high-side switch is on.

Rev. 2.0 July 2013 www.aosmd.com Page 6 of 13

AOZ3015PI

Protection Features Application Information

The AOZ3015PI has multiple protection features to The basic AOZ3015PI application circuit is show in

prevent system circuit damage under abnormal Figure 1. Component selection is explained below.

conditions.

Input Capacitor

Over Current Protection (OCP) The input capacitor must be connected to the VIN pin and

The sensed inductor current signal is also used for over the PGND pin of AOZ3015PI to maintain steady input

current protection. Since the AOZ3015PI employs peak voltage and filter out the pulsing input current. The

current mode control, the COMP pin voltage is voltage rating of input capacitor must be greater than

proportional to the peak inductor current. The COMP pin maximum input voltage plus ripple voltage.

voltage is limited to be between 0.4 V and 3.1 V internally.

s

The peak inductor current is automatically limited The input ripple voltage can be approximated by

n

cycle-by-cycle. equation below:

ig

When the output is shorted to ground under fault IO VO VO

V IN = ----------------- 1 – --------- ---------

es

conditions, the inductor current slowly decays during a f C IN V IN V IN

switching cycle because the output voltage is 0 V.

D

To prevent catastrophic failure, a secondary current limit Since the input current is discontinuous in a buck

is designed inside the AOZ3015PI. The measured converter, the current stress on the input capacitor is

ew

inductor current is compared against a preset voltage another concern when selecting the capacitor. For a buck

which represents the current limit. When the output circuit, the RMS value of input capacitor current can be

current is greater than the current limit, the high side calculated by:

N

switch will be turned off. The converter will initiate a soft

start once the over-current condition is resolved. VO VO

I CIN_RMS = I O --------

r - 1 – --------

-

V IN V IN

Fo

OCP (typ) vs. Input Voltage

3.9

if we let m equal the conversion ratio:

d

3.7

VO

de

3.5

--------

- = m

OCP Average (A)

3.3

V IN

en

3.1

The relationship between the input capacitor RMS

current and voltage conversion ratio is calculated and

m

2.9

shown in Figure 2 below. It can be seen that when VO is

2.7

om

half of VIN, CIN is under the worst current stress. The

2.5 worst current stress on CIN is 0.5 x IO.

5 7 9 11 13 15 17

0.5

ec

Input Voltage (V)

0.4

R

Power-On Reset (POR)

A power-on reset circuit monitors the input voltage. When

ICIN_RMS(m) 0.3

ot

the input voltage exceeds 4 V, the converter starts

IO

operation. When input voltage falls below 3.7 V, the

N

0.2

converter will be shut down.

0.1

Thermal Protection

An internal temperature sensor monitors the junction 0

temperature. The sensor shuts down the internal control 0 0.5 1

circuit and high side PMOS if the junction temperature m

exceeds 150 ºC. The regulator will restart automatically

under the control of the soft-start circuit when the junction Figure 2. ICIN vs. Voltage Conversion Ratio

temperature decreases to 100 ºC.

Rev. 2.0 July 2013 www.aosmd.com Page 7 of 13

AOZ3015PI

For reliable operation and best performance, the input Output Capacitor

capacitors must have a current rating higher than The output capacitor is selected based on the DC output

ICIN_RMS at the worst operating conditions. Ceramic voltage rating, output ripple voltage specification and

capacitors are preferred for input capacitors because of ripple current rating.

their low ESR and high current rating. Depending on the

application circuits, other low ESR tantalum capacitors The selected output capacitor must have a higher rated

may be used. When selecting ceramic capacitors, X5R or voltage specification than the maximum desired output

X7R type dielectric ceramic capacitors should be used voltage including ripple. De-rating needs to be

for their better temperature and voltage characteristics. considered for long term reliability.

Note that the ripple current rating from capacitor

manufactures are based on a certain operating life time. Output ripple voltage specification is another important

Further de-rating may need to be considered for long factor for selecting the output capacitor. In a buck

s

term reliability. converter circuit, output ripple voltage is determined by

n

inductor value, switching frequency, output capacitor

ig

Inductor value and ESR. It can be calculated by the equation

below:

es

The inductor is used to supply constant current to output

when it is driven by a switching voltage. For a given input 1

and output voltage, inductance and switching frequency V O = I L ESR CO + -------------------------

8fC

D

together decide the inductor ripple current, which is: O

ew

VO VO where,

I L = ----------- 1 – --------

- CO is output capacitor value, and

fL V IN

ESRCO is the equivalent series resistance of the output

N

capacitor.

The peak inductor current is:

r

When a low ESR ceramic capacitor is used as the output

Fo

I L

I Lpeak = I O + -------- capacitor, the impedance of the capacitor at the switching

2 frequency dominates. Output ripple is mainly caused by

capacitor value and inductor ripple current. The output

d

High inductance gives low inductor ripple current but ripple voltage calculation can be simplified to:

de

requires larger size inductor to avoid saturation. Low 1

ripple current reduces inductor core losses. It also V O = I L -------------------------

8fC

en

reduces RMS current through inductor and switches, O

which results in less conduction loss. Usually, peak to

If the impedance of ESR at switching frequency

m

peak ripple current on the inductor is designed to be

20 % to 40 % of output current. dominates, the output ripple voltage is mainly decided by

capacitor ESR and inductor ripple current. The output

om

When selecting the inductor, confirm it is able to handle ripple voltage calculation can be further simplified to:

the peak current without saturation at the highest

V O = I L ESR CO

ec

operating temperature.

The inductor takes the highest current in a buck circuit.

R

For lower output ripple voltage across the entire

The conduction loss on the inductor needs to be checked operating temperature range, X5R or X7R dielectric type

for thermal and efficiency requirements. of ceramic, or other low ESR tantalum capacitors are

ot

recommended as output capacitors.

Surface mount inductors in different shape and styles are

N

available from Coilcraft, Elytone and Murata. Shielded In a buck converter, output capacitor current is

inductors are small and radiate less EMI noise. However, continuous. The RMS current of output capacitor is

they cost more than unshielded inductors. The choice decided by the peak to peak inductor ripple current. It can

depends on EMI requirement, price and size. be calculated by:

I L

I CO_RMS = ----------

12

Rev. 2.0 July 2013 www.aosmd.com Page 8 of 13

AOZ3015PI

Usually, the ripple current rating of the output capacitor is The zero given by the external compensation network,

a smaller issue because of the low current stress. When capacitor CC and resistor RC, is located at:

the buck inductor is selected to be very small and

inductor ripple current is high, the output capacitor could 1

f Z2 = -----------------------------------

be overstressed. 2 C C R C

Loop Compensation To design the compensation circuit, a target crossover

The AOZ3015PI employs peak current mode control for frequency fC to close the loop must be selected. The

ease of use and fast transient response. Peak current system crossover frequency is where the control loop

mode control eliminates the double pole effect of the has unity gain. The crossover is the also called the

output L&C filter. It also greatly simplifies the converter bandwidth. Generally a higher bandwidth

compensation loop design.

s

means faster response to load transients. However, the

bandwidth should not be too high because of system

n

With peak current mode control, the buck power stage stability concern. When designing the compensation

ig

can be simplified to be a one-pole and one-zero system loop, converter stability under all line and load condition

in frequency domain. The pole is dominant pole can be

es

must be considered.

calculated by:

Usually, it is recommended to set the bandwidth to be

D

1

f P1 = ----------------------------------- equal or less than 1/10 of the switching frequency.

2 C O R L

ew

The strategy for choosing RC and CC is to set the cross

The zero is a ESR zero due to the output capacitor and over frequency with RC and set the compensator zero

its ESR. It is can be calculated by: with CC. Using selected crossover frequency, fC, to

N

calculate RC:

1

f Z1 = ------------------------------------------------ r

2 C O ESR CO VO 2 C C

Fo

R C = f C ---------- -----------------------------

-

where; V G G

FB EA CS

CO is the output filter capacitor,

d

where;

RL is load resistor value, and

de

fC is the desired crossover frequency. For best performance,

ESRCO is the equivalent series resistance of output capacitor. fC is set to be about 1/10 of the switching frequency;

en

VFB is 0.8V,

The compensation design shapes the converter control

loop transfer function for the desired gain and phase. GEA is the error amplifier transconductance, which is

200 x 10-6 A/V, and

m

Several different types of compensation networks can be

used with the AOZ3015PI. For most cases, a series GCS is the current sense circuit transconductance, which is

om

capacitor and resistor network connected to the 8 A/V

COMP pin sets the pole-zero and is adequate for a stable

high-bandwidth control loop. The compensation capacitor CC and resistor RC together

ec

make a zero. This zero is put somewhere close to the

In the AOZ3015PI, FB and COMP are the inverting input dominate pole fp1 but lower than 1/5 of the selected

crossover frequency. CC can is selected by:

R

and the output of the internal error amplifier. A series

R and C compensation network connected to COMP

1

provides one pole and one zero. The pole is: C C = -----------------------------------

ot

2 R C f P1

G EA

N

f P2 = -------------------------------------------

2 C C G VEA The above equation can be simplified to:

where; CO RL

C C = ---------------------

GEA is the error amplifier transconductance, which is 200 x 10-6 RC

A/V,

GVEA is the error amplifier voltage gain, which is 500 V/V, and An easy-to-use application software which helps to

design and simulate the compensation loop can be found

CC is the compensation capacitor in Figure 1.

at www.aosmd.com.

Rev. 2.0 July 2013 www.aosmd.com Page 9 of 13

AOZ3015PI

Thermal Management and Layout Layout Considerations

Considerations The AOZ3015PI is an exposed pad SO-8 package.

In the AOZ3015PI buck regulator circuit, high pulsing Several layout tips are listed for the best electric and

current flows through two circuit loops. The first loop thermal performance.

starts from the input capacitors, to the VIN pin, to the

1. The exposed pad (LX) is connected to the internal

LX pad, to the filter inductor, to the output capacitor and

PFET and NFET drains. Connected a large copper

load, and then returns to the input capacitor through

plane to the LX pin to help thermal dissipation.

ground. Current flows in the first loop when the high side

switch is on. The second loop starts from the inductor, 2. Do not use a thermal relief connection to the VIN pin

to the output capacitors and load, to the low side or the PGND pin. Pour a maximized copper area to

NMOSFET. Current flows in the second loop when the the PGND pin and the VIN pin to help thermal

s

low side NMOSFET is on. dissipation.

n

3. The input capacitor should be connected as close as

ig

In PCB layout, minimizing the area of the two loops will

possible to the VIN pin and the PGND pin.

reduce the noise of the circuit and improves efficiency.

es

A ground plane is strongly recommended to connect the 4. A ground plane is preferred. If a ground plane is not

input capacitor, the output capacitor, and the PGND pin used, separate PGND from AGND and only connect

D

of the AOZ3015PI. them at one point to avoid the PGND pin noise

coupling to the AGND pin.

In the AOZ3015PI buck regulator circuit, the major power

ew

5. Make the current trace from the LX pad to L to Co to

dissipating components are the AOZ3015PI and the

the PGND as short as possible.

output inductor. The total power dissipation of converter

N

circuit can be measured by input power minus output 6. Pour copper plane on all unused board area and

power: connect it to stable DC nodes, like VIN, GND or

r VOUT.

P total_loss = V IN I IN – V O I O

Fo

7. Keep sensitive signal trace away from the LX pad.

The power dissipation of the inductor can be

d

approximately calculated by the output current and DCR

value of the inductor:

de

P inductor_loss = IO2 R inductor 1.1

en

The actual junction temperature can be calculated by the

m

power dissipation in the AOZ3015PI and the thermal

impedance from junction to ambient:

om

T junction = P total_loss – P inductor_loss JA

ec

The maximum junction temperature of the AOZ3015PI is

150 ºC, which limits the maximum load current capability.

R

The thermal performance of the AOZ3015PI is strongly

affected by the PCB layout. Care should be taken during

ot

the design process to ensure that the IC will operate

under the recommended environmental conditions.

N

Rev. 2.0 July 2013 www.aosmd.com Page 10 of 13

AOZ3015PI

Package Dimensions, SO-8 EP1

Gauge plane

D0 0.2500

C

L1

E2 E3 E1 E

n s

ig

es

D

D1 L1'

Note 5

D

θ

ew

7 (4x)

N

A2 A

r

Fo

B e

A1

Dimensions in millimeters Dimensions in inches

d

Symbols Min. Nom. Max. Symbols Min. Nom. Max.

de

RECOMMENDED LAND PATTERN A 1.40 1.55 1.70 A 0.055 0.061 0.067

A1 0.00 0.05 0.10 A1 0.000 0.002 0.004

en

3.70

A2 1.40 1.50 1.60 A2 0.055 0.059 0.063

B 0.31 0.406 0.51 B 0.012 0.016 0.020

m

C 0.17 — 0.25 C 0.007 — 0.010

2.20 D 4.80 4.96 5.00 D 0.189 0.195 0.197

om

D0 3.20 3.40 3.60 D0 0.126 0.134 0.142

5.74 D1 3.10 3.30 3.50 D1 0.122 0.130 0.138

E 5.80 6.00 6.20 E 0.228 0.236 0.244

ec

2.71

e — 1.27 — e — 0.050 —

2.87 E1 3.80 3.90 4.00 E1 0.150 0.153 0.157

R

E2 2.21 2.41 2.61 E2 0.087 0.095 0.103

E3 0.40 REF E3 0.016 REF

ot

L 0.40 0.95 1.27 L 0.016 0.037 0.050

N

0.80 y — — 0.10 y — — 0.004

1.27 θ 0° 3° 8° θ 0° 3° 8°

0.635

UNIT: mm | L1–L1' | — 0.04 0.12 | L1–L1' | — 0.002 0.005

L1 1.04 REF L1 0.041 REF

Notes:

1. Package body sizes exclude mold flash and gate burrs.

2. Dimension L is measured in gauge plane.

3. Tolerance 0.10mm unless otherwise specified.

4. Controlling dimension is millimeter, converted inch dimensions are not necessarily exact.

5. Die pad exposure size is according to lead frame design.

6. Followed from JEDEC MS-012

Rev. 2.0 July 2013 www.aosmd.com Page 11 of 13

AOZ3015PI

Tape and Reel Dimensions, SO-8 EP1

Carrier Tape P1

D1

P2

T

E1

E2 E

n s

B0

ig

K0 D0

A0 P0 Feeding Direction

es

UNIT: mm

Package A0 B0 K0 D0 D1 E E1 E2 P0 P1 P2 T

D

SO-8 6.40 5.20 2.10 1.60 1.50 12.00 1.75 5.50 8.00 4.00 2.00 0.25

(12mm) ±0.10 ±0.10 ±0.10 ±0.10 ±0.10 ±0.10 ±0.10 ±0.10 ±0.10 ±0.10 ±0.10 ±0.10

ew

N

Reel

W1

r

Fo

S

G

d

de

N

M K

V

en

R

m

H

om

W

UNIT: mm

Tape Size Reel Size M N W W1 H K S G R V

ec

12mm ø330 ø330.00 ø97.00 13.00 17.40 ø13.00 10.60 2.00 — — —

±0.50 ±0.10 ±0.30 ±1.00 +0.50/-0.20 ±0.50

R

ot

Leader/Trailer and Orientation

N

Trailer Tape Components Tape Leader Tape

300mm min. or Orientation in Pocket 500mm min. or

75 empty pockets 125 empty pockets

Rev. 2.0 July 2013 www.aosmd.com Page 12 of 13

AOZ3015PI

Part Marking

Z3015PI

Part Number Code

FAYWLT

ns

ig

Fab & Assembly Location Assembly Lot Code

es

Year & Week Code

D

ew

r N

Fo

d

de

LEGAL DISCLAIMER

en

Applications or uses as critical components in life support devices or systems are not authorized. AOS does not

m

assume any liability arising out of such applications or uses of its products. AOS reserves the right to make

changes to product specifications without notice. It is the responsibility of the customer to evaluate suitability of the

om

product for their intended application. Customer shall comply with applicable legal requirements, including all

applicable export control rules, regulations and limitations.

ec

AOS' products are provided subject to AOS' terms and conditions of sale which are set forth at:

http://www.aosmd.com/terms_and_conditions_of_sale

R

LIFE SUPPORT POLICY

ot

ALPHA AND OMEGA SEMICONDUCTOR PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL

N

COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS.

As used herein:

1. Life support devices or systems are devices or 2. A critical component in any component of a life

systems which, (a) are intended for surgical implant into support, device, or system whose failure to perform can

the body or (b) support or sustain life, and (c) whose be reasonably expected to cause the failure of the life

failure to perform when properly used in accordance support device or system, or to affect its safety or

with instructions for use provided in the labeling, can be effectiveness.

reasonably expected to result in a significant injury of

the user.

Rev. 2.0 July 2013 www.aosmd.com Page 13 of 13

You might also like

- KA3842Document7 pagesKA3842QXNNo ratings yet

- General Description Features: 28V/10A Synchronous Ezbuck RegulatorDocument15 pagesGeneral Description Features: 28V/10A Synchronous Ezbuck RegulatorholinsunNo ratings yet

- 90W Smps For Monitors With Standby Function: AN1132 Application NoteDocument12 pages90W Smps For Monitors With Standby Function: AN1132 Application NoteGrzegorz WegnerNo ratings yet

- AOZ1267QI-01: General Description FeaturesDocument16 pagesAOZ1267QI-01: General Description Featuresvictory_1410No ratings yet

- For New Designs: AOZ1051PIDocument14 pagesFor New Designs: AOZ1051PISelmar CavalcantiNo ratings yet

- For New Designs: AOZ1051PIDocument14 pagesFor New Designs: AOZ1051PIGioVoTamNo ratings yet

- AOZ3015AIDocument14 pagesAOZ3015AIIcomNo ratings yet

- Features Description: LT8631 100V, 1A Synchronous Micropower Step-Down RegulatorDocument26 pagesFeatures Description: LT8631 100V, 1A Synchronous Micropower Step-Down RegulatorAle NqnNo ratings yet

- Acer Al1916w Psu-Inverter dt830Document55 pagesAcer Al1916w Psu-Inverter dt830LuisNo ratings yet

- PWM Control 2-3A Step-Down Converter Technical SpecificationsDocument7 pagesPWM Control 2-3A Step-Down Converter Technical SpecificationsDimas BarretoNo ratings yet

- Bd9g341aefj LBDocument30 pagesBd9g341aefj LBFantazsta White Trash.No ratings yet

- DC-DC Converter Control Circuits: Description DIP-8Document15 pagesDC-DC Converter Control Circuits: Description DIP-8Полецкий ОлегNo ratings yet

- DC-DC Converter Control Circuit DatasheetDocument16 pagesDC-DC Converter Control Circuit DatasheetKrittapop SaleechanNo ratings yet

- UC3842B 43 44 45. UC2842-3-4-5pdf PDFDocument15 pagesUC3842B 43 44 45. UC2842-3-4-5pdf PDFVictor Hugo Pulido QuiñonesNo ratings yet

- Controller IC For Current Resonant Type Switching Power Supply With Half-Bridge Resonance, High Efficiency and Low NoiseDocument2 pagesController IC For Current Resonant Type Switching Power Supply With Half-Bridge Resonance, High Efficiency and Low Noisejoil alvesNo ratings yet

- 3842a DatasheetDocument8 pages3842a DatasheetVịnh DemoNo ratings yet

- AOZ1038DIDocument15 pagesAOZ1038DIjiledarNo ratings yet

- XC9110Document35 pagesXC9110Loc ManucianNo ratings yet

- 2A, 380 KHZ Step-Down Converter: The Future of Analog Ic TechnologyDocument10 pages2A, 380 KHZ Step-Down Converter: The Future of Analog Ic TechnologyAnonymous aP1FSUPoNo ratings yet

- AozDocument16 pagesAozAndreNo ratings yet

- 28V/10A Synchronous Buck Regulator with 0.8V OutputDocument15 pages28V/10A Synchronous Buck Regulator with 0.8V OutputРоман ІкалюкNo ratings yet

- 2SC3280 SILICON NPN TRIPLE DIFFUSED POWER AMP AUDIO AMPDocument2 pages2SC3280 SILICON NPN TRIPLE DIFFUSED POWER AMP AUDIO AMPLaZúu DomiciliosNo ratings yet

- Aoz2262qi 1Document16 pagesAoz2262qi 1Eric ArcherNo ratings yet

- VNB10N07/K10N07FM VNP10N07FI/VNV10N07: "Omnifet": Fully Autoprotected Power MosfetDocument14 pagesVNB10N07/K10N07FM VNP10N07FI/VNV10N07: "Omnifet": Fully Autoprotected Power MosfetEduardo MontoyaNo ratings yet

- SSC9512SDocument2 pagesSSC9512SSamaro RodriguezNo ratings yet

- 1.5A Step Down Switching RegulatorDocument12 pages1.5A Step Down Switching Regulatorjavier ortizNo ratings yet

- AOZ1268QI 01 AlphaOmegaSemiconductorsDocument15 pagesAOZ1268QI 01 AlphaOmegaSemiconductorsrcgruwanNo ratings yet

- TB9000AFGDocument11 pagesTB9000AFGLoengrin MontillaNo ratings yet

- General Description Features: 28V/6A Synchronous Ezbuck RegulatorDocument15 pagesGeneral Description Features: 28V/6A Synchronous Ezbuck RegulatorholinsunNo ratings yet

- Flexible Step-Down Switching Regulators With Built-In Power MOSFETDocument26 pagesFlexible Step-Down Switching Regulators With Built-In Power MOSFETNgân Hàng Ngô Mạnh TiếnNo ratings yet

- EM5106 3A LDO Regulator Technical OverviewDocument10 pagesEM5106 3A LDO Regulator Technical OverviewSib Repair CenterNo ratings yet

- General Description Features: 28V/12A Synchronous Ezbuck RegulatorDocument16 pagesGeneral Description Features: 28V/12A Synchronous Ezbuck RegulatorholinsunNo ratings yet

- VNP20N07FI VNB20N07/VNV20N07: "Omnifet": Fully Autoprotected Power MosfetDocument13 pagesVNP20N07FI VNB20N07/VNV20N07: "Omnifet": Fully Autoprotected Power MosfetНаталія ЛіськевичNo ratings yet

- Hxh2kz TCS9708 DatasheetDocument9 pagesHxh2kz TCS9708 DatasheetprreNo ratings yet

- Features: Lt1375/Lt1376 1.5A, 500Khz Step-Down Switching RegulatorsDocument29 pagesFeatures: Lt1375/Lt1376 1.5A, 500Khz Step-Down Switching RegulatorsSergio MuriloNo ratings yet

- Ame5269 AmeDocument18 pagesAme5269 AmeCharles PNo ratings yet

- TNY278PN Design For 5V, 2A Adaptor (Rev-3) : No Y Cap Design For 10W Very Low No - Load Power Consumption High EfficiencyDocument16 pagesTNY278PN Design For 5V, 2A Adaptor (Rev-3) : No Y Cap Design For 10W Very Low No - Load Power Consumption High EfficiencyCorban MihaiNo ratings yet

- 7915Document13 pages7915ysfhkNo ratings yet

- Niko-Sem: 0.8A Fixed and Adjustable Low Dropout Linear Regulator (LDO)Document6 pagesNiko-Sem: 0.8A Fixed and Adjustable Low Dropout Linear Regulator (LDO)Lite HhhNo ratings yet

- Apu8836 3Document6 pagesApu8836 3dataNo ratings yet

- EE-SX461-P11: Photomicrosensor (Transmissive)Document106 pagesEE-SX461-P11: Photomicrosensor (Transmissive)Daniel NicholasNo ratings yet

- L6565 Sample SchematicsDocument9 pagesL6565 Sample SchematicsНикита АндронкинNo ratings yet

- AD9mark PDFDocument14 pagesAD9mark PDFLe DungNo ratings yet

- For New Designs: AOZ1033AIDocument15 pagesFor New Designs: AOZ1033AIPaulo Roberto s freireNo ratings yet

- Ci CS2841B PDFDocument6 pagesCi CS2841B PDFEdson CostaNo ratings yet

- ST2SC3202Document3 pagesST2SC3202Pedro JoseNo ratings yet

- DELTA VFD-L Quickstart ManualDocument16 pagesDELTA VFD-L Quickstart ManualManojh sebastienNo ratings yet

- MP2303Document12 pagesMP2303Sophie GelNo ratings yet

- SC1531 Semtech CorporationDocument11 pagesSC1531 Semtech Corporation94430s19684No ratings yet

- 150KHz 3A PWM Buck DC/DC Converter ModuleDocument11 pages150KHz 3A PWM Buck DC/DC Converter Modulebibib bibibNo ratings yet

- Contact Block EatonDocument2 pagesContact Block EatonsydifiaNo ratings yet

- Eaton 015036 T0 5 8361 E en - GBDocument6 pagesEaton 015036 T0 5 8361 E en - GBSeoane GustavoNo ratings yet

- L7900 Series: Negative Voltage RegulatorsDocument13 pagesL7900 Series: Negative Voltage Regulatorsmhd_almahayniNo ratings yet

- Catalog Khoi Dong Mem Chint NJR2 ZXDocument6 pagesCatalog Khoi Dong Mem Chint NJR2 ZXsatthubattuongNo ratings yet

- PV PanelDocument17 pagesPV PanelMuhammad RiazNo ratings yet

- Borro ToDocument9 pagesBorro TomaugrysNo ratings yet

- Datasheet MP2380DNDocument11 pagesDatasheet MP2380DNchevicitNo ratings yet

- Teac H300 Dab TunerDocument24 pagesTeac H300 Dab TunerKate KnightNo ratings yet

- HANS - Udyam Registration CertificateDocument2 pagesHANS - Udyam Registration Certificateshivi mishraNo ratings yet

- 4 Suspension BenchDocument5 pages4 Suspension BenchTecnicas Reunidas de AutomociónNo ratings yet

- Quality AssuranceDocument6 pagesQuality AssuranceعلاءإدريسNo ratings yet

- Commvault Intellisnap For NetAppDocument28 pagesCommvault Intellisnap For NetAppSenthilkumar MuthusamyNo ratings yet

- Tips For Use Cube Uk 1Document4 pagesTips For Use Cube Uk 1LucasNo ratings yet

- Simatic S7-PDIAG For S7-300 and S7-400 Configuring Process DiagnosticsDocument198 pagesSimatic S7-PDIAG For S7-300 and S7-400 Configuring Process DiagnosticsOleksandr HusievNo ratings yet

- Turkstream Pipeline PrecommissioningDocument2 pagesTurkstream Pipeline PrecommissioningWayne BerreyNo ratings yet

- Directional Driller X CVDocument2 pagesDirectional Driller X CVMino MinoNo ratings yet

- Naveen Kumar GDocument2 pagesNaveen Kumar GRajeshkumar PothupalepuNo ratings yet

- Asus X553MA Repair Guide Rev2.0Document7 pagesAsus X553MA Repair Guide Rev2.0UMA AKANDU UCHENo ratings yet

- AnnabellaBracco Resume 2021Document1 pageAnnabellaBracco Resume 2021ANNABELLA BRACCONo ratings yet

- EU Funds Development of Manned-Unmanned Teaming for Combat HelicoptersDocument3 pagesEU Funds Development of Manned-Unmanned Teaming for Combat Helicoptersgian franco borroniNo ratings yet

- ROKS KPI Canvas - ExcelDocument2 pagesROKS KPI Canvas - ExcelwhauckNo ratings yet

- CIS RAM For IG1 Workbook v21.10.25Document144 pagesCIS RAM For IG1 Workbook v21.10.25pikanteNo ratings yet

- Boot Options PDFDocument6 pagesBoot Options PDFBashar MohammedNo ratings yet

- Economics of Tablet MarketDocument33 pagesEconomics of Tablet Marketkhushi sikariaNo ratings yet

- Arco en C Siemens Polymobil 3 MS EngDocument34 pagesArco en C Siemens Polymobil 3 MS EngAzucena RivasNo ratings yet

- Purple Finder PDFDocument12 pagesPurple Finder PDFsahil jadonNo ratings yet

- Assessment of Small Reciprocating Engine Manufacturers and Generator Set PackagersDocument66 pagesAssessment of Small Reciprocating Engine Manufacturers and Generator Set PackagersAnonymous zfmlsb2GjA100% (1)

- MySAP CRM Mobile Sales MonitoringDocument51 pagesMySAP CRM Mobile Sales MonitoringSuresh ReddyNo ratings yet

- Data File - 01Document939 pagesData File - 01Dhruvil DesaiNo ratings yet

- ZXA10 C610 Product Description - V1.1.0 - 20190411Document64 pagesZXA10 C610 Product Description - V1.1.0 - 20190411Edson Lira100% (2)

- TEC3r Manual 1.9.FDocument130 pagesTEC3r Manual 1.9.FerasmolsdiasNo ratings yet

- JSP: Overview of lifecycle, architecture, elements, implicit objects and exception handlingDocument73 pagesJSP: Overview of lifecycle, architecture, elements, implicit objects and exception handlingRushikesh YadavNo ratings yet

- Airline Benchmarking and Performance ImprovementDocument27 pagesAirline Benchmarking and Performance ImprovementJatin ParmarNo ratings yet

- Engine Controls Hybrid System Circuit D2Document1 pageEngine Controls Hybrid System Circuit D2FranciscoNo ratings yet

- Computer Security Log BookDocument13 pagesComputer Security Log Bookhappinessokon750No ratings yet

- Silcostart: Static Motor Softstarter Solving Starting ProblemsDocument4 pagesSilcostart: Static Motor Softstarter Solving Starting ProblemsMohamed AlkharashyNo ratings yet

- Solidworks SyllabusDocument7 pagesSolidworks SyllabusSelvaNo ratings yet