Professional Documents

Culture Documents

A2 Slot CAT2 QP

Uploaded by

Severus SnapeOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

A2 Slot CAT2 QP

Uploaded by

Severus SnapeCopyright:

Available Formats

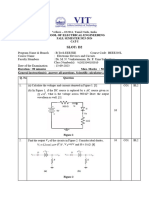

Vellore – 632014, Tamil Nadu, India

SCHOOL OF ELECTRICAL ENGINEERING

WINTER SEMESTER 2022-2023

CAT-II

SLOT: A2

Programme Name & Branch : B.Tech EEE & EIE Course Code: BEEE208L

Course Name : Analog Electronics

Faculty Members : Dr. M.N. Venkataraman, Dr. G. Arunkumar and Dr. R. Gnanavignesh

Class Number(s) : VL2022230502462, VL2022230502062 and VL2022230502063

Date of the Examination : 13-March-2023

Duration: 90 minutes Max. Marks : 50

General instruction(s): Use calculator to the numerical with three decimal points.

Answer ALL Questions

Q. Question Max. CO BL

No. Marks

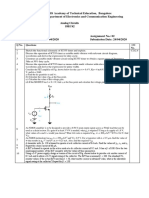

1. (a) Develop the circuit diagram of a 6-bit inverted R-2R ladder DAC circuit. And give 5 5 L3

the output voltage.

(b) Construct the 3 bit flash type ADC circuit with reference voltage as 12 V. Also 5

provide its encoder truth table.

2. (a) Design a monostable multivibrator using 555 timer to produce pulse width of 100 5 5 L4

ms. And sketch circuit diagram and necessary waveforms.

(b) For the Astable multivibrator RA = 2.2 kΩ, RB = 6.8 kΩ and c = 0.1 μF. Discover

(i) thigh, (ii) tlow, (iii) free running frequency and (iv) duty cycle. Also sketch the circuit 5

diagram.

3. (a) Construct a positive voltage regulator for an output voltage 12 V from 24 V. 5 5 L4

Assume load current as 1 A.

(b) Construct a negative voltage regulator for an output voltage -15 V from -32 V. 5

Assume load current as -2 A.

4. Calculate the input power, output power and percentage efficiency of the series fed 10 1 L5

directly coupled Class A power amplifier circuit with the following specifications;

VCC = 24 V, RB = 1 kΩ, RL = 20 Ω, and base current of 10 mA peak.

5. For a class B push pull amplifier with VCC = 30 V driving an 10 Ω load, determine (a) 10 1 L4

maximum input power, (ii) maximum output power (iii) maximum circuit efficiency.

Question Paper Setter: Moderator:

Dr. G. Arunkumar

You might also like

- Edsa PaladinDocument89 pagesEdsa PaladinIulian PârjoleanuNo ratings yet

- VSC-FACTS-HVDC: Analysis, Modelling and Simulation in Power GridsFrom EverandVSC-FACTS-HVDC: Analysis, Modelling and Simulation in Power GridsNo ratings yet

- Detector Metale CEIA THS21 PDFDocument144 pagesDetector Metale CEIA THS21 PDFRadulescu AdrianNo ratings yet

- Electrical Measurements Sample PapersDocument4 pagesElectrical Measurements Sample PapersDeeo DhadiwalNo ratings yet

- IA2 Question PaperDocument18 pagesIA2 Question PaperravirayappaNo ratings yet

- EET285-Dynamic Circuits and SystemsDocument9 pagesEET285-Dynamic Circuits and SystemsDeepa M SNo ratings yet

- Questions Edc Set3Document2 pagesQuestions Edc Set3Severus SnapeNo ratings yet

- KTU EDC Previous Question PapersDocument12 pagesKTU EDC Previous Question PapersVarun DevNo ratings yet

- 9a02304-Basic Electrical & Electronics EngineeringDocument4 pages9a02304-Basic Electrical & Electronics Engineeringsivabharathamurthy0% (1)

- 9A02304 Basic Electrical & Electronics EngineeringDocument8 pages9A02304 Basic Electrical & Electronics EngineeringsivabharathamurthyNo ratings yet

- FY Btech - EX - Electrical & Electronics Engineering - SEM - I - JAN 2023Document3 pagesFY Btech - EX - Electrical & Electronics Engineering - SEM - I - JAN 2023kumbhalkarvalay8No ratings yet

- Full Marks: 50 Duration: 3 HoursDocument2 pagesFull Marks: 50 Duration: 3 HoursK JaiswalNo ratings yet

- 3 Hours / 70 Marks: Seat NoDocument4 pages3 Hours / 70 Marks: Seat No58 EX Ramawat PankajNo ratings yet

- S5 S6 Electrical & Electronics EngineeringDocument209 pagesS5 S6 Electrical & Electronics EngineeringThomas NigilNo ratings yet

- Electrical Engineering: Instructions: 1) The Question Paper Has Been Divided Into Three Parts, "A", "B"Document4 pagesElectrical Engineering: Instructions: 1) The Question Paper Has Been Divided Into Three Parts, "A", "B"Miral_KagathraNo ratings yet

- Set No: 1 R10Document4 pagesSet No: 1 R10Viswa ChaitanyaNo ratings yet

- U20EE201 - CT - Model QPDocument4 pagesU20EE201 - CT - Model QPvinothkumarNo ratings yet

- Electrical Meas May 2012Document8 pagesElectrical Meas May 2012Rama raoNo ratings yet

- Dit 0206 Analogue ElectronicsDocument5 pagesDit 0206 Analogue ElectronicspatrickNo ratings yet

- Electrical and Electronics Engineering - NewDocument28 pagesElectrical and Electronics Engineering - NewanushafiNo ratings yet

- Basics of Electrical and ElectronicsDocument11 pagesBasics of Electrical and ElectronicsannpotterNo ratings yet

- Semester-1 - Chemistry Stream - Mid+end PaperDocument15 pagesSemester-1 - Chemistry Stream - Mid+end PaperGopiNo ratings yet

- Int1 20ees02 Civil ADocument12 pagesInt1 20ees02 Civil ADHARANIKA T C1557No ratings yet

- Electronic Measurements and InstrumentationsDocument4 pagesElectronic Measurements and InstrumentationsSatish BunnyyNo ratings yet

- 2020 11 04SupplementaryCS207CS207 H Ktu QbankDocument3 pages2020 11 04SupplementaryCS207CS207 H Ktu QbankpittalasureshNo ratings yet

- Set - A Beee QPDocument2 pagesSet - A Beee QPThiaga RajanNo ratings yet

- Answer All QuestionsDocument1 pageAnswer All QuestionsBIBIN CHIDAMBARANATHANNo ratings yet

- NR 320204 HIgh Voltge EngineeringDocument4 pagesNR 320204 HIgh Voltge EngineeringSrinivasa Rao GNo ratings yet

- NR 310204 Power ElectronicsDocument8 pagesNR 310204 Power ElectronicsSrinivasa Rao G100% (1)

- Analogue II Exams Eee 2210 Mechatronics-PrintreadyDocument4 pagesAnalogue II Exams Eee 2210 Mechatronics-PrintreadyMike ShakespeareNo ratings yet

- BT Electrical Engg. 3rd Sem Exam Measuring InstrumentsDocument4 pagesBT Electrical Engg. 3rd Sem Exam Measuring InstrumentsAmlan SarkarNo ratings yet

- Candidates Are Required To Give Their Answers in Their Own Words As Far As Practicable. The Figures in The Margin Indicate Full MarksDocument2 pagesCandidates Are Required To Give Their Answers in Their Own Words As Far As Practicable. The Figures in The Margin Indicate Full MarkssushilNo ratings yet

- JNTU Network Theory Exam QuestionsDocument3 pagesJNTU Network Theory Exam Questions2BL20EC096spoorti NidoniNo ratings yet

- NR-221103 - Digital Circuits Design and ApplictionDocument5 pagesNR-221103 - Digital Circuits Design and ApplictionSrinivasa Rao G100% (1)

- ANUC END OF SEMESTER EXAMDocument4 pagesANUC END OF SEMESTER EXAMDesmond Owusu- AnsahNo ratings yet

- ECA Exams Term 1Document2 pagesECA Exams Term 1Fred RotichNo ratings yet

- Sample Question Paper Applied ElectronicsDocument4 pagesSample Question Paper Applied Electronicssachin barge100% (1)

- 2022 Summer Question Paper (Msbte Study Resources)Document4 pages2022 Summer Question Paper (Msbte Study Resources)first kingNo ratings yet

- Q1371 Analog ElectronicsDocument1 pageQ1371 Analog ElectronicsDivyanshu BoseNo ratings yet

- Answer Any Two Full Questions, Each Carries 15 Marks.: Reg No.: - NameDocument2 pagesAnswer Any Two Full Questions, Each Carries 15 Marks.: Reg No.: - Namesheena mNo ratings yet

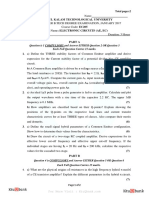

- JSS Academy of Technical Education, Bangalore Department of Electronics and Communication Engineering Analog Circuits AssignmentDocument2 pagesJSS Academy of Technical Education, Bangalore Department of Electronics and Communication Engineering Analog Circuits AssignmentSamarth SamaNo ratings yet

- NSTU EEE Power Electronics Assignment QuestionsDocument6 pagesNSTU EEE Power Electronics Assignment QuestionsSalma AkterNo ratings yet

- Question Paper - 3Document2 pagesQuestion Paper - 3ABCDNo ratings yet

- Set No. 1: Cosφ Cosφ.Cos (φ−β) wL RDocument8 pagesSet No. 1: Cosφ Cosφ.Cos (φ−β) wL RViswa ChaitanyaNo ratings yet

- BMS College of Engineering, Bangalore-560019: December 2015 Semester End Main ExaminationsDocument3 pagesBMS College of Engineering, Bangalore-560019: December 2015 Semester End Main ExaminationsrameshNo ratings yet

- TUNE HOME RADIO WITH CIRCUIT CONCEPTDocument1 pageTUNE HOME RADIO WITH CIRCUIT CONCEPTElujekwute BenjaminNo ratings yet

- rr312202 Industrial ElectronicsDocument5 pagesrr312202 Industrial ElectronicsSRINIVASA RAO GANTANo ratings yet

- Engineering Department: RESIT FINAL ASSIGNMENT: Semester-2, 2019-20 EEPW2251: Electrical Power TechnologyDocument3 pagesEngineering Department: RESIT FINAL ASSIGNMENT: Semester-2, 2019-20 EEPW2251: Electrical Power TechnologyFarooq KhanNo ratings yet

- Ec 303Document2 pagesEc 303jeetendrasidhiNo ratings yet

- KTU EC205 ELECTRONIC CIRCUITS (AE, EC) - MAin - Jan - 2017 - Ktu Qbank-MergedDocument16 pagesKTU EC205 ELECTRONIC CIRCUITS (AE, EC) - MAin - Jan - 2017 - Ktu Qbank-MergedsunNo ratings yet

- R7410402 Electronic Measurements & InstrumentationDocument4 pagesR7410402 Electronic Measurements & InstrumentationsivabharathamurthyNo ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological UniversityHet ShahNo ratings yet

- B21 B22 B23 Eee1001-Ecs Tee QPDocument2 pagesB21 B22 B23 Eee1001-Ecs Tee QPADARSH JHANo ratings yet

- BITS PILANI K K BIRLA GOA CAMPUS EEE F111 COMPREHENSIVE EXAMDocument4 pagesBITS PILANI K K BIRLA GOA CAMPUS EEE F111 COMPREHENSIVE EXAMMonit AgrawalNo ratings yet

- Answer All Questions. Each Question Carries 2 MarksDocument2 pagesAnswer All Questions. Each Question Carries 2 MarksJaferNo ratings yet

- ENEL2EEH1 - Electrical & Electronic EngineeringDocument7 pagesENEL2EEH1 - Electrical & Electronic EngineeringqanaqNo ratings yet

- 9A04604 Electronic Measurements and InstrumentationDocument4 pages9A04604 Electronic Measurements and InstrumentationsivabharathamurthyNo ratings yet

- Pulse and Digital CircuitsDocument8 pagesPulse and Digital CircuitsSatish SmartNo ratings yet

- 9A02504 Power ElectronicsDocument4 pages9A02504 Power ElectronicsMohan Krishna100% (1)

- Lakireddy Bali Reddy College of Engineering (Document9 pagesLakireddy Bali Reddy College of Engineering (raman yarramilliNo ratings yet

- Electrical and Electronic Principles 3 Checkbook: The Checkbook SeriesFrom EverandElectrical and Electronic Principles 3 Checkbook: The Checkbook SeriesNo ratings yet

- Diode Experiment1Document11 pagesDiode Experiment1Severus SnapeNo ratings yet

- Electronics Experiments 2Document8 pagesElectronics Experiments 2Severus SnapeNo ratings yet

- BJTsDocument7 pagesBJTsSeverus SnapeNo ratings yet

- Pottery 21BEE0163Document7 pagesPottery 21BEE0163Severus SnapeNo ratings yet

- 21bee0159 BJTDocument7 pages21bee0159 BJTSeverus SnapeNo ratings yet

- Types of Clampers and Their BiasesDocument20 pagesTypes of Clampers and Their BiasesSeverus SnapeNo ratings yet

- Zero bias and voltage clamping circuits explainedDocument4 pagesZero bias and voltage clamping circuits explainedSeverus SnapeNo ratings yet

- Kirk Key Systems PDFDocument6 pagesKirk Key Systems PDFGlenys MuñozNo ratings yet

- Steinway & Sons: Model O: A Stunning PerformanceDocument2 pagesSteinway & Sons: Model O: A Stunning PerformanceMohammad FamuNo ratings yet

- High and Lower Pressure Sodium LampDocument2 pagesHigh and Lower Pressure Sodium LampJohn Paul LiwaliwNo ratings yet

- Vibrators CT ScreedDocument20 pagesVibrators CT ScreedMuhaiminNo ratings yet

- Computer Hardware and Its FunctionDocument12 pagesComputer Hardware and Its FunctionBiway RegalaNo ratings yet

- Measure and Compare Electrical QuantitiesDocument59 pagesMeasure and Compare Electrical QuantitiesRajaa HusseinNo ratings yet

- Acti9 iCT - A9C24763 PDFDocument3 pagesActi9 iCT - A9C24763 PDFFranck-Willy KAMGAINNo ratings yet

- Basic Electrical MCQ Online TestDocument9 pagesBasic Electrical MCQ Online Testsumanta.kundu318020No ratings yet

- 16-Bit, 100 Ksps/200 Ksps Bicmos A/D ConvertersDocument16 pages16-Bit, 100 Ksps/200 Ksps Bicmos A/D ConvertersmhasansharifiNo ratings yet

- Password Based Door Lock SystemDocument25 pagesPassword Based Door Lock SystemChaudhary PavitraNo ratings yet

- Arroyo 5300 Tec Source Users ManualDocument44 pagesArroyo 5300 Tec Source Users ManualAnonymous 60esBJZIjNo ratings yet

- Sync To HSYNC and VSYNC ConverterDocument1 pageSync To HSYNC and VSYNC ConverterAzmi PlgNo ratings yet

- Description and Operation: Unison Industries Component Maintenance Manual Ignition LeadsDocument2 pagesDescription and Operation: Unison Industries Component Maintenance Manual Ignition Leadsmaty englerNo ratings yet

- Electric Motorcycle Charging Station Powered by SoDocument11 pagesElectric Motorcycle Charging Station Powered by SoAbass BILANo ratings yet

- Control Engineering Syllabus and Lesson PlanDocument68 pagesControl Engineering Syllabus and Lesson PlanDr-Bharath Vedashantha MurthyNo ratings yet

- Com Par at orDocument7 pagesCom Par at orసదాశివ మద్దిగిరిNo ratings yet

- Water Power Technologies Office 2017 Hydropower Market ReportDocument8 pagesWater Power Technologies Office 2017 Hydropower Market Reporthimiko togaNo ratings yet

- BEE - Chapter 6Document63 pagesBEE - Chapter 6Engr Saad Bin SarfrazNo ratings yet

- Arc Interruption Theory ExplainedDocument9 pagesArc Interruption Theory ExplainedMurari SivakumarNo ratings yet

- 6 - Dynamic Model of The Induction MotorDocument11 pages6 - Dynamic Model of The Induction MotorQuynh tran100% (2)

- Fpga Motor Control Reference Design: Spartan™-3 Microblaze™Document15 pagesFpga Motor Control Reference Design: Spartan™-3 Microblaze™ASOCIACION ATECUBONo ratings yet

- Modular Analog Audio Mixer - PAPERDocument11 pagesModular Analog Audio Mixer - PAPERFabio MonteiroNo ratings yet

- 754412Document483 pages754412Giuseppe FerrariNo ratings yet

- TX Harris FAX SeriesDocument11 pagesTX Harris FAX SeriesHever RodriguezNo ratings yet

- MATLAB Matrices and DC Circuits AnalysisDocument5 pagesMATLAB Matrices and DC Circuits AnalysisAhmad Ash SharkawiNo ratings yet

- Hierarchical Design and Formal Verification: Experiment No. 04Document10 pagesHierarchical Design and Formal Verification: Experiment No. 04dragondignityNo ratings yet

- UP EN 50HzDocument4 pagesUP EN 50HzRadu GheorghițăNo ratings yet