Professional Documents

Culture Documents

MK4164

MK4164

Uploaded by

Erasmo Franco0 ratings0% found this document useful (0 votes)

69 views11 pagesCopyright

© © All Rights Reserved

Available Formats

PDF or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

0 ratings0% found this document useful (0 votes)

69 views11 pagesMK4164

MK4164

Uploaded by

Erasmo FrancoCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

You are on page 1of 11

65 536-BIT (65 536-WORD BY 1-BIT) DYNAMIC RAM.

MITSUBISHI LSIs

MSK4164AL-12, -15

DESCRIPTION

This is a family of 65 536-word by 1-bit dynamic RAMs,

fabricated with the high performance N-channel silicongate

MOS process, and is ideal for large-capacity memory

systems where high speed, tow power dissipation, and low

costs are essential. The use of double-layer polysilicon

process technology and @ single-transistor dynamic storage

‘cell privide high circuit density at reduced costs, and the

use of dynamic circuitry including sense amplifiers assures

low power dissipation. Multiplexed address inputs permit

both a reduction in pins to the 16-pin zigzag inline package

configuration and an increase in system densities, The

MBK4164AL operates on a 5V power supply using the

on-chip substrate bias generator.

FEATURES

© High speed

| ] ae

| | a

MSK#164AL-12 |

oKeT64aL-13

© 16 pin zigzag inline package

© Single 510% supply

© Low standby power dissipation: 22mW (max)

© Low operating power dissipation:

MBK4164AL-12 275mW (max)

MBK4164AL-15 250mW (max)

© Unlatched output enables two-dimensional chip selec-

tion and extended page boundary

‘© Early-write operation gives common 1/0 capability

© Read-modity-write, RASonly refresh, and page-mode

capabilities

PIN CONFIGURATION (TOP VIEW)

COLUMN ADDRESS es eee

wns congege g —afip Bo 8 onra maur

3h E rf axa tearour

fae if Ag ADORESS INPUT

pooress | * Sal vec (sv)

se >} sgnees

Outline 16P5A

All input terminals have low input capaciatance and are

directly TTL-compatible

Output is three-state and directly TTL-compatible

128 refresh cycles every 2ms

(16K dynamic RAMs M5K4116P, S compatible)

TAS controlled output allows hidden refresh

Output data can be held infinitely by CAS

APPLICATION

© Main memory unit for computers

© Refresh memory for CRT

BLOCK DIAGRAM ee eee 7 1

WRITE CONTROL INPUT —D-- aim Bl

SrRoar taser CASS TLOGK GENERATOR TD Vee tv

SPRLAP RE oe ) vss cov

(2Q Te} Fito] wand then | | E |

P@]4 weNOny cru al ee} 7

soones nrrs {2 OEE ox adi Eliane | |

| as SENSE REFRESH AMPLIFIER -

ae MEMORY CELL i

ls it nc Bs ESLUNS|

cou orcooen —} 4

i

MITSUBISHI

38

ELECTRIC

65 536-BIT (65 536-WORD BY 1-1

MITSUBISHI LSIs

MSK4164AL-12, -15

T) DYNAMIC RAM

FUNCTION

‘The MSKA4164AL provides, in addition to normal read,

write, and read-modify-write operations, a number of other

functions, e.g., page mode, RAS-only refresh, and delayed-

write, The input conditions for each are shown in Table 1

Table 1 Input conditions for each mode»

—— mle |e

Res _ ‘acr_| act | nac | one | aro | apo | aac | vio | ves)

[reser we aer_| act | act_| woo | aro Toxac [vio [ves i

| Seitretesh Towac Tone | one | onc ‘act [om | ves

palais | [act

[Tren at ers wac_| act | “owe | one | ove [ome | acr | wo] ves |

SUMMARY OF OPERATIONS

Addressing

To select one of the 65536 memory cellsin the MEK4164AL,

the 16-bit address signal must be multiplexed into 8 address,

signals, which are then latched into the on-chip latch by

two externally-applied clock pulses. First, the negative

going edge of the row-addressstrobe pulse (RAS) latches,

the 8 row-address bits; next, the negative-going edge of the

column-addressstrobe pulse (CAS) latches the 8 column-

address bits, Timing of the RAS and CAS clocks can be

selected by either of the following two methods

1, The delay time from RAS to CAS tainas-cas) is set

between the minimum and maximum values of the

limits. In this case, the internal CAS control signals are

inhibited almost until tynas-casimen (gated CAS!

operation). The external CAS signal cen be applied with

4 margin not affecting the on-chip circuit operations, e.9,

access time, and the address inputs can be easily changed

‘rom row address to column address.

1 The delay time tainas.cas) is set larger than the

maximum value of the limits. In this_case the internal

inhibition of CAS has already been released, so that the

internal CAS control signals are controlled by the

externally applied GAS, which also controls the access

time.

Data Input

Date to be written into a selected cell is strobed by the later

of the two negative transitions of W input and GAS input.

‘Thus when the W input makes its negative transition prior

to CAS input (early write), the data input is strobed by

CAS, and the negative transition of CAS is set as the

reference point for set-up and hold times, In the read-write

‘or read-modify-write cycles, however, when the W input

makes its negative transition after CAS, the W negative

transition is set as the reference point for setup and hold

times.

Data Output Control

‘The output of the MSK4164AL is in the high-impedance

state when CAS is high, When the memory cycle in progress

is a read, read-modify-write, or a delayedwrite cycle, the

data output will go from the high-impedance state to the

active condition, and the data in the selected cell will be

read. This data output will have the same polarity as the

input data. Once the output has entered the active

condition, this condition will be maintained until CAS goes

hhigh, irrespective of the condition of RAS.

‘The output will remain in the high-impedance state

throughout the entire cycle in an early-write cycle

‘These output conditions, of the MK4164AL, which can

readily be changed by controlling the timing of the write

pulse in a write cycle, and the width of the CAS pulse ina

read cycle, offer capabilities for a number of applications,

as follows.

1, Common 1/0 Operation

{fall write operations are performed in the early-write

mode, input and output can be connected directly to give a

‘common I/O data bus.

2. Data Output Hold

‘The data output can be held between read cycles, without

lengthening the cycle time, This enables extremely flexible

clock-timing settings for RAS and CAS.

MITSUBISHI

ELECTRIC

65 536-BIT (65 536-WORD BY 1-1

MITSUBISHI LSIs

MSK4164AL-12, -15

) DYNAMIC RAM

3. Two Methods of Chip Selection

Since the output is not latched, CAS is not required to keep

the outputs of selected chips in the matrix in a high:

impedance state, This means that CAS and/or RAS can

both be decoded for chip selection,

4, Extended-Page Boundary

By decoding CAS, the page boundary can be extended

beyond the 256 cotumn locations in a single chip. In this

case, RAS must be applied to all devices.

Page-Mode Operation

This operation allows for muttiple-column addressing at the

same row address, and eliminates the power dissipation

associated with the negative-going edge of RAS, because

fonce the row address has been strobed, IAS is maintained.

‘Also, the time required to strobe in the row address for the

second and subsequent cycles is eliminated, thereby de-

creasing the access and cycle times,

Refresh

Each of the 128 rows (Ao ~ Ag! of the MSK4164AL must

be refreshed every 2 ms to maintain data, The methods of

refreshing for the MEK4164AL ae as follows.

1. Normal Refresh

Read cycle and Write cycle (early write, delayed write or

read-modify-write) refresh the selected cow as defined by

the low order (RAS) addresses, Any write cycle, of course,

may change the state of the selected cell, Using a read,

write, oF read-modify-write cycle for refresh is not recom:

‘mended for systems which utilize “wireOR” outputs since

output bus contention will occu

2, RAS Only Refresh

‘A RASonly refresh cycle isthe recommended technique

for most applications t0 provide for data retention. A

RASonly refresh cycle maintains the output in the

high-impedence state with a typical power reduction of

20% over a ead or write cycle

3. Automatic Refresh

5 (REF) has two special functions. The MSKA16AL

has a refresh address counter, refresh address multiplexer

and refresh timer for these operations. Automatic refresh is

initiated by bringing REF tow after RAS has precharged

and is used during standard operation just like RAS-only

refresh, excent that sequential row addresses from an

external counter are no longer necessary.

‘At the end of automatic refresh cycle, the internal

refresh address counter will be automatically incremented,

“The output state of the refresh address counter is initiated

by some eight REF, RAS or RAS/CAS cycle after power is

applied, Therefore, 2 special operation is not necessary to

initiate it

RAS must remain inactive during REF activated cycles.

Likewise, REF must remain inactive during RAS generated

cycle,

The other function of pin 5 (REF) is solfrefresh. Timing

for selfrefresh is quite similar to that for automatic refresh

As long as RAS remains high and REF remains low, the

MBKA4164AL will refresh itself. This internal sequence re:

eats asynchronously every 12 to 16 us. After 2 ms, the on:

chip refresh address counter has advanced through all the row.

addresses and refreshed the entire memory. Self-refresh is

primarily intended for trouble free power-down operation

For example, when battery backup is used to maintained

data integrity in the memory. REF may be used to place

the device in the self-refresh mode with no external timing

signals necessary to keep the information alive.

In summary, the pin § (REF) refresh function gives the

user @ feature that is free, save him hardware on the board,

{and in fact, will simplify his battery backup procedures,

increase his battery life, and save him overall cost while

iving him improved system performance.

‘There is an internal pullup resister (= 3M22) on pin 6, so

if the pin 5 (REF) function is not used, pin 5 may be left

‘open (not connect) without affecting the normal operations.

5. Hidden Refresh

A feature of the MBK4164AL is that refresh cycles may

be performed while maintaining velid data at the output pin

by extending the CAS active time from a previous memory

read cycle. Ths teature is refered to as hidden refresh

Hidden refresh is performed by holding CAS at V,_ and

taking RAS high and after a specified precharge period,

executing a RASonly cycling, automatic refresh and

self-refresh, but with CAS held low.

The advantage of this refresh mode is that data can be

held valid at the output data port indefinitely by leaving

the CAS asserted. In many applications this eliminates the

need for off-chip latches.

Power Dissipation

Most of the circuitry in the MSK4164AL is dynamic, and

most of the power is dissipated when addresses are strobed

Both RAS and CAS are decoded and applied to the

MBK4164AL as chip-select in the memory system, but if

FAS is decoded, all unselected devices go into stand-by

independent of the CAS condition, minimizing system

ower dissipation.

Power Supplies

‘The MBK4164AL operates on a single 5V power supply.

‘A wait of some 500us and eight or more dummy cycle is

necessary after power is applied to the device before

memory operation is achieved.

MITSUBISHI

ELECTRIC

MITSUBISHI LSIs

MSK4164AL-12, -15

65 536-BIT (6S 536-WORD BY 1-BIT) DYNAMIC RAM

ABSOLUTE MAXIMUM RATINGS

or ——

bs aan

RECOMMENDED OPERATING CONDITIONS (1-0-7, unis oitrasensts) ote 1

I s [ss tw

| [ss

Low ve iets oa Tv

ELECTRICAL CHARACTERISTICS (12 =0- 70°, voo=

£1096, Ves=0V, voles ethers not) (Note 2)

Vow] Wahine ciple Tou= Sma.

Vox Le eet vote Tout ama

Toe ‘irae vent @ toatng OV EVour 38.50

1 router OV SVin6,5V, At ore ons=0V

vccuney | Beeeaescolv cre Wom Vee. [MBKAIG4AL-12] FES, CAB cxieg

cvme) | geri ate beseetsean

, Torta ory care en Vee, [MBRAIBAAL 12

een180) | reteming (ote) insrainent rs

“anor voy core von Voc, [MBKAI64AL-12

P| sae oe, MSKAGUAL=15 eau

2 i REF xg

7 15] tocner)=mn. rout conn

Yeeeav) | seg tot cna rm Ves wenn Pee

S|

ico) | inowt cape _ Vives

rye [ps enchant conea nD roan

Gianash [loo anata, AES epat dV mv

rica) | E

Cueners | - | ——

Co Won es. SIM, Veter

MITSUBISHI

ELECTRIC 2-37

MITSUBISHI LSIs

M5K4164AL-12, -15

65 536-BIT (65 536-WORD BY 1-BIT) DYNAMIC RAM

TIMING REQUIREMENTS (For Read, Write, Read-Modity-Write, Refresh, and Page-Mode Cycle)

(Ta =0- 79, Veo 5¥ 11096, Vos=0V. sn thine Se re 5647)

Crug [on MERATSURE= TF | MBRETERACTS

few acca ee ine z 2 poe

Tease) | FAS na psa Tar x 730 me

Twine) | Wa ow eh Tmug_| tao | 0000 | 50 [0000 | ne

Twigasci tS tow te wath tas [= a a

Tease] CASran oh wit mam] teen 30 % 8

Thomas cast {ERS ate te RS tess | ¥0 10 a

Treas-nus) | PAS ane ate tase [6 75 D

| to tcas-nas) | Deloy we, CAS to RAS Nowe 3 tone 20 20 ns

Tecnas. cash | Oven ie RAT OEE ‘how [taco a8 Ce tone

Tena ns | Row ne uy wre ae RAE tase ° ° ig

Tsutex cas) [Cou a steele OE tase a a a

Tag nay | Bow cir ate FE Trak 15 2 8

Teas ca) | Cokie senate ser CHE Teac 0 z =

Tnnas.cay | Colon aston ote ve RE tan =o % 2

ue Temition tine u 3 8 2 solos

Ne 5. Art ea fi ereatr ru uno aa sal FEF RAS RAUEES cistron denon wh

© Tenn dormmneeseloent peo

Sessa ake rac esae westerns eee eee eee eee

© Chae papooe aaa

3 reson egret ny pte tr RESIS een rece Zones, or sms we CAS he eae FAB)

SWITCHING CHARACTERISTICS (t=

porn ihn th 1 ¢mas- cas} rox ht tes hat Tamas Max on Leet. Td (mas. casjmas sting Terence pt oes

a ynascas) afeat than he sbooted td (mas. cas) MH. then acs Une ented schaey My fcas

ta ans. casion =U caasna)mn+ PE Te yon) + 'guica-casim0,

10° ,, Veg BV £109, Ves OV, ure there roid)

Read Cycle

Grane Jo MSRATEIAL=12 | MBKEISVAL=15

sume ree oe = a un

Tee Reed ee tne Tre 220 260) 7

‘su mons) | Prods teeters CAS nes ° a ms

Tousen | Re ois ie fe CAS noe | tc ° 0 28

Thinagia, | Ara hls ore ater FS (ote ER io 20 im

Tensions) | Onsot dab ive howe | tore ° = ° o a8

Taicas) CaS ie ‘ere | Tene: 0 75 a

Ta6as) BAS oes wre ‘ote | trae 20 150 rm

Note 11 Eater th (mag: oT (casa) Mus tated or arene ele

Note 12. tis easymax defines te time at ic te Gitput awe he oe cx onion an 8 ot Feletene 2 Vow et VoL

Note 13 Thiis the lus when td caas-cas)=te (nas: cas)man Tes condone, Load = 27 TL.Cy = 100pF

Nowe 14 Trsuein aun wher 13 teas-oas) tw angen * Irwin)

16 t¢maw min it ind ot Vonsew min =Ta nasiman + Theysnas) + (nas + BUTLMC tad

17. teuqwens), td caas-w, and 13 (cxs-w) 2 not dling he bts of cpmaton, but re ela elec rac Sy

vimen tau mecasytou tm-casymn, an ery wnt cycle parlor andthe de out aps he highpass

when tdcaas-w)2td nas. wit Snd td cas. wiBtSyin-casynn 8rd wn

For alleen ote than those deci bow, he conan of eu at ces tne anv CAS goes bak 0 Vin 6 Nt ei,

Page-Mode Cycle

T amare MSNA TS

soma | Franae ae eo Une

‘eren Tapoae ney sine Tee. ns

“Te roman | Paes rndcioatvwnie erie me : : m=

Toeceasro | CRS rah ose wath te 7

Automatic Refresh Cycle

Semune [LMERGTGWAL=1 | MSKUTSAAL-15

Pte incr) utomaie Rete cycle me Tre m0 260 ns

Ta inas Aer) ine, RAS 0 FEF Treo. 0 300 7

Teinerc) | REF ow oases | So | oo) oo! pln a Ean

Twinern) | REF ha woe warn tr | 2 a]

Toiner-naS) | Dearne, AEF to RAS — “Trse | ons 8

tu cer nas)| REF ove se vn ton PAE ten | 250 255 8

Self-Refresh Cycle

Groune | MERGTSIAL-12 | MEKETBIAC=15 |

sie ror ea u n ne

Tinere i) = a

nee. nas) tron | 250 ne

MITSUBISHI

ELECTRIC 2-39

MITSUBISHI LSIs

MSK4164AL-12, -15

65 536-BIT (65 536-WORD BY 1-BIT) DYNAMIC RAM

TIMING DIAGRAMS oo 1

Read Cycle nor 181

TE ‘ons ms)

| [ames

me nom

[triesnasteyiccasy

ee ER is EBD sess ER ao

ee TOO CORO

ae NE

oS SRR CEE ER Ranh

eel eee

cn ronnie stare

MITSUBISHI

2-40 ae ELECTRIC

MITSUBISHI LSIs

MSK4164AL-12, -15

65 536-BIT (65 536-WORD BY 1-BIT) DYNAMIC RAM

Read-Write and Read-Modity-Write Cycles. ove 1

AAS vee

: —Naicas-nast th icas-RAs).

_—— tweens. —

tsuinunas|

‘areas teocoas)

eas swans sa Kj wmwe S

vo. -——F nf yy?

—_——tacras) — a

twinasty

° er

9. MITSUBISHI

ELECTRIC 2-1

MITSUBISHI LSIs

MSK4164AL-12, -15

65 536-BIT (65 536-WORD BY 1-BIT) DYNAMIC RAM

Page-Mode Read Cycle we 19:

a

ii

Page-Mode Write Cycle iw-i10

petty

inasont) ——y

me 1 f

a reser Liirase

De tid ORR

MITSUBISHI

2-42 ELECTRIC

MITSUBISHI LSIs

MSK4164AL-12, -15

6S S36-BIT (65 S36-WORD BY 1-BIT) DYNAMIC RAM

Automatic Pulse Refresh Cycle (Multiple Pulse) iso. 211

Automatic Pulse Refresh Cycle (Single Pulse) tw 21

- tocnes-nery tsucnernas)

Taine

me Yr VF

Self-Refresh Cycle

twinerey

Fk +

‘a onemaay

aimee cas)

a wN- twicast

mea Jagiass “

teuinenas

°

% MITSUBISHI

ELECTRIC 2-43

MITSUBISHI LSIs

MSK4164AL-12, -15

65 S36-BIT (65 S36-WORD BY 1-BIT) DYNAMIC RAM

Hidden Self-Refresh Cycle

—_ _fwioase a fT

Aooress

ar

u faves) tainer-nasi| |

— avs cas

q aa

Hidden Refresh Cycle ow 12:

can eveut ernesn cvcue ernesn cveie

aca ton of

|

mf

—T

| menas-auy

we wn RTT KSAAER RR RCI

ae RRR TERN SRR

7 Vou

MITSUBISHI

2-46 nen ELECTRIC

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5813)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1092)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (844)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (540)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (348)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (822)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Rele de Estado SolidoDocument11 pagesRele de Estado SolidoErasmo FrancoNo ratings yet

- Solid State Relay or Solid State SwitchDocument1 pageSolid State Relay or Solid State SwitchErasmo FrancoNo ratings yet

- Relay de ReemplazoDocument3 pagesRelay de ReemplazoErasmo FrancoNo ratings yet

- TC75S58F Datasheet en 20190911Document8 pagesTC75S58F Datasheet en 20190911Erasmo FrancoNo ratings yet

- Operation Manual E-Series ET Analog 551890 enDocument33 pagesOperation Manual E-Series ET Analog 551890 enErasmo FrancoNo ratings yet

- Operation Manual E-Series ET SSI 551889 enDocument29 pagesOperation Manual E-Series ET SSI 551889 enErasmo FrancoNo ratings yet

- SigneticsDocument68 pagesSigneticsErasmo FrancoNo ratings yet

- SBC 80-10BDocument7 pagesSBC 80-10BErasmo FrancoNo ratings yet

- M5K4164AP 12 MitsubishiDocument11 pagesM5K4164AP 12 MitsubishiErasmo FrancoNo ratings yet

- Treadmill DC Motor MC-60 Control - CTM ProjectsDocument1 pageTreadmill DC Motor MC-60 Control - CTM ProjectsErasmo FrancoNo ratings yet

- SBC 186-410Document12 pagesSBC 186-410Erasmo FrancoNo ratings yet

- SN75115Document11 pagesSN75115Erasmo FrancoNo ratings yet

- MT! Service ManualDocument60 pagesMT! Service ManualErasmo FrancoNo ratings yet

- Data Sheet Preliminary Jun83Document40 pagesData Sheet Preliminary Jun83Erasmo FrancoNo ratings yet

- M5M51008CFP MitsubishiElectricSemiconductorDocument7 pagesM5M51008CFP MitsubishiElectricSemiconductorErasmo FrancoNo ratings yet

- MC3340Document4 pagesMC3340Erasmo FrancoNo ratings yet

- Tma Datasheet 3049640Document5 pagesTma Datasheet 3049640Erasmo FrancoNo ratings yet

- MAX696 MaximDocument16 pagesMAX696 MaximErasmo FrancoNo ratings yet

- Pcm5820 SeriesDocument120 pagesPcm5820 SeriesErasmo FrancoNo ratings yet

- Semikron Sk70gar063Document4 pagesSemikron Sk70gar063Erasmo FrancoNo ratings yet

- Small Switching: TransistorsDocument6 pagesSmall Switching: TransistorsErasmo FrancoNo ratings yet

- SK70WT SemikronInternationalDocument2 pagesSK70WT SemikronInternationalErasmo FrancoNo ratings yet

- Protecciones OVP - UVP - OPP - SCP - SIP. Que Son - Hiditec - Inspiring SensationsDocument1 pageProtecciones OVP - UVP - OPP - SCP - SIP. Que Son - Hiditec - Inspiring SensationsErasmo FrancoNo ratings yet

- Tipos de Transformadores Por Su Sistema de Enfriamiento - British Federal MexicoDocument1 pageTipos de Transformadores Por Su Sistema de Enfriamiento - British Federal MexicoErasmo FrancoNo ratings yet

- 5820 Edition 2Document114 pages5820 Edition 2Erasmo FrancoNo ratings yet

- AS3711 Datasheet EN v1-1214616Document104 pagesAS3711 Datasheet EN v1-1214616Erasmo FrancoNo ratings yet

- Vishay Siliconix SPICE Device Model Si9934BDY Dual P-Channel 2.5-V (G-S) MOSFETDocument4 pagesVishay Siliconix SPICE Device Model Si9934BDY Dual P-Channel 2.5-V (G-S) MOSFETErasmo FrancoNo ratings yet

- Is Now Part ofDocument17 pagesIs Now Part ofErasmo FrancoNo ratings yet

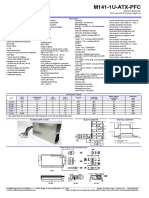

- M141-1U-ATX-PFC: Industrial Application Multi Output AC-DC Power Supply UnitDocument1 pageM141-1U-ATX-PFC: Industrial Application Multi Output AC-DC Power Supply UnitErasmo FrancoNo ratings yet

- CD 40103Document14 pagesCD 40103Erasmo FrancoNo ratings yet