Professional Documents

Culture Documents

Sessional II Spring 2017

Uploaded by

Jannat Nasir0 ratings0% found this document useful (0 votes)

2 views9 pagesThis document contains instructions and questions for a digital logic design midterm exam. It includes 5 questions worth a total of 50 marks. Question 1 asks students to design a half-adder using only 2-input NOR gates. Question 2 describes a 2x1 multiplexer implementation and asks students to determine its function. Question 3 involves a 4-bit priority encoder circuit. Question 4 deals with designing a combinational circuit to check data integrity using parity. Question 5 asks students to draw an SR latch using NAND gates and provide its truth table.

Original Description:

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentThis document contains instructions and questions for a digital logic design midterm exam. It includes 5 questions worth a total of 50 marks. Question 1 asks students to design a half-adder using only 2-input NOR gates. Question 2 describes a 2x1 multiplexer implementation and asks students to determine its function. Question 3 involves a 4-bit priority encoder circuit. Question 4 deals with designing a combinational circuit to check data integrity using parity. Question 5 asks students to draw an SR latch using NAND gates and provide its truth table.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

2 views9 pagesSessional II Spring 2017

Uploaded by

Jannat NasirThis document contains instructions and questions for a digital logic design midterm exam. It includes 5 questions worth a total of 50 marks. Question 1 asks students to design a half-adder using only 2-input NOR gates. Question 2 describes a 2x1 multiplexer implementation and asks students to determine its function. Question 3 involves a 4-bit priority encoder circuit. Question 4 deals with designing a combinational circuit to check data integrity using parity. Question 5 asks students to draw an SR latch using NAND gates and provide its truth table.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 9

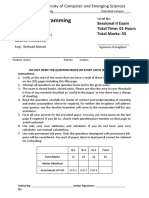

Serial No:

EE-227 Digital 2nd Midterm Exam

Logic Design Total Time:1 Hour

Monday 27th March, 2017 Total Marks: 50

Course Instructor

________________

Dr Mehwish Hasan, Ms Mehreen Alam & Signature of Invigilator

Mr. Jawad Hassan

_____________________________________________ _____________________

Roll No Section Signature

DO NOT OPEN THE QUESTION BOOK OR START UNTIL INSTRUCTED.

Instructions:

1. Attempt on question paper. Attempt all of them. Read the question carefully,

understand the question, and then attempt it.

2. No additional sheet will be provided for rough work. Use and mark the back of the

last page for rough work.

3. If you need more space write on the back side of the paper and clearly mark

question and part number etc.

4. After asked to commence the exam, please verify that you have Nine (9) different

printed pages including this Title page and a rough work page at the end. There are

total of five 5 questions.

5. Use permanent ink pens only. Any part done using soft pencil will not be marked

and cannot be claimed for rechecking.

6. For each question show your complete method in solution.

Q-1 Q-2 Q-3 Q-4 Q-5 Total

Total

5 10 10 18 7 50

Marks

Marks

Obtained

Vetted By: ____________________________Vetter Signature: _____________________

National University of Computer and Emerging Sciences

Department of Computer Science Islamabad Campus

Q1. [ 5 pts] Design a half-adder (inputs: A, B, outputs: S and Cout) using only 2-input

NOR gates. For full credit, you must use minimum number of gates as possible.

Final Exam Spring 2016 Page 2 of 9

National University of Computer and Emerging Sciences

Department of Computer Science Islamabad Campus

Q2. [ 10 pts] What function is implemented by the following 2 x 1 MUX

implementation? Do show intermediary output functions for full credit.

Final Exam Spring 2016 Page 3 of 9

National University of Computer and Emerging Sciences

Department of Computer Science Islamabad Campus

Q3. [ 2+4+4+2 = 10 pts] Consider a 4-bit priority encoder with the priority sequence

D1 > D0 > D3 > D2.

a. Write the priority table.

b. Write the complete 4-bit table.

Final Exam Spring 2016 Page 4 of 9

National University of Computer and Emerging Sciences

Department of Computer Science Islamabad Campus

c. Write minimized equations.

d. Draw the resultant circuit diagram. Do not show the internal encoder

implementation.

Final Exam Spring 2016 Page 5 of 9

National University of Computer and Emerging Sciences

Department of Computer Science Islamabad Campus

Question No.4 [2 + 4 + 6 + 6 = 18]

Q4. [ 2+4+6+6 = 18] Design a combinational circuit for data integrity (data correctness

using parity bit) checker that has four inputs A3, A2, A1, and A0 and one output Fi.

The output will used to implement odd parity i.e., the output Fi = 1 when input has even

number of 1's and 0 otherwise.

a. Construct truth table for Fi

Final Exam Spring 2016 Page 6 of 9

National University of Computer and Emerging Sciences

Department of Computer Science Islamabad Campus

b. Minimize the function and draw the circuit

c. Implement the function Fi using 3 x 8 decoders with enable lines.

Final Exam Spring 2016 Page 7 of 9

National University of Computer and Emerging Sciences

Department of Computer Science Islamabad Campus

d. Implement the function Fi using 2 x 4 decoders with enable lines.

Q5. [ 3+4 = 7 pts] Draw SR latch with NAND gate and give its function table.

Final Exam Spring 2016 Page 8 of 9

National University of Computer and Emerging Sciences

Department of Computer Science Islamabad Campus

ROUGH WORK SHEET

Final Exam Spring 2016 Page 9 of 9

You might also like

- International Maths Olympiad - Class 1 (With CD): Theories with examples, MCQs & solutions, Previous questions, Model test papersFrom EverandInternational Maths Olympiad - Class 1 (With CD): Theories with examples, MCQs & solutions, Previous questions, Model test papersRating: 2 out of 5 stars2/5 (3)

- Algebra Old Exam Papers 91027Document106 pagesAlgebra Old Exam Papers 91027sajith_senanayake_1100% (2)

- Pyramid A e Civil Model Exam 2Document12 pagesPyramid A e Civil Model Exam 2Hironmoy Dash89% (9)

- 840C BA OEM 0797 enDocument292 pages840C BA OEM 0797 enRogerio Medeiros da SilvaNo ratings yet

- Value Learning Chip Level SyllabusDocument5 pagesValue Learning Chip Level SyllabusVenkatareddy MulaNo ratings yet

- Divisions of Art StudyDocument21 pagesDivisions of Art StudyJewel SkyNo ratings yet

- Crash Course: 3 Hours Introduction To Pic Microcontroller byDocument43 pagesCrash Course: 3 Hours Introduction To Pic Microcontroller bysadariahNo ratings yet

- Maintain Training FacilitiesDocument124 pagesMaintain Training Facilitiesmelaigin92% (39)

- CSS 9 1st Periodical TestDocument4 pagesCSS 9 1st Periodical TestKaty Chenee Napao PerezNo ratings yet

- Sessional II Spring 2017Document9 pagesSessional II Spring 2017Jannat NasirNo ratings yet

- Sessional II Spring 2018Document2 pagesSessional II Spring 2018Jannat NasirNo ratings yet

- Sessional II Spring 2015Document7 pagesSessional II Spring 2015Jannat NasirNo ratings yet

- Automata - Mid 1 - Fall 2016-1Document8 pagesAutomata - Mid 1 - Fall 2016-1Amna SumbalNo ratings yet

- CS217 Spring-2020 Final ExamDocument9 pagesCS217 Spring-2020 Final Examihaseebarshad10No ratings yet

- CS118 PF FinalRemoteRetakeExamPaper Spring 2020Document6 pagesCS118 PF FinalRemoteRetakeExamPaper Spring 2020AsadAliBhattiNo ratings yet

- Mth601 Collection of Old PapersDocument33 pagesMth601 Collection of Old Paperscs619finalproject.com86% (7)

- Worksheet 1.2Document5 pagesWorksheet 1.2Stant BoiNo ratings yet

- Ca Mid1 2017Document9 pagesCa Mid1 2017hruitNo ratings yet

- PF Sessional2 Fall 22Document10 pagesPF Sessional2 Fall 22fakhar_fastNo ratings yet

- Tips To Solve QP of Cs (Python) Class 12Document24 pagesTips To Solve QP of Cs (Python) Class 12amogh pantNo ratings yet

- SEMESTER I, 20152016 MidtermDocument6 pagesSEMESTER I, 20152016 Midtermকফি ওয়ান টুNo ratings yet

- CS-685-HCI - LAB-Final Term - Spring 2020Document5 pagesCS-685-HCI - LAB-Final Term - Spring 2020Shahzaib MirzaNo ratings yet

- Introduction To Programming - CS201 Spring 2006 Final Term Paper Session 2Document4 pagesIntroduction To Programming - CS201 Spring 2006 Final Term Paper Session 2Muhammad SaleemNo ratings yet

- EE 313 Laboratory Exercise No. 1 FormatDocument6 pagesEE 313 Laboratory Exercise No. 1 FormatPaul Andrie CosoNo ratings yet

- Department of Computer Science Online Mid Term ExaminationDocument3 pagesDepartment of Computer Science Online Mid Term ExaminationMalik KashifNo ratings yet

- Midterm 2Document3 pagesMidterm 2aliidrees8600No ratings yet

- CE221 MT QuestionsDocument4 pagesCE221 MT Questionsliside7602No ratings yet

- ECE 190 - Mon Exam 2 - SP 2012 - v2Document7 pagesECE 190 - Mon Exam 2 - SP 2012 - v2Lee GillNo ratings yet

- BCA 1st Sem Assignment 2016-17Document10 pagesBCA 1st Sem Assignment 2016-17Kamal TiwariNo ratings yet

- CS2210 Midterm Paper 2 For Class11 2014-15 With Mark KeyDocument18 pagesCS2210 Midterm Paper 2 For Class11 2014-15 With Mark KeybissoonNo ratings yet

- Assignemnt 1Document7 pagesAssignemnt 1Rafay NaveedNo ratings yet

- UCK 337 Introduction To Optimization Spring 2019-2020 Problem Set IIDocument3 pagesUCK 337 Introduction To Optimization Spring 2019-2020 Problem Set IIMim Alperen YarenNo ratings yet

- End-Term Examinations: Year 10Document10 pagesEnd-Term Examinations: Year 10USHA PERUMALNo ratings yet

- Exam Fall 2015Document9 pagesExam Fall 2015Hadi SleemNo ratings yet

- Automata Mid2 Fall2015Document7 pagesAutomata Mid2 Fall2015Amna SumbalNo ratings yet

- COL106 Major 2019-20 Sem2Document5 pagesCOL106 Major 2019-20 Sem2Vishal kumar SawNo ratings yet

- Institute of Southern Punjab Multan Online Examination: Department of Computer ScienceDocument4 pagesInstitute of Southern Punjab Multan Online Examination: Department of Computer ScienceAqeel Asghar pansotaNo ratings yet

- EE 213M - Mid Sem Exam Paper 1Document3 pagesEE 213M - Mid Sem Exam Paper 1Arpit SurekaNo ratings yet

- Homework Assignment 2 (100 + 10 Points.) : Deadline: Sat. Jul. 1st, 2023, 9:00 AMDocument3 pagesHomework Assignment 2 (100 + 10 Points.) : Deadline: Sat. Jul. 1st, 2023, 9:00 AMAlbina HakobyanNo ratings yet

- Final Exam TemplateDocument3 pagesFinal Exam TemplateSomeguy123551234512No ratings yet

- Lesson Plan Project Educ 5312 WeeblyDocument6 pagesLesson Plan Project Educ 5312 Weeblyapi-290266366No ratings yet

- MsDocument33 pagesMsmahimaNo ratings yet

- Introduction To Computing and Information Technology 2 Mid-Term Examination MakeupDocument6 pagesIntroduction To Computing and Information Technology 2 Mid-Term Examination MakeupKhalidNo ratings yet

- Exam DT106GDocument7 pagesExam DT106GahmadNo ratings yet

- CSP2151 Sample TestDocument5 pagesCSP2151 Sample TestminurajpereraNo ratings yet

- Cse 215: Programming Language Ii Sec - 2 & 3, Faculty: SvaDocument2 pagesCse 215: Programming Language Ii Sec - 2 & 3, Faculty: SvaMD ShahriarNo ratings yet

- Assignment # 06: National University of Computer and Emerging SciencesDocument7 pagesAssignment # 06: National University of Computer and Emerging Sciencesnawab janiNo ratings yet

- ECOR 2606 PASS Mock Midterm 2014Document8 pagesECOR 2606 PASS Mock Midterm 2014Sadaf SalehiNo ratings yet

- MCA III Semester IGNOU AssignmentDocument12 pagesMCA III Semester IGNOU AssignmentMayur AsodariyaNo ratings yet

- Assignment Chapter 4 DLDDocument20 pagesAssignment Chapter 4 DLDTayyaba Asif100% (1)

- Sessional II Spring 2013Document8 pagesSessional II Spring 2013Jannat NasirNo ratings yet

- ST Lab Manual - 2021-22Document75 pagesST Lab Manual - 2021-22Guru RajNo ratings yet

- COMSATS University, Islamabad: Islamabad Campus Department of Computer ScienceDocument3 pagesCOMSATS University, Islamabad: Islamabad Campus Department of Computer ScienceAhmed BashirNo ratings yet

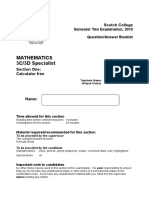

- Scotch 3cdmas Mock ExamDocument32 pagesScotch 3cdmas Mock ExamFredNo ratings yet

- USOL Panjab University Diploma in Computer Applications AssignmentsDocument6 pagesUSOL Panjab University Diploma in Computer Applications AssignmentsJamil Wolf0% (1)

- Mid-Term Exam ITCPDocument2 pagesMid-Term Exam ITCPnayyabkanwal2004No ratings yet

- Eca FileDocument11 pagesEca Fileblitzz fbNo ratings yet

- Practice Final sp22Document10 pagesPractice Final sp22Ajue RamliNo ratings yet

- Optimization Techniques and ApplicationsDocument10 pagesOptimization Techniques and ApplicationsRRNo ratings yet

- Truong Quang Tuong ITITIU20130 Lab 2 CDocument6 pagesTruong Quang Tuong ITITIU20130 Lab 2 CTrương Quang TườngNo ratings yet

- Cambridge International General Certificate of Secondary EducationDocument12 pagesCambridge International General Certificate of Secondary EducationAhmed ZeeshanNo ratings yet

- YR 10 Mathematical - Sems Two - Calc - Free - Exam - 2019Document10 pagesYR 10 Mathematical - Sems Two - Calc - Free - Exam - 2019javysrandomNo ratings yet

- Attachfile 1588395515 Iqhzu8uWtf PDFDocument1 pageAttachfile 1588395515 Iqhzu8uWtf PDFmayar khaledNo ratings yet

- Csca48 Final 2013wDocument20 pagesCsca48 Final 2013wexamkillerNo ratings yet

- General Instructions:: Book-Open, Laptops Are Allowed. NO Internet Connections Are Allowed During Test TimeDocument2 pagesGeneral Instructions:: Book-Open, Laptops Are Allowed. NO Internet Connections Are Allowed During Test TimeNguyễn Khắc HuyNo ratings yet

- Cs201 Mid Spring2007 s1Document6 pagesCs201 Mid Spring2007 s1bc190404936 ZULQARNAINNo ratings yet

- CSC 201-FinalProjectDocumentDocument2 pagesCSC 201-FinalProjectDocumentpavanilNo ratings yet

- 01 Computer VisionDocument52 pages01 Computer VisionmohamedNo ratings yet

- Fundamentals of IT SlidesDocument8 pagesFundamentals of IT SlidesSerah JavaidNo ratings yet

- Yokogawa Centum Cs 3000 DCS Training Course: Hamid EghbalpourDocument1 pageYokogawa Centum Cs 3000 DCS Training Course: Hamid EghbalpourRicardo Martinez ArteagaNo ratings yet

- 07 - Chapter 1 PDFDocument27 pages07 - Chapter 1 PDFنورالدنياNo ratings yet

- Chapter 4: IT Infrastructure: Hardware and Software IT Infrastructure: Provides Platform For Supporting All Information Systems in TheDocument8 pagesChapter 4: IT Infrastructure: Hardware and Software IT Infrastructure: Provides Platform For Supporting All Information Systems in TheDiep Ai NhiNo ratings yet

- What To Do After Graduation ArticleDocument6 pagesWhat To Do After Graduation ArticleAtubrah PrinceNo ratings yet

- A. Choose The Right Answer by Crossing A, B, C, D Ore: and Off. The Underlined Words Have The SameDocument2 pagesA. Choose The Right Answer by Crossing A, B, C, D Ore: and Off. The Underlined Words Have The SameMuhammad PurwatiNo ratings yet

- Makalah Inside Computer BSIDocument17 pagesMakalah Inside Computer BSIWahyu Ramdani100% (1)

- Case Study CPE 58001/ 9. PRACTICE PROFESSIONAL ETHICSDocument31 pagesCase Study CPE 58001/ 9. PRACTICE PROFESSIONAL ETHICStradelNo ratings yet

- Prepared by - Abhishek Kumar Jaiswal Faculty RTI AllahabadDocument32 pagesPrepared by - Abhishek Kumar Jaiswal Faculty RTI AllahabadAbhishek JaiswalNo ratings yet

- Computer Studies Paper 1 Teacher - Co - .KeDocument70 pagesComputer Studies Paper 1 Teacher - Co - .Ketezom techeNo ratings yet

- GC33-0155-2 CICS VS Version 1.6 and 1.7 General Information Jul85 PDFDocument101 pagesGC33-0155-2 CICS VS Version 1.6 and 1.7 General Information Jul85 PDFSubramanianNo ratings yet

- 2024 - S1 - CFAF05D Study Guide v2Document27 pages2024 - S1 - CFAF05D Study Guide v2Monwa BisiNo ratings yet

- Diploma Timetable April2018Document23 pagesDiploma Timetable April2018Anonymous nIcSGEwNo ratings yet

- Quick Start Guide: Ibm Infosphere Information Server Pack For SiebelDocument4 pagesQuick Start Guide: Ibm Infosphere Information Server Pack For SiebelItalo HeviaNo ratings yet

- Fundamentals of MicrocontrollerDocument23 pagesFundamentals of Microcontrollerashley panganNo ratings yet

- Sample Thesis Introduction Computer ScienceDocument8 pagesSample Thesis Introduction Computer Sciencebethhernandezpeoria100% (2)

- TQ Grade 7Document2 pagesTQ Grade 7Marq QoNo ratings yet

- Presentation, Project and Technical Report On " Computer Hardware "Document12 pagesPresentation, Project and Technical Report On " Computer Hardware "Muhammad HuzaifaNo ratings yet

- Dhaka International University: Department of CSE (1 Shift)Document2 pagesDhaka International University: Department of CSE (1 Shift)SakilNo ratings yet

- Intelligent Traffic Light ControlDocument8 pagesIntelligent Traffic Light ControlPavan Murali ManoharaNo ratings yet

- Selected Computerr ConceptDocument60 pagesSelected Computerr ConceptsemerainfotechNo ratings yet

- CMO 13, S. 2008 - APPROVED PS FOR THE BSCpEDocument14 pagesCMO 13, S. 2008 - APPROVED PS FOR THE BSCpEkryschaineNo ratings yet