Professional Documents

Culture Documents

SEMICONDUCTOR Jee With Questions

SEMICONDUCTOR Jee With Questions

Uploaded by

surya pratap0 ratings0% found this document useful (0 votes)

14 views30 pagesOriginal Title

SEMICONDUCTOR jee with questions

Copyright

© © All Rights Reserved

Available Formats

PDF or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

0 ratings0% found this document useful (0 votes)

14 views30 pagesSEMICONDUCTOR Jee With Questions

SEMICONDUCTOR Jee With Questions

Uploaded by

surya pratapCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

You are on page 1of 30

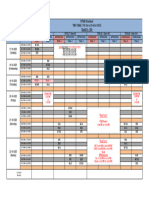

JUESTIONS FOR COMPETITIVE EXAMS Ft

RRR oa COMPILED BY: SATISH KUMAR SIR Cerin

\QUESTIONS FOR COMPETITIVE EXAMS

COMPILED BY:

SATISH KUMAR SIR

32S.KUMAR2: PHYSICS CLASSES? SYMBOL OF EXCELLENCE 8368037835 7503449542

SEMICONDUCTOR ELECTRONICS

TYPES OF MATERIALS

1. (AIPMT 2005) Choose the only false statement from the

following

(a) In conductors, the valence and conduction bands may

overlap

(b) substances with energy gap of the order of 1 eV are

insulators

(©) The resistivity of a semiconductor decreases with

increase in temperature

(d) The conductivity of a semiconductor increases with

increase in temperature

Ans: (b)]

2 (AIPMT 2005) Carbon, Silicon and Germanium atoms

| have four valence electrons each. Their valence and

£ cbnduetion bands are separated by energy band gaps

represented by (Eq)e . (Eq)si and (Eq) respectively

Which one of the following relationships fs true in their

() Ede > Eds: (0) Ede < Est

(© Ede = Ex)si (8 (Egle < Ence

[Ans: (a)]

3. (AIPMT 2004) In semiconductor, at room temperature

(a) the conduction band is completely empty

(b) the valence band is partially empty and the conduction,

7 band is partially filled

{1 (c) the valence band is completely filled and the

conduction band is partially filled

(@) the valence band is completely filled

Ans: (b)]

4. (AIPMTT) At absolute zer0 temperature, Si acts as

(a) non-metal (b) metal

(©) insulator (4) none of these

Ans: (o)]

5. At what temperature would an intrinsic semiconductor

behave like a perfect insulator?

f @OK (273K

$ (273K (4)373K

[Ans: (a)]

6. (AIPMT 2012) C and Si both have same lattice structure,

having 4 bonding electrons in each. However, C is

insulator whereas Si is intrinsic semiconductor. This is

because

(a) in case of C the valence band is not completely filled

at absolute zero temperature

10.

11

12.

(b) in case of C the conduction band is partly filled even

at absolute zero temperature

(©) the four bonding electrons in the ease of C lie in the

second orbit, whereas in the case of Si they lie in the

third

(@) the fourth bonding electrons in the case of C lie in the

third orbit, whereas for Si they lie in the fourth orbit,

Ans: (€)]

(AIPMT) When arsenic is added as an impurity to silicon,

the resulting material is,

(a) n-type semiconductor (b) p-type semiconductor

(©) ntype conductor (a) insulator

Ans: (a)]

(AIPMT) Which of the following when added acts as an

impurity into silicon produced n-type semiconductor?

(aP () Al

©@B @Mg

{Ans: (2))

(NEET 2020) An intrinsic semiconductor is converted into

n-type extrinsic semiconductor by doping it with

(a) Germanium —(b) Antimony

(©) Silver (@) Aluminium

Ans: (b)]

(AIPMT) To obtain a p-type germanium semiconductor,

must be doped with

(a) Arsenic (b) Antimony

(©) Indium — (@) Phosphorus

[Ans: (91

(EE (Main) 2021] Statement I: By doping silicon

Semiconductor with pentavalent material, the electrons

density increases.

Statement II: The n-type semiconductor has net negative

charge.

In the light ofthe above statements, choose the most

appropriate answer from the options given below:

(a) Statement is true but Statement-I is false.

(b) Statements fase but Statement-Il is true.

(6) Both Statement-l and Statement-Il are true,

(@) Both Statement- and Statement-II are false.

Ans: (9)

(AIPMT 2011) Ifa small amount of antimony is added to

germanium crystal then

(a) it becomes a p-type semiconductor

SS SS SS SST eee

2,

yYMBOL OF EXCELLENCE)

() the antimony becomes an acceptor atom

(©) there will be more free electrons than holes in the

semiconductor

(@) its resistance is increased

Ans: (@)]

}. (AIPMT 2003) When phosphorus and antimony are mixed

in germanium, then

(a) p-type semiconductor is formed

(b) n-type semiconductor is formed

(©) both (a) and (b)

(@) None of the above

TAns: (b))

. (AIPMT) In p-type semiconductor, the majority charge

carriers are

(a)holes —_(b) electrons

(© protons (d) neutrons

(Ans: (a)

. (NEET 2013) In an n-type semiconductor, which of the

following statement is true?

(@) Electrons are minority carriers and pentavalent atoms

are dopants

(b) Holes are minority carriers and pentavalent atoms are

dopants

(©) Holes are majority carriers and pentavalent atoms are

dopants

(@) Electrons are majority carriers and trivalent atoms are

dopants,

[Ans: (b)]

;. (NEET 2018) In a p-type semiconductor, which of the

following statement is true?

(a) Electrons are minority carriers and pentavalent atoms

are dopants

(b) Holes are minority carriers and pentavalent atoms are

dopants

(©) Holes are majority carriers and trivalent atoms are

dopants

(@) Electrons are majority carriers and trivalent atoms are

dopants.

Ans: (&)]

(AIPMT 2010) Which one of the following statement is

false

(a) pure Si doped with trivalent impurities gives a p-type

semiconductor

(b) majority cariers in a ntype semiconductor are holes

(©) minority carriers in a ptype semiconductor are

electrons

(@) the resistance of intrinsic semiconductor decreases

‘with increase of temperature

Fas: (b))

|. (NEET 2021) The electron concentration in an n-type

semiconductor is the same as hole concentration in a p=

type semiconductor. An extemal field (electric) is applied

‘across each of them. Compare the currents in them.

(a) No current will flow in p-type, current will only flow

inn-type

(b) Current in n-type = current in p-type

(©) Current in p-type > current in n-type

(@) Current in n-type > current in p-type

[Ans: (@))

{AIPMT) When n-type semiconductor is heated then

(a) number of electrons increases while that of holes

decreases

(b) number of holes increases while that of electrons

decreases

(©) number of electrons and holes remain same

(@) number of electrons and holes increases equally

Ans: (@)]

[SEE (Main) 2021] For extrinsic semiconductors; when

doping level is increased

(a) Fermi-level of p-type semiconductor will go upward

and Fermiclevel of netype semiconductors will go

downward

(b) Fermi-level of p-type semiconductors will go

downward and Fermi-ievel of n-type semiconductors

will go upward

(©) Fermi-level of p and n-type semiconductors will not

beaffected

(2) Fermi-level of both p-type and n-type semiconductors

will go upward for 7 > Tp K and downward for >

Tp K, where Ty is Fermi temperature

Ans: (b)]o

|. (AIPMT 2007) In the energy band diagram of a material

shown below, the open circles and filled circles denote

holes and electrons respectively.

edganaan

The materials

(a) An insulator

() A metal

(©) An n-type semiconductor

(@ A prtype semiconductor

. The ratio of number of holes and number of conduction

electrons in an intrinsic semiconductor

(12100 (b)6:1

©

[Ans: (©)

. The energy gaps in the energy band diagrams of a

conductor, semiconductor and insulator are E,, E, and Ey

Choose the correct option.

(a) Ey= By (b) > E> By

Terres nicenriyyriey COMPILED BY. SATISH KUMAR sinneenneenere

(EE, Ey

TAns: (c)]

24.{EE (Main) 2023] The effect of increase in temperature

{on the number of electrons in conduction band (ng) and

resistance of a semiconductor will be as

(a) both ng and resistance decrease

(b) Both ng and resistance increase

(©) ng increases, resistance decreases

(d) Me decreases, resistance increases

Ans: (©)

25, [JEE (Main) 2023] Match the List I with List Il.

List Lisi

Tnirnsie Fenni-level near

Semiconductor conduction band

Type Fermi-level at

semiconductor middle

Pype Fermi-level near

semiconductor valence band

‘Metals Fermiclevel inside

conduction band_ |

{Choose the correct answer from the options given below:

| (a) (A) 1, (B) +1, (©) II, (D) > 1V

“(b) (A) +1, (B) +1, (© IL, D) + 1V

£ © (IL) il, C1.) 1V

(@ (A) =i, @) 1, ©) — 1) 1V

Tans: (©)

26, {JEE (Main) 2021] In a semiconductor, the number

density of intrinsie charge carriers at 27 °C is 1.5%10!° per

m’, If the semiconductor is doped with impurity atom, the

hole density increases to 4.510" per m’. The electron

density in the doped semiconductor is

(a) 10° perm — (b) 310° per m?

(©) 710° perm? (d) 5x10? per m>

f tans:

27. Suppose a pure Si erystal has 5x10" atoms per m?. It is,

doped by 1 ppm concentration of pentavalent As. If m=

1.5*10" per m’, the number of holes will be

(a) 5*10” perm? (6) 210° per m?

(€)4.5x10% perm (€) 45x10? perm?

Ans: (]

28, (AIPMT 2011) Pure Si at 500 K equal number of electron

(Me) and hole (nq) concentrations of 1.510" m®. Doping

by" indium increases m, to 4.5*10 m°, The doped

semiconductor is of|

(a) mtype with electron concentration me = $*10"

(b) p-type with electron concentration me = 2.5*10! ry

(©) type with electron concentration ng = 2.5%10° =

(@) p-type having electron concentration re = 5%10? mr

[Ans: ()]

29, JEE (Main) 2020] If a semiconductor photodiode can,

detect a photon with a maximum wavelength of 400 nm,

then its band gap energy is

()2eV W)15eV

©31eV @itev

[Ans: (€)]

). Ifthe forbidden energy gap in Ge is 0.72 eV, the maximum

wavelength of electromagnetic radiation which can create

an electron-hole pair in Ge, will be

(a) 1.72x10% m_(b) 9.5*10°m

(©)42%10%m (4) 3.210% m

Ans: (9)

(EE (Main) 2022] The energy band gap _of

semiconducting material to produce violet” light,

(wavelength = 4000 A) is (Round off tothe nearest integer)

{a)3eV— (b) 7eV

()SeV (d) 1leV

(Ans: (9)

P-N JUNCTION DIODE

. (AIPMT) In a junction diode, the holes are due to.

(a) protons _(b) extra electrons

(e)neutrons (d) missing electrons

[Ans: (@)]

. (NEET 2013) In an unbiased p-n junction, holes diffuse

from the p-region to n-region because of

(a) the potential difference across the p-n junction

(b) the attraction of free electrons of n-region

(©) the higher hole concentration in p-region than that in

n-region

(@) the higher concentration of electrons in the n-region

than that in the p-region

Ans: ()]

|. (AIPMT) The depletion layer in the p-n junction region is

caused by

(a) drift of holes

(b) diffusion of charge carriers

(©). migration of impurity ions

(@) drift of electrons

Ans: (b)]

. (AIPMT) The cause of the potential barrier in a p-n diode

(a) depletion of positive charges near the junction

(b) concentration of positive charges near the jun:

(©) depletion of negative charges near the junction

(@) concentration of positive and negative charges near the

junction

Ans: (@)]

|. (AIPMT) A depletion layer consists of

{a)electrons —_(b) protons.

ions (@) immobi

enna GOMPILED BY: SATISH KUMAR SUR DC H

37. (AIPMT 2003) Barrier potential of a p-n junction diode

does not depend on

(a) doping density (b) diode design

(©) temperature (d) forward bias

Tans: (b)]

(AIPMT 2014) The barrier potential of a p-n junction

depends on

(A) type of semiconductor material

(B) amount of doping

(©) temperature

Which one of the following is correct?

(a) (A) and (B) only (6) (B) only

(©)(B) and (©) only (@) (A), (B) and (C)

Tans: @]

. [JEE (Main) 2023] Statement 1: When a Si sample is

doped with Boron, it becomes p-type semiconductor and

when doped by Arsenic it becomes n-type semiconductor

such that p-type has excess holes and n-type has excess

electrons,

Statement II: When such p-type and type

semiconductors, are fused to make a junction, a current

will automatically flow which can be detected with an

‘externally connected ammeter.

In the light of above statements, choose the most

appropriate answer from the options given below:

(a) Both Statement I and statement Il are incorrect

(b) Statement | is incorrect but statement Il is correct,

(©) Both Statement I and statement Il are correct

(@) Statement | is correct but statement Il is incorrect,

TAns: (d)]

[JEE (Main) 2022} If the potential barrier across a p-n

junction is 0.6 V, then the electric field intensity, in the

depletion region having the width of 610 m, will be

(a) 2x10 NIC (b) 4105 NIC

(©) Sx10°NIC (@) 10° NIC

(Ans: ()]

|. (AIPMT) p-n junction is said to be forward biased when

(a) The positive pole of the battery is joined to the n-

semiconductor and p-semiconductor

(b) The positive pole of the battery is connected to n-

semiconductor and p-semiconductor

(©) The positive pole of the battery is joined to the p-

semiconductor and negative pole to the nm

semiconductor

(@) A mechanical force is applied in the forward direction

TAns: (€)]

(AIPMT 2011) In forward biasing of the p-n junction

{(@) the positive terminal of the battery is connected to p-

side and the depletion region becomes thick

(b) the positive terminal of the battery is connected to n-

side and the depletion region becomes thin

(©) the positive terminal of the battery is connected to n-

side and the depletion regions becomes thick

(@) the positive terminal of the battery is connected to p-

side and the depletion region becomes thin

4B.

[Ans: (@)}

(AIPM'T) In the case of forward biasing of p-n junction,

which one of the following figures correctly depicts the

direction of flow of carriers?

tAns: (@)]

J. (AIPMT 2002) In forward biasing of p-n junction diode

(a) the potential of the p and n-sides becomes higher

altemately

(b) the p-side is at higher electrical potential than the n-

side

(©) the n-side is at higher electrical potential than the p-

side

(@) both the p and n-side are at the same potential

[Ans: (b)]

. (AIPMT) In forward bias, the width of potential barrier in

ap-n junction diode

(a) increases

(©) remains constant

[Ans: (b)}

(b) decreases

(@) first 1 and then 2

. (AIPMT 2005) Application of a forward bias to a p-n

junction

(a) widens the depletion zone

(b) increases the potential difference across the depletion

zone

(©) increases the number of donors on the n-side

(@) increases the electric field in the depletion zone

Ans: (©)]

1. What happens to the width of depletion layer of a p-n

Jjunction diode when itis reverse biased?

(a) increases

(©) decreases

(6) remains same

(@) increases frst and then decreases

[Ans: (a)

. (NET 2020) The increase in the width of the depletion

region in a p-n junction diode is due to

(a) reverse bias only

(b) both forward bias and reverse bias

(©) increase in forward current

(@) forward bias only

[Ans: (a)

TEs COMPILED BY: SATISH KUMAR SIR

49. (AIPMT) A semi-conducting device is connected in a

series circuit with a battery and a resistance. A current is

found to pass through the circuit, If the polarity of the

battery is reversed, the current drops to almost zero, The

device may be

(a) A p-n junction

(b) An int

(©) A p-type semiconductor

(@)_Annetype semiconductor

Tans: (a)

(NEET 2018) In a p-n junction diode, change in

temperature due to heating

(2) does not affect resistance of p-n junction

(b) affects only forward resistance

(6) affects only reverse resistance

(2) affects the overall V-i characteristics of pon junction

Tans: (]

(AIPMT 2003) Reverse bias applied to a junction diode

(a) Increase the minority carrier current

(b) Lowers the potential barrier

(©) Raises the potential barrier

(@) Increases the majority carrier current

[Ans: (¢)]

. (NEET 2022) In the given circuits (a), (b) and (c), the

potential drop across the two p-n junctions are equal in

@

(EIK}—1RIFh

NIE} —{HIF}

cs

@

(a) circuit (a) only (by circuit (by only.

(©) circuit (c) only (4) both circuits (a) and (c)

fans: (@)]

. [JEE (Main) 2022] For using a multimeter to identify

diode from electrical components, choose the correct

statement out ofthe following about the diode.

(a) It is two terminal device which conducts current in

both directions.

(b) It is two terminal device which conducts current in one

direction only.

(©) It does not conduct current gives an initial deflection

which decays to 2er0.

(A) It is three terminal device which conducts current in

‘one direction only between central terminal and either

of the remaining two terminals.

Ans: (b)]

|. (AIPMT) When a p-n junction diode is reverse biased the

flow of current across the junction is mainly due to

(a) diffusion of charges

(b) drift of charges

(€) depends on the nature of material

(@) both drif and diffusion of charges

[Ans: (b)}

. [JEE (Main) 2023] Given below are two statements: one

is labelled as Assertion A and the other is labelled as

Reason R.

Assertion A: Diffusion current in a pon junction is greater

than the drift current in magnitude if the junction is

forward biased,

Reason R: Diffusion current in a p-n junction is from the

de to the p-side ifthe junction is forward biased.

Inthe light ofthe above statements, choose the most

appropriate answer from the options given below:

(@) Both A and R are correct and R is the correct

explanation of A

(b) Both A and R are correct but R is not the correct

explanation of A

(©) Ais correct but R isnot correct

(@) Ais not correct but R is correct

Tans: (©)

(EE (Main) 2022] A potential barrier of 0.4 V exists

across a p-n junction. An electron enters the junction from

the n-side with a speed of 6x10° mvs. If the speed with

Which electron enters the p-side is ¥x 20° ms, then the

value of x will be (Given mass of electron = 9*10"" kg,

charge on electron = 1.6*10" C)

@I 16

©l4 @s

[Ans: (e)]

. (AIPMT) A p-n junction diode can be used as

(a) condenser (b) regulator

(amplifier (a) rectifier

) 2021] For the forward biased diode

characteristics shown in the figure, the dynamic resistance

at fp = 3 mA will be

4

@ 102 @isa

@5Q @25a

Ans: (@)]

59, JEE (Main) 2022] The 1-V characteristics of a p-n

Junction diode in forward bias is shown in the figure.

TE

5, KUMARI PHYSICS CLASSESC‘trutot or xcteNcO_ (XI, XIl, NEET & JEE]

Tend) 10p-—

3

0 2 244d

Yevol) —>

‘The ratio of dynamic resistance, corresponding to forward

bias voltages of 2 V and 4 V respectively, is

(1:2 Sit

1:40 (@)2

Tans: (b)]

60. (AIPMT 2000, 2006, NEET 2017) The forward biased

diode is

eo +2v

Ans: (@)]

61. (NEET 2020) Out of the following, which one is a forward

biased diode?

wo Li —-3v

oy 2Y pp ww — 2

7} wt — 5

op 20

Ans: (3))

62, (AIPMT 2004) Of the diodes. shown in following

diagrams, which one is reverse biased?

a]

i a

Ow

(Ans: (a)

63, (AIPMT 2011) In the following figure, the diodes which

are forward biased are

vov

te wt

a

© say

e oe s

Lev

©

+ A

sv

{a)Conly (b) Cand A

()BandA (@)A, Band D

[Ans: (b)}

64, (NEET 2022) In half wave rectification, if the input

frequency is 60 Hz, then the output frequency would be

(a) zero (b) 30 Hz

(©)60H2 (a) 120 Hz

fans: (0

65. (NEET 2023) A full wave rectifier circuit consists of two

p-n junction diodes, a centre-tapped transformer, capacitor

and a load resistance. Which of these components remove

the ac ripple from the rectified output?

(a) A centre-tapped transformer

(b) p-n junction diodes

(©) Capacitor

(@) Load resistance

[Ans: (©]

66, (AIPMT 2014) If in p-n junction, a square input signal of

10 Vis applied as shown,

+5V

P RL

o5v.

then the output across Ry will be

10¥; a

@ ©

“sv

sy os po

© ©

= 10

[Ans: (0)

67. {JEE (Main) 2022] In the given circuit the input voltage

Vjq is shown in figure.

sec.)

D,

y,

The cut~in voltage of p-n junction diode (Dy or D,) is 0.6

V. Which of the following output voltage (Vg) waveform

across the diode is correct?”

wh 0 fh

i

\

@

nm

()

|. [JEE (Main) 2021] Statement I: To get a steady dc.

© (-fi),

@) (1)-Gi), 2), Gili), (@4{iv)

Ans: (a)]

‘output from the pulsating voltage received from a full

‘wave rectifier we can connect a capacitor across the output

parallel to the load Ry,

Statement II: To get a steady dc. output from the

pulsating voltage received from a full wave rectifier we

‘can connect an inductor in series with Ry.

In the light of the above statements, choose the most

appropriate answer from the options given below:

(a) Statement I is true but Statement Il is false

(b) Statement I is false but Statement Il is true

(©) Both Statement | and Statement IL are false

(@) Both Statement I and Statement Il are true

Ans: (@)]

[JEE (Main) 2022] Two ideal diodes are connected in the

network as shown in figure.

200? is

TAns: (@]

. (AIPMT) In figure, the input is across the terminals A and

Cand the output is across B and D.

s n.

x

A

D

‘Then the output is

(a) zero (b) same as the input

(e) half wave rectified (A) full wave rectified

Tans: (@)]

69, (JEE (Main) 2021] Match List I with List I

List 1 List 11

(1) Rectifier (Used either for stepping

up or stepping down the

ac. voltage

(ii) Used to convert a.c,

voltage into d.c. voltage

(Git) Used to remove any ripple in

the rectified output voltage

(iv) Used for constant output

voltage even when the input

voltage or load current change

Choose the correct answer from the options given below:

(@) (Hi), iv), B)0), @iii)

&) (Ki), @iv), @-(). @Ei

Q) Stabilizer

B.

(3) Transformer

4) Filter

©,

1S. KUMARE: PHYSICS CLASSES isrmaot or excettence)

‘The equivalent resistance between A and B is

(552 (b)202

259 @15Sa

Ans: (€)]

(AIPMT 2002) A dic. battery of V volt is connected to a

series combination of a resistor R and an ideal diode D as

shown in the figure below. The potential difference across

Rowill be

a 0,

—S"

(a) 2V when diodes Torward Biased

(b) Zero when diode is forward biased

(©) V when diode is reverse biased

(@) V when diode is forward biased

Ans: (d)]

(AIPMT 2015) In the given figure, a diode D is connected

to an external resistance R = 100 Q and an emf of 3.5 V. If

the barrier potential developed across the diode is 0.5 V,

the current in the circuit will be?

°

too

R

L4)—__]

35

———_

(@)40.mA (6) 20mA.

(©)35mA (a) 30mA

(Ans: (@))

74. (NEET 2016) Consider the junction diode as ideal. The

value of current flowing through AB is

ri Mae

A__py win 3

ta

(aOA (b) 107A

(1A (103A

tAns: ()1

75. {JEE (Main) 2020] When a diode is forward biased, it has

voltage drop of 0.5 V. The safe limit of current through

the diode is 10 mA. Ifa battery of emf 1.5 V is used in the

circuit, the value of minimum resistance to be connected in

series with the diode so that the current does not exceed the

safe limit is

(a) 1002 (b)s00

{3002 (@)2002

(Ans: (a)]

76. (AIPMT) The diode used in the circuit shown in the figure

has a constant voltage drop of 0.5 V at all currents and a

maximum power rating of 100 mW.

Rk 05y

sai — Dt

sv

What should be the value of the resistance R connected in

series with the diode, for obtaining maximum current i?

(a)2002 ()6.679

(52 (@1sa

tAns: (6)

77. (JEE (Main) 2018] The reading of the ammeter for a

silicon diode in the given circuit is

2000

(a) 15 mA (b) 11.5 mA

(©) 13.5 mA (a) zero

(Ans: (6)]

NOTE: 1. The potenti in forward biasing of

Si based p-n junction diode is 0.7 V.

2. The potential barrier in forward biasing of Ge based

p-n junction diode is 0.3 V.

(AIPMT 2001) If internal resistance of cell is negligible,

2B. f

then current flowing through the circuit is.

po} wr

= 42

4

3 z

wea Wea

ZA Wea "

(Ans: (b)]

79. (AIPMT 2012) Two ideal diodes are connected to a

battery as shown in the circuit,

Dy 108

ai

20a

Cf $v fo

ey Ie

‘The current supplied by the battery is

(a)0.75A (b) zero

(025A (@)05A

Ans: (@)]

80. (NEET 2016) The given circuit has two ideal diodes

81. (JEE (Main) 2021] A 5 V battery is connected acros:

82,

connected as shown in the figure below.

20

a $0

10v- he oa

‘The current flowing through the resistance Ry will be

(143A (b)3.13A

(925A (@)10A

[Ans: (c))

the

points X and Y. Assume Dy and Dz to be normal silicon

diodes.

XY

What is the current supplied by the baitery, if the positive

terminal ofthe battery is connected to point X?

(05 A

Q)ISA

(043A

[JEE (Main) 2019) The circuit shown below contains two

ideal diodes, each with a forward resistance of 30.”

exceiuence,

000.

If the battery voltage is 6 V, the current through the 100 2

resistance (in Amperes) is

(a) 0.027 (b) 0.020

(©) 0.030 (4) 0.036

Ans: (b))

83. [JEE (Main) 2021} The circuit contains two diodes each

with a forward resistance of 50.0 and with infinite reverse

resistance.

D,

1300

D,

1200

ev

voTtage 1s

Ifthe bat

resistance is

(a) 10 mA

(©) 20 mA

1 Fans: (9)

Tie CurTENt Through the 120.0

(b) 5 mA,

(@4ma

84. JEE (Main) 2022] The cut-off voltage of the diodes

7 (shown in figure) in forward bias is 0.6 V.

oa Pr

AND

+6

OD,

i we

Vv 40s

‘The current through the resister of 40.9 is

(@)20mA (b)4mA.

(© 12mA (@)8mA

Ans: (b)]

85, [JEE (Main) 2022] As per the given circuit, the value of

current through the battery will be

Db

pin

De

100% en Zion

(@2A

ISA

(b)25A

@IA

| ey

©,

86. [JEE (Main) 2023] In the given circuit, the current /

through the battery will be

100 py

Ler,

@ISA

(254

Ans: (@)]

@IA

@2A

87. Ifeach of the diode has a forward bias resistance of 25 0

and infinite resistance in. reverse bias, the values of

ceurrents fy, fz fy and Iy are

P 250

Aw

db 1250

b 1250

eb pew

1

ay 250

sv

a

(a) 0.15 A, 0.05 A, 0, 0,025 A

(b) 0.05 A, 0.025 A, 0, 0.025 A

(©) 0.05 A, 0.05 A, 0, 0.125 A.

(a) 0.0 A, 0.025 A, 0, 0.025 A

Ans: (6)

88, [JEE (Main) 2021] In the given figure, each diode has a

forward bias resistance of 30 © and infinite r

reverse bias hon

tn

1300

1300

Ht

“hay 39

7200

The current / willbe

(@)3.75A (b)4A

(©)2A (2) 2.734

(Ans: (©)

89, (JEE (Main) 2023] If each diode has a forward bias

resistance of 25 @ in the below circuit

(SYMBOL OF EXCELLENCE)

on.

93.

Which of the following options is correct?”

@p=1 @e=1

[JEE (Main) 2019] Ge and Si diodes start conducting at

0,3 V and 0.7 V respectively. In the following figure if Ge

diode connection are reversed, the value of Vo changes by

(assume that the Ge diode has large breakdown voltage)

a

g

Me

aK

(@)06V_ (O8V

©@04V @02V

[Ans: (©)]

[JEE (Main) 2020] Both the diodes used in the circuit

shown are assumed to be ideal and have negligible

resistance when these are forward biased.

DA Day

127v

ow

Built in potential in each diode is 0.7 V. For the input

voltages shown in the figure, the voltage at point A is

@6V WRV

©@3V @9V

[Ans: (b)]

. [JEE (Main) 2021] Zener breakdown occurs in @ p-n

junetion having p and n both

(@) lightly doped and have wide depletion layer

(b) heavily doped and have narrow depletion layer

(©) lightly doped and have narrow depletion layer

(d) heavily doped and have wide depletion layer

[Ans (b)]

(NEET 2021) Consider the following statements (A) and

(B) and identify the correct answer.

(A) A zener diode is connected in reverse bias, when used

asa voltage regulator.

(B) The potential barrier of p-n junction lies between 0.1,

V1003 V.

(a) (A) is incorrect but (B) is correct

(b) (A) and (B) both are correct

(©) (A) and (B) both are incorrect

(A) (A) is correct and (B) is incorrect

fAns: (4)]

. [JEE (Main) 2023] Choose the correct statement about

Zener diode:

(a) It works as a voltage regulator in reverse bias and

bbchaves like simple p-n junction diode in forward bias.

(b) It works as a voltage regulator in both forward and

reverse bias.

(©) tworks a voltage regulator only in forward bias.

(@) It works as a voltage regulator in forward bias and

bochaves like simple p-n junction diode in reverse bias.

Ans: (a)]

98. (AIPMT 2005) Zener diode is used for

(a) amplification

(b) rectification

(©) stabilization

(@) producing oscillations in an oscillator

[Ans: ()]

96, [JEE (Main) 2023] Given below are two statements : one

is labeled as Assertion A and the other is labeled as Reason

R

Assertion A: Photodiodes are used in forward bias usually

for measuring the light intensity.

Reason R: For a p-n junction diode, at applied voltage V.

the current in the forward bias is more than the current in

the reverse bias for [Vel > +V 2 |Vol where Vo is the

threshold voltage and Vy is the breakdown voltage.

In the light ofthe above statements, choose the correct

answer from the options given below:

(a) Both A and R are true and R is correct explanation A

(b) Both A and R are true but R is NOT the correct

explanation A.

(©) Ais false but Ris true

(@) Aistrue but Ris false

(Ans: (61

97. (NEET 2023) Given below are two statements:

Statement I: Photovoltaic devices can convert optical

radiation into electricity.

Statement I: Zener diode is designed to operate under

reverse bias in breakdown region.

Inthe light of the above statements, choose the most

appropriate answer from the options given below:

(a) Both Statement I and Statement Il are correct.

(b) Both Statement I and Statement I! are incorrect

(©) Statement | is correct but Statement Il is incorrect

(@) Statement lis incorrect but Statement II is correct

Ans: (@)]

98. [JEE (Main) 2020] Take the breakdown voltage of the

Zener diode used in the given circuit as 6 V. For the input

voltage shown in figure below, the time variation of the

output voltage is (graphs drawn are schematic and not 10

scale)

{ fAns: (6)

Do.

99. |JEE (Main) 2021] Choose the correct waveform that can

represent the voltage across R of the following circuit,

assuming the diode as ideal one.

t [Ans: (b)]

1)0.{3EE (Main) 2020} Two Zener diodes (A and B) having

"& breakdown voltages of 6 V and 4 V respectively, are

connected as shown in the circuit below.

The output voltage Vo variation with input voltage linearly

increasing with time, is given by (Vingue= 0 V at ¢ = 0)

{_ (figures are qualitative)

}|ATISH KUMAR SI.

101.{JEE (Main) 2022] In the given circuit- the value of

‘current J, will be

80022

(@)3ma

(©4ma

fAns: (b)]

(b)5mA

(@)6mA

102.(AIPMT 2011) A Zener diode, having breakdown voltage

equal to 15 Y, is used in a voltage regulator circuit shown

in figure.

‘The current through the diode is

(@)10mA- (b) 15 mA

()20mA (Sma

Ans: (a)]

103,{JEE (Main) 2019] The reverse breakdown voltage of a

Zener diode is 5.6 V in the given circuit.

2000

‘The current /z through the Zener is

(@)7mA — (b) 17 mA

(© 10mA (4) 1SmA

Ans: (¢)]

104,{JEE (Main) 2021] The Zener diode has a Zener voltage

/, = 30 V. The current passing through the diode for the

following circuit is

449

v, — vi,

[ ‘Hi

sma

(9 mA

ov

Es

(0) 6 mA

(8 mA

tAns: (€)]

105,[JEE (Main) 2019] For the circuit shown below, the

‘current through the Zener diode is

120v>

(a)SmA

(© 14ma

Ans: (@)]

(b)zer0

(@) 9 mA

106,[JEE (Main) 2021] For the circuit shown below, the value

of Iz will be

R,= 10000

(b) 0.15A

(005A

(a) 25 mA

(O14

(Ans: (a)]

107,{JEE (Main) 2021] In connection with the circuit drawn

below, the value of current flowing through 2 k® resistor is

TRO

|

lov

(b) 15x104 A

(@)SS5x104A

sv

(a) 25104 A,

(©) 1Sx104 A

[Ans: (a)]

108,[JEE (Main) 2022] In the circuit shown below, maximum,

zener diode current will be

440

100.125) ve

(a)6mA_—(b)3mA

(©)12mA (a) 9mA

fAns: (d)}

109,{JEE (Main) 2021] The value of power dissipated across

the le (Vz = 15 V) connected in the circuit as

shown inthe figure is

(0) 3.5 W

@osw

@iw

@1SW

Ans: (a)]

110.{JEE (Main) 2022] An $ V zener diode along with a series

resistance R is connected across a 20 V supply as shown in

the figure.

1

20v

Ifthe maximum zener current is 25 mA, then the minimum

value of R will be

(@) 240 (6) 4800

(©3209 (a) 1600

Ans: (b)]

LIL[JEE (Main) 2023] A zener diode of power rating 1.6 Wis

to be used as voltage regulator.

&

Unregulated Regulated

volage vollage

If the zener diode has a breakdown voltage of 8 V and it

has to regulate voltage fluctuating between 3 V and 10 V,

‘The value of resistance R, for safe operation of diode will,

be

@) 1330

(10a

Ans: ())

@) 129

@139

112.|JEE (Main) 2021] A zener diode having zener voltage §

V and power dissipation rating of 0.5 W is connected

across a potential divider arranged with maximum

potential drop across zener diode is as shown in the

diagram.

20V

The value of protective resistance Rp is

(@) 862 (b) 192.0

432 (@129a

[Ans: (b)}

113, [JEE (Main) 2021] In a given circuit diagram, a $ V zener

diode along with a series resistance is connected across a

50 V power supply.

qaEEREntes

<2 COMPILED BY: SATISH KUMAR SIRS

The minimum value of the resistance required, if the

‘maximum zener current is 90 mA, will be

@ 2002 2509

} @400Q (@s00Q

f Tans: @

114, [JEE (Main) 2022] A Zener diode of breakdown voltage

Vz = 8 V and maximum zener current, faq = 10 mA is

subjected to an input voltage Vj = 10 V with series

resistance R = 100 © In the given circuit Ry represents the

Variable load resistance,

[ R=1000

V.=10V n oa

Ve=8v]

l= 10mA

‘The ratio of maximum and minimum value of R, is

(5:3 (b)221

(6:5 @Sz1

Tans: (b))

HISJEE (Main) 2019] The figure represents a voltage

regulator circuit using a Zener diode.

R

Ry

The breakdown voltage of the Zener diode is 6 V and the

load resistance is Ry = 4 kA. The series resistance of the

circuit is R; = 1 KQ. If the battery voltage Vp varies from 8

V to 16 V, what are the minimum and maximum values of

the current through Zener diode?

(a)0.5mA,6mA — (b) 0.5 mA, 8.5 mA

(e) LS mA, 8.5 mA (d) 1 mA, 8.5 mA

Tans: (0)}

116,[JEE (Main) 2021] For the given circuit, the power across,

‘zener diode is

1a

(@) 0.12

(90.15 W

[Ans: (a)]

(b) 0.2 W

(0.18 W

INLIEE (Onin) 2019] Figure shows « DC voltage regulsor

circuit, with a Zener diode of breakdown voltage =

Is

R= dk

If the unregulated input voliage varies Between 10 V to 16

‘V, then what isthe maximum Zener current?

(@)25mA —(b)3.5mA

(©7SmA @1SmA

Tans: (0)

118,{JEE (Main) 2020] The circuit shown below is working as

a8 V de. regulated voltage source.

2000

w

[»

‘When 12 V is used as input, the power dissipated (in mW)

in each diode is (considering both zener diodes are

identical)

(40° (6) 20

© @so

Tans: (a)

2000

119.{JEE (Main) 2021] A zener diode of power rating 2 W is

tobe used as.a voltage regulator.

R,

Unregulated

volte

If the zener diode has a breakdown OF TO-V-and it has to

regulate voltage fluctuated between 6 V and 14 V, the

value of R, for safe operation should be

@10Q (sa

(@15SQ (@2a

[Ans: (@)]

120,[JBE (Main) 2019] In the given circuit the current through

Zener diode is close to

122,

123.

128.

ws.

(a)6mA (b)4 mA.

()6.7mA (d) zero

(Ans: (@]

121.(AIPMT 2008) A p-n photodiode is made of a material

with a band gap of 2 eV. The minimum frequency of the

radiation that can be detected by the material is nearly

(a) 1010" Hz (b) x10" Hz

(©) 1x10" Hz (d) 2010" Hz

[Ans: (6))

(VEE (Main) 2021] LED is constructed from Ga-As-P

semiconducting material. The energy gap of this LED is

1.9 eV. The wavelength of light emitted and its colour will

be (h = 6.63x10™ Js and c = 3x10" m/s)

(@) 1046 nm and red colour

(©) 654 nm and orange colour

(©) 1046 nm and blue colour

(@) 654 nm and red colour

TAns: ()]

[SEE (Main) 2020] With increasing biasing voltage of

photodiode, the photocurrent magnitude

{@) increases initially and saturates finally

(b) increases initially and after attaining certain value, it

decreases

(©) increases linearly

(@) remains constant

Ans: (@)]

[JEE (Main) 2022] The photodiode is used to detect the

‘optical signals. These diodes are preferably operated in

reverse biased mode because

(@) fractional change in majority carriers produce higher

forward bias current

(©) fractional change in majority carriers produce higher

reverse bias current

(©) fractional change in minority carriers produce higher

forward bias current

(@) fractional change in minority carriers produce higher

reverse bias current

Ans: ()]

[JEE (Main) 2023] Given below are two statements: one

is labelled as Assertion A and the other is labelled as

Reason R.

Assertion A: Photodiodes are preferably operated in

reverse bias condition for ight intensity measurement.

Reason R: The current in the forward bias is more than the

‘current in the reverse bias for a p-n junction diode.

In the light of the above statements, choose the correct

answer from the options given below:

(a) Ais false but R is true

(b) Both A and R are true but R is not the correct,

explanation of A

(©) Ais true but Ris false

(@) Both A and R are true and R is the correct explanation

ofA

fAns: (b))

126. (AIPMT 2009) A p-n photodiode is fabricated from a

. [JEE (Main) 2021} Consider a situation in which reverse

1. [JEE (Main) 2022} Identify the solar cell characteristics

|. (AIPMT 2014) The given graph represents Y-I

3b OF EXCELLENCE

semiconductor with a band gap of 2.5 eV. It can detect a

signal wavelength

(a) 4950 nm (b) 6000 nm

(©4000 (d) 6000 A

[Ans: (a)]

1. (AIPMT 2004) In a p-n junction photocell, the value of the

photo-clectromotive force produced by monochromatic

light is proportional to

(a) the voltage applied at the p-n junction

(b) the barrier voltage at the p-n junction

(©) the intensity of the light falling on the cell

(@) the frequency of the light falling on the cell

(Ans: (©)

biased current ofa particular p-n junction increases when it

is exposed t0 a light of wavelength < 621 nm. During this

process, enhancement in cartier concentration takes place

due to generation of hole-electron pairs. The value of band

‘gap is nearly

()2eV (b)4eV

lev @OSev

Ans: (@))

from the following options:

y 1

() Oo}

y y

© @

TWO

¥

Ans: (b)]

characteristics for a semiconductor device.

{|

i

v=

ak

Which of the following statements is correct?

(@) It is V-I characteristic for solar cell where, point A

represents open circuit voltage and point B short

cirouit current

(b) Is for solar cell and point A and B represents open

ircuit voltage and current respectively

(©) Itis for photodiode and point A and B represents open

circuit voltage and current respectively

(@) Wis for LED and point A and b represents open circuit

voltage and short circuit current, respectively

[Ans: (a)

eet

EOE OOMP LER BY; SATISH SH KUMAR SIRS sisters

131, SEE (Main) 2023] Which of the following statement is

| Rot correct in the case of light emitting diodes?

A. Itisa heavily doped p-n junetion,

B. It emits light only when it is forward biased.

. Items light only when iti reverse biased.

D. The energy of the light emitted is equal to or slightly

less than the energy gap of the semiconductor used.

Choose the correct answer from the options given

below:

(CandD A

, wc @B

3, (Ans: (©)

4 TRANSISTOR

132. [JEE (Main) 2023] Given below are two statements:

Statement I: In a typical transistor, all three regions

emitter, base and collector have same doping level.

Statement Il: In transistor, collector is the thickest and

base isthe thinnest segment.

In the light of the above statements, choose the most

appropriate answer from the options given below:

(a) Both Statement I and Statement Il are correct

(b) Both Statement [and Statement Il are incorrect

(€) Statement is incorrect but Statement Il is correct

§ (@) Statement is correct but Statement Il is incorrect

[Ans: (©)

133, (AIPMT) The part of the transistor which is heavily doped

to produce large number of majority carriers is

(a) emitter

(b) base

(©) collector

(@) any of the above depending upon the nature of

transistor

[Ans: (a)

134. In a transistor, if the doping level in base is increased

slightly then

(a) base current decreases and collector current increases

(b) base current increases and collector current decreases

(©) base and collector currents both increase

(@) base and collector currents both decrease

Ans: (b)]

135, (NEET 2020) For transistor action, which of the following,

statements is correct?

(a) Base, emitter and collector regions should have same

(b) Both emitter junction as well as the collector junction

| are forward biased

(©) The base region must be very thin and lightly doped

(@) Base, emitter and collector regions should have same

doping concentrations

[Ans: (©)]

136, (AIPMT 2010) For transistor action

(J) Base, emitter and collector r

size and doping concentrations

(2) The base region must be very thin and lightly doped

(3) The emitter-base junction is forward biased and base-

collector junction is reverse biased

(4) Both the emitter-base junction as well as the base-

collector junction are forward biased

@)G).4) (4).

©M.2) MQ)

[Ans: (@)]

. [JE (Main) 2022} Given below are two statements: One

is labelled as Assertion A and the other is labelled as

Reason R.

Assertion A: n-p-n transistor permits more current than a

p-n-p transistor.

Reason R: Electrons have greater mobility as a charge

Choose the correct answer from the options given

below:

(a) Both A and R are true and R is correct explanation of

A

(b) Both A and R are true but R is not the correct

explanation of A

(©) Aistrue but Ris false

(@) Ais false but R is true

[Ans: (@)

{AIPMT) To use a transistor as an amplifier

(a) The emitter base junction is forward biased and the

base collector junction is reverse biased

(b) No bias voltage is required

(©) Both junctions are forward biased

(@) Both junctions are reverse biased

Ans: (a)],

(AIPMT 2003) An n-p-n transistor conducts when

(a) Both collector and emitter are negative with respect to

the base

(b) Both collector and emitter are positive with respect to

the base

(©) Collector is positive and emitter is negative with

respect to the base

(@) Collector is positive and emitter is at same potential as

the base

Ans: (6)]

. (NEET 2013) One way in which the operation of an n-p-n

transistor differs from that of a p-n-p

(a) The emitter junction is reverse biased in n-p-n

(®) the emitter junction injects minority carriers into the

base region of the p-n-p

(©) The emitter injects holes into the base ofthe p-n-p and

electrons into the base region of n-p-n

(@) The emitter injects holes into the base of n-p-n

[Ans: (01

|. (AIPMT) When an n-p-n transistor is used as an amplifier

then

(a) the electrons flow from emitter to collector

(b) the holes flow from emitter to collector

(©) the electrons flow from collector to emitter

COMPILED BY: SATISH KUM,

AR.

SIRDHS Se

(@) the electrons flow from battery to emitter

TAns: (a)}

142, (AIPMT) In a common base amplifier the phase difference

between the input signal voltage and the output voltage is

@o

oF

@x

143, (AIPMT 2015) The input signal given to a CE amplifier

having a voltage gain of 150 is, = 2cos(15¢-+2) The

corresponding output signal will be

(a) 75¢0s(15t+2) — () 2cos(i5t +2)

(©)300c0e(15¢+%) (4) 300c0s(15¢+2

(Ans: ()]

144, The direct current gain for common emitter amplifier is 59.

Ifthe emitter current is 6 mA, the collector current is

(@) L6mA (b) 0.1 mA

(21 mA (d)5.9mA

tAns: (@)

14S. (AIPMT) The current gain for a transistor working as

common-base amplifier is 0.96, If the emitter current is 7.2

mA, then the base current is

(@)0.29 mA (b) 0.35 mA

(©)0.39mA (4) 0.43 mA.

tans: (a)]

146, (JEE (Main) 2021, AIPMT 2000] In the study of a

transistor as an amplifier, fa = 12 and f = 1 where fc,

Ig and I are the collector, base and emitter currents, then

the correct relation a and fis

@p=%= wp=*

O6= OB

(Ans: (3)

(EE (Main) 2021, AIPMT] The correct relationship

between the two current gains a (ratio of collector current

to emitter current) and fi (ratio of collector current to base

current) of a transistor is

=e e

B= Fo OES Tg

@a=5 wa=$

Ans: ()

148, (AIPMT 2001 Fora common enter crit if © = 05

then current gain for common emitter circuit will be

(49 (b) 98

©49 (255

(Ans: (a)]

149. (AIPMT 2002) In the case of @ common emitter transistor

amplifier, the ratio of the collector current to the emitter

current is 0.96, the current gain of the amplifier is

150.

Asi.

182.

153,

154.

155,

—_—_—_—_—_—_—_—_—_—_—_—_—

11S. KUMARS: PHYSICS CLASSES ernect or xcutence £XI, XIL, NEET & JEE]

36803763= 7503449542 _SH-5S, SHASTRI NAGAR, GHAZIABAD.

(a6 (b) 48

(24 (@i2

fAns: (&)

For a common emitter amplifier, ifthe values of resistance

gain and voltage gain are 3000 and 2800 respectively, the

power gain is

(a) 3600 (b) 2565

(©) 2604 (a) 1000

Ans: (©)

[JEE (Main) 2023] In an n-p-n common emitter (CE)

transistor the collector current changes from 5 mA to 16

mA for the change in base current from 100 4A and 200

MA, respectively. The current gain of transistoris

(@) 110 (6) 0.9

(210 (a9

TAns: (a)]

‘Two amplifiers are connected one after the other in series

(cascaded). The first amplifier has a voltage gain of 10 and

the second has a voltage gain of 20. If the input signal is

0.01 V, the output voltage will be

@2V_()02V

(©) 200V (@)20V

Ans: (a))

(NEET 2020) An n-p-n transistor is connected in common

emitter configuration (see figure) in which collector

voltage drop across load resistance 800 2 connected to the

collector circuit is 0.8 V.

The collector current is

(@)0.2mA (b)2mA

(©0.1mA (1 mA

(Ans: (d)]

[JEE (Main) 2021) If the emitter current is changed by 4

‘mA, the collector current changes by 3.5 mA. The value of

B will be

@7 (b) 0.5

(0875 (a) 3.5

Ans: (a)

(AIPMT 2011) A transistor is operated in common emitter

configuration at Ve = 2 V such that a change in the base

urettfrom 100 WA to 300 HA produces change in the

collector current from 10 mA to 20 mA. The current gain i

ome mA. The current gain is

(100 (a)25

Ans: (a))

so

186. (ALPMT 2006) A transistor is operated in common emitter

configuration at constant collector voltage V. = 1.5 V such

that a change in the base current from 100 HA to 150 WA

produces a change in the collector current S mA to 10 mA.

The current gain B is

(@) 75 (b) 100

(S067

Tans: (b))

. (AIPMT 2010) A common emitter amplifier has a voltage

gain of 50, an input impedance of 100 9 and an output

impedance of 200 2. The power gain of the amplifier is

(a) 500 (6) 1000

(© 1280 (@) 50,

[Ans: (€)]

. (AIPMT 2012) In a CE transistor amplifier, the audio

signal voltage across the collector resistance of 2 kA is 2

V. If the base resistance is 1 kQ and the current

amplification of the transistor is 100, the input signal

voltage is

@O1V

(@1mv

(iv

(@d) 10mV.

(AIPMT 2012) The input resistance of a silicon transistor

is 100 ©. Base current is changed by 40 HA which results

ina change in collector current by 2 mA. This transistor is

used as a common emitter amplifier with a load resistance

of 4 KO. The voltage gain of the amplifier is

(@) 2000) 3000

(©) 4000 (a) 1000

Ans: (9)

). (NEET 2016) For CE transistor amplifier, the audio signal

voltage across the collector resistance of 2k is 4 V. Ifthe

ccurrent amplification factor of the transistor is 100 and the

base resistance is 1 kO, then the input signal voltage is

{a)30mV (b) 1S mV

(©) 10mV (4)20mV

ans: (@)]

|. JE (Main) 2021] An n-p-n transistor operates as a

common emitter amplifier with a power gain of 10°. The

input circuit resistance is 100 and the output load

resistance is 10 k®. The common emitter current gain will

be

(a) 10

(©) 100

Tans: (0)

(b) 50

(@) 1000

(NEET 2017) In a CE transistor amplifier the audio signal

voltage across the collector is 3 V. The resistance of

collector is 3 kQ. If current gain is 100 and the base

resistance is 2 kQ, the voltage and power gain of the

amplifier is

(a) 15 and200_(b) 150 and 15000

(©) 20 and 2000 (4) 200 and 1000

Ans: (b)]

RE COMPILED BY: SATISH KUMAR siRnennnennnrt

163. In a common emitter transistor amplifier, the input

resistance of a transistor is 1000 ©. On changing its base

‘current by 10 HA, the collector current increases by 2 mA.

Ifa load resistance of $ k® is used in the circuit, the

‘current gain and voltage gain ofthe amplifier are

(a) 100, (b) 200, 1000

(©) 500, 1000 (a) 200, 300

Ans: (b)]

|. (NEET 2016) An n-p-n transistor is connected in common

emitter configuration in a given amplifier. A load

resistance of 800 2 is connected in the collector circuit and

the voltage drop across it is 0.8 V. If the current

amplification factor is 0.96 and the input resistance of the

circuit is 192 9, the voltage gain and the power gain of the

amplifier will respectively by

(a) 4,384 (b)3.69,3.84

(44 (43.69

TAns: (®)]

. (AIPMT) The transfer ratio f of a transistor is 50. The

input resistance of the transistor when used in the common

emitter configuration is 1 kQ. The peak value of the

collector AC current for an AC input voltage of 0.01 V

peak is

(2) 100 A (b) 0.01 mA

(©0.5mA (A) 200 nA

Tans: (0)

[SEE (Main) 2021) A transistor is connected in common

emitter cireut configuration, the collector supply voltage is

10 V and the voltage drop across a resistor of 1000 Q in

the collector circuit is 0.6 V. If the current gain factor (B)

is 24, then the base current is (Round off to the Nearest

Integer)

(2) 25 uA

(©) 15 pA

(Ans: @)

(b) 10 pa.

(@)20 na

[JEE (Main) 2022] A transistor is used in an amplifier

circuit in common emitter mode. If the base current

changes by 100 nA, it brings a change of 10 mA in

collector current. If the load resistance is 2 kO and input

resistance is 1 kQ, the value of power gain is

(a) 20000

(© 15000

Ans: (a)]

(b) 2000

(@) 1000

(EE (Main) 2019] An n-p-n transistor is used in common

emitter configuration as an amplifier with 1 KO load

resistance, Signal voltage of 10 mV is applied across the

base-emitter. This produces a3 mA change in the collector

current and 15 A change in the base current of the

amplifier. The input resistance and voltage gain are

(a) 0.339, 15 (6) 0.67 2, 200

(©) 0.33 KO, 300 (€) 0.67 KO 300

TAns: (a)

2,

22S. KUMARS PHYSICS CLASSES®(srmaot or exceLLeNcE 1X), XIL, NEET & JE]

169. [JEE (Main) 2022] A transistor is used in common-emitter

‘mode in an amplifier circuit. When a signal of 10 mV is

added to the base-emitter voltage, the base current changes

by 10 WA and the collector current changes by 1.5 mA. The

load resistance is 5 k9. The voltage gain of the transistor

will be

(250 (6) 750

(©) 500 (a) 1500

[Ans: (b)}

170, (NEET 2013) In a CE amplifier having a voltage gain G.

‘The transistor used has trans-conductance 0,03 mho and

current gain 25. If the above transistor is replaced with

another one with trans-conductance 0.02 mho and current

gain 20, the voltage gain will be

we ws

of @%

Ans: @}0

|. [JEE (Main) 2019] A common emitter amplifier circuit,

built using an n-p-n transistor, is shown in the figure.

Its direct current gain is 250, Re = 1 k® and Voc = 10 V.

What is the minimum base current for Veg to reach

saturation?

(@) 100A (0) 7 HA

(40 pA (A) 10 pA

[Ans: (¢)]

172, [JEE (Main) 2023] For a given transistor amplifier circuit

in CE configuration Vgc = 1 V, Re= 1 KO, Ry = 100 k@

and B = 100.

174,

178,

20v ;

Redaka

ic

Re

Wait J

The values of fy , ic and are given by

(8) ig =20 HA ic = S mA, B = 250

(b) fy =25 HA, ic =5 mA, B= 200

(©) ig =40 HA, ic = 10mA, f = 250

(@ ig =40 pA, ic = SA, B= 125

[Ans: (@)]

[JEE (Main) 2019] In the figure, given that Vyq supply

ccan vary from 0 to 5 V,Vec = $V. Bue = 200, Ry = 100

KO, Re = 1k and Vyg = LV.

‘The minimum base current and the input voltage at which

the transistor will go to saturation, will be, respectively

(8) 20 wAand2.8V (b)20 nA and 3.5.V

(©) 25 pAand3.5V (d) 20 pA and 2.8 V

Tans: 1

(JEE (Main) 2022] An n-p-n transistor with current gain 8

= 100 in common emitter configuration is shown in figure

i

10 ka

Vout

Value of base current Ip is

(a) 1yA—(6)0.1 HA

(©) 100 nA (d) 101A

[Ans: (d)]

173, (NEET 2018) In the circuit shown in the figure, the input

voltage V; is 20 V.

‘The output voltage of the amplifier will be

@OLV WIV

(10V @)100V

[Ans: (b)}

(EE (Main) 2019] An n-p-n transistor operates as a

common emitter amplifier, with a power gain of 60 4B.

‘The input circuit resistance is 100 Q and the output load

resistance is 10 k®. The common emitter current gain f is

(a) 60. () 10"

(©) 6x10? (a) 10°

[Ans: @)] 0

0. PI LED BY; SAT! SH KUMAR SIRS

177. (JE (Main) 2022} In an experiment of CE configuration

of n-p-n transistor, the transfer charactersties are observed

as given in figure,

ena)

8

0

s

aa

100 200 300 hase

If the input resistance 1s 200 2 and output resistance is 60

Q, the voltage gain in this experiment will be

(@)20 (by 10

(30 @is

tans: (@)]

. [JEE (Main) 2022] The t

Aload

of the circuit used. The input resistance of the trans

0.5 kQ. The voltage gain of the transistor is

(a) 150 (b) 800

(c) 500 (d) 200

tans: (1

). [SEE (Main) 2019] The transfer characteristic curve of

transistor, having input and output resistance 100 and

100 A respectively, is shown in the figure.

“400, 20)

1300, 15)

A200, 10)

(100, 5)

Gal

‘The voltage and power gain are respectively

(a) 5x10%, 5x10

(b) 5*10%, Sx10*

(o) Sx10*, 25x10"

(d) 2.5*108, 2.5%10°

(Ans: (©)

|, [JEE (Main) 2023] From the given transfer characteristic

of a transistor in CE configuration, the value of power gain

of this configuration is 10°, for Ry = 10 kA, and Re

Ka.

remy

9

rt)

30]

20

1a}

0)

100 200 300 400 S00, lar(itA)

The value of x is

2 Ss

4 3

Tans: (@)]

181, [JEE (Main) 2021] The typical output characteristies

curve for a transistor working in the common-emitter

configuration is shown in the figure.

Koma).

8

(a) 100

(©) 150

Ans: (@)]

(b) 50

(@) 200

182, [JEE (Main) 2020] The output characteristics

transistor is shown in the figure,

(te)

OHA

SOWA

=} 4008

3008

2OHA

=| 100A

Tris

6 8 10

(Va) in vos

When Veg is 10 V and le = 4 mA, then value of Bie is

lose to

(a) 100

(©) 150

Ans: ()Ie

(b) 50

(a 75

| VEE (Main) 2022] For a constant collector-emitter

voltage of § V, the collector current of a transistor reached

to the value of 6 mA from 4 mA, Whereas base current

changed from 20 WA to 25 WA value, If transistor is in

active state, small signal current gain (current amplification

factor) will be

(a) 240 (&) 400

(©) 0.0025 (a) 200

2S, KUMAR! PHYSICS CLASSES vwaot or excetuench_ 1X1, XiL, NEET & JEE)

SUS QUESTIONS FOR GOMPE XAMS FOR S ON 2023-20241 Fs

SRR ED BY: SATISH KUMAR SIRE 2:12

[Ans: (b)) (SV (@)20V

TRANSISTOR AS AN OSCILLATOR

189, (AIPMT 2006) A transis Fusing a resonant

circuit with an inductor L (of negligible resistance) and a

capacitor C in series produce oscillations of frequency f. If

{Lis doubled and ¢ is changed to 4C, the frequency will be

‘which aets as the base terminal,

Statement Hl: In the study of transistor, the amplification,

factor B indicates ratio of the collector current to the base

current. i

Inthe light of the above statements, choose the correct Oy, Wer

answer from the options given below: o5 ws

(a) Statement 1 is false but Statement Il is true

(b) Both Statement I and Statement Il are true

(©) Both Statement I and Statement Il are false

(@) Statement 1 is true but Statement Il is false

Tans: (a)]

tans: (©

190. [JEE (Main) 2022] The positive feedback is required by

an amplifier to act as an oscillator. The feedback here

(a) extemal input is necessary fo sustain a. signal in

188, (AIPMT 2012) Transfer characteristics [output voltage Vo 2 ‘output " e ™

¥s input voltage Vi} for a base biased transistor in CE (©) 4 portion ofthe ouput power is etumed back to the

configuration as show in the figure. inp

(©) feedback can be achieved by LR network

(@) the base-collector junction must be forward biased

[Ans: (b)] =

Vopt i

LOGIC GATES

191, (AIPMT) The symbol represents

vw

For using transistor as a switch, ts used ap

(2) in region 3 (b) both in region Land 3

(in region 2 (€) in region | (0) AND gate (@) NOR gate

tans: (1 (ONAND gate (a) OR gate

Tans: (1

186. [JEE (Main) 2022] For a transistor to act as a switeh, it

must be operated in 192, (AIPMT 2009) The

(a) active region sates are given below:

(b) saturation state only

(©) cut-off state only ol >

(@) saturation and cut-off state ws

pe oo

187, [JEE (Main) 2021] For a transistor in CE mode to be used

‘san amplifier, it must be operated in wt )—.

(a) both cut-off and Saturation —

(b) saturation region only,

(© cutoff region only wy >

(@) the active region only

jmbolic representation of four logic

laser The logie symbols for OR, NOT, and NAND gates are

respectively

188, [JEE (Main) 2021] A circuit is arranged as shown in OV. OH GY.G.H,

figure. The output voltage Vp is equal to 0.GiE) A). 0)

193, (AIPMT 2011) Symbolic representations of four logic

ales are as shown,

(a) 10 V(b) zero

Pick out which ones are for AND, NAND and NOT gates 199. (AIPMT 2001) The truth table given below is for which

respectively gate?

MAA. OO.@.M x ¥

OM.G.4) @ QA) 0 1

[Ans: (d)) 0 T

i T

1 0

(NEET 2020) Which of the following is called universal

‘gate? (@)XOR (6) OR

(a) NOT gate (b) OR gate (AND (d) NAND

(©) AND gate _(d) NAND gate Ans: (d)]

fans: (@)]

|. [JEE (Main) 2020] Which of the following gives a

The values of inputs A and B for the Boolean reversible operation?

cexpression(A + B). (AB)

(@A=1,B-1 ()A=0,B=1 = —e

@A=0,B=0 ()A=1,

Ans: (1

g. (AIPMT) Which of the following gates will have an

output of 12 2 OI

©4 @3

oD eS] | el

a iD D. > g resows a chet having wo pa jet ode,

8 we —bH

[Ans: ()] C >, mi

. (AIPMT) The following truth table corresponds tothe ale.

logic-gate

‘The gate which will be obtained by combining a NOT gate

with the above circuit will be

(OR gate (b) AND gate

(©) NAND gate () NOR gate

(a) NAND_ (BOR (Ans: (@)}

(AND (@)XOR

Ans: ()) . [JEE (Main) 2022] In the circuit, the logical value of A =

1 or B= 1 when potential at A or B is SV and the logical

(AIPMT 2000) A gate has the following truth table value of A = 0 or B = 0 when potential at A or Bis 0 V.

x B ¥ Dy

1 H

i o

0 1

0 0 8

The gate is sv

(AND (b) NOR

(OR — (@)NAND Fve0

Ans: (9)

‘The truth table of the given circuit will be

eco ok ooo

[Ans: (a)

203, (AIPMT 2004) The output of AND gate is 1

(a) if either input is zero

() if both inputs are zero

(6) iether or both inputs are 1

(@) only if both inputs are 1

[Ans: (@)]

[JE (Main) 2023] The logic gate equivalent to the given

circuit i

(@)ORGate _(b) NAND Gate

(©) NOR Gate (4) AND Gate

[Ans: (6)]

5. (JE (Main) 2023] Name the logic gate equivalent to the

diagram attached.

(NOR gate

(@) AND gate

(a) OR gate

(©) NAND gate

Ans: (b)]

206, (NEET 2019) The correct Boolean operation represented

by the circuit diagram drawn is

Bt

(a AND @)OR

(@)NAND (a) XOR

Ans: (@)]

207, {JEE (Main) 2023] The logic performed by the circuit

shown in figure is equivalent to

a

Y

b

(b) NAND gate

(@) NOR gate

(ANDaue

one

tense

208, (SEE (Main 2025} The ouput froma NAND gate having

fata A td given blow willbe

ar

;

ora"!

t

1

'

i

1

209, [JEE (Main) 2019] The logic gate equivalent to the given

logic circuit is

(@) OR

(NOR

Ans: (@)]

(BAND

(@) NAND

210, [JEE (Main) 2022] Identify the logic operation performed

by the given circuit :

a

(a) AND gate

(©) NOR gate

Ans: (a)]

(b) OR gate

(@) NAND gate

211, (NEET 2016) To get the output | for the following circuit,

the correct choice for the input is

215, [JEE (Main) 2019] The truth table for the circuit given in

the figure is

—DT

c.

} @)A=0.B=1,C 0

(A=1,B=1,C

Ans: (d)]

=0 (A=1B

=0 @A=1,B

212. (AIPMT 2012) To get an output Y = 1 in given circuit

Which of the following input will be correct:

[)}—

tAns: (b)]

213. (NEET 2013) The output X of the logic circuit shown in

figure will be

A

[>

pol

| @x-kB_ @x=A8

xe AB X= AB

[Ans: (b)]

214, (AIPMT 2007) In the following circuit, the output Y for

all possible inputs A and B is expressed by the truth table

oD

©

soxom sonon

moooy coon,

[Ans: (c)]

Ans: (a)]

216, (NEET 2020) For the logic circuit shown, the truth table is

A

°

°

1

1

A

°

°

1

1

Ans: (@)]

217. (NEET 2023) For the following loge ere, the ruth

table is

De

218, (NEET 2022)

A

i

‘The rath table Tor the given Togie Sire is

age AB

dojo «00

@otlt @o1

1 10

oa

ic AB

7

°

1

°

vo

01

10

14

©

Ses elo soo a0

fans: ()]

219, (JEE (Main) 2021]

As

Cc

Be

‘The logic circuit shown above is equivalent to

a Cc

sec) a

De

) C

”

Be

Ac

©

Ac

Bo—1

Ans: ()]

220, (AIPMT 2003) Following diagram performs the logic

A

—

(a) XOR gate —_(b) AND gate

(©) NAND gate (d) OR gate

Ans: (6)]

221. (NEET 2013) The output from a NAND gate is divided

into two in parallel and fed to another NAND gate.

A or

a } {|

‘The resulting gates

(@) NOT gate (b) AND gate

2,

NOR gate

Ans: (b)}

(a) OR gate

222. (AIPMT 2015) Which logic gate is represented by the

following combination of logic gates?

Ap

=

Bee

(a) NAND (by AND

(NOR (@)OR

Ans: (b)]

223, (AIPMT 2008) The circuit is equivalent to

NOR _NAND NOT

DoDb

(a) AND gate (b) NAND gate

(©) NOR gate (4) OR gate

Ans: (@)]

224, (NEET 2017) The given electrical network is equivalent to

DDD

(a) OR gate) NOR gate

(©) NOT gate (d) AND gate

[Ans: (b)]

225. The logic gate represented by the circuit shown in figure

will be

x

Y

8,

(a) OR gate (b) AND gate

(©) NAND gate (d) NOR gate

[Ans: ©)

226. {JEE (Main) 2021} Identify the logic operation carried out

by the given circuit.

(a) OR gate {BY AND gare

(©) NOR gate (a) NAND gate

Ans: (@)]

SYMBOL OF EXCELLENCE)

(a) OR gate

(©) NAND gate

tAns: (a)]

(b) AND gate

(A) NOR gate

[SEE (Main) 2021) Identify the logic operation carried

out.

A

Y

Bs

(a) OR gate (by AND gate

(©) NOR gate (d) NAND gate

[Ans: ()]

44, [JEE. (Main) 2021] The following logic gate is equivalent

D—--D-—

to

(a) NOR gate (b) OR gate

(©) AND gate (d) NAND gate

[Ans: (a)]

|. [JEE (Main) 2021] The output of the given combination

gates represents

A

B:

(a) XOR gate (b) NAND gate

(©) AND gate (4) NOR gate

[Ans: (b)]

AI, {JEE (Main) 2021] Which one of the following will be the

output of the given circuit?”

_—tp>—_b-

(a) NOR gate

(© AND gate

[ans: (@)]

(b) NAND gate

(@ XOR gate

; SATISH KUMAR SIRS

232, [JEE (Main) 2023] The logic operations performed by the

given digital circuit is equivalent to

—

BS

(a) AND gate (b) NOR gate

(©)OR gate (d) NAND gate

Tans: (a)

. (NEET 2016) What is the output Y in the following

when all the three inputs A, B, C are first O and

ae my

by 11

(0,0

(@) 1,0

(0,1

Ans: (@)]

[JEE (Main) 2021} In the logic circuit shown in the figure,

if input A and B are 0 to 1 respectively, the output at Y

would be

A

B

«tT wo

(©)may be 0 orl (a) none of these

Ans: (b)}

[JEE (Main) 2019] The output of the given logic circuit is

re

D-

(AB

(48 +B

Tans: (6)

() AB

(@) AB +AB

21S. KUMAR:x PHYSICS CLASSES©(svwsot or exceLtence IXI, XII, NEET & JEE]

[JEE (Main) 2020] Identify the operation performed by

the circuit given below

(@) AND

(OR

tAns: (a)

(b) NAND.

(@) NOT

237, (NEET 2018) In the combination of the following gates,

the output ¥ can be written in terms of inputs A and B as

A

Be

@AB+AB Q)AB+AB

@aB @ArB

tans: ()]

238. (JEE (Main) 2019] To get output 1 at R, for the given

logic gate circuit the input values must be

x

—D-

@X=0,Y=1

(@X=0,Y=0

[Ans: ()]

()X=1Y

@X=LY

239, (JEE (Main) 2020] In the given circuit, value of Y is

[>>—r

Cc _d

(@) will not execute

() 0

(©) toggles between 0 and 1

@1

n) 2021] Find the truth table forthe function Y

nthe following figure.

[Ans: OT

241. [JEE (Main) 2023] For the given logic gates combination,

the correct truth table will be

=e

pI

[Ans: (1

242, (JEE (Main) 2023] The output Y for the inputs A and B of

circuit is given by

Y~Ouput

(SYMBOL OF EXCELLENCE)

EXAI

Toneneno nena evarteoes COMPILED BY: SATISH KUMAR sngusricrnecimeeeerety

A AB

(a)? (b) a Q [Ans: (4)]

l

1

YX

T

1

1

0 $. [JEE (Main) 2020] In the following digital circuit, what

will be the output at Z, when the inputs (A, B) are (1,0),

{¥ (0,0), (ut), 1)

0

L

1

1

ad OT5P*

Bi

(@) 1,011 (6)0,1,0,0

©0,0,1,0 (@)1,1,0,1

“ Ans:

(Ans: (@)]

243. [JEE (Main) 2021] The truth table for the following logic

circuit is

. [JEE (Main) 2021] In the following logic circuit the

sequence of the inputs A, B are (0, 0), (0, 1), (1, 0) and (1,

ye

A

eo B

Q

= “The output ¥ For this sequence willbe

r (@)1,0,1,0 (b)0,1,0,1

L110 @0,01,1

0

0 Ans: (1

1

1

. (AIPMT 2011) The following figure shows a logic gate

(ans: ®)] circuit with two inputs A and B and the output Y.

244. (JEE (Main) 2021] Four NOR gates are connected as A Logic gate]

shown in figure. pe—| crcut

A

‘The voltage waveTorms OFA, Band Y are given

A

pe—

‘The truth table for the given figure is

‘The logic gate is

(@) AND (b) NOR

(OR (@) AND

Ans: (@)]

- (a) NAND gate (b) NOR gate

logical (OR gate (d) AND gate

below, is Ans: (@)]

hit Bh

251, (JEE (Main) 2022] A logic gate circuit has two inputs A

and B and output Y. The voltage waveforms of A, B and Y

are shown below:

A

B

1

YL

‘The logic Grout is

(@) AND gate (b) OR gate

(@)NOR gate (d) NAND gate

Ans: (a)]

Ans: (@)]

252. [JEE (Main) 2020] Identify the correct output signal Y in

the given combination of gates (as shown) for the given

249. (AIPMT 2012) The figure shows a logic circuit with two

inputs A and B.

inputs A and B and the output C. The voltage wave forms

across A, B and C are as given.

B.

A

(a) OR gate _(b) NOR gate

(©) AND gate (d) NAND gate

Tans: (a)]

. (AIPMT 2006) The following figure shows a logic gate

circuit with two inputs A and B and the output C.

a—

Logie gate!

‘circuit iS

The voltage waveforms of A, B and C are as shown below.

[Ans: ©

283. (JEE (Main) 2021)

A

7

B.

a

A—c

Ans: (4)

255, [JEE (Main) 2023] For the logic circuit shown, the output

waveform at ¥ is

The output signal V inthe given combination oF gates will

be

«©

a

(Ans:

256. (NEET 2021) For the given circuit, the input digital

signals. are applied at the terminals A, B and C. What

would be the output atthe terminal y?

Ans: ()]

254, [JEE (Main) 2023] For the following circuit and given

inputs A and B, choose the correct option for output Y.

. (JEE (Main) 2022] Identify the correct Logie Gate for the

following output (Y) of two inputs A and B.

[Ans: (6))

258, The input ‘A* shown here is used with another unknown

input “B’ is fed to a logic gate shown in dotted box, the

output *Y” has the form shown. The time intervals over

which the input ‘B” is necessarily in its high state are

#

elt ds.

wat deede ces

(a)0104&7108 (b)3t05&7to8

(©) 1to2&4to5 (d)2104 &6to7

fans: (0)

S¢SATISH KUMAR SIRX+

You might also like

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (822)