Professional Documents

Culture Documents

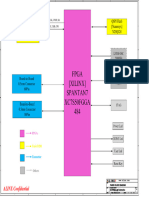

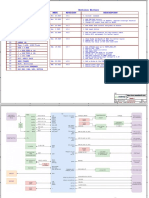

AntMiner ControlBoard XC7010 V1.01控制板-S9

Uploaded by

Satvik HardatOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

AntMiner ControlBoard XC7010 V1.01控制板-S9

Uploaded by

Satvik HardatCopyright:

Available Formats

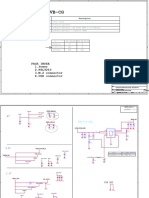

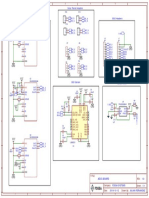

5 4 3 2 1

D

Boot Mode Select D

V3P3 V3P3

JP1 JP3

1 1

1 2 R1 20K 1 2 R2 20K

2 PS_MIO2_NAND_ALE 3,10 2 PS_MIO3_NAND_WE# 3,10

3 3

3 3

SIP_2.54mm SIP_2.54mm

V3P3 V3P3

JP2 JP4

1 1

1 2 R3 20K 1 2 R4 20K

2 PS_MIO4_NAND_DQ2 3,10 2 PS_MIO5_NAND_DQ0 3,10

C 3 3 C

3 3

SIP_2.54mm SIP_2.54mm

Boot Mode JP1 JP2 JP3 JP4

Cascade JTAG 0 0 0 0

TF Card 0 1 0 1

QSPI Flash 0 0 0 1

NOR Flash 0 0 1 0

NAND Flash 0 1 0 0

B B

A A

Title

AntMiner_ControlBoard_XC7010

Size Document Number Rev

A <Doc> V1.0

Date: Friday, July 01, 2016 Sheet 1 of 15

5 4 3 2 1

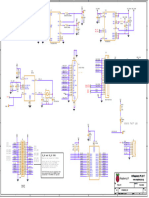

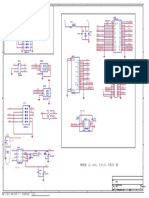

5 4 3 2 1

BANK 0

V3P3

R5 4.7K

R6 4.7K

U1A R7 4.7K

R8 4.7K

M9 J6 JTAG_TMS

D DXP_0 TMS_0 G6 JTAG_TDI D

TDI_0 F6 JTAG_TDO

M10 TDO_0 F9 JTAG_TCK

DXN_0 TCK_0 V3P3

R9 0 K9

VP_0 R10 R10 4.7K

INIT_B_0 L6 R11 4.7K

R12 0 L10 PROGRAM_B_0 R11 DONE

VN_0 DONE_0

K6 V3P3

VCCO_0 V3P3

FB1 R13 0 L9 T6

100R/3A R14 0 K10 VREFP_0 RSVDVCC1 R6

VREFN_0 RSVDVCC2

C1

C2

C3

C4

J10 N6

V1P8 GNDADC_0 RSVDVCC3 F10 D1

RSVDGND

G/25mA/0603

V3P3

10uF

0.1uF

0.1uF

0.1uF

FB2 J9

100R/3A VCCADC_0 M6

CFGBVS_0 V3P3

C C

C5

C6

R182

R17

F11

VCCBATT_0 R15 4.7K

R16

0.47uF

0.1uF

330

220

xc7z010clg400_10

0 D Q4

DONE G 2N7002-7-F

S SOT23_3

V3P3 V2P5

J10 V3P3

1 2 R18 0

3 1 2 4 JTAG_TMS R19 1K U2 R20 1K

B

5 3 4 6 JTAG_TCK 4 5 B

7 5 6 8 JTAG_TDO PS_SRST# 3 A2 B2 6 JTAG_RST# V3P3

9 7 8 10 JTAG_TDI 2 A1 B1 7

11 9 10 12 1 Vref_A Vref_B 8 R21 200K

13 11 12 14 JTAG_RST# V2P5 GND EN

13 14 LSF0102DCTR C7 0.1uF

HEADER 2X7

C8 0.1uF

V2P5

R22 4.7K S1

KMR231GLFS

R23 0 1 2

4 PS_MIO47_KEY_RESET R24 0 NC

4 PS_SRST#

3 4

A A

Title

AntMiner_ControlBoard_XC7010

Size Document Number Rev

A <Doc> V1.0

Date: Friday, July 01, 2016 Sheet 2 of 15

5 4 3 2 1

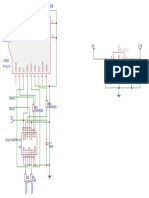

5 4 3 2 1

BANK 500 D

V3P3 R25 4.7K

Y1 U1B

4 1

VCC ENA/DSI

C9

2 3 R26 33 PS_CLK_33M33 E7 E6

GND OUT PS_CLK_500 PS_MIO0_500 PS_MIO0_NAND_CS# 10

A7 PS_MIO1_NAND_WP# 10

33..330MHz C7 PS_MIO1_500 B8

12,15 P_GOOD PS_POR_B_500 PS_MIO2_500 PS_MIO2_NAND_ALE 1,10

D6 PS_MIO3_NAND_WE# 1,10

PS_MIO3_500

0.1uF

B7

PS_MIO4_500 PS_MIO4_NAND_DQ2 1,10

A6

PS_MIO5_500 PS_MIO5_NAND_DQ0 1,10

A5

PS_MIO6_500 PS_MIO6_NAND_DQ1 10

D8 PS_MIO7_NAND_CLE 10

PS_MIO7_500 D5

V3P3 PS_MIO8_500 PS_MIO8_NAND_RE# 10

C B5 C

PS_MIO9_500 PS_MIO9_NAND_DQ4 10

E9

PS_MIO10_500 PS_MIO10_NAND_DQ5 10

C6

PS_MIO11_500 PS_MIO11_NAND_DQ6 10

D9

PS_MIO12_500 PS_MIO12_NAND_DQ7 10

E8

PS_MIO13_500 PS_MIO13_NAND_DQ3 10

C10

C11

C12

C13

B6 C5

VCCO_MIO0_500_1 PS_MIO14_500 PS_MIO14_NAND_R/B# 10

D7 C8

VCCO_MIO0_500_2 PS_MIO15_500

V3P3

100uF

10uF

0.1uF

0.1uF

D2

PS_MIO15_LED R27 220

xc7z010clg400_10

G/25mA/0603

V3P3

B PS_MIO0_NAND_CS# R187 B

1K

PLL ENABLED PS_MIO6_NAND_DQ1 R28 20K PS_MIO1_NAND_WP# R188 1K

BANK500:3.3V PS_MIO7_NAND_CLE R29 20K PS_MIO14_NAND_R/B#R189 1K

BANK501:2.5V PS_MIO8_NAND_RE# R30 20K

PS_MIO0_NAND_CS# R175 20K

During an SD memory card boot sequence, the BootROM

reads the logic level on the MIO pin 0 as an SD Card

Detect. MIO pin 0 must be Low during the SDIO boot

process.

A A

Title

AntMiner_ControlBoard_XC7010

Size Document Number Rev

A <Doc> V1.0

Date: Friday, July 01, 2016 Sheet 3 of 15

5 4 3 2 1

5 4 3 2 1

U1C

A19 D14 R31 33 PS_MIO40_CD_CLK 11

12 ETH_TX_CLK E14 PS_MIO16_501 PS_MIO40_501 C17

12 ETH_TXD0 PS_MIO17_501 PS_MIO41_501 PS_MIO41_CD_CMD 11

B18 E12

12 ETH_TXD1 PS_MIO18_501 PS_MIO42_501 PS_MIO42_CD_D0 11

D10 A9

12 ETH_TXD2 PS_MIO19_501 PS_MIO43_501 PS_MIO43_CD_D1 11

A17 F13

12 ETH_TXD3 PS_MIO20_501 PS_MIO44_501 PS_MIO44_CD_D2 11

F14 B15

D 12 ETH_TX_CTRL PS_MIO21_501 PS_MIO45_501 PS_MIO45_CD_D3 11 D

12 ETH_RX_CLK B17

D11 PS_MIO22_501

12 ETH_RX0 PS_MIO23_501

12 ETH_RX1 A16

F15 PS_MIO24_501

12 ETH_RX2 PS_MIO25_501

12 ETH_RX3 A15 A14 PS_MIO32_EN5 13

D13 PS_MIO26_501 PS_MIO32_501 D15

12 ETH_RX_CTRL PS_MIO27_501 PS_MIO33_501 PS_MIO33_EN6 13

A12 PS_MIO34_EN7 13

PS_MIO34_501 F12

PS_MIO35_501 PS_MIO35_EN8 13

C16 PS_MIO28_EN1 13

PS_MIO28_501

BANK 501

A10 PS_MIO37_LED_R

PS_MIO37_501 E13 PS_MIO38_LED_G

PS_MIO38_501 C18 PS_MIO39_BEEP

PS_MIO39_501

C13 PS_MIO29_EN2 13

PS_MIO29_501 C15

PS_MIO30_501 PS_MIO30_EN3 13

E16 PS_MIO31_EN4 13

PS_MIO31_501 A11

C

PS_MIO36_501 PS_MIO36_EN9 13 C

2 PS_SRST# B10

V2P5 E11 PS_SRST_B_501

PS_MIO_VREF_501

R32 1K R33 1K

D16

PS_MIO46_501 PS_MIO46_CD_SW 11

B14

PS_MIO47_501 PS_MIO47_KEY_RESET 2

B12 MIO48_UART_TXD 11

A13 PS_MIO48_501 C12

VCCO_MIO1_501_1 PS_MIO49_501 MIO49_UART_RXD 11

V2P5 B16 B13

VCCO_MIO1_501_2 PS_MIO50_501 PS_MIO51_IP_GET PS_MIO50_CD_WP 11

D12 B9

E15 VCCO_MIO1_501_3 PS_MIO51_501 C10

VCCO_MIO1_501_4 PS_MIO52_501 ETH_MDC 12

C11

PS_MIO53_501 ETH_MDIO 12

C15

C16

C17

C18

C19

C14

V3P3

D3

100uF

10uF

0.1uF

0.1uF

0.1uF

0.1uF

B xc7z010clg400_10 B

R34 220 4 3

D Q3 R35 220 2 1

PS_MIO37_LED_R G 2N7002-7-F

V3P3 V2P5 S SOT23_3 F5G1

D Q2

R36 4.7K S2 PS_MIO38_LED_G G 2N7002-7-F

BZ1 KMR231GLFS

D4

C20

1 PS_MIO51_IP_GET 1 2 S SOT23_3

1N4148

2

0.1uF

3 4

Bell

PS_MIO39_BEEP R39 1K Q1

A MMBT3904 A

V2P5

Title

AntMiner_ControlBoard_XC7010

ETH_MDC R37 1K

ETH_MDIO R38 1K Size Document Number Rev

A <Doc> V1.0

Date: Friday, July 01, 2016 Sheet 4 of 15

5 4 3 2 1

5 4 3 2 1

U1D

N2 C3

9 DDR3_A0 PS_DDR_A0_502 PS_DDR_DQ0_502 DDR3_DQ0 9

K2 B3

9 DDR3_A1 PS_DDR_A1_502 PS_DDR_DQ1_502 DDR3_DQ1 9

M3 A2

9 DDR3_A2 PS_DDR_A2_502 PS_DDR_DQ2_502 DDR3_DQ2 9

K3 A4

9 DDR3_A3 PS_DDR_A3_502 PS_DDR_DQ3_502 DDR3_DQ3 9

M4 D3

9 DDR3_A4 PS_DDR_A4_502 PS_DDR_DQ4_502 DDR3_DQ4 9

L1 D1

D 9 DDR3_A5 PS_DDR_A5_502 PS_DDR_DQ5_502 DDR3_DQ5 9 D

L4 C1

9 DDR3_A6 PS_DDR_A6_502 PS_DDR_DQ6_502 DDR3_DQ6 9

K4 E1

9 DDR3_A7 PS_DDR_A7_502 PS_DDR_DQ7_502 DDR3_DQ7 9

K1 E2

9 DDR3_A8 PS_DDR_A8_502 PS_DDR_DQ8_502 DDR3_DQ8 9

J4 E3

9 DDR3_A9 PS_DDR_A9_502 PS_DDR_DQ9_502 DDR3_DQ9 9

F5 G3

9 DDR3_A10 PS_DDR_A10_502 PS_DDR_DQ10_502 DDR3_DQ10 9

G4 H3

9 DDR3_A11 PS_DDR_A11_502 PS_DDR_DQ11_502 DDR3_DQ11 9

E4 J3

9 DDR3_A12 PS_DDR_A12_502 PS_DDR_DQ12_502 DDR3_DQ12 9

D4 H2

9 DDR3_A13 PS_DDR_A13_502 PS_DDR_DQ13_502 DDR3_DQ13 9

F4 H1

9 DDR3_A14 PS_DDR_A14_502 PS_DDR_DQ14_502 DDR3_DQ14 9

J1

PS_DDR_DQ15_502 DDR3_DQ15 9

P1

PS_DDR_DQ16_502 DDR3_DQ16 9

L5 P3

9 DDR3_BA0 PS_DDR_BA0_502 PS_DDR_DQ17_502 DDR3_DQ17 9

R4 R3

9 DDR3_BA1 PS_DDR_BA1_502 PS_DDR_DQ18_502 DDR3_DQ18 9

J5 R1

9 DDR3_BA2 PS_DDR_BA2_502 PS_DDR_DQ19_502 DDR3_DQ19 9

T4

PS_DDR_DQ20_502 DDR3_DQ20 9

U4

PS_DDR_DQ21_502 DDR3_DQ21 9

U2

PS_DDR_DQ22_502 DDR3_DQ22 9

C P5 U3 C

9 DDR3_CAS# PS_DDR_CAS_B_502 PS_DDR_DQ23_502 DDR3_DQ23 9

P4 V1

9 DDR3_RAS# PS_DDR_RAS_B_502 PS_DDR_DQ24_502 DDR3_DQ24 9

M5 Y3

9 DDR3_WE# PS_DDR_WE_B_502 PS_DDR_DQ25_502 DDR3_DQ25 9

N1 W1

9 DDR3_CS# PS_DDR_CS_B_502 PS_DDR_DQ26_502 DDR3_DQ26 9

Y4

PS_DDR_DQ27_502 DDR3_DQ27 9

Y2

PS_DDR_DQ28_502 DDR3_DQ28 9

R40 80.6 W3

PS_DDR_DQ29_502 DDR3_DQ29 9

L2 V2

9 DDR3_CLK_P PS_DDR_CKP_502 PS_DDR_DQ30_502 DDR3_DQ30 9

M2 V3

9 DDR3_CLK_N PS_DDR_CKN_502 PS_DDR_DQ31_502 DDR3_DQ31 9

N3

9 DDR3_CKE N5 PS_DDR_CKE_502

9 DDR3_ODT PS_DDR_ODT_502

R41 80.6 H5 C2

PS_DDR_VRP_502 PS_DDR_DQS_P0_502 DDR3_DQS0_P 9

V1P5 R42 80.6 G5 B2

PS_DDR_VRN_502 PS_DDR_DQS_N0_502 DDR3_DQS0_N 9

G2

PS_DDR_DQS_P1_502 DDR3_DQS1_P 9

VREF_DDR3 F2

PS_DDR_DQS_N1_502 DDR3_DQS1_N 9

P6 R2

PS_DDR_VREF1_502 PS_DDR_DQS_P2_502 DDR3_DQS2_P 9

H6 T2

B PS_DDR_VREF0_502 PS_DDR_DQS_N2_502 DDR3_DQS2_N 9 B

W5

PS_DDR_DQS_P3_502 DDR3_DQS3_P 9

C21

C22

W4

PS_DDR_DQS_N3_502 DDR3_DQS3_N 9

V4

U1 VCCO_DDR_502_1

VCCO_DDR_502_2

0.1uF

0.1uF

R5 A1 DDR3_DM0 9

P2 VCCO_DDR_502_3 PS_DDR_DM0_502 F1

VCCO_DDR_502_4 PS_DDR_DM1_502 DDR3_DM1 9

L3 T1 DDR3_DM2 9

H4 VCCO_DDR_502_5 PS_DDR_DM2_502 Y1

VCCO_DDR_502_6 PS_DDR_DM3_502 DDR3_DM3 9

G1

V1P5 E5 VCCO_DDR_502_7 B4

VCCO_DDR_502_8 PS_DDR_DRST_B_502 DDR3_RESET# 9

D2

V1P5 A3 VCCO_DDR_502_9

VCCO_DDR_502_A

C25

C26

C27

C28

C29

C30

C31

C32

C33

xc7z010clg400_10

BANK 502

C23

C24

A A

Title

10uF

10uF

10uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

100uF

100uF

AntMiner_ControlBoard_XC7010

Size Document Number Rev

A <Doc> V1.0

Date: Friday, July 01, 2016 Sheet 5 of 15

5 4 3 2 1

5 4 3 2 1

U1E

PL BANK34 、35 U1F

13 BANK34_0_PLUG2 R19 G14

T11 IO_0_34 C20 IO_0_35

13 BANK34_L1P_PLUG1 IO_L1P_T0_34 IO_L1P_T0_AD0P_35

T10 B20

13 BANK34_L1N_RST1 T12 IO_L1N_T0_34 B19 IO_L1N_T0_AD0N_35

13 BANK34_L2P_TXD1 U12 IO_L2P_T0_34 A20 IO_L2P_T0_AD8P_35

13 BANK34_L2N_RXD1 IO_L2N_T0_34 IO_L2N_T0_AD8N_35

D PUDC_B U13 E17 D

V13 IO_L3P_T0_DQS_PUDC_B_34 D18 IO_L3P_T0_DQS_AD1P_35

13 BANK34_L3N_RST2 V12 IO_L3N_T0_DQS_34 D19 IO_L3N_T0_DQS_AD1N_35

13 BANK34_L4P_TXD2 W13 IO_L4P_T0_34 V3P3 D20 IO_L4P_T0_35

13 BANK34_L4N_RXD2 IO_L4N_T0_34 IO_L4N_T0_35

T14 E18

13 BANK34_L5P_PLUG3 IO_L5P_T0_34 IO_L5P_T0_AD9P_35

T15 E19

13 BANK34_L5N_RST3 P14 IO_L5N_T0_34 R178 220 G/25mA/0603 D7 BANK35_L6P_LED F16 IO_L5N_T0_AD9N_35

13 BANK34_L6P_TXD3 R14 IO_L6P_T0_34 F17 IO_L6P_T0_35

13 BANK34_L6N_RXD3 IO_L6N_T0_VREF_34 IO_L6N_T0_VREF_35

Y16 R179 220 G/25mA/0603 D5 BANK35_L7P_LED M19

13 BANK34_L7P_PLUG4 IO_L7P_T1_34 IO_L7P_T1_AD2P_35

Y17 M20

13 BANK34_L7N_RST4 W14 IO_L7N_T1_34 R180 220 G/25mA/0603 D6 BANK35_L8P_LED M17 IO_L7N_T1_AD2N_35

13 BANK34_L8P_TXD4 Y14 IO_L8P_T1_34 M18 IO_L8P_T1_AD10P_35

13 BANK34_L8N_RXD4 IO_L8N_T1_34 IO_L8N_T1_AD10N_35

T16 R181 220 G/25mA/0603 D8 BANK35_L9P_LED L19

13 BANK34_L9P_PLUG5 IO_L9P_T1_DQS_34 IO_L9P_T1_DQS_AD3P_35

U17 L20

13 BANK34_L9N_RST5 V15 IO_L9N_T1_DQS_34 K19 IO_L9N_T1_DQS_AD3N_35

13 BANK34_L10P_TXD5 W15 IO_L10P_T1_34 J19 IO_L10P_T1_AD11P_35

13 BANK34_L10N_RXD5 IO_L10N_T1_34 IO_L10N_T1_AD11N_35

U14 L16

13 BANK34_L11P_PLUG6 IO_L11P_T1_SRCC_34 IO_L11P_T1_SRCC_35

U15 L17

13 BANK34_L11N_RST6 U18 IO_L11N_T1_SRCC_34 BANK35_L12P_MRCC_100M K17 IO_L11N_T1_SRCC_35

13 BANK34_L12P_TXD6 U19 IO_L12P_T1_MRCC_34 TP1 CLOCK_OUT K18 IO_L12P_T1_MRCC_35

13 BANK34_L12N_RXD6 IO_L12N_T1_MRCC_34 IO_L12N_T1_MRCC_35

N18 H16

BANK34_L13P_MRCC_100M P19 IO_L13P_T2_MRCC_34 H17 IO_L13P_T2_MRCC_35

N20 IO_L13N_T2_MRCC_34 J18 IO_L13N_T2_MRCC_35

P20 IO_L14P_T2_SRCC_34 14 BANK35_L14P_FAN_PWM H18 IO_L14P_T2_AD4P_SRCC_35

C

T20 IO_L14N_T2_SRCC_34 F19 IO_L14N_T2_AD4N_SRCC_35 C

13 BANK34_L15P_PLUG7 IO_L15P_T2_DQS_34 14 BANK35_L15P_FAN_SPEED1 IO_L15P_T2_DQS_AD12P_35

U20 14 BANK35_L15N_FAN_SPEED2 F20

13 BANK34_L15N_RST7 V20 IO_L15N_T2_DQS_34 G17 IO_L15N_T2_DQS_AD12N_35

13 BANK34_L16P_TXD7 IO_L16P_T2_34 14 BANK35_L16P_FAN_SPEED3 IO_L16P_T2_35

W20 G18

13 BANK34_L16N_RXD7 IO_L16N_T2_34 14 BANK35_L16N_FAN_SPEED4 IO_L16N_T2_35

13 BANK34_L17P_PLUG8 Y18 14 BANK35_L17P_FAN_SPEED5 J20

Y19 IO_L17P_T2_34 H20 130IO_L17P_T2_AD5P_35

13 BANK34_L17N_RST8 IO_L17N_T2_34 14 BANK35_L17N_FAN_SPEED6 IO_L17N_T2_AD5N_35

V16 G19

13 BANK34_L18P_TXD8 W16 IO_L18P_T2_34 G20 IO_L18P_T2_AD13P_35

13 BANK34_L18N_RXD8 IO_L18N_T2_34 IO_L18N_T2_AD13N_35

R16 H15

13 BANK34_L19P_PLUG9 IO_L19P_T3_34 IO_L19P_T3_35

R17 G15

13 BANK34_L19N_RST9 T17 IO_L19N_T3_VREF_34 K14 IO_L19N_T3_VREF_35

13 BANK34_L20P_TXD9 IO_L20P_T3_34 IO_L20P_T3_AD6P_35

R18 J14

13 BANK34_L20N_RXD9 V17 IO_L20N_T3_34 V3P3 N15 IO_L20N_T3_AD6N_35

V18 IO_L21P_T3_DQS_34 N16 IO_L21P_T3_DQS_AD14P_35

W18 IO_L21N_T3_DQS_34 R183 4.7K Baord_ID3 L14 IO_L21N_T3_DQS_AD14N_35

13 BANK34_L22P_SCL1 W19 IO_L22P_T3_34 R184 4.7K Baord_ID2 L15 IO_L22P_T3_AD7P_35

13 BANK34_L22N_SDA1 IO_L22N_T3_34 IO_L22N_T3_AD7N_35

N17 R185 4.7K Baord_ID1 M14

13 BANK34_L23P_SCL2 P18 IO_L23P_T3_34 R186 4.7K Baord_ID0 M15 IO_L23P_T3_35

13 BANK34_L23N_SDA2 IO_L23N_T3_34 IO_L23N_T3_35

P15 K16

P16 IO_L24P_T3_34 J16 IO_L24P_T3_AD15P_35

T19 IO_L24N_T3_34 J15 IO_L24N_T3_AD15N_35

IO_25_34 IO_25_35

V3P3

B B

V3P3 C19

F18 VCCO_35_1

N19 H14 VCCO_35_2

VCCO_34_1 VCCO_35_3

C34

C35

C36

C37

C38

C39

C40

C41

C42

R15 J17

T18 VCCO_34_2 K20 VCCO_35_4

VCCO_34_3 VCCO_35_5

C43

C44

C45

C46

C47

C48

C49

C50

C51

V14 M16

W17 VCCO_34_4 VCCO_35_6

VCCO_34_5

100uF

10uF

10uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

Y20

VCCO_34_6

xc7z010clg400_10

100uF

10uF

10uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

xc7z010clg400_10

V3P3 R47 4.7K NC

V3P3 R48 4.7K NC Y2

V3P3 4 1

Y3 2 VCC ENA/DSI 3 R49 33 NC BANK35_L12P_MRCC_100M

GND OUT

C52

4 1

BANK34_L22P_SCL1 R50 1K 2 VCC ENA/DSI 3 R51 33 NCBANK34_L13P_MRCC_100M 100MHz NC

GND OUT

C53

A BANK34_L22N_SDA1 R52 1K A

0.1uF NC

BANK34_L23P_SCL2 R53 1K 100MHz NC

BANK34_L23N_SDA2 R54 1K

0.1uF NC

PUDC_B R190 1K

R191 1K NC

Title

AntMiner_ControlBoard_XC7010

Size Document Number Rev

B <Doc> V1.0

Date: Friday, July 01, 2016 Sheet 6 of 15

5 4 3 2 1

5 4 3 2 1

V1P0 U1G V1P8

G13 J11

H12 VCCINT_1 VCCAUX_1 L11

J13 VCCINT_2 VCCAUX_2 N9

K12 VCCINT_3 VCCAUX_3 P10

D

L13 VCCINT_4 VCCAUX_4 R9 D

M12 VCCINT_5 VCCAUX_5 N11 V1P8

N13 VCCINT_6 VCCAUX_6

P12 VCCINT_7 G9

R13 VCCINT_8 VCCPAUX_1 F8

V1P0 VCCINT_9 VCCPAUX_2 H8

VCCPAUX_3 K8

G7 VCCPAUX_4 M8 V1P0

J7 VCCPINT_1 VCCPAUX_5

L7 VCCPINT_2 G11 V1P8

N7 VCCPINT_3 VCCBRAM_1 H10

P8 VCCPINT_4 VCCBRAM_2 G8 FB3

R7 VCCPINT_5 VCCPLL 100R/3A

VCCPINT_6

C54

C55

Y10 V3P3

VCCO_13_1 W7

VCCO_13_2 U11

VCCO_13_3 T8

VCCO_13_4

0.47uF

10uF

C C

xc7z010clg400_10

V1P0 V1P8

C56

C57

C58

C59

C60

C61

C62

C63

C64

C65

C66

C67

C68

C69

C70

C71

C72

C73

C74

C75

C76

C77

C78

100uF

100uF

100uF

10uF

10uF

10uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

100uF

10uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

B B

V1P0 V1P0 V1P8

C79

C80

C81

C82

C83

C84

C85

C86

C87

C88

C89

C90

C91

C92

C93

C94

C95

C96

C97

C98

100uF

10uF

10uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

100uF

10uF

0.1uF

0.1uF

100uF

10uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

A A

Title

AntMiner_ControlBoard_XC7010

Size Document Number Rev

A <Doc> V1.0

Date: Friday, July 01, 2016 Sheet 7 of 15

5 4 3 2 1

5 4 3 2 1

D D

U1H

A8 L18 U1I

A18 GND_01 GND_31 M1

B1 GND_02 GND_32 M7 V5 W9

B11 GND_03 GND_33 M11 U7 NC_01 NC_13 U9

C4 GND_04 GND_34 M13 V7 NC_02 NC_14 U8

C14 GND_05 GND_35 N4 T9 NC_03 NC_15 W11

K11 GND_06 GND_36 N8 U10 NC_04 NC_16 Y11

D17 GND_07 GND_37 N10 Y7 NC_05 NC_17 T5

E10 GND_08 GND_38 N12 Y6 NC_06 NC_18 U5

E20 GND_09 GND_39 N14 Y9 NC_07 NC_19 Y12

F3 GND_10 GND_40 P7 Y8 NC_08 NC_20 Y13

F7 GND_11 GND_41 P9 V8 NC_09 NC_21 V11

G10 GND_12 GND_42 P11 W8 NC_10 NC_22 V10

G12 GND_13 GND_43 P13 W10 NC_11 NC_23 V6

G16 GND_14 GND_44 P17 NC_12 NC_24 W6

C C

H7 GND_15 GND_45 R8 NC_25

H9 GND_16 GND_46 R12

H11 GND_17 GND_47 R20

GND_18 GND_48 xc7z010clg400_10

H13 T3

H19 GND_19 GND_49 T7

J2 GND_20 GND_50 T13

J8 GND_21 GND_51 U6

J12 GND_22 GND_52 U16

K5 GND_23 GND_53 V9

K7 GND_24 GND_54 V19

C9 GND_25 GND_55 W2

K13 GND_26 GND_56 W12

K15 GND_27 GND_57 Y5

L8 GND_28 GND_58 Y15

L12 GND_29 GND_59

GND_30

B B

xc7z010clg400_10

A A

Title

AntMiner_ControlBoard_XC7010

Size Document Number Rev

A <Doc> V1.0

Date: Friday, July 01, 2016 Sheet 8 of 15

5 4 3 2 1

5 4 3 2 1

U3

MT41K256M16HA-125:E U4

Manufacturer = Micron MT41K256M16HA-125:E

PART_NUMBER = Y091K2560000 Manufacturer = Micron

N3 DDR3 Device PART_NUMBER = Y091K2560000

5 DDR3_A0 A0

P7 E3 DDR3_A0 N3 DDR3 Device

5 DDR3_A1 A1 DQ0 F7 DDR3_DQ0 5 A0

P3 DDR3_A1 P7 E3

5 DDR3_A2 A2 DQ1 F2 DDR3_DQ5 5 A1 DQ0 F7 DDR3_DQ18 5

N2 DDR3_A2 P3

5 DDR3_A3 A3 DQ2 F8 DDR3_DQ2 5 A2 DQ1 F2 DDR3_DQ22 5

P8 DDR3_A3 N2

5 DDR3_A4 A4 DQ3 H3 DDR3_DQ4 5 A3 DQ2 F8 DDR3_DQ19 5

P2 DDR3_A4 P8

5 DDR3_A5 A5 DQ4 H8 DDR3_DQ3 5 A4 DQ3 H3 DDR3_DQ23 5

D R8 DDR3_A5 P2 D

5 DDR3_A6 A6 DQ5 G2 DDR3_DQ7 5 A5 DQ4 H8 DDR3_DQ17 5

R2 DDR3_A6 R8

5 DDR3_A7 A7 DQ6 H7 DDR3_DQ1 5 A6 DQ5 G2 DDR3_DQ21 5

T8 DDR3_A7 R2

5 DDR3_A8 A8 DQ7 D7 DDR3_DQ6 5 A7 DQ6 H7 DDR3_DQ16 5

R3 DDR3_A8 T8

5 DDR3_A9 A9 DQ8 C3 DDR3_DQ14 5 A8 DQ7 D7 DDR3_DQ20 5

L7 DDR3_A9 R3

5 DDR3_A10 A10/AP DQ9 C8 DDR3_DQ8 5 A9 DQ8 C3 DDR3_DQ28 5

R7 DDR3_A10 L7

5 DDR3_A11 A11 DQ10 C2 DDR3_DQ12 5 A10/AP DQ9 C8 DDR3_DQ30 5

N7 DDR3_A11 R7

5 DDR3_A12 A12/BCn DQ11 A7 DDR3_DQ9 5 A11 DQ10 C2 DDR3_DQ27 5

T3 DDR3_A12 N7

5 DDR3_A13 A13 DQ12 A2 DDR3_DQ13 5 A12/BCn DQ11 A7 DDR3_DQ31 5

T7 DDR3_A13 T3

5 DDR3_A14 A14 DQ13 B8 DDR3_DQ10 5 A13 DQ12 A2 DDR3_DQ25 5

DDR3_A14 T7

DQ14 A3 DDR3_DQ15 5 A14 DQ13 B8 DDR3_DQ24 5

5 DDR3_CKE K9

J7 CKE DQ15 DDR3_DQ11 5 DDR3_CKE K9 DQ14 A3 DDR3_DQ29 5

5 DDR3_CLK_P CK_P CKE DQ15 DDR3_DQ26 5

K7 F3 DDR3_CLK_P J7

5 DDR3_CLK_N CK_N LDQS_P G3 DDR3_DQS0_P 5 CK_P

DDR3_CLK_N K7 F3

E7 LDQS_N C7 DDR3_DQS0_N 5 CK_N LDQS_P G3 DDR3_DQS2_P 5

5 DDR3_DM0 LDM UDQS_P B7 DDR3_DQS1_P 5 LDQS_N C7 DDR3_DQS2_N 5

5 DDR3_DM1 D3 5 DDR3_DM2 E7

UDM UDQS_N DDR3_DQS1_N 5 D3 LDM UDQS_P B7 DDR3_DQS3_P 5

5 DDR3_DM3 UDM UDQS_N DDR3_DQS3_N 5

L2

5 DDR3_CS# CS

L3 J1 DDR3_CS# L2

5 DDR3_WE# WE NC1 CS

J3 J9 DDR3_WE# L3 J1

5 DDR3_RAS# RAS NC2 WE NC1

K3 L1 DDR3_RAS# J3 J9

5 DDR3_CAS# CAS NC3 RAS NC2

L9 DDR3_CAS# K3 L1

M2 NC4 M7 CAS NC3 L9

5 DDR3_BA0 BA0 NC5 NC4

N8 DDR3_BA0 M2 M7

C 5 DDR3_BA1 BA1 BA0 NC5 C

M3 DDR3_BA1 N8

5 DDR3_BA2 BA2 BA1

T2 DDR3_BA2 M3

5 DDR3_RESET# RESETn BA2

K1 DDR3_RESET# T2

5 DDR3_ODT ODT RESETn

L8 DDR3_ODT K1

ZQ B1 L8 ODT

VREF_DDR3 H1 VSSQ B9 ZQ B1

VREFDQ VSSQ VSSQ

R55

M8 D1 VREF_DDR3 H1 B9

VREFCA VSSQ VREFDQ VSSQ

R56

D8 M8 D1

B2 VSSQ E2 VREFCA VSSQ D8

D9 VDD VSSQ E8 B2 VSSQ E2

240 G7 VDD VSSQ F9 D9 VDD VSSQ E8

K2 VDD VSSQ G1 240 G7 VDD VSSQ F9

K8 VDD VSSQ G9 VREF_DDR3 K2 VDD VSSQ G1

N1 VDD VSSQ K8 VDD VSSQ G9

N9 VDD J2 N1 VDD VSSQ

R1 VDD VSS J8 N9 VDD J2

VDD VSS VDD VSS

C100

C101

C102

C103

R9 A9 R1 J8

VDD VSS M1 R9 VDD VSS A9

A1 VSS M9 VDD VSS M1

A8 VDDQ VSS B3 A1 VSS M9

VDDQ VSS VDDQ VSS

0.1uF

0.1uF

0.1uF

0.1uF

C1 P1 A8 B3

C9 VDDQ VSS P9 C1 VDDQ VSS P1

D2 VDDQ VSS E1 C9 VDDQ VSS P9

V1P5 E9 VDDQ VSS T1 D2 VDDQ VSS E1

B B

F1 VDDQ VSS T9 V1P5 E9 VDDQ VSS T1

H2 VDDQ VSS G8 F1 VDDQ VSS T9

H9 VDDQ VSS H2 VDDQ VSS G8

VDDQ H9 VDDQ VSS

VDDQ

VTT_DDR3

V1P5

DDR3_RESET# R57 40.2 NC

R58 4.7K

VTT_DDR3

C104

C105

C106

C107

C108

C109

C110

C111

C112

C113

C114

C115

C116

C117

C118

C119

C120

C121

C122

C123

VTT_DDR3 DDR3_CKE R59 40.2

DDR3_CS# R60 40.2

DDR3_A0 R61 40.2 DDR3_WE# R62 40.2

100uF

10uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

DDR3_A1 R63 40.2 DDR3_RAS# R64 40.2

DDR3_A2 R65 40.2 DDR3_CAS# R66 40.2

DDR3_A3 R67 40.2 DDR3_BA0 R68 40.2

V1P5 DDR3_A4 R69 40.2 DDR3_BA1 R70 40.2

DDR3_A5 R71 40.2 DDR3_BA2 R72 40.2

DDR3_A6 R73 40.2 DDR3_ODT R74 40.2

A DDR3_A7 R75 40.2 A

DDR3_A8 R76 40.2

C124

C125

C126

C127

C128

C129

C130

C131

C132

C133

C134

C135

C136

C137

C138

C139

C140

C141

C142

C143

DDR3_A9 R77 40.2

DDR3_A10 R78 40.2

DDR3_A11 R79 40.2

DDR3_A12 R80 40.2 Title

100uF

10uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

DDR3_A13 R81 40.2 AntMiner_ControlBoard_XC7010

DDR3_A14 R82 40.2

Size Document Number Rev

B <Doc> V1.0

Date: Friday, July 01, 2016 Sheet 9 of 15

5 4 3 2 1

5 4 3 2 1

NAND FLASH D

U5

1 44 PS_MIO12_NAND_DQ7 3

2 NC1 I/O7 43

NC2 I/O6 PS_MIO11_NAND_DQ6 3

3 42 PS_MIO10_NAND_DQ5 3

4 NC3 I/O5 41

NC4 I/O4 PS_MIO9_NAND_DQ4 3

5 32 PS_MIO13_NAND_DQ3 3

6 NC5 I/O3 31

R/B2#/NC I/O2 PS_MIO4_NAND_DQ2 1,3

10 30 PS_MIO6_NAND_DQ1 3

11 CE2#/NC I/O1 29

NC6 I/O0 PS_MIO5_NAND_DQ0 1,3

V3P3 14

15 NC7

20 NC8

C C

21 NC9

22 NC10

NC11

C144

C145

C146

C147

C148

C149

23 7 PS_MIO14_NAND_R/B# 3

24 NC12 R/B# 17

NC13 ALE PS_MIO2_NAND_ALE 1,3

27 16

NC14 CLE PS_MIO7_NAND_CLE 3

28 18

NC15 WE# PS_MIO3_NAND_WE# 1,3

10uF

1uF

0.1uF

0.1uF

0.1uF

0.1uF

33 19

NC16 WP# PS_MIO1_NAND_WP# 3

35

40 NC17 8

NC18 RE# PS_MIO8_NAND_RE# 3

45 9

NC19 CE# PS_MIO0_NAND_CS# 3

46

47 NC20

NC21 38

NC27 26

V3P3 NC23

12 36

B

37 VCC1 VSS2 13 B

34 VCC2 VSS1 25

39 NC24 NC22 48

NC25 NC26

MT29F2G08AACWP

A A

Title

AntMiner_ControlBoard_XC7010

Size Document Number Rev

A <Doc> V1.0

Date: Friday, July 01, 2016 Sheet 10 of 15

5 4 3 2 1

5 4 3 2 1

V2P5 V3P3 Micro SD Card

C150 10uF C151 10uF

D D

C152 0.1uF C153 0.1uF

U6

21

17

5

J11

VCC_A

VCC_B0

VCC_B1

19 SDIO_CLK 5 6

CLK_B0 20 SDIO_CMD 3 CLOCK VSS 9

6 CMD_B0 18 SDIO_D0 7 CMD GND 11

4 PS_MIO42_CD_D0 DAT0_A DAT0_B0 DAT0 GND3

7 16 SDIO_D1 8 12

4 PS_MIO43_CD_D1 DAT1_A DAT1_B0 DAT1 GND4

1 22 SDIO_D3 2 13

microSD

4 PS_MIO44_CD_D2 DAT2_A DAT3_B0 CD/DAT3 GND5

3 23 SDIO_D2 1 14

4 PS_MIO45_CD_D3 DAT3_A DAT2_B0 DAT2 GND6

V3P3 4 15

4 10 VDD GND7 16

4 PS_MIO41_CD_CMD CMD_A CD GND8

C154

4 PS_MIO40_CD_CLK 9

CLK_A

C155 0.1uF

C 13 V2P5 SCHA5B0200 C

CLK_B1 12

R83 4.7K 24 CMD_B1 14

SEL_B0# DAT0_B1

10uF

R176

15 R85 0

DAT1_B1 8 R86 0

DAT2_B1 10

DAT3_B1

T-PAD

GND1

GND2

V2P5

4.7K

TXS02612RTWR

25 4 PS_MIO46_CD_SW

11

2

4 PS_MIO50_CD_WP R177 4.7K

R84

UART

0 NC

B B

V2P5

V3P3

U7 MIO49_UART_RXD R88 1K

4 5 MIO49_UART_RXD_V3P3 MIO48_UART_TXD R89 1K

MIO49_UART_RXD 3 A2 B2 6 MIO48_UART_TXD_V3P3 V3P3 MIO49_UART_RXD_V3P3 R90 1K

MIO48_UART_TXD A1 B1

2 7 MIO48_UART_TXD_V3P3 R91 1K

1 Vref_A Vref_B 8 R87 200K

V2P5 GND EN

LSF0102DCTR C156 0.1uF

C157 0.1uF J12

RXD 1 MIO49_UART_RXD_V3P3

2

A TXD 3 MIO48_UART_TXD_V3P3 A

Title

HEADER_3 AntMiner_ControlBoard_XC7010

DEPOP

Size Document Number Rev

A <Doc> V1.0

Date: Friday, July 01, 2016 Sheet 11 of 15

5 4 3 2 1

5 4 3 2 1

V2P5

C160 0.1uF

C158 0.1uF

C159 0.1uF

D U8 G2405CG T1 D

29

34

J13

1

1 24

40 14 2 TCT3 MCT3 23 PX_1 1 9 R92 4.7K

OVDD

OVDD_RGMII_1

OVDD_RGMII_2

4 ETH_TX_CLK GTXCLK TRD[0]+ TD3+ MX3+ TX0+ LED1-

35 15 3 22 PX_2 2 10 R93 220 ACT_LED

4 ETH_TX_CTRL TX_EN TRD[0]- TD3- MX3- TX0- LED1+

4 21

39 18 5 TCT2 MCT2 20 PX_3 3

4 ETH_TXD0 TXD[0] TRD[1]+ TD2+ MX2+ RX0+

38 17 6 19 PX_6 6 11 R94 220 LNK_LED

4 ETH_TXD1 TXD[1] TRD[1]- TD2- MX2- RX0- LED2-

37 7 18 12

4 ETH_TXD2 TXD[2] TCT1 MCT1 LED2+ V2P5

36 20 8 17 PX_4 4

4 ETH_TXD3 TXD[3] TRD[2]+ TD1+ MX1+ TX1+

21 9 16 PX_5 5

TRD[2]- 10 TD1- MX1- 15 TX1-

24 11 TCT0 MCT0 14 PX_7 7 13

TRD[3]+ 23 12 TD0+ MX0+ 13 PX_8 8 RX1+ SHELD1 14

TRD[3]- TD0- MX0- RX1- SHELD2

C161 0.1uF

C162 0.1uF

C163 0.1uF

C164 0.1uF

RJ45

R95

R96

R97

R98

33

4 ETH_RX_CLK 26 RXC

4 ETH_RX_CTRL RX_DV

45 75 75 75 75

R99 33 32 LED1 44 LNK_LED V3P3

4 ETH_RX0 R100 33 31 RXD[0] LED2 43 ACT_LED R101 0

4 ETH_RX1 R102 33 28 RXD[1] LED3 42 LED4 C166 10uF C167 1000PF R103 0

C 4 ETH_RX2 R104 33 27 RXD[2] LED4 R105 0

C

4 ETH_RX3 RXD[3] C165 0.1uF R106 0

4

REGSUPPLY

48 REG_V1P2

4 ETH_MDC MDC

C168

C169

C170

4 ETH_MDIO 47

MDIO 3

8 REGOUT

XTALI

0.1uF

0.1uF

10uF

2

Y4 DVDD_1 30

1 3 7 DVDD_2

2 X1 X2 4 XTALO FB4

NC1 NC2

C173

C174

C175

41 13 100R/3A

XXCBBCNANF-25.000MHz PHYA[0] AVDDL_1 19 V1P8 V3P3

C171 C172 AVDDL_2 25

AVDDL_3 C235 0.1uF

12pF 12pF

0.1uF

0.1uF

10uF

11

PLLVDD

V2P5

FB5 LED4 R107 4.7K

C176

C177

R108 1K 100R/3A

B B

0.1uF

10uF

V3P3

3,15 P_GOOD 46 22 FB6

RESET AVDD_2 16 100R/3A

AVDD_1 12

BIASVDD

C178

C179

C180

C181

C182

R109 1.24K 10

RDAC

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

9

XTALVDD

PADDLE_GND

TEST2

TEST3

B50612

6

5

PDL

A A

Title

AntMiner_ControlBoard_XC7010

Size Document Number Rev

B <Doc> V1.0

Date: Friday, July 01, 2016 Sheet 12 of 15

5 4 3 2 1

5 4 3 2 1

V3P3

V3P3 V3P3 V3P3

J1 J5 R110 4.7K J9

16 8 16 8 16 8

18 VCC A0 7 18 VCC A0 7 18 VCC A0 7

4 PS_MIO28_EN1 EN A1 4 PS_MIO32_EN5 EN A1 4 PS_MIO36_EN9 EN A1

5 6 5 6 5 6

6 BANK34_L1P_PLUG1 15 PLUG A2 2 6 BANK34_L9P_PLUG5 15 PLUG A2 2 6 BANK34_L19P_PLUG9 15 PLUG A2 2

6 BANK34_L1N_RST1 RST GND_0 6 BANK34_L9N_RST5 RST GND_0 6 BANK34_L19N_RST9 RST GND_0

R111

R112

R113

R114

R115

R116

R117

R118

D 12 1 12 1 12 1 D

6 BANK34_L2N_RXD1 11 RXD GND_1 10 6 BANK34_L10N_RXD5 11 RXD GND_1 10 6 BANK34_L20N_RXD9 11 RXD GND_1 10

6 BANK34_L2P_TXD1 TXD GND_2 6 BANK34_L10P_TXD5 TXD GND_2 6 BANK34_L20P_TXD9 TXD GND_2

4 9 4 9 4 9

6,13 BANK34_L22P_SCL1 SCL GND_3 6,13 BANK34_L22P_SCL1 SCL GND_3 6 BANK34_L23P_SCL2 SCL GND_3

6,13 BANK34_L22N_SDA1 3 14 6,13 BANK34_L22N_SDA1 3 14 6 BANK34_L23N_SDA2 3 14

17 SDA GND_4 13 17 SDA GND_4 13 17 SDA GND_4 13

NC GND_5 NC GND_5 NC GND_5

4.7K

4.7K

4.7K

4.7K

4.7K

4.7K

4.7K

4.7K

HashBoard Connector HashBoard Connector HashBoard Connector

V3P3 PS_MIO28_EN1 EN1

V3P3 V3P3 V3P3 BANK34_L1P_PLUG1 PLUG1

BANK34_L1N_RST1 RST1

J2 J6 R120 4.7K BANK34_L2P_TXD1 TXD1

16 8 R119 4.7K 16 8 R121 4.7K BANK34_L2N_RXD1 RXD1

18 VCC A0 7 18 VCC A0 7

4 PS_MIO29_EN2 EN A1 4 PS_MIO33_EN6 EN A1

5 6 5 6 PS_MIO29_EN2 EN2

6 BANK34_0_PLUG2 15 PLUG A2 2 6 BANK34_L11P_PLUG6 15 PLUG A2 2 BANK34_0_PLUG2 PLUG2

6 BANK34_L3N_RST2 RST GND_0 6 BANK34_L11N_RST6 RST GND_0

R122

R123

R124

12 1 12 1 BANK34_L3N_RST2 RST2

6 BANK34_L4N_RXD2 11 RXD GND_1 10 6 BANK34_L12N_RXD6 11 RXD GND_1 10 BANK34_L4P_TXD2 TXD2

6 BANK34_L4P_TXD2 TXD GND_2 6 BANK34_L12P_TXD6 TXD GND_2

4 9 4 9 BANK34_L4N_RXD2 RXD2

6,13 BANK34_L22P_SCL1 SCL GND_3 6,13 BANK34_L22P_SCL1 SCL GND_3

6,13 BANK34_L22N_SDA1 3 14 6,13 BANK34_L22N_SDA1 3 14

C

17 SDA GND_4 13 17 SDA GND_4 13 PS_MIO30_EN3 EN3

C

NC GND_5 NC GND_5

4.7K

4.7K

4.7K

BANK34_L5P_PLUG3 PLUG3

HashBoard Connector HashBoard Connector BANK34_L5N_RST3 RST3

BANK34_L6P_TXD3 TXD3

BANK34_L6N_RXD3 RXD3

PS_MIO31_EN4 EN4

V3P3 BANK34_L7P_PLUG4 PLUG4

V3P3 BANK34_L7N_RST4 RST4

V3P3 V3P3 BANK34_L8P_TXD4 TXD4

R125 4.7K BANK34_L8N_RXD4 RXD4

J3 R126 4.7K J7 R127 4.7K

16 8 16 8 PS_MIO32_EN5 EN5

18 VCC A0 7 18 VCC A0 7 BANK34_L9P_PLUG5 PLUG5

4 PS_MIO30_EN3 EN A1 4 PS_MIO34_EN7 EN A1

5 6 5 6 BANK34_L9N_RST5 RST5

6 BANK34_L5P_PLUG3 PLUG A2 6 BANK34_L15P_PLUG7 PLUG A2

R130

15 2 15 2 BANK34_L10P_TXD5 TXD5

6 BANK34_L5N_RST3 RST GND_0 6 BANK34_L15N_RST7 RST GND_0

R128

R129

12 1 12 1 BANK34_L10N_RXD5 RXD5

6 BANK34_L6N_RXD3 11 RXD GND_1 10 6 BANK34_L16N_RXD7 11 RXD GND_1 10

6 BANK34_L6P_TXD3 TXD GND_2 6 BANK34_L16P_TXD7 TXD GND_2

4 9 4 9 PS_MIO33_EN6 EN6

6,13 BANK34_L22P_SCL1 SCL GND_3 6,13 BANK34_L22P_SCL1 SCL GND_3

3 14 3 14 BANK34_L11P_PLUG6 PLUG6

6,13 BANK34_L22N_SDA1 SDA GND_4 6,13 BANK34_L22N_SDA1 SDA GND_4

4.7K

17 13 17 13 BANK34_L11N_RST6 RST6

NC GND_5 NC GND_5

4.7K

4.7K

BANK34_L12P_TXD6 TXD6

HashBoard Connector HashBoard Connector BANK34_L12N_RXD6 RXD6

B B

PS_MIO34_EN7 EN7

BANK34_L15P_PLUG7 PLUG7

BANK34_L15N_RST7 RST7

BANK34_L16P_TXD7 TXD7

BANK34_L16N_RXD7 RXD7

V3P3 V3P3 PS_MIO35_EN8 EN8

V3P3 V3P3 BANK34_L17P_PLUG8 PLUG8

J8 BANK34_L17N_RST8 RST8

J4 16 8 R132 4.7K BANK34_L18P_TXD8 TXD8

16 8 R131 4.7K 18 VCC A0 7 R133 4.7K BANK34_L18N_RXD8 RXD8

VCC A0 4 PS_MIO35_EN8 EN A1

18 7 R134 4.7K 5 6 R135 4.7K

4 PS_MIO31_EN4 EN A1 6 BANK34_L17P_PLUG8 PLUG A2

5 6 15 2 PS_MIO36_EN9 EN9

6 BANK34_L7P_PLUG4 PLUG A2 6 BANK34_L17N_RST8 RST GND_0

15 2 12 1 BANK34_L19P_PLUG9 PLUG9

6 BANK34_L7N_RST4 RST GND_0 6 BANK34_L18N_RXD8 RXD GND_1

R136

12 1 11 10 BANK34_L19N_RST9 RST9

6 BANK34_L8N_RXD4 RXD GND_1 6 BANK34_L18P_TXD8 TXD GND_2

11 10 4 9 BANK34_L20P_TXD9 TXD9

6 BANK34_L8P_TXD4 TXD GND_2 6,13 BANK34_L22P_SCL1 SCL GND_3

4 9 3 14 BANK34_L20N_RXD9 RXD9

6,13 BANK34_L22P_SCL1 SCL GND_3 6,13 BANK34_L22N_SDA1 SDA GND_4

6,13 BANK34_L22N_SDA1 3 14 17 13

17 SDA GND_4 13 NC GND_5 BANK34_L22P_SCL1 SCL1

NC GND_5

4.7K

HashBoard Connector BANK34_L22N_SDA1 SDA1

HashBoard Connector BANK34_L23P_SCL2 SCL2

BANK34_L23N_SDA2 SDA2

A A

Title

AntMiner_ControlBoard_XC7010

Size Document Number Rev

B <Doc> V1.0

Date: Friday, July 01, 2016 Sheet 13 of 15

5 4 3 2 1

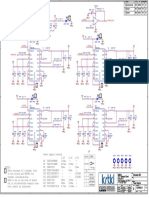

5 4 3 2 1

V12P0 V12P0

V3P3 V3P3

C183 330uF

C184 0.1uF

C185 330uF

C186 0.1uF

R137

R138

D9

D10

D D

FAN1 FAN2

1N4148

1N4148

1 1

1 1

10K

10K

2 2

3 2 3 2

6 BANK35_L15P_FAN_SPEED1 4 3 6 BANK35_L16N_FAN_SPEED4 4 3

6,14 BANK35_L14P_FAN_PWM 4 6,14 BANK35_L14P_FAN_PWM 4

R139 4.7K C187 0.1uF FAN HEADER_NC R140 4.7K C188 0.1uF FAN HEADER_NC

V12P0 V12P0

V3P3 V3P3

C189 330uF

C190 0.1uF

C191 330uF

C192 0.1uF

R141

R142

D11

D12

C C

FAN3 FAN4

1N4148

1N4148

1 1

1 1

10K

10K

2 2

3 2 3 2

6 BANK35_L15N_FAN_SPEED2 4 3 6 BANK35_L17P_FAN_SPEED5 4 3

6,14 BANK35_L14P_FAN_PWM 4 6,14 BANK35_L14P_FAN_PWM 4

R143 4.7K C193 0.1uF FAN HEADER_NC R144 4.7K C194 0.1uF FAN HEADER_NC

V12P0 V12P0

V3P3 V3P3

C195 330uF

C196 0.1uF

C197 330uF

C198 0.1uF

B B

R145

R146

D13

D14

FAN5 FAN6

1N4148

1N4148

1 1

1 1

10K

10K

2 2

3 2 3 2

6 BANK35_L16P_FAN_SPEED3 4 3 6 BANK35_L17N_FAN_SPEED6 4 3

6,14 BANK35_L14P_FAN_PWM 4 6,14 BANK35_L14P_FAN_PWM 4

R147 4.7K C199 0.1uF FAN HEADER_NC R148 4.7K C200 0.1uF FAN HEADER_NC

A A

Title

AntMiner_ControlBoard_XC7010

Size Document Number Rev

A <Doc> V1.0

Date: Friday, July 01, 2016 Sheet 14 of 15

5 4 3 2 1

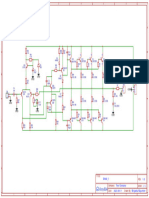

5 4 3 2 1

Imax=3A

V12P0

U9

V1P0 V12P0

U10

Imax=1A V2P5

10 1 L1 2.2uH 10 1 L2 1.0uH

11 AVIN SW1 2 11 AVIN SW1 2

12 PVIN1 SW2 3 12 PVIN1 SW2 3

C201 PVIN2 SW3 PVIN2 SW3

C202

R150

C203

C204

C205

R152

C206

R149 4.7K 13 14 PG_V1P5 13 14

EN VOS 4 PG_V1P0 R153 240 EN VOS 4 PG_V2P5 R151 1K

D

9 PG 9 PG D

SS/TR SS/TR

10uF

10uF

4.99K R156

22uF

10uF

10uF

42.2K R157

22uF

7 R154 4.99K 7 R155 4.99K

C207 8 FSW 5 C208 8 FSW 5

DEF FB DEF FB

PGND1

PGND2

PGND1

PGND2

AGND

AGND

0.0033uF 0.0033uF

TP

TP

TLV62130RGT TLV62130RGT

6

17

16

15

17

16

15

19.6K

20K

V12P0 Imax=1A V1P8

V12P0

U12

Imax=2A V3P3

U11 10 1 L4 1.0uH R158 220

10 1 L3 1.0uH 11 AVIN SW1 2

11 AVIN SW1 2 12 PVIN1 SW2 3

PVIN1 SW2 PVIN2 SW3

C209

C213

R159

C214

12 3 D15

PVIN2 SW3

C210

C211

R161

C212

PG_V2P5 13 14 G/25mA/0603

PG_V1P0 13 14 EN VOS 4 P_GOOD R162 1.58K

EN VOS 4 PG_V1P8 R160 1K 9 PG

PG SS/TR

10uF

10uF

61.9K R166

22uF

9 7 R163 4.99K

SS/TR FSW

24.9K R165

10uF

10uF

22uF

7 R164 4.99K C216 8 5

C215 8 FSW 5 DEF FB

PGND1

PGND2

DEF FB

AGND

0.0033uF

PGND1

PGND2

AGND

0.0033uF When all the power is given properly, The LED is ON

TP

TLV62130RGT

TP

C C

TLV62130RGT

6

17

16

15

6

17

16

15

19.6K

20K

P_GOOD

P_GOOD 3,12

DDR3 Termination Regulator

V12P0

U13

Imax=1A V1P5

V1P5

U14

V3P3

10 1 L5 1.0uH R167 10K

11 AVIN SW1 2 1 10

12 PVIN1 SW2 3 REFIN VIN

PVIN2 SW3

C217

C218

R171

C219

R168

C220

C223

V1P5 TPS51200

PG_V1P8

C221

C222

13 14 9 R169 4.7K

EN VOS 4 PG_V1P5 R170 1K 2 PGOOD

PG VLDOIN

1000pF

9

SS/TR

10uF

10uF

17.4K R173

22uF

10K

10uF

7 R172 4.99K

FSW

10uF

10uF

C224 8 5 VTT_DDR3 8

DEF FB GND

PGND1

PGND2

AGND

0.0033uF 3

VO

TP

C225

C226

C227

TLV62130RGT 7 R174 4.7K VREF_DDR3

B

4 EN B

6

17

16

15

PGND 6

REFOUT

20K

10uF

10uF

10uF

5 11

VOSNS GND_TH C228

0.1uF

12V Power CONN V12P0

V12P0 V12P0

J14 J15 J16

C231

C232

C233

C234

1 6 1 1 D16

C229

C230

2 5 2 2

3 4 3 3

SMBJ15(C)A

4 4

330uF

330uF

10uF

10uF

0.1uF

0.1uF

HEADER 3X2

HEADER 4 HEADER 4

A A

Title

AntMiner_ControlBoard_XC7010

Size Document Number Rev

C <Doc> V1.0

Date: Friday, July 01, 2016 Sheet 15 of 15

5 4 3 2 1

You might also like

- Chris Jones Push Pull LegsDocument26 pagesChris Jones Push Pull Legshaathabaitun30288% (24)

- Special Teams Depth Chart PXFBDocument1 pageSpecial Teams Depth Chart PXFBPhilip StambaughNo ratings yet

- RTL9210-VB-CG Demo V203 PDFDocument5 pagesRTL9210-VB-CG Demo V203 PDFCenusa MihaiNo ratings yet

- Ac7050 - SDM - Xc7s50-1fgga484iDocument10 pagesAc7050 - SDM - Xc7s50-1fgga484imahimithran16No ratings yet

- WPL5 (Completo)Document5 pagesWPL5 (Completo)Jorge Garcia100% (1)

- Panel 01 ModeloDocument1 pagePanel 01 ModeloAlexis Algüerno ContrerasNo ratings yet

- LED555Document1 pageLED555yduvan918No ratings yet

- CircuitDocument3 pagesCircuitAswathypr KumpalathuNo ratings yet

- 3 - MemoryDocument1 page3 - MemoryHungNo ratings yet

- Raspberry Pi Zero 2 W Reduced SchematicsDocument1 pageRaspberry Pi Zero 2 W Reduced SchematicsEugênio MagalhãesNo ratings yet

- Outseal PLC Shield NANODocument1 pageOutseal PLC Shield NANOJeffri Maulana Sholehuddin100% (1)

- Outseal - PLC - Shield - NANO V.1.0 PDFDocument1 pageOutseal - PLC - Shield - NANO V.1.0 PDFPanggung TriyanaNo ratings yet

- Outseal PLC Shield NANO PDFDocument1 pageOutseal PLC Shield NANO PDFalfitoNo ratings yet

- Pentode PDFDocument1 pagePentode PDFAntonio ZappuloNo ratings yet

- Mini2440 SchematicsDocument9 pagesMini2440 Schematicsali_saitNo ratings yet

- J3 FPC50-0.5mm (AT070TN92) J4 FPC40-0.5mm (AT070TN92) : R4 NC R33 NC R32 10KDocument2 pagesJ3 FPC50-0.5mm (AT070TN92) J4 FPC40-0.5mm (AT070TN92) : R4 NC R33 NC R32 10KYuksel NuhogluNo ratings yet

- Micro SD Card Module Catalex Schematic - 2022 10 25Document1 pageMicro SD Card Module Catalex Schematic - 2022 10 25Pablo Juan CazallaNo ratings yet

- Compal LS-565AP r10 BTN BoardDocument1 pageCompal LS-565AP r10 BTN BoardQuenitoLucianoJoãoNo ratings yet

- Schematic - Internal Boards FOSSASAT - 1 - Sheet - 1 - 20191107210138Document1 pageSchematic - Internal Boards FOSSASAT - 1 - Sheet - 1 - 20191107210138ADRIEL RAMIREZ VARGASNo ratings yet

- Schematic Hybrid 7510Document17 pagesSchematic Hybrid 7510Marco KersulNo ratings yet

- Stepper Motor Controller: Gert BaarsDocument2 pagesStepper Motor Controller: Gert BaarsJosé ManuelNo ratings yet

- Wizfi360: Lqfp48Document1 pageWizfi360: Lqfp48rdsonsantos0No ratings yet

- Vest3000mkii TurntableDocument16 pagesVest3000mkii TurntableElkin BabiloniaNo ratings yet

- SCH 1010Document1 pageSCH 1010轮摇No ratings yet

- REPEATER IDER ISD25xx - Repeater Ider Isd2590 16f877aDocument1 pageREPEATER IDER ISD25xx - Repeater Ider Isd2590 16f877amanuel contrerasNo ratings yet

- Circuit Diagram: U101 AD6537BABCDocument7 pagesCircuit Diagram: U101 AD6537BABCsousalrNo ratings yet

- Outseal PLC Shield UNODocument1 pageOutseal PLC Shield UNODadang Ibnu SetyawanNo ratings yet

- Diagrama Esquematico PIC TRAINERDocument1 pageDiagrama Esquematico PIC TRAINERDaniel Haro100% (3)

- PiSmasher Schematic r4p1Document10 pagesPiSmasher Schematic r4p1labashlkNo ratings yet

- uSDX MicronDocument1 pageuSDX MicronAdrian AdrianNo ratings yet

- Schematic 1Document1 pageSchematic 1shigidavisNo ratings yet

- Quiz#08 - 02 - Timer Circuit - To PLCDocument1 pageQuiz#08 - 02 - Timer Circuit - To PLC22146015No ratings yet

- Outseal - PLC - Shield - UNO v.1 PDFDocument1 pageOutseal - PLC - Shield - UNO v.1 PDFPanggung TriyanaNo ratings yet

- Outseal PLC Shield UNO 1Document1 pageOutseal PLC Shield UNO 1ilhamNo ratings yet

- Outseal PLC Shield UNODocument1 pageOutseal PLC Shield UNOwramadhani65No ratings yet

- Seeed Studio EdgeBox-ESP-100 Schematic PDFDocument15 pagesSeeed Studio EdgeBox-ESP-100 Schematic PDFhidden MaskNo ratings yet

- SchmeaticsDocument1 pageSchmeaticsmuhammad samrozNo ratings yet

- R2-750R Uart Mbus BDMDocument1 pageR2-750R Uart Mbus BDMnelson linceNo ratings yet

- Title:: File: Arduino - LDR - KICAD - SCH SheetDocument1 pageTitle:: File: Arduino - LDR - KICAD - SCH SheetakNo ratings yet

- Circuit Thesis PDFDocument1 pageCircuit Thesis PDFKostas PaternasNo ratings yet

- SM30 - Media Key - Rev SaDocument1 pageSM30 - Media Key - Rev SajjoaquimmartinsNo ratings yet

- Cyber Dom. Capital Capital: END GameDocument2 pagesCyber Dom. Capital Capital: END Gametracy_vNo ratings yet

- 1p - Smart Meter - Rev-03Document4 pages1p - Smart Meter - Rev-03infoNo ratings yet

- SisminDocument1 pageSisminAnonymous 0LkvQhHNo ratings yet

- Sismin PDFDocument1 pageSismin PDFAnonymous 0LkvQhHNo ratings yet

- Schematic Combo LedDocument12 pagesSchematic Combo LedH S MannNo ratings yet

- Schematic - LED DriverDocument2 pagesSchematic - LED DriverBilal AhmedNo ratings yet

- 2020 06 30 - 20 57 53 - 958102Document1 page2020 06 30 - 20 57 53 - 958102Daniel OfoeNo ratings yet

- Ux425ug Ux425ug Ux425ug Ux425ug Ux425ug Ux425ugDocument55 pagesUx425ug Ux425ug Ux425ug Ux425ug Ux425ug Ux425ugNoel MirandaNo ratings yet

- 24bit1 AdcDocument1 page24bit1 AdcKishore PagarNo ratings yet

- Iprog Powerboard SCHDocument1 pageIprog Powerboard SCHdrsNo ratings yet

- Ax7035 SCHDocument18 pagesAx7035 SCHmahimithran16No ratings yet

- STM32F103C8T6 Schematic PDFDocument1 pageSTM32F103C8T6 Schematic PDFNguyễn Hưng100% (1)

- weatherSTAMP - UnknownDocument1 pageweatherSTAMP - UnknownJony DarkoNo ratings yet

- Haptics: VREG - S4A - 1P8 NFC - Simvcc1Document6 pagesHaptics: VREG - S4A - 1P8 NFC - Simvcc1AlineNo ratings yet

- Redmi K20pro 1Document6 pagesRedmi K20pro 1SitrayasTech EcNo ratings yet

- Sub PCB SchematicDocument6 pagesSub PCB Schematichemantasahoo1009No ratings yet

- Secure Soic Click Schematic v100Document1 pageSecure Soic Click Schematic v100Gogo GogevNo ratings yet

- 1 1.sch 2 2.sch 3 3.schDocument4 pages1 1.sch 2 2.sch 3 3.schPrasanna Kumar VotarikariNo ratings yet

- SCH Te0727 02 41C34Document14 pagesSCH Te0727 02 41C34Satvik HardatNo ratings yet

- Tinkerfest - ViiiDocument1 pageTinkerfest - ViiiSatvik HardatNo ratings yet

- Intel® Pentium® and Celeron® Processor N-And J - Series: Datasheet Volume 3 of 3Document4,654 pagesIntel® Pentium® and Celeron® Processor N-And J - Series: Datasheet Volume 3 of 3Satvik HardatNo ratings yet

- Pentium Celeron N Series J Series Datasheet Vol 1 PDFDocument220 pagesPentium Celeron N Series J Series Datasheet Vol 1 PDFRivai GoBlog100% (1)

- NUC5i5RYB NUC5i3RYB TechProdSpecDocument73 pagesNUC5i5RYB NUC5i3RYB TechProdSpecJanNo ratings yet

- SDZNMMBHER 008G SanDiskDocument67 pagesSDZNMMBHER 008G SanDiskSatvik HardatNo ratings yet

- ATL Tinkerpreneur 2022 Brochure PDFDocument14 pagesATL Tinkerpreneur 2022 Brochure PDFSatvik HardatNo ratings yet

- Snapdragon 865 Mobile HDK Product Brief - 87 pn003 1 PDFDocument2 pagesSnapdragon 865 Mobile HDK Product Brief - 87 pn003 1 PDFSatvik HardatNo ratings yet

- W65C02S Microprocessor Data Sheet: The Western Design Center, IncDocument40 pagesW65C02S Microprocessor Data Sheet: The Western Design Center, IncJayath GayanNo ratings yet

- qrb5165 Soc Product Brief - 87 28730 1 BDocument2 pagesqrb5165 Soc Product Brief - 87 28730 1 BSatvik HardatNo ratings yet

- stm32h750vbt6 PDFDocument335 pagesstm32h750vbt6 PDFSatvik HardatNo ratings yet

- LicenseDocument1 pageLicenseAbderrahmane SmaaliNo ratings yet

- Pgurl 12192663594361198Document4 pagesPgurl 12192663594361198Satvik HardatNo ratings yet

- 114atom c2000 Microserver DatasheetDocument746 pages114atom c2000 Microserver DatasheetSatvik HardatNo ratings yet

- Pgurl 2665033432894930Document1 pagePgurl 2665033432894930Satvik HardatNo ratings yet

- BeagleV V0.9wbergerDocument21 pagesBeagleV V0.9wbergerSatvik HardatNo ratings yet

- w65c02s 2572Document33 pagesw65c02s 2572Satvik HardatNo ratings yet

- En - mb1364 H753ZI C01 SchematicDocument9 pagesEn - mb1364 H753ZI C01 SchematicJonathan GonzagaNo ratings yet

- MCT 8316 Awghw 4 GDDocument178 pagesMCT 8316 Awghw 4 GDSatvik HardatNo ratings yet

- Adverbs AlexDocument11 pagesAdverbs AlexAlex Highlander MunteanuNo ratings yet

- Warlock Dragon PatreonDocument11 pagesWarlock Dragon PatreonBleizyNo ratings yet

- Cor Pulmonale - A Student To Student GuideDocument4 pagesCor Pulmonale - A Student To Student GuideVaseem ZamairNo ratings yet

- Puzzle 1 (Medium, Difficulty Rating 0.50)Document4 pagesPuzzle 1 (Medium, Difficulty Rating 0.50)hahattproNo ratings yet

- Pattern - Amigurumi Cat Doll: Created by Havva ÜnlüDocument30 pagesPattern - Amigurumi Cat Doll: Created by Havva ÜnlüRamos MontseNo ratings yet

- Códigos para RegeditDocument9 pagesCódigos para RegeditElvin Ronald Cabrera Moreno100% (6)

- Akira's Flying Wheelchair Chapter One PreviewDocument12 pagesAkira's Flying Wheelchair Chapter One PreviewMarco BalsamoNo ratings yet

- Yfm350fwa07 5uhg GrizzlyDocument83 pagesYfm350fwa07 5uhg GrizzlyHercílio JuniorNo ratings yet

- Sinag Pep Squad: Adversities Behind Victories: Deped Beefs Up Digital Education ThroughDocument8 pagesSinag Pep Squad: Adversities Behind Victories: Deped Beefs Up Digital Education ThroughBilly Grant Ponayo BalonaNo ratings yet

- Dan Dan Kokoro Hikareteku PDFDocument4 pagesDan Dan Kokoro Hikareteku PDFROSA MASINo ratings yet

- Pokemon Teams I've UsedDocument16 pagesPokemon Teams I've UsedLuis MendezNo ratings yet

- Secret Love SongDocument3 pagesSecret Love SongPaul ValerosNo ratings yet

- Sony Interactive EntertainmentDocument7 pagesSony Interactive EntertainmentMary MejíaNo ratings yet

- Joints Movements in Planes and AxesDocument1 pageJoints Movements in Planes and AxesNaveera GhouriNo ratings yet

- Catalogo Vidrio Mobicell DistribuidorDocument3 pagesCatalogo Vidrio Mobicell DistribuidorANTHONY SANCHEZNo ratings yet

- Cardiac RehabDocument52 pagesCardiac RehabPraneethaNo ratings yet

- #StayAtHome GamesDocument37 pages#StayAtHome GamesIRDINA ADLIN BINTI FIRDAUS MoeNo ratings yet

- Doc559863158 662202728Document22 pagesDoc559863158 662202728babibel19100% (2)

- TB016Document1 pageTB016frank rodriguezNo ratings yet

- Soc MailDocument6 pagesSoc MailAhmed Abo HamzaNo ratings yet

- 6042 Parts 8990467 02-22-12 ANSI EnglishDocument462 pages6042 Parts 8990467 02-22-12 ANSI EnglishwalmadasanNo ratings yet

- Risk in ICCP Anode ChangesDocument2 pagesRisk in ICCP Anode ChangeskazishahNo ratings yet

- NewBridgeMag - 2019-02Document101 pagesNewBridgeMag - 2019-02KoolDoodNo ratings yet

- Vier Französische Weihnachtslieder: Quatre Noëls FrançaisDocument1 pageVier Französische Weihnachtslieder: Quatre Noëls FrançaisSebastian HernandezNo ratings yet

- Dinosaur Plush Bundle Embroidery UpdateDocument22 pagesDinosaur Plush Bundle Embroidery UpdatedavisonromoNo ratings yet

- Pre-Delivery InspectionDocument5 pagesPre-Delivery InspectionSergio FallasNo ratings yet

- Suspencion CenturyDocument11 pagesSuspencion CenturyDenis HernandezNo ratings yet

- Spahn Award Edmond Sun 12-30-14Document1 pageSpahn Award Edmond Sun 12-30-14Price LangNo ratings yet