Professional Documents

Culture Documents

A 1.15μ W 5.54mm Sup 3 - Sup Implant With A Bidirectional Neural Sensor and Stimulator SoC Utilizing Bi-Phasic Quasi-Static Brain Communication

Uploaded by

Generation GenerationOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

A 1.15μ W 5.54mm Sup 3 - Sup Implant With A Bidirectional Neural Sensor and Stimulator SoC Utilizing Bi-Phasic Quasi-Static Brain Communication

Uploaded by

Generation GenerationCopyright:

Available Formats

C13-2

A 1.15μW 5.54mm3 Implant with a Bidirectional Neural Sensor and Stimulator SoC utilizing

Bi-Phasic Quasi-static Brain Communication achieving 6kbps-10Mbps Uplink

with Compressive Sensing and RO-PUF based Collision Avoidance

Baibhab Chatterjee, Gaurav Kumar K, Mayukh Nath, Shulan Xiao, Nirmoy Modak, Debayan Das, Jayant Krishna and Shreyas Sen

Purdue University, West Lafayette, IN, USA. email: {bchatte, shreyas}@purdue.edu

Abstract during TP/SP. A 17nW charge pump generates 1.8V VPUMP to bias the

To solve the challenge of powering and communication in a brain power gates (on the supply of the duty-cycled modules) in deep-

implant with low end-end energy loss, we present Bi-Phasic Quasi- subthreshold during off-state to reduce leakage by 500X (from

static Brain Communication (BP-QBC), achieving < 60dB worst-case 0.51μW to 1nW). A ring-oscillator based Physical Un-clonable

channel loss, and ~41X lower power w.r.t. traditional Galvanic body Function (RO-PUF) with a 9b-PRBS ensures that different nodes

channel communication (G-BCC) at a carrier frequency of 1MHz within the brain enters TP/SP in staggered timeslots, thereby enabling

(~6X lower power than G-BCC at 10MHz) by blocking DC current collision avoidance without a MAC layer. A wake-up based CS front

paths through the brain tissue. An additional 16X improvement in net end reduces the Tx DR, resulting in an average duty-cycled power of

energy-efficiency (pJ/b) is achieved through compressive sensing 1.15μW (0.52μW without leakage), at 10Mbps with CS. This results

(CS), allowing a scalable (6kbps-10Mbps) duty-cycled uplink (UL) in a >60X improvement in energy-efficiency (pJ/b) as compared to the

from the implant to an external wearable, while reducing the active narrowband state-of-the-art BMIc [2]. The CS module is equipped

power consumption to 0.52μW at 10Mbps, i.e. within the range of with an on-chip 2-stage DWT-based sparsifier and dual varying-seed-

harvested body-coupled power in the downlink (DL), with externally PRBS sensing-matrix generator, to compress both sparse and non-

applied electric currents < 1/5th of ICNIRP safety limits. BP-QBC sparse signals with varying compression factor (CF) from 5X to

eliminates the need for sub-cranial interrogators, utilizing quasi-static 33.33X. The BMIc Node DL Rx consists a 10.1nW Front-End (FE)

electrical signals for end-to-end BCC, avoiding transduction losses. amplifier, a 3.2nW 4-stage passive envelope detector and a 16.2nW

Introduction and Motivation fully digital oversampled CDR. The model for the BMIc channel

Traditional brain-machine interfaces (BMIc) with tethered data transfer function (TF) is developed analytically from dipole coupling

transmission/powering increases risks of cortical scarring, gliosis, theory and is verified with Finite Element method (FEM)-based

infection, and cerebrospinal fluid (CSF) leakage. Recently, untethered simulations as well as IC-measurements using the implemented SoC,

miniaturized wireless neural sensors [1-3] and stimulators [4-6] have which enables realistic BCC-based BMIc channel measurements for

been demonstrated with various data/power transmission modalities the first time because of its small form-factor (node volume < 6mm3).

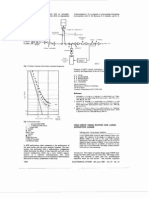

as shown in Fig. 1. RF [1,7] suffers from increased tissue absorption, Measurement Results

requiring large Tx power (0.5W in [1,7] which exceeds ICNIRP safety Fig. 4(a) shows the Power consumption of the Tx over 42kHz-

guidelines [8] by ~10X). Optical (OP) [2] and Ultrasonic (US) [3] 1GHz and compares with traditional G-BCC measurements. At a

telemetry are safer, at the cost of significant loss due to scattering and nominal quasi-static frequency of 1MHz, BP-QBC offers 41X lower

skull absorption (110dB loss in [3]), requiring a sub-cranial power than G-BCC. Fig. 4(a) also shows the randomized time slots

interrogator which needs to be surgically placed, and reduces end-to- for duty-cycled TP/SP, along with the time-domain stimulation

end efficiency. Magneto-Electric (ME) [4] methods exhibit low waveforms in a 0.9% phosphate buffered saline (PBS) solution. The

tissue-absorption but has large transduction loss (0.1mT magnetic measurements with CS are shown in Fig. 4(b). For CF=33.33X, the

field, equivalent to ~300kV/m electric field requirement in [4] for iso- 10Mbps TP power reduces from 7.23mW to 217μW, while

energy-density). As an alternative, Fig. 1 describes BP-QBC for consuming additional computation power of 212μW, resulting in

communication in a neural implant. The implant can sense and overall power reduction of ~16X. The memory requirement is also

transmit information to a wearable headphone-shaped hub through the reduced by >10X as compared to a ‘store and send’ scenario. EEG

UL. The hub sends power and configuration/scan bits to the implant waveforms from GigaScience database are passed through the CS

through the DL. Both UL and DL use fully electrical signals to avoid (CF=33.33X), and are reconstructed in MATLAB. In Fig. 5(a), the

transduction losses (a challenge in OP, US and ME systems). The UL power consumption of the DL Rx is plotted w.r.t. the DR, showing an

use MHz-GHz narrow-band frequencies to (1) avoid interfering with energy efficiency of < 35pJ/b at 1kbps. The charging of the C STORE

physiological signals and (2) avoid stimulating the brain tissue with w.r.t. the DL input signal amplitude shows a minimum input voltage

low-frequencies. For traditional G-BCC, the electrodes on the implant requirement of 70mVp for charging up to 1.2V. The In-vitro setup for

are shorted through the low-impedance (~kΩ) tissue/fluids in the body, BP-QBC channel TF measurement is shown in Fig. 5(b). Brain slices

resulting in high DC power consumption. A DC-blocking capacitor in from the C57BL/6J Mouse strain are used, adhering to the overseeing

the signal path for BP-QBC creates a bi-phasic output that eliminates Animal Care and Use Committee guidelines. 500μm-2mm thick slices

the DC power going into the tissue and maintains ion balance. are placed in a measurement dish containing artificial CSF saturated

System on a Chip (SoC) Architecture and Implementation with carbogen (95% O2+5% CO2). Two electrodes (signal+ref) are

The implemented BP-QBC SoC in 65nm CMOS (Fig. 2, top) placed on the surface of the brain slice. The Rx electrodes are placed

features (1) a 52pJ/b, duty-cycled, OOK-based scalable UL Tx with at a distance (L) from the Tx electrodes. The experiments are repeated

on -chip clock, CS and collision avoidance, (2) a 31nW DL Rx to with PBS in a PET container with similar dimensions as that of the

receive system configuration bits and control signals, (3) a 89.2% human skull (diameter~110mm). The channel TF shown in Fig. 5(b)

efficiency (IStim/IDC) bi-phasic stimulator and (4) a 30-stage RF- exhibits a loss of ~20dB for the mouse brain and ~60dB in PBS with

rectifier (RR) based energy-harvester [9], capable of generating 1V human-brain sized dimensions. Fig. 6 compares the SoC performance

supply with ~70mVp input. Dual supply domains are utilized: 0.4V with state-of-the-art BMIc telemetry/stimulators, exhibiting (1)

for low-leakage/low-power in always-on timer/controller modules, highest DR (3000X improvement vs. [2]) for narrowband BMIc, (2)

and 1V for duty-cycled data transmission/stimulation. The SoC uses max. channel length with (3) lowest always-on power and (4) lowest

1:1000 duty cycling with a 100ms transmit phase (TP) + 100ms end-to-end loss (>20 dB better than prior art) due to fully-electrical

stimulation phase (SP) within 100s. Additional modes with 1:100 and quasi-static signaling, while demonstrating the first BP-QBC link

1:10 duty cycling can be configured through DL control bits. A 13nW with simultaneous powering, communication, CS and stimulation.

reference (0.4V, 1V) generator and two 24nW LDOs are used to

References

supply VDD for the SoC, utilizing the energy harvested from an RR. [1] J. Lee, NER 2019, pp.871. [2] J. Lim, ISSCC 2020, pp.416. [3] M. Ghanbari,

Fig. 3 shows the design details of the building blocks of the SoC. The ISSCC 2019, pp.284. [4] Z. Yu, ISSCC 2020, pp.510. [5] Y. Jia, ISSCC 2018,

external CSTORE at the output of RR is carefully optimized for a max. pp.468. [6] Y. Lo, ISSCC 2016, pp.382. [7] J. Lee, bioRxiv, 2020, 2020.09.

data rate (DR) with <<100s charging time and <100mV voltage droop 11.293829. [8] ICNIRP Guidelines 2020. [9] N. Roberts, ISSCC 2016, pp.450.

1 978-4-86348-780-2 ©2021 JSAP 2021 Symposium on VLSI Circuits Digest of Technical Papers

You might also like

- 2015-BIOCAS-A 64-Channel Ultra-Low Power Bioelectric Signal Acquisition System For Brain-Computer InterfaceDocument4 pages2015-BIOCAS-A 64-Channel Ultra-Low Power Bioelectric Signal Acquisition System For Brain-Computer InterfaceLuật TrầnNo ratings yet

- Thomas Barber JR., Phil Carvey, Anantha Chandrakasan: BBN's 141. ForDocument5 pagesThomas Barber JR., Phil Carvey, Anantha Chandrakasan: BBN's 141. FormharitmsNo ratings yet

- Regular Correspondence: Compact High-Frequency Output Buffer For Testing of Analog CMOS VLSI CircuitsDocument3 pagesRegular Correspondence: Compact High-Frequency Output Buffer For Testing of Analog CMOS VLSI CircuitsSaranya ChakrabortyNo ratings yet

- A 2.4-Ghz, Hybrid 10-Mb/S BPSK Backscatter and 1-Mb/S FSK Bluetooth TX With Hardware ReuseDocument3 pagesA 2.4-Ghz, Hybrid 10-Mb/S BPSK Backscatter and 1-Mb/S FSK Bluetooth TX With Hardware ReuseAli M. HayajnehNo ratings yet

- 1.12-Tbs 32-QAM-OfDM Superchannel With 8.6-BsHz Intrachannel Spectral Efficiency and Space-Division Multiplexing With 60-BsHz Aggregate Spectral EfficiencyDocument3 pages1.12-Tbs 32-QAM-OfDM Superchannel With 8.6-BsHz Intrachannel Spectral Efficiency and Space-Division Multiplexing With 60-BsHz Aggregate Spectral Efficiencymalhiavtarsingh100% (1)

- A Low-Power Sensor Read-Out Circuit With FSK Telemetry For Inductively-Powered Implant SystemDocument4 pagesA Low-Power Sensor Read-Out Circuit With FSK Telemetry For Inductively-Powered Implant SystemSreelal SreedharanNo ratings yet

- 12.3 A 6nW Inductive-Coupling Wake-Up Transceiver For Reducing Standby Power of Non-Contact Memory Card by 500×Document3 pages12.3 A 6nW Inductive-Coupling Wake-Up Transceiver For Reducing Standby Power of Non-Contact Memory Card by 500×felix_007_villedaNo ratings yet

- BSN SummaryDocument6 pagesBSN Summaryhex0x1No ratings yet

- (Doi 10.1109/ISSCC.2013.6487622) Parikh, S. Kao, T. Hidaka, Y. Jian Jiang, Toda, A. Mcleod, - (IEEE 2013 IEEE International Solid-State Circuits Conference (ISSCC 2013) - San Francisco, CA (2Document3 pages(Doi 10.1109/ISSCC.2013.6487622) Parikh, S. Kao, T. Hidaka, Y. Jian Jiang, Toda, A. Mcleod, - (IEEE 2013 IEEE International Solid-State Circuits Conference (ISSCC 2013) - San Francisco, CA (2sulagnadeyNo ratings yet

- Miniaturized Six-Port Receiver For 60 GHZ Communication ENDocument5 pagesMiniaturized Six-Port Receiver For 60 GHZ Communication ENWalter Santiago Campos ArandaNo ratings yet

- A 52 PJ Bit OOK Transmitter With Adaptable Data RateDocument4 pagesA 52 PJ Bit OOK Transmitter With Adaptable Data RatejaberyemeniNo ratings yet

- A 5-Gbs Adaptive Digital CDR Circuit With SSC Capability and Enhanced High-Frequency Jitter Tolerance PDFDocument5 pagesA 5-Gbs Adaptive Digital CDR Circuit With SSC Capability and Enhanced High-Frequency Jitter Tolerance PDFMinh KhangNo ratings yet

- A 65nm CMOS Ultra Low Power and Low Noise 131M Front-End Transimpedance AmplifierDocument5 pagesA 65nm CMOS Ultra Low Power and Low Noise 131M Front-End Transimpedance AmplifierBerry KueteNo ratings yet

- Design and Optimization of ÷8/9 Divider in PLL Frequency Synthesizer With Dynamic Logic (E - TSPC)Document5 pagesDesign and Optimization of ÷8/9 Divider in PLL Frequency Synthesizer With Dynamic Logic (E - TSPC)himaja1No ratings yet

- Performance Analysis of A Driver Cricuit and An Input Amplifier For BCCDocument8 pagesPerformance Analysis of A Driver Cricuit and An Input Amplifier For BCCAJER JOURNALNo ratings yet

- Compact Notch Uwb10Document3 pagesCompact Notch Uwb10Satyadip PaulNo ratings yet

- BCS Practice Questions - 2021Document11 pagesBCS Practice Questions - 2021bharatshrawagiNo ratings yet

- 24.2 A 1.15Gb/s Fully Parallel Nonbinary LDPC Decoder With Fine-Grained Dynamic Clock GatingDocument3 pages24.2 A 1.15Gb/s Fully Parallel Nonbinary LDPC Decoder With Fine-Grained Dynamic Clock GatingNguyen Van ToanNo ratings yet

- Isscc 2019 / Session 22 / Physiological Monitoring / 22.1Document3 pagesIsscc 2019 / Session 22 / Physiological Monitoring / 22.1郭圳龍No ratings yet

- Polystim Neurotechnologies Laboratory Department of Electrical Engineering, École Polytechnique de Montréal, Canada Benoit - Gosselin@Polymtl - CaDocument4 pagesPolystim Neurotechnologies Laboratory Department of Electrical Engineering, École Polytechnique de Montréal, Canada Benoit - Gosselin@Polymtl - CaAlex WongNo ratings yet

- Isscc 2010 / Session 20 / Next-Generation Optical & Electrical Interfaces / 20.4Document3 pagesIsscc 2010 / Session 20 / Next-Generation Optical & Electrical Interfaces / 20.4Karthikeyan GunasekaranNo ratings yet

- 11 A Low-Power Single-Phase Clock MultibandDocument5 pages11 A Low-Power Single-Phase Clock MultibandDilip KumarNo ratings yet

- A Wide-PCE-Dynamic-Range CMOS Cross-Coupled Differential-Drive Rectifier For Ambient RF Energy HarvestingDocument5 pagesA Wide-PCE-Dynamic-Range CMOS Cross-Coupled Differential-Drive Rectifier For Ambient RF Energy Harvestinghusam hamidNo ratings yet

- A High-Speed Continuous-Time Bandpass VHF Filter in TechnologyDocument4 pagesA High-Speed Continuous-Time Bandpass VHF Filter in Technologyعاطف رضاNo ratings yet

- Analysis of Pre-Emphasis Techniques For Channels With Higher-Order Transfer FunctionDocument12 pagesAnalysis of Pre-Emphasis Techniques For Channels With Higher-Order Transfer FunctionPraveen KumarNo ratings yet

- Pulse Oximeter Improvement With An ADC-DAC Feedback Loop and A Radial Reflectance SensorDocument4 pagesPulse Oximeter Improvement With An ADC-DAC Feedback Loop and A Radial Reflectance SensorFatih Mehmet FerahNo ratings yet

- Digital Detection and Feedback Fluxgate MagnetometerDocument7 pagesDigital Detection and Feedback Fluxgate MagnetometerhsongunNo ratings yet

- Ibm PllserdesDocument3 pagesIbm PllserdesMeeraNo ratings yet

- Ultra-Low Power Phase-Locked LoopDocument4 pagesUltra-Low Power Phase-Locked Loophawking1122No ratings yet

- Imaging The Heart With Ultrasound: Zili YuDocument28 pagesImaging The Heart With Ultrasound: Zili YuAshwin BhatNo ratings yet

- Keshav (2022jop2591)Document5 pagesKeshav (2022jop2591)keshavNo ratings yet

- Assessment of LTE Uplink Power Control With Different Frequency Reuses SchemesDocument7 pagesAssessment of LTE Uplink Power Control With Different Frequency Reuses SchemesMuhammad ElGhawabyNo ratings yet

- Treesa s2Document5 pagesTreesa s2jayalakshmisnairNo ratings yet

- A 4.5mm2 Multimodal Biosensing SoC For PPG, ECG, BIOZ and GSR Acquisition in Consumer Wearable DevicesDocument3 pagesA 4.5mm2 Multimodal Biosensing SoC For PPG, ECG, BIOZ and GSR Acquisition in Consumer Wearable DevicesgetitabidNo ratings yet

- A Low Power Low Noise Chopper-Stabilized Tow-Stage Operational Amplifier For Portable Bio-Potential Acquisition Systems Using 90 NM TechnologyDocument18 pagesA Low Power Low Noise Chopper-Stabilized Tow-Stage Operational Amplifier For Portable Bio-Potential Acquisition Systems Using 90 NM TechnologyVitaliyGNo ratings yet

- 2session 27 Overview: Biomedical CircuitsDocument26 pages2session 27 Overview: Biomedical CircuitsGiang HoaiNo ratings yet

- Ban Pimrc 2010Document6 pagesBan Pimrc 2010ragaconiNo ratings yet

- Ultra Low Power Ldo ThesisDocument6 pagesUltra Low Power Ldo Thesisninavazquezhartford100% (2)

- Blind Paper SpineDocument5 pagesBlind Paper SpineJoao PauloNo ratings yet

- Andre Carpenter 02072014 Tracked VersionDocument6 pagesAndre Carpenter 02072014 Tracked VersionnikhatskhanNo ratings yet

- 2007 07 A Multi-Mode Power Gating Structure For Low-Voltage Deep-Submicron CMOS ICsDocument5 pages2007 07 A Multi-Mode Power Gating Structure For Low-Voltage Deep-Submicron CMOS ICsKuldeep SinghNo ratings yet

- A 0.5V 9.26µW 15.28mΩ√Hz Bio-Impedance Sensor IC with 0.55° Overall Phase ErrorDocument3 pagesA 0.5V 9.26µW 15.28mΩ√Hz Bio-Impedance Sensor IC with 0.55° Overall Phase ErrorJack GengNo ratings yet

- 2011 Scaling CPLDocument5 pages2011 Scaling CPLankushwreNo ratings yet

- Simple PotentiostatDocument3 pagesSimple PotentiostatguiburNo ratings yet

- A 0.0021 mm2 1.82 MW 2.2 GHZ PLL Using Time-Based Integral Control in 65 NM CMOSDocument13 pagesA 0.0021 mm2 1.82 MW 2.2 GHZ PLL Using Time-Based Integral Control in 65 NM CMOSnayakadarsh2000No ratings yet

- QDocument4 pagesQSri NikethanNo ratings yet

- A Self-Organized Uplink Power Control For Cross-Tier Interference Management in Femtocell NetworksDocument6 pagesA Self-Organized Uplink Power Control For Cross-Tier Interference Management in Femtocell NetworksMark KGNo ratings yet

- An Fpga-Based Electronic Cochlea With Dual Fixed-Point ArithmeticDocument6 pagesAn Fpga-Based Electronic Cochlea With Dual Fixed-Point ArithmeticcutiepiemaniNo ratings yet

- A 5.8-Ghz High Efficient, Low Power, Low Phase Noise Cmos Vco For Ieee 802.11ADocument4 pagesA 5.8-Ghz High Efficient, Low Power, Low Phase Noise Cmos Vco For Ieee 802.11ARitika SinghNo ratings yet

- Conclusion:: To DiagnosticsDocument3 pagesConclusion:: To DiagnosticsDhaval PatelNo ratings yet

- An Ultra-Low Power ISM-band Integer-N Frequency Synthesizer Dedicated To Implantable Medical MicrosystemsDocument10 pagesAn Ultra-Low Power ISM-band Integer-N Frequency Synthesizer Dedicated To Implantable Medical MicrosystemsJakrawat BudNo ratings yet

- A High-Speed/Low-Power Multiplier Using An Advanced Spurious Power Suppression TechniqueDocument4 pagesA High-Speed/Low-Power Multiplier Using An Advanced Spurious Power Suppression TechniqueBappy DebnathNo ratings yet

- 2011-TBCAS-folded-A Low-Power 32-Channel Digitally Programmable Neural Recording Integrated CircuitDocument11 pages2011-TBCAS-folded-A Low-Power 32-Channel Digitally Programmable Neural Recording Integrated CircuitLuật TrầnNo ratings yet

- Mmwave Submmwave SoC RFIT11Document4 pagesMmwave Submmwave SoC RFIT11workmanjNo ratings yet

- Advanced Communication Lab Manual PDFDocument46 pagesAdvanced Communication Lab Manual PDFMythri RangaswamyNo ratings yet

- A Fast and Accurate Bunch-By-bunch Current Monitor - Mopd40Document3 pagesA Fast and Accurate Bunch-By-bunch Current Monitor - Mopd40beautifulmind33No ratings yet

- A 1.8Ghz Cmos: Low-Power Truly-Modular Programmable Divider in Standard TechnologyDocument4 pagesA 1.8Ghz Cmos: Low-Power Truly-Modular Programmable Divider in Standard TechnologyMuhammad_Swilam_2010No ratings yet

- 07501825Document15 pages07501825Ma SeenivasanNo ratings yet

- Paper LC Vco SohiniDocument5 pagesPaper LC Vco SohiniDr-Umakanta NandaNo ratings yet

- Wireless Issues and Spectrum ReformDocument107 pagesWireless Issues and Spectrum ReformGeneration GenerationNo ratings yet

- Fulltext01Document5 pagesFulltext01Generation GenerationNo ratings yet

- Part1 Medical Device Networking For Smarter Healthcare WPDocument1 pagePart1 Medical Device Networking For Smarter Healthcare WPGeneration GenerationNo ratings yet

- RF, and Microwaves in Medicine and Biology, (Doi:: 10.1109/JERM.2020.3026588Document16 pagesRF, and Microwaves in Medicine and Biology, (Doi:: 10.1109/JERM.2020.3026588Generation GenerationNo ratings yet

- Torture and The Cruel, Inhuman and Degrading Treatment of Detainees The Effectiveness and Consequences of 'Enhanced' InterrogationDocument39 pagesTorture and The Cruel, Inhuman and Degrading Treatment of Detainees The Effectiveness and Consequences of 'Enhanced' InterrogationGeneration Generation100% (1)

- !!!FDAVaccines Can Be Approved Even If They Do Not Prevent Infection or Transmission April 2023Document33 pages!!!FDAVaccines Can Be Approved Even If They Do Not Prevent Infection or Transmission April 2023Generation GenerationNo ratings yet

- 1 s2.0 S0013935120307854 MainDocument10 pages1 s2.0 S0013935120307854 MainMaya NettaNo ratings yet

- ! - Katalog - Gesamt - 2011 - GB - 1.qxd - 1674904Document2 pages! - Katalog - Gesamt - 2011 - GB - 1.qxd - 1674904Generation GenerationNo ratings yet

- 246544159-AWY-9400-ManualDocument1 page246544159-AWY-9400-ManualGeneration GenerationNo ratings yet

- Mainstream Brain-Computer Interfaces Are Coming - Just Ask Synchron, Neuralink, Paradromics, and HackerBCIDocument6 pagesMainstream Brain-Computer Interfaces Are Coming - Just Ask Synchron, Neuralink, Paradromics, and HackerBCIGeneration GenerationNo ratings yet

- Neurosurg Focus Article PE10 1Document8 pagesNeurosurg Focus Article PE10 1Generation GenerationNo ratings yet

- Bocan TissueModels IEEESensorsDocument2 pagesBocan TissueModels IEEESensorsGeneration GenerationNo ratings yet

- Fneur 13 880814Document18 pagesFneur 13 880814Generation GenerationNo ratings yet

- Neurosurg Focus Article PE10 1Document8 pagesNeurosurg Focus Article PE10 1Generation GenerationNo ratings yet

- The Missing Manuscript of Dr. Jose Delgado S Radio Controlled Bulls - June-15-R29Document2 pagesThe Missing Manuscript of Dr. Jose Delgado S Radio Controlled Bulls - June-15-R29Generation GenerationNo ratings yet

- Fneur 13 880814Document18 pagesFneur 13 880814Generation GenerationNo ratings yet

- A Compact Wireless Power Transfer System at 915 MHZ With Supercapacitor For Optogenetics Applications - ScienceDirectDocument7 pagesA Compact Wireless Power Transfer System at 915 MHZ With Supercapacitor For Optogenetics Applications - ScienceDirectGeneration GenerationNo ratings yet

- Passive Impedance Matching For Implanted Brain-Electrode InterfacesDocument8 pagesPassive Impedance Matching For Implanted Brain-Electrode InterfacesGeneration GenerationNo ratings yet

- Biology and HealthDocument6 pagesBiology and HealthGeneration GenerationNo ratings yet

- A High Performance Delta-Sigma Modulator For Neurosensing - Sensors-15-19466-1Document2 pagesA High Performance Delta-Sigma Modulator For Neurosensing - Sensors-15-19466-1Generation GenerationNo ratings yet

- A Compact Dual-Band Implantable Antenna For Wireless Biotelemetry in Arteriovenous GraftsDocument1 pageA Compact Dual-Band Implantable Antenna For Wireless Biotelemetry in Arteriovenous GraftsGeneration GenerationNo ratings yet

- A New Wireless-Enabled Audio Processor For Hearing Aids and Cochlear Implants - NewsDocument7 pagesA New Wireless-Enabled Audio Processor For Hearing Aids and Cochlear Implants - NewsGeneration GenerationNo ratings yet

- Research Article Small Triple-Band Meandered PIFA For Brain-Implantable Biotelemetric Systems: Development and Testing in A Liquid PhantomDocument1 pageResearch Article Small Triple-Band Meandered PIFA For Brain-Implantable Biotelemetric Systems: Development and Testing in A Liquid PhantomGeneration GenerationNo ratings yet

- A Brief Review On Implantable Antennas FDocument16 pagesA Brief Review On Implantable Antennas FMai VũNo ratings yet

- A Fully Implantable Wireless ECoG 128-Channel Recording Device For Human Brain-Machine Interfaces W-HERBS - Fnins-12-00511Document11 pagesA Fully Implantable Wireless ECoG 128-Channel Recording Device For Human Brain-Machine Interfaces W-HERBS - Fnins-12-00511Generation GenerationNo ratings yet

- Decoding Raw Frames - Generic - Libre Space CommunityDocument7 pagesDecoding Raw Frames - Generic - Libre Space CommunityGeneration GenerationNo ratings yet

- Encore 29901 Programmer and CareLink 2090 Programmer MedtronicDocument7 pagesEncore 29901 Programmer and CareLink 2090 Programmer MedtronicGeneration GenerationNo ratings yet

- Diffusion Tensor Imaging, Intra-Operative Neurophysiological Monitoring and Small Craniotomy: Results in A Consecutive Series of 103 GliomasDocument11 pagesDiffusion Tensor Imaging, Intra-Operative Neurophysiological Monitoring and Small Craniotomy: Results in A Consecutive Series of 103 GliomasGeneration GenerationNo ratings yet

- Bypassing Software Update Package Encryption - Extracting The Lexmark MC3224i Printer Rmware (Part 1)Document38 pagesBypassing Software Update Package Encryption - Extracting The Lexmark MC3224i Printer Rmware (Part 1)Generation GenerationNo ratings yet

- 802.15.4 Traffic Monitoring (Wireshark) - Troubleshooting - ParticleDocument5 pages802.15.4 Traffic Monitoring (Wireshark) - Troubleshooting - ParticleGeneration GenerationNo ratings yet

- Airborne TrailblazerDocument244 pagesAirborne Trailblazerapi-3819355No ratings yet

- Wing Design ParametersDocument5 pagesWing Design ParametersMakam VenkateshNo ratings yet

- IT Cyber SecurityDocument32 pagesIT Cyber SecurityJamesgalbNo ratings yet

- Thule FitGuide 2019Document74 pagesThule FitGuide 2019Snaps RoadNo ratings yet

- Welding FundamentalsDocument44 pagesWelding FundamentalsDhinasuga DhinakaranNo ratings yet

- 4-H Communications Toolkit 4H1560 PDFDocument179 pages4-H Communications Toolkit 4H1560 PDFMistor Dupois WilliamsNo ratings yet

- Amity University Rajasthan: Amity School of EngineeringDocument15 pagesAmity University Rajasthan: Amity School of EngineeringRewa ShankarNo ratings yet

- New Microsoft Word DocumentDocument6 pagesNew Microsoft Word DocumentAnonymous EUNhdkrUNo ratings yet

- 17.02.SI.0009. Princess Etab Ben Jalawi A'al Saud Villa 1Document2 pages17.02.SI.0009. Princess Etab Ben Jalawi A'al Saud Villa 1Arafat BauntoNo ratings yet

- West Bengal Pollution Control Board ContactDocument18 pagesWest Bengal Pollution Control Board ContactAvik PattanayakNo ratings yet

- E BallDocument22 pagesE BallKanishk YenugulaNo ratings yet

- Frame 3014B / 3024B Winding 6: Shunt Arep/PmgDocument4 pagesFrame 3014B / 3024B Winding 6: Shunt Arep/PmgDaniel SobralNo ratings yet

- Capability Maturity Model (CMM) : Purpose: To Assess and Help Improve Process in Software Development OrganizationsDocument45 pagesCapability Maturity Model (CMM) : Purpose: To Assess and Help Improve Process in Software Development Organizationsbooster6699No ratings yet

- Design and Fabrication of Power Operated Tiller MachineDocument3 pagesDesign and Fabrication of Power Operated Tiller Machinevj balajiNo ratings yet

- Integra Optics XFP Modules For 10 Gigabit Ethernet and Packet-Over-SONET ApplicationsDocument4 pagesIntegra Optics XFP Modules For 10 Gigabit Ethernet and Packet-Over-SONET Applicationsishak8No ratings yet

- Discover ANSTODocument17 pagesDiscover ANSTOowirwojNo ratings yet

- Ad Js Injection - JsDocument2 pagesAd Js Injection - JsWalison SilvaNo ratings yet

- Industrial Control 11)Document33 pagesIndustrial Control 11)Arindam LayekNo ratings yet

- Effect of Mechanical Properties On Multi Axial Forged LM4 Aluminium AlloyDocument6 pagesEffect of Mechanical Properties On Multi Axial Forged LM4 Aluminium AlloySharath P CNo ratings yet

- Uic Code: Harmonised Commodity Code (NHM)Document10 pagesUic Code: Harmonised Commodity Code (NHM)rahatNo ratings yet

- 2004 Viking-Excalibur ManualDocument45 pages2004 Viking-Excalibur ManualjackNo ratings yet

- Different Types of Sensors: Infrared Sensor (IR Sensor)Document7 pagesDifferent Types of Sensors: Infrared Sensor (IR Sensor)Yossry AwadNo ratings yet

- Brittleness IndexDocument3 pagesBrittleness IndexViviRachmawatiNo ratings yet

- Solid Rocket Motor PropulsionDocument63 pagesSolid Rocket Motor Propulsionram narayanNo ratings yet

- Unity Point Phishing ScamDocument1 pageUnity Point Phishing ScamdmronlineNo ratings yet

- O ITP 12 04 012 # 1 - Inspection & Test PlanDocument1 pageO ITP 12 04 012 # 1 - Inspection & Test PlaniuliiulianNo ratings yet

- CV Chandra Salim, M.TDocument4 pagesCV Chandra Salim, M.TChandra SalimNo ratings yet

- PC800SE-7-M1 S/N 40001-UP: Travel Motor (4/4)Document2 pagesPC800SE-7-M1 S/N 40001-UP: Travel Motor (4/4)midalllNo ratings yet

- General Awareness PDFDocument72 pagesGeneral Awareness PDFDildar JahangirNo ratings yet

- Twyford CatalogDocument35 pagesTwyford CatalogCarlos YupanquiNo ratings yet