Professional Documents

Culture Documents

A Low Power Low Noise Chopper-Stabilized Tow-Stage Operational Amplifier For Portable Bio-Potential Acquisition Systems Using 90 NM Technology

Uploaded by

VitaliyGOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

A Low Power Low Noise Chopper-Stabilized Tow-Stage Operational Amplifier For Portable Bio-Potential Acquisition Systems Using 90 NM Technology

Uploaded by

VitaliyGCopyright:

Available Formats

International Journal of Hybrid Information Technology

Vol. 7, No. 6 (2014), pp. 25-42

http://dx.doi.org/10.14257/ijhit.2014.7.6.03

A Low Power Low Noise Chopper-Stabilized Tow-stage Operational

Amplifier for Portable Bio-potential Acquisition Systems Using 90

nm Technology

Fateh Moulahcene1, Nour-Eddine Bouguechal1 and Youcef Belhadji2

1

Advanced Electronics Laboratory (LEA), University of Batna, Avenue Chahid

Boukhlouf, 05000, Batna,Algeria

Micro30.sysfateh@gmail.com

2

Unit of research of materials and renevable energies, faculty of science,

Abou bekr Belkaid University,

PB 119 Tlemcen 13000, Algeria

Abstract

This paper presents a high performance chopper-Stabilized Two-stage operational

amplifier for biomedical applications. This Two-stage is designed for low noise, low power,

high PSRR and high CMRR. The Miller compensation technique (Cc) is used with a nulling

active resistance (Rz) implemented using Transmission gate (TG) transistors for stable

operation in feedback mode. Chopper stabilization technique has been widely used in

amplifiers for flicker (1/f) noise and offsets reduction purposes using the principles of

modulation and demodulation. Thus, the functionality and performance of modulation and

demodulation circuits determines the realization and attainment of chopper stabilization. The

operational amplifier was manufactured in a SPECTRE using GPDK 90nm CMOS

technology with threshold voltages of a 0.17 V and - 0.14 V achieve a low power 2.6uW,

13 . 5 nV / Hz at 10Hz high CMRR up to 130dB and PSRR up to 70dB at 1V power supply.

Keywords: Two-stage amplifier, Miller compensation, Transmission gate, CMRR

(Common mode Rejection Ratio), Modulation, Demodulation, Chopper stabilization

1. Introduction

The trend in the use of low-voltage power supplies for CMOS integrated circuits is by the

reliability issue of small size MOSFET transistors and the increasing use of low-weight long

life battery-operated portable electronic systems [1, 2].

With the rapid development of microelectronics in the recent past years, more and more

applications require an ultra-low amplitude signal measurement module, such as implantable

devices in biomedical application to monitor several Neuro-muscular activities [3-6].

Monitoring biomedical signals of the human body is a very interesting topic since it can be

used to know vital health information of the body from the acquired data. These data

capacitates medical practitioners to diagnose diseases [7, 8].

Biomedical signals, such as electrocardiogram (ECG), Electromyogram (EMG),

Electroencephalogm (EEG), are characterized by their low voltage-levels and low frequency,

Table 1 shows the characteristics of these signals [8 -12].

ISSN: 1738-9968 IJHIT

Copyright ⓒ 2014 SERSC

International Journal of Hybrid Information Technology

Vol. 7, No. 6 (2014)

Table 1. Most Commonly used Biomedical Signals

Signal Frequency Amplitude

ECG 0.05-250 Hz 5 uV-8 mV

EEG 0.5-200 Hz 2 uV-200 uV

EMG 0.01-10 KHz 50 uV-10 mV

A low noise and low power consumption amplifier is one of the key circuits for detecting

the small level signals in the biomedical applications. However, in CMOS technology the 1/f

noise becomes a serious problem which limits the minimum detectable signal in amplifier at

low frequency [13, 14]. The chopping technique is widely used in amplifier for low noise. It

is a modulation and demodulation technique that can be employed to reduce the effect of

operational amplifier imperfections including noise and input referred dc offset voltage [15].

The Famous architecture used in a biomedical monitoring system, are an operational

amplifier, must exhibit very low-referred noise, low power and high Common Mode

Rejection Ratio (CMRR).

In this paper, a low voltage, low noise and high CMRR operational amplifier for portable

monitoring system is proposed. The operational amplifier is able to work under 1-V supply,

has high CMRR and low noise.

2. ECG Data Acquisition System

ECG data acquisition begins with the use of electrodes that attached to body skin. Three

electrodes are used as sensors to detect the heart signals from a human body. Two electrodes

are placed each on the left and right wrist while the third electrode is placed on the ankle of

the leg as ground [16].

The ECG signal that acquired is in the range of 5uV to 8 mV. Due to the weak voltage

level, the signal is fed into an amplifier circuit to be amplified to a desirable voltage level.

Output from the amplifier is then fed into a bandpass filter circuit and a High Q notch filter.

The purpose of this filter is to filter out the very low and high frequency noise components of

the signals and the 60-Hz power line interference. The desirable analog output from the filter

is then sent to S/H and ADC to become a digital signal. After that, these digital data will

processed in PCs or microprocessors. Figure.1 shows the proposed ECG data acquisition

system [7, 16-19].

Digital

Biomedical Output

signal ECG

LowPass Sample –and- Analog-to-Digital

Electrode Amp filter Hold S/H Converter(ADC)

Figure 1. The Proposed ECG Data Acquisition

We have collected data from MIT-BIH Arrhythmia Database [20-22], for training and

testing of proposed ECG amplifier Design. See Figure 2 of the input (VIN) ECG signal.

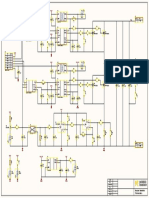

3. ECG Amplifier Design

A normal ECG signal falls in the range of 5uV – 8mV. The amplifier is required to

increase this weak signal into an acceptable level. The main operational amplifier for

26 Copyright ⓒ 2014 SERSC

International Journal of Hybrid Information Technology

Vol. 7, No. 6 (2014)

biomedical applications is illustrated in Figure 3. This Two-stage architecture with miller

compensation capacitor (Cc) and nulling active resistor (Rz), is used for the design of the

operational amplifier with the first stage being a differential input pair and the second, a gain

stage.

Figure 2. ECG Signal from MIT-BIH Arrhythmia Database (Vin(max)=1.5mV)

This Two-stage architecture with miller compensation capacitor (Cc) and nulling active

resistor (Rz), is used for the design of the operational amplifier with the first stage being a

differential input pair and the second, a gain stage. Because the Biomedical signal is so weak,

the noise will affect the real biomedical signal. Due to the low frequency of biomedical signal

the flicker noise dominates, it has strong dependence on the width and length product of a

CMOS transistor. The flicker noise is modeled in Eq (1), the spectral density of flicker noise

is inversely proportional to the transistor area, WL. In other words, 1/f noise can have a lesser

effect on larger devices. However the input pair (M1 and M2) of the input stage has been

designed using large PMOS transistors. A P-channel current source (M5) and an n-channel

current mirror load (M3 and M4) are used in the input stage.

K 1

Vn

2

. (1)

C OX WL f

The second stage of the operational amplifier includes an n-channel common-source

amplifier (M6) with a p-channel current source load (M7).

The high output resistances of these two transistors (M7, M6) equate to a relatively large

gain for this stage and an overall moderate gain for the complete amplifier. Because the

operational amplifier inputs are connected to the gates of MOS transistors, the input

resistance is essentially infinite. The sizes of the transistors were designed for a bias current

of 0.5μA to provide for sufficient output voltage swing, output-offset voltage, slew rate, and

gain-bandwidth product.

3.1. Current Mirrors

Current mirrors are used extensively in MOS analog circuits both as biasing elements and

as active loads to obtain high AC voltage gain [23, 24]. Enhancement mode transistors remain

in saturation when the gate is tied to the drain, as the drain-to source voltage (VDS) is greater

than the gate-to-source voltage (VGS) due to the threshold voltage (Vth) drop, i.e.,

Copyright ⓒ 2014 SERSC 27

International Journal of Hybrid Information Technology

Vol. 7, No. 6 (2014)

V DS V GS V Th (2)

Based on Eq (2), constant current sources are obtained through current mirrors designed by

passing a reference current through a diode-connected (gate tied to drain) transistor. We

choose a simple current mirror because low voltage (1-V), Figures 4(a) and (b) show the

PMOS and NMOS current mirrors design. A PMOS mirror serve as a current source while the

NMOS acts as a current sink.

Figure 3. Schematic of Two-stage Operational Amplifier

The voltage developed across the diode-connected transistor is applied to the gate and the

source of the second transistor, which provides a constant output current. Since both the

transistors have the same gate to source voltage, the currents when both transistors are in the

saturation region of operation, are governed by the following Eq (3) and Eq(4) assuming

matched transistors. The current ratio Iout/Iref is determined by the aspect ratios of the

transistors. The reference current that was used in the design is 0.5μA. The desired output

current is 1μA.

For the PMOS current mirror, we can write,

W7

I OUT

L7 (3)

I REF W8

L8

For the NMOS current mirror, we can write,

W4

I OUT

L4 (4)

I REF W3

L3

28 Copyright ⓒ 2014 SERSC

International Journal of Hybrid Information Technology

Vol. 7, No. 6 (2014)

Figure 4. (a) PMOS Current Mirror, (b) NMOS Current Mirror

3.2. Active Resistors

There are two active resistors used in the design. Firstly, the reference current that is

applied to the current mirror is obtained by means of an active resistor. The resistor here is

obtained by simply connecting the gate of an NMOS (M11) to its drain as shown in Figure 5.

This connection forces the MOSFET to operate in saturation.

Figure 5. Active Resistor

The second active resistor a transmission gate (TG) shown in Figure 7 has been used to

realize the nulling active resistance (Rz) to reduce the effects of the right hand plane zero in

the transfer function. The gate of these transistors M9, M10 is biased at VDD, VSS

respectively. Its small signal output resistance is obtained from Eq (5) and Eq(6) (V ds very

small).

The dynamic range limitations associated with single channel MOS switches can be

avoided with CMOS switch shown in figure 6. Using the CMOS technology, a switch usually

constructed by connecting P-channel and N-channel enhancement mode in parallel as

illustrated.

Copyright ⓒ 2014 SERSC 29

International Journal of Hybrid Information Technology

Vol. 7, No. 6 (2014)

Figure 6. Transmission Gate (TG)

For this configuration, When Q is low; both transistors are off, creating an effective open

circuit. When Q is high both transistors are on, giving a low impedance state. The bulk

potentials of the p-channel and n-channel devices are taken at the highest and lowest

potentials respectively. The primary advantage of the CMOS switch over the single channel

MOS switch is that the dynamic analog-single range in the ON state is greatly increased [24].

1

R ON (5)

W

U n C OX (V GS V Thn )

L

1

R OP (6)

W

U P C OX (V SG V Thp )

L

4. Chopper Stabilization Structure

CMOS technology suffers from a specific type of noise namely flicker noise is

concentrated in low frequency bands. It arises from the channel of the MOS transistor, due to

the imperfect silicon crystal structure at the interface between the gate oxide and the silicon

substrate [13]. Amongst the technique used to reduce the effect of such noise type is chopper

stabilization technique, when compared to other published techniques, chopper stabilization

efficiently reduces the flicker noise in the design of an analog circuit [14]. In Figure 7, we

show the theory of the chopper stabilization structure.

30 Copyright ⓒ 2014 SERSC

International Journal of Hybrid Information Technology

Vol. 7, No. 6 (2014)

Figure 7. Chopper Stabilisation Structure

In Figure 7, the input signal is firstly modulated by the chopping signal with the chopping

frequency Fchop and shifted to odd harmonic of the chopping frequency. And after

amplification it is demodulated to the even harmonics. However, the noise and DC offset

before the amplifier is just modulated once and shifted to the odd harmonics of chopping

frequency. It leaves the thermal noise at the base-band and reduces much of flicker noise.

Figure 8 shows the signal and noise wave at the node of chopper stabilization structure.

Through the chopper stabilization technique, we can reduce the low frequency noise and DC

offset effectively [25].

4.1. Modulation and Demodulation Circuit

Figure 8. Chopping Principal in Frequency Domain

For the switches of modulation and demodulation circuit, the structure of differential

NMOS switch which is shown in figure 9 is used in this design [26, 27] .

The modulator inverts the signal when Q is low and does not invert the signal when Q is

high. The demodulator is identical. However, the modulator and demodulator can be

independently controlled which makes it possible to adjust for phase delay problems

Copyright ⓒ 2014 SERSC 31

International Journal of Hybrid Information Technology

Vol. 7, No. 6 (2014)

The modulator circuit, which is placed before the chopper amplifier, is critical to range of

nonlinearities and noise. Hence for low noise Two-stage operational amplifier applications,

critical attention should be given to the design of the modulator part for better noise and offset

minimization.

Figure 9. Differential NMOS Switch

Clock feed-through and charge injection are the main factors resulting in nonlinearity in

MOS switches .figure 10 shows differential NMOS chopper circuit with half size dummy

switchs incorporation [27-29].

Figure 10. Differential Chopper Circuit with Dummy Switches

5. Simulation and Discussion

The proposed two-stage operational amplifier consists of a differential difference amplifier

and a chopper circuit. The following subsections explain the simulation of each module.

32 Copyright ⓒ 2014 SERSC

International Journal of Hybrid Information Technology

Vol. 7, No. 6 (2014)

5.1. Device Parameter

Table 2 gives the device parameter for a Two-stage operational amplifier.

Table 2. Device Parameter for Two-stage Amplifier

Device Type W(um) L(um)

M1,M2 P 10 0.378

M3,M4 N 18 0.556

M5,M8 P 35 0.460

M7 P 80 0.530

M6 N 15 0.100

M9 N 1 0.100

M10 P 10 0.100

M11 N 3 0.800

5.2. Frequency Response, Compensation

Operational amplifier architectures are generally two types: single-stage externally

compensated or two stage internally compensated amplifiers, both of which can have a

dominant two pole type frequency response [30]. Ignoring higher order poles, the small signal

behavior of the two stage amplifier can be modeled by the general two poles, one zero small

signal equivalent circuit shown in Figure 11. Referring back to the model of the input stage

Figure 3 (Without (Cc) and (Rz)), We have two poles these are Eq (7) and Eq (8)

1

P1 (7)

1

C1

g m3

1

P2 (8)

C 2 ( r 02 r 04 )

The compensation of the two stage CMOS amplifier can be carried out using a pole splitting

capacitor. The goal of the compensation task is to achieve a phase margin greater than 45

degree. The circuit can be approximately represented by the small signal equivalent circuit of

Figure 11 (without Rz), if the non-dominant poles which may exist on the circuit are

neglected.

Figure 11. Simplified Small Signal Model of the Basic Two Stage Op-amp

Added with The Nulling Resistor

Copyright ⓒ 2014 SERSC 33

International Journal of Hybrid Information Technology

Vol. 7, No. 6 (2014)

The circuit displays two poles and a half right plane zero, which under an assumption that

the poles are widely separated can be shown to be approximately located at (Eq (9), Eq (10)

and Eq (11)).

1

P1 (9)

1 g m 2 R 2 C C R 1

g m2C C

P2 (10)

C 2C1 C C C1 C 2C C

g m2

Z (11)

CC

Note that the pole due to the capacitive loading of the first stage by the second, p1, has

been pushed down to a very low frequency by the miller effect in the second stage, while the

pole due to the capacitance at the output node of the second stage p2, has been pushed to a

very high frequency due to the shunt feedback. For this reason, the compensation technique is

called pole splitting.

Physically, the zero arises because the compensation capacitor provides a path for the

signal to propagate directly through the circuit to the output at high frequencies. Since there is

no inversion in that signal path as there is in the inverting path dominant at low frequencies,

stability degraded.

An even simpler approach is to insert an active nulling resistor (Rz) in series with the

compensation capacitor as shown in Figure 4 and Figure 8. If Rz is assumed to be less than R1

or R2 and the poles are widely spaced, then the poles are: (Eq(12),Eq(13),Eq(14) and Eq(15)).

1 1

P1 (12)

(1 g m 2 R 2 ) C C R 1 g m 2C C R1 R 2

g m 2C C g m2

P2 (13)

C 1C 2 C C C 2 C 1C C C2

1

P3 (14)

RZC

1

1

Z (15)

1

CC ( )

g m2 RZ

The resistor RZ= (Ron||Rop) allows independent control over the placement of the zero.

The zero vanishes when RZ is made equal to 1/gm2. In fact, the resistor can be further

increased to move the zero into the left half-plane and place it on top of p2 to improve the

amplifier phase margin. RZ can be realized by a CMOS switch transistor in the triode region.

Using CMOS switch is to increase dynamic range. Where the resistance of CMOS switch

is plotted as a function of the input voltage figure 12, in this figure, the p-channel M10 and n-

channel M9 devices are sized in such a way that they have an equivalent resistance to

identical terminal conditions.

34 Copyright ⓒ 2014 SERSC

International Journal of Hybrid Information Technology

Vol. 7, No. 6 (2014)

The peak behavior at midrange (near VDD/2), is due the parallel combination of the two

devices M9 and M10. In the right n-channel M9 dominating when E is low, and in the left p-

channel M10 dominating when E is high (near VDD).

Figure 13 shows a typical variation of the gain and phase versus frequency, with Cc =0.6

pF, Cp=1 pF.

Figure 12. Rz of Figure 6, as a Function of E

Figure 13. Shows a Typical Variation of the Gain and Phase versus Frequency

5.3. Common Mode Rejection Ratio CMRR

Due to the large amount of 60-Hz human in bio-potential measurements, common-mode

rejection is as important as low-noise operation. CMRR is defined as the ratio of the voltage

gain for a differential-mode input signal to the voltage gain for a common-mode input signal,

and can be stated as [22]. Therefore, measuring the dc CMRR involves determining the

change in the offset voltage due to any change in the applied common-mode voltage. But,

power supply voltage variation may affect the output as well as the offset voltage. In order to

Copyright ⓒ 2014 SERSC 35

International Journal of Hybrid Information Technology

Vol. 7, No. 6 (2014)

ensure that the measured change in the offset voltage is only due to a change in common-

mode input voltage, the output voltage of the Two-stage operational amplifier is maintained at

a fixed voltage for the complete test sequence.

We simulate the complete circuit in single power supply for CMRR. The results of CMRR

are up to 130dB as shown in Figure 14.

Figure 14. Shows a Variation of the CMRR versus Frequency

5.4. Noise

The input stage dominates the noise of the op amp. PMOS devices offer lower flicker noise

which is advantageous in our op amp design. Also, the noise component of the load devices is

scaled by the ratio of their transconductance to that of the input pair devices. So, the

transconductance of the input differential pair needs to be larger than that of the load pair in

order to ensure low input-referred noise. There exists a trade-off between noise and the output

swing of the stage. Generally, the overdrive voltage of the current loads is minimized to

realize a wide output swing, but for a fixed current bias this increases the transconductance

(due to increased W) and thereby results in a larger input-referred noise.

The simulation results of the input referred noise spectrum is depicted in Figure 15, flicker

noise below 100Hz is clearly visible, it achieve input referred noise density of 138 nV Hz

at 10Hz.

36 Copyright ⓒ 2014 SERSC

International Journal of Hybrid Information Technology

Vol. 7, No. 6 (2014)

Figure 15. Simulated Input-refred Noise Spectrum

5.5. Chopper Circuit

The simulation result of the modulator and demodulator circuits in Cadence Virtuoso

Spectre circuit simulator showed that the differential NMOS chopper circuit implantation

exhibit large charge injections and spikes Whereas, the dummy switch incorporated chopper

circuit results in smooth modulated signal output as shown in Figure 16, in Figure 16 is the

output modulator signal with dummy switches and Figure 17 is the output of our operational

amplifier without low pass filter. The chopper clock is chosen to be a 10 KHz square-wave

and the input is 0.5 KHz sinusoidal signal.

Figure 16. Output Modulated Signal

Copyright ⓒ 2014 SERSC 37

International Journal of Hybrid Information Technology

Vol. 7, No. 6 (2014)

Figure 17. Output of Operational Amplifier without Low Pass Filter

Figure 18 indicates the simulation of the input referred noise spectrum with chopper or

without chopper. Compared with non-chopper amplifier with chopper amplifier at 10Hz, the

input referred noise of chopper amplifier is improved significantly, and when we using the

chopper with dummy switch the input referred noise is much better( 13 . 5 nV / Hz ).

Figure 18. Balanced Two-stage Operational Amplifier Frequency Characteristic

Next the length of the transistor was fixed at the constant value of 0.1um and width was

made to vary from 10u up to 50um. According to the recorded results, the width variation

38 Copyright ⓒ 2014 SERSC

International Journal of Hybrid Information Technology

Vol. 7, No. 6 (2014)

resulted in almost a linear response with the total input referred noise figure magnitude, as

shown in figure 19. The wider the transistor used the lower the total input referred noise

contribution. Hence, it is important to set the width of the transistors in the modulator

demodulator circuit by taking in to consideration the current level.

Figure 19. Effect of Transistor Width on Total Input Referred Noise

This a standard two-stage 11-transistor amplifier Figure 3 with miller compensation and

zero-nulling active resistor Rz=(Rn//Rp). All the devices operate in saturation region except

the transistors M9 and M10 operate in the linear region. The input differential stage draws

1uA, while the output stage current is 1.1uA. This results in a total current consumption of

2.1uA plus the current reference Iref=0.5uA , i.e. a 2.6 uW power consumption from single

1V supply.

The overall performance summary of the complete circuit two-stage operational amplifier

for biomedical applications is given in Table 3.

Table 3. Simulation Results of Schematic Two-stage Amplifier

Process 90nm CMOS

Power supply 1V

Power dissipation 2.6uW

CMRR 131 dB

Bandwidth 15.3kHz

PSRR+ 70.7 dB

Ad 55.1 dB

Input offset voltage (Vos) 6.42um

PM 69.46

Input-referred-noise at 10 Hz 13 . 5 nV / Hz

Table 4 shows a performance comparison between the proposed and currently used [13],

[26], [29]. It can be seen that this work achieves the low input referred noise and lowest

Power consumption.

Copyright ⓒ 2014 SERSC 39

International Journal of Hybrid Information Technology

Vol. 7, No. 6 (2014)

Table 4. Performance Comparison between Others Amplifier Circuits

This work Ref.[13] Ref.[26] Ref.[29]

Power supply(V) 1 1.8 3.3 3.3

Technology CMOS (m) 90n 0.35u 0.18u 0.35u

CMRR(dB) 131 120 110 -

Amplifier voltage gain (dB) 48 51 - 124.57

Power consumption (u W) 2.6 775 420 -

Input offset voltage(uV) 6.24 - 0.582 <60

13.5 56 22 312.86

Input referred noise( nV / Hz ) @10Hz

6. Conclusion

In this paper, we present a Two-stage operational amplifier topology for low voltage and

low power, ECG Monitoring System applications, This two-stage amplifier with Miller

compensation can be used in low power, low voltage High CMRR and PSRR applications

such Biomedical instrument and a small battery operated devices. The circuit has been

designed in a SPECTRE using 90nm CMOS technology.

To reduce the noise of the amplifier, we used the P-channel input devices with N-channel

load, because it’s flicker noise is less than that the N-channel input devices with P-channel

load.

We have described an ECG amplifier with low input-referred noise, 131-dB CMRR, less

than 3uW of power consumption, and good cardiac signal fidelity.

Proposed two-stage operational amplifier with Miller compensation (Cc) and nulling active

resistor (Rz), is well suited to biomedical systems such as cardiac pacemaker,

electrocardiogram (ECG) where low-power consumption is of primary concern.

using the chopper technique improve the input-referred-noise, even if we used the

differential NMOS with dummy switches , there is a problem of spikes causing by clock feed-

through and charge injection, we can reducing these spikes by using another type of switch

like , CMOS Transmission gate with dummy switches or we use other techniques.

References

[1] T. H. Ning, P. W. Cook, R. H. Dennard, C. M. Osburn, S. E. Schuster, and H. N. Yu, “1um MOSFET VLSI

technology, Part IV-Hot-electron design constraints”, IEEE Trans.Electron.Devices, vol. 26,(1979), pp. 346-

353.

[2] M. F. Li, Uday Dasgupta, X. W. Zhang, and Yong Ching Lim, “A low-Voltage CMOS OTA with Rail-to-

Rail Differential Input Range”, IEEE Transactions on circuits and systems, vol. 47, (2000) January, pp.1-8.

[3] M. Swan, K. Arabi and B. Provost, “Implantable volume monitor and miniaturized simulator dedicated to

bladder control”, Artificial Organs, vol. 21, no. 3, (1997), pp. 219-222.

[4] R. Stein, B. Charles, D. Davis, L. Jhamandas, J. A. Mannard, And T. R. Nichols, “Principles underlying new

methods for chronic neural recording”, Can. J. Of Neuro.SCI., (1975) August, pp. 235-244.

[5] D. Popovic, B. Stein, R. B. Jovanovic, K. L. Dai, A. R. Kostovand, and W.W. Armstrong, “Sensory nerve

recording for closed-loop control to restore motor function”, IEEE Trans. Biomed.Eng., vol. 40, no. 10,

(1993) October, pp. 1024-1031.

[6] Y. Hu and M. Sawan, “CMOS Front-end Amplifier Dedicated to Monitor Very low Amplitude Signal from

Imlantable Sensors”, Kluwer Academic Publishers. Manufactured in the Netherlands, vol. 33, (2002), pp. 29-

41.

[7] W.-S. Wang, Z.-C. Wu, H.-T. Huang and C.-H. Luo, “Low Power Instrumental Amplifier for Portable ECG”,

IEEE Circuits and Systems International Conference, (2009) April, pp. 1-4.

[8] C.-T. Ma, P.-I. Mak, M.-I Vai, P.-u. Mak, S.-H. Pun, W. Feng and R. P. Martins, “A 90nm CMOS Bio-

Potential Signal Readout Front-End with Improved Powerline Interference Rejection”, IEEECircuits and

Systems, (2009) 24-27 May, pp. 665-668.

40 Copyright ⓒ 2014 SERSC

International Journal of Hybrid Information Technology

Vol. 7, No. 6 (2014)

[9] C.-C. Huang, S.-H. Hung and J.-F. Chung, “Front-End Amplifier of low-Noise and Tunable B/W Gain for

Portable Biomedical Signal Acquidition”, IEEE Circuits and Systems, (2008) May, pp. 2717 – 2720.

[10] D. Yates, E. Lopez-Morillo and R. G. Carvajal, “A Low-Voltage Low-Power Front-End for wearable EEG

Systems”, conference of the IEEE EMBS, (2007) August.

[11] L. Lentola, A. Mozzi, A. Neviani and A. Baschirotto, “A 1uA Front-End for Pacemaker Atrial Sensing

Channels”, IEEE, (2009) September.

[12] C. Bronskowski and D. Schroeder, “An ultra-low–noise CMOS Operational Amplifier with programmable

Noise-Power Trade-off ”, IEEE Solid-State Circuits Conference,(2006) September , pp. 368 – 371

[13] Y. Hu and M. Sawan, “CMOS front-end amplifier dedicated to monitor very low amplitude signal from

implantable sensors.” Analog Int. Circ. Signal Proc, (2002) October, vol. 33, pp. 29–41,

[14] N. Ahmed and N. Hesham, “A low Power low noise Capacitively Coupled Chopper Instrumentation

Amplifier in 134 nm CMOS for Portable Biopotential Acquisition Systems”, IEEE, (2013).

[15] L. Zhang and L. He, ‘’system design of o low noise, low offset instrumentation amplifier with chopper

stabilization’’ IEEE, 7th International Conference, (2007) October 22-25, pp. 627-630. .

[16] J. G. Webster, “Medical instrumentation: Application and design”, 3rd ed, John Wiley & sons Inc., (1998).

[17] H.-C. Chow and B.-S. Tang, “A high Performance Current-mode Instrumentation Amplifier for Biomedical

applications”, 2nd International Conference on Signal Processing Systems, (2010) July, pp. V2-64 - V2-67.

[18] C. Ken and L. Xiaoying, “A Zigbee Based Mesh Network for ECG Monitoring System”, Bioinformatics and

Biomedical Engineering (iCBBE), (2010) June, pp. 1-4.

[19] Y. F. Low, I. B. Mustaffa, N. B. Mohd Saad and A. H. Bin Hamidon, “Development of PC-Based ECG

Monitoring System”, IEEE Research and Development, 4th Student Conference , (2006) June, pp. 66-69.

[20] PhysioBank, physiologic signal archives for biomedical research [Online]. Available:

http://www.physionet.org/physiobank/

[21] The MIT-BIH Arrhythmia Database [Online]. Available: http:// physionet.org/physiobank/database/mitdb/

[22] The MIT-BIH Compression Test Database [Online]. Available: http://

www.physionet.org/physiobank/database/cdb/

[23] R. L. Geiger, P. E. Allen and N. R. Strader, “VLSI Design Techniques for Analog and Digital Circuits”,

McGraw-Hill, (1990).

[24] P. E. Allen and D. R Holberg, “CMOS Analog Circuit Design”, Second Edition, Oxford University Press,

(2002).

[25] R. Wo, “Precision Instrumentation amplifiers and read-out IC for sensor Interfacing”, Delft, 12 December

(2012).

[26] A. Voulkidou and S. Siskos, “A Low Noise Low Offset Current Mode Instrumentation Amplifier”, MIXDES

2012, 19th International Conference "Mixed Design of Integrated Circuits and Systems", (2012), May 24-26,

Warsaw, Poland.

[27] N. Y. Sutri and J. O. Dennis, “Low-Noise, Low-offset Modulator Demodulator Circuit for Chopper

Stabilization Technique in CMOS-MEMS Sensor Applications”, IEEE, (2014), June, pp. 1-5.

[28] J. Nebhen, S. Meillère and M. Masmoudi, “A 250 μW 0.194 nV/rtHz Chopper-Stabilized Instrumentation

Amplifier for MEMS Gas Sensor”, IEEE, International Conference on Design & Technology of Integrated

Systems in Nanoscale Era, (2012), 16-18 May, pp. 1-5.

[29] Q. Fu and X. Yan, “Analysis and Design od Instrumentation amplifier Based On Chopper Technology”, IEEE

Laser Physics and Laser Technologies (RCSLPLT), (2010) July 28, pp. 318 – 321.

[30] E. J. Kennedy, “Operational Amplifier Circuits, Theory and Applications”, Holt, Rinehart and Winston, Inc,

New York, (1988).

Copyright ⓒ 2014 SERSC 41

International Journal of Hybrid Information Technology

Vol. 7, No. 6 (2014)

42 Copyright ⓒ 2014 SERSC

You might also like

- Design of CMOS Based Biosensor OTA 2018Document10 pagesDesign of CMOS Based Biosensor OTA 2018RajeeNo ratings yet

- A Study On An EMG Sensor With High Gain and Low Noise For Measuring Human Muscular Movement Patterns For Smart HealthcareDocument11 pagesA Study On An EMG Sensor With High Gain and Low Noise For Measuring Human Muscular Movement Patterns For Smart HealthcareRoker boyNo ratings yet

- A Cmos Instrumentation Amplifier With 90-Db CMRR at 2-Mhz Using Capacitive Neutralization: Analysis, Design Considerations, and ImplementationDocument12 pagesA Cmos Instrumentation Amplifier With 90-Db CMRR at 2-Mhz Using Capacitive Neutralization: Analysis, Design Considerations, and ImplementationKaitoNo ratings yet

- Design of Low-Power High-Gain Operational Amplifier For Bio-Medical ApplicationsDocument6 pagesDesign of Low-Power High-Gain Operational Amplifier For Bio-Medical ApplicationsAFSAL ANo ratings yet

- 2session 27 Overview: Biomedical CircuitsDocument26 pages2session 27 Overview: Biomedical CircuitsGiang HoaiNo ratings yet

- Conference Proceeding NTAFM 2013Document3 pagesConference Proceeding NTAFM 2013atifthestarNo ratings yet

- Isscc 2019 / Session 22 / Physiological Monitoring / 22.1Document3 pagesIsscc 2019 / Session 22 / Physiological Monitoring / 22.1郭圳龍No ratings yet

- A Low Power Bioimpedance Module For Wearable Systems: SciencedirectDocument4 pagesA Low Power Bioimpedance Module For Wearable Systems: SciencedirectDmitriyNo ratings yet

- A Biomedical Sensor Interface With A Sinc Filter andDocument11 pagesA Biomedical Sensor Interface With A Sinc Filter andabishusNo ratings yet

- 2015-BIOCAS-A 64-Channel Ultra-Low Power Bioelectric Signal Acquisition System For Brain-Computer InterfaceDocument4 pages2015-BIOCAS-A 64-Channel Ultra-Low Power Bioelectric Signal Acquisition System For Brain-Computer InterfaceLuật TrầnNo ratings yet

- C. Damian, C. Zet, I. Enculescu, R. Spohr: Virtual PotentiostatDocument5 pagesC. Damian, C. Zet, I. Enculescu, R. Spohr: Virtual Potentiostatnajam696No ratings yet

- Ijatcse18692202020200511 64048 Alnur7 With Cover Page v2Document7 pagesIjatcse18692202020200511 64048 Alnur7 With Cover Page v2YasmenNo ratings yet

- bpw34 AvrDocument4 pagesbpw34 AvrNedim Avicena AlićNo ratings yet

- IJEDR1502089Document7 pagesIJEDR1502089Rizwan Shaik PeerlaNo ratings yet

- Design of A High Gain, Temperature Compensated Biomedical Instrumentation Amplifier For EEG ApplicationsDocument5 pagesDesign of A High Gain, Temperature Compensated Biomedical Instrumentation Amplifier For EEG ApplicationsAhmad AbunassarNo ratings yet

- A Low-Power Sensor Read-Out Circuit With FSK Telemetry For Inductively-Powered Implant SystemDocument4 pagesA Low-Power Sensor Read-Out Circuit With FSK Telemetry For Inductively-Powered Implant SystemSreelal SreedharanNo ratings yet

- Performance Analysis of A Driver Cricuit and An Input Amplifier For BCCDocument8 pagesPerformance Analysis of A Driver Cricuit and An Input Amplifier For BCCAJER JOURNALNo ratings yet

- Design of A Intellectualized Ultrasonic Generator: Xiyang Liu, Xiaodong Cui, Fuhua MaDocument5 pagesDesign of A Intellectualized Ultrasonic Generator: Xiyang Liu, Xiaodong Cui, Fuhua MaEd Gar YundaNo ratings yet

- Fiber_Optics_Communication_EnDocument50 pagesFiber_Optics_Communication_EnMinh Đức Phạm TrầnNo ratings yet

- Slyt416 Ecg EegDocument18 pagesSlyt416 Ecg EegsakthyinNo ratings yet

- ISSN 1392-1215 Pulse Sensor of Physiological Parameter Monitoring System 2007 V78 P 67-70Document4 pagesISSN 1392-1215 Pulse Sensor of Physiological Parameter Monitoring System 2007 V78 P 67-70Himanshu DixitNo ratings yet

- Glucose LevelDocument6 pagesGlucose LevelHakan SayilganNo ratings yet

- Design of A PC-Based Electrocardiogram (ECG) Recorder As - Internet ApplianceDocument29 pagesDesign of A PC-Based Electrocardiogram (ECG) Recorder As - Internet ApplianceSankar PadmanabhanNo ratings yet

- TOMOGRAFO Design OF SENSOR ELECTRONICS FOR CACPACITANCE TOMOGRAPHY PDFDocument6 pagesTOMOGRAFO Design OF SENSOR ELECTRONICS FOR CACPACITANCE TOMOGRAPHY PDFVictor Jose BriceñoNo ratings yet

- A 2.2 W, Current Sensing Readout Interface IC With Injection-Locking Clock GenerationDocument10 pagesA 2.2 W, Current Sensing Readout Interface IC With Injection-Locking Clock GenerationMa SeenivasanNo ratings yet

- AIC Term Project TemplateDocument3 pagesAIC Term Project TemplateFarabi GulandazNo ratings yet

- GSM HarvesterDocument17 pagesGSM HarvesterSarah HeadNo ratings yet

- 128122-Accelerometer & VelomitorTransducerOperationDocument22 pages128122-Accelerometer & VelomitorTransducerOperationNorman MoralesNo ratings yet

- Design and Construction The Low Cost Defibrillator AnalyzerDocument4 pagesDesign and Construction The Low Cost Defibrillator AnalyzerEmilio CánepaNo ratings yet

- Nuclear Instruments and Methods in Physics Research BDocument4 pagesNuclear Instruments and Methods in Physics Research BguiburNo ratings yet

- Polystim Neurotechnologies Laboratory Department of Electrical Engineering, École Polytechnique de Montréal, Canada Benoit - Gosselin@Polymtl - CaDocument4 pagesPolystim Neurotechnologies Laboratory Department of Electrical Engineering, École Polytechnique de Montréal, Canada Benoit - Gosselin@Polymtl - CaAlex WongNo ratings yet

- Remake LCR Meter - Elektor Magazine PDFDocument12 pagesRemake LCR Meter - Elektor Magazine PDFMiguel ClementeNo ratings yet

- Analog Communication Lab ManualDocument30 pagesAnalog Communication Lab ManualANIRUDDHA PAULNo ratings yet

- A Low-Noise Chopper Amplifier Designed For Multi-Channel Neural Signal AcquisitionDocument11 pagesA Low-Noise Chopper Amplifier Designed For Multi-Channel Neural Signal AcquisitionRajeeNo ratings yet

- A 0.5V 9.26µW 15.28mΩ√Hz Bio-Impedance Sensor IC with 0.55° Overall Phase ErrorDocument3 pagesA 0.5V 9.26µW 15.28mΩ√Hz Bio-Impedance Sensor IC with 0.55° Overall Phase ErrorJack GengNo ratings yet

- ECG Com LaunchPadDocument14 pagesECG Com LaunchPadFrancisco FambriniNo ratings yet

- Mkm1133 Instrumentation and Control SystemDocument19 pagesMkm1133 Instrumentation and Control SystemNurul Nadia Mohd ZawawiNo ratings yet

- L P 16-C D S F B - M A: OW Ower Hannel ATA Elector OR IO Edical PplicationsDocument8 pagesL P 16-C D S F B - M A: OW Ower Hannel ATA Elector OR IO Edical PplicationsAnonymous e4UpOQEPNo ratings yet

- A Low Power OTA For Biomedical ApplicationsDocument5 pagesA Low Power OTA For Biomedical ApplicationsCyberJournals MultidisciplinaryNo ratings yet

- Imaging The Heart With Ultrasound: Zili YuDocument28 pagesImaging The Heart With Ultrasound: Zili YuAshwin BhatNo ratings yet

- Universal Application-Specific Integrated Circuit For Bioelectric Data AcquisitionDocument7 pagesUniversal Application-Specific Integrated Circuit For Bioelectric Data AcquisitionSohei LaNo ratings yet

- 5716 4791 1 PB PDFDocument8 pages5716 4791 1 PB PDFJunika Purnama ZulkifliNo ratings yet

- Data Collection System of EEG Based On USB InterfaceDocument4 pagesData Collection System of EEG Based On USB InterfaceAdonis LealNo ratings yet

- Design of A Voltammetry Potentiostat For Biochemical SensorsDocument7 pagesDesign of A Voltammetry Potentiostat For Biochemical SensorsJoão CostaNo ratings yet

- Minimization of Total Harmonic Distortion Using Pulse Width TechniqueDocument12 pagesMinimization of Total Harmonic Distortion Using Pulse Width TechniqueIOSRjournalNo ratings yet

- A MEMS Based Microelectrode Sensor With Integrated Signal Processing CircuitryDocument4 pagesA MEMS Based Microelectrode Sensor With Integrated Signal Processing CircuitrySrivardhan ReddyNo ratings yet

- Comparative Study of Howland CurrentDocument8 pagesComparative Study of Howland CurrentSteve GutierrezNo ratings yet

- An Ultra-Low Power ISM-band Integer-N Frequency Synthesizer Dedicated To Implantable Medical MicrosystemsDocument10 pagesAn Ultra-Low Power ISM-band Integer-N Frequency Synthesizer Dedicated To Implantable Medical MicrosystemsJakrawat BudNo ratings yet

- JSSC 2011 2143610Document10 pagesJSSC 2011 2143610Rizwan Shaik PeerlaNo ratings yet

- Analysis and Design of High Speed Low Power Comparator in ADCDocument6 pagesAnalysis and Design of High Speed Low Power Comparator in ADCNoReply ProgramNo ratings yet

- Ijcse15 07 02 100Document7 pagesIjcse15 07 02 100Shouvik Dutta RoyNo ratings yet

- Enhancement of Mobile Tele-Health System Via GSMDocument5 pagesEnhancement of Mobile Tele-Health System Via GSMarunnehru_aucseNo ratings yet

- Micro Resistance Tester Based On AC Constant Current ExcitationDocument6 pagesMicro Resistance Tester Based On AC Constant Current ExcitationFor GosNo ratings yet

- Low Power Portable Solar Based ECG SystemDocument3 pagesLow Power Portable Solar Based ECG SystemInternational Journal of Innovative Science and Research TechnologyNo ratings yet

- 2007-A Low-Noise Preamplifier With Adjustable Gain and Bandwidth For Biopotential Recording ApplicationsDocument4 pages2007-A Low-Noise Preamplifier With Adjustable Gain and Bandwidth For Biopotential Recording ApplicationsLuật TrầnNo ratings yet

- Edn Design Ideas IIIDocument5 pagesEdn Design Ideas IIIagmnm1962100% (2)

- In-Depth Analysis of Cardiac Signals Using Novel Equipment and SoftwareDocument6 pagesIn-Depth Analysis of Cardiac Signals Using Novel Equipment and SoftwareHoracio DorantesNo ratings yet

- Simulation and Analysis of 5th Order Butterworth Filter for ECG DetectionDocument8 pagesSimulation and Analysis of 5th Order Butterworth Filter for ECG DetectionKarima Ben salahNo ratings yet

- ENG DS 1-1773870-7 Filter-Connector 0616Document74 pagesENG DS 1-1773870-7 Filter-Connector 0616VitaliyGNo ratings yet

- En CD00246267Document713 pagesEn CD00246267Laza UrosevicNo ratings yet

- Understanding Boost Power StagesDocument32 pagesUnderstanding Boost Power StagesphanioletyNo ratings yet

- Datasheet - Live: The Fastest MIL-DTL-38999 Series III Filter ConnectorDocument8 pagesDatasheet - Live: The Fastest MIL-DTL-38999 Series III Filter ConnectorVitaliyGNo ratings yet

- Schematic Half-Bridge ModuleDocument1 pageSchematic Half-Bridge ModuleVitaliyGNo ratings yet

- BuckDocument36 pagesBuckBatuhan IzmırlıNo ratings yet

- MC13783 Buck and Boost Inductor Sizing: Application NoteDocument8 pagesMC13783 Buck and Boost Inductor Sizing: Application NoteVitaliyGNo ratings yet

- AN-10 Design Procedure For Microprocessor Buck RegulatorsDocument13 pagesAN-10 Design Procedure For Microprocessor Buck RegulatorsVitaliyGNo ratings yet

- Slva 477 BDocument8 pagesSlva 477 BAnonymous QakmLc3kTINo ratings yet

- Tez 1Document97 pagesTez 1zekiye-sozmen-erdem-9389No ratings yet

- Application Note AN-1214: LED Buck Converter Design Using The IRS2505LDocument16 pagesApplication Note AN-1214: LED Buck Converter Design Using The IRS2505LVitaliyGNo ratings yet

- An842 - Mathcad Calculates Input Capacitor For Step-Down Buck RegulatorDocument5 pagesAn842 - Mathcad Calculates Input Capacitor For Step-Down Buck RegulatorVitaliyGNo ratings yet

- A Cost Effective Solar Charge Controller and Load Driver For DC Home AppliancesDocument9 pagesA Cost Effective Solar Charge Controller and Load Driver For DC Home AppliancesIOSRjournalNo ratings yet

- Modeling of Grid-Connected With Permanent Magnet Synchronous Generator (PMSG) Using Voltage Vector ControlDocument11 pagesModeling of Grid-Connected With Permanent Magnet Synchronous Generator (PMSG) Using Voltage Vector ControlAhmed RazaNo ratings yet

- 003 PDFDocument37 pages003 PDFVitaliyGNo ratings yet

- A 1 V Low-Noise CMOS Amplifier Using Autozeroing and Chopper Stabilization TechniqueDocument6 pagesA 1 V Low-Noise CMOS Amplifier Using Autozeroing and Chopper Stabilization TechniqueVitaliyGNo ratings yet

- Sciencedirect: A B C A B CDocument9 pagesSciencedirect: A B C A B CVitaliyGNo ratings yet

- 01177a PDFDocument14 pages01177a PDFVitaliyGNo ratings yet

- Comparison ARP4754 and ARP4754ADocument7 pagesComparison ARP4754 and ARP4754AVgfdfsdf FasdfasdfNo ratings yet

- A Different Approach On Pythagorean Triangle, Which SatisfiesDocument4 pagesA Different Approach On Pythagorean Triangle, Which SatisfiesVitaliyGNo ratings yet

- GNU/Linux and FPGA in Real-Time Control Applications: Pavel Pisa Pisa@cmp - Felk.cvut - CZ CC By-SaDocument44 pagesGNU/Linux and FPGA in Real-Time Control Applications: Pavel Pisa Pisa@cmp - Felk.cvut - CZ CC By-SaVitaliyGNo ratings yet

- GP Zone-2 SWAP Project Technical Site Survey ReportDocument3 pagesGP Zone-2 SWAP Project Technical Site Survey Reportmeem akterNo ratings yet

- A Ku Band Circularly Polarized 2x2 Microstrip Antenna Array For Remote Sensing ApplicationsDocument2 pagesA Ku Band Circularly Polarized 2x2 Microstrip Antenna Array For Remote Sensing ApplicationsChristopher ChrisNo ratings yet

- DLD Notes SummaryDocument7 pagesDLD Notes SummaryProgrammer Beats (KalimUllahkhan)No ratings yet

- Harman/Kardon HK-595 User's GuideDocument18 pagesHarman/Kardon HK-595 User's GuideWayne LundNo ratings yet

- First Summative Test in CSS 1Document3 pagesFirst Summative Test in CSS 1Ricky Rom MonteNo ratings yet

- Cea 708 BDocument107 pagesCea 708 Bplasmondofo100% (1)

- Quidway AR 18 - 1X Series Routers Installation - ManualDocument86 pagesQuidway AR 18 - 1X Series Routers Installation - ManualCarmen Rosa LopezNo ratings yet

- Pap2 DatasheetDocument2 pagesPap2 Datasheetabdu_ihsanNo ratings yet

- 3 Band Car Audio Processor: FeaturesDocument29 pages3 Band Car Audio Processor: FeaturesRudy ArmannNo ratings yet

- Laboratory Exercise 10: An Enhanced ProcessorDocument6 pagesLaboratory Exercise 10: An Enhanced ProcessorRyan ReasNo ratings yet

- Schem, MLB, PB15"Document40 pagesSchem, MLB, PB15"Jose ValentimNo ratings yet

- Iot Platform For Home AutomationDocument118 pagesIot Platform For Home Automationيوسف الدرسيNo ratings yet

- C2002947 Thytronic PRON NA 21 IEC 103 Attestation of Conformity 22 02 25056091f2Document1 pageC2002947 Thytronic PRON NA 21 IEC 103 Attestation of Conformity 22 02 25056091f2İsmail Okuyan (ORION)No ratings yet

- 58 - Sony boombox bridges portable and home audioDocument2 pages58 - Sony boombox bridges portable and home audioCrispin Jr. SisonNo ratings yet

- CNCC Question Bank MRM 2K22Document7 pagesCNCC Question Bank MRM 2K22Dayana dossNo ratings yet

- Lecture#3Document17 pagesLecture#3nomi ghousNo ratings yet

- Bank Security System: Protect Customer Data with Network SecurityDocument19 pagesBank Security System: Protect Customer Data with Network SecurityApex ishu100% (1)

- Multi Media Project GuidelinesDocument2 pagesMulti Media Project GuidelinesAngelica AlejandroNo ratings yet

- Difference Between NGN and Legacy TDM NetworkDocument18 pagesDifference Between NGN and Legacy TDM Networkweb1_webteam50% (2)

- Motion Sensors Data SheetDocument2 pagesMotion Sensors Data SheetWín Bolotano De GuzmanNo ratings yet

- FRA4 PicoscopeDocument3 pagesFRA4 Picoscopeeng.fabio.griloNo ratings yet

- Fm4000 Operators Manual ADocument84 pagesFm4000 Operators Manual Ahugo delacruzNo ratings yet

- Communications & Power Industries TriodeDocument2 pagesCommunications & Power Industries TriodeathinabebaNo ratings yet

- Ul E486184 Nraq7 All Dec2021Document10 pagesUl E486184 Nraq7 All Dec2021Choirul anwar RomadhonNo ratings yet

- 2SB1132 BluerocketelectronicsDocument6 pages2SB1132 BluerocketelectronicsAno InkNo ratings yet

- HP PageWide Enterprise Color 556 and HP PageWide Enterprise Color MFP 586Document77 pagesHP PageWide Enterprise Color 556 and HP PageWide Enterprise Color MFP 586Alves Carvalho100% (1)

- Magellan Mg5000Document48 pagesMagellan Mg5000Everest HimalaiaNo ratings yet

- TSM 94 - TSM 94 B - Digital Remote Display PanelDocument3 pagesTSM 94 - TSM 94 B - Digital Remote Display Panelluat1983No ratings yet

- Marconi OMS 1200 DatasheetDocument4 pagesMarconi OMS 1200 DatasheethamidNo ratings yet

- Microsoft Azure Infrastructure Services for Architects: Designing Cloud SolutionsFrom EverandMicrosoft Azure Infrastructure Services for Architects: Designing Cloud SolutionsNo ratings yet

- AWS Certified Cloud Practitioner Study Guide: CLF-C01 ExamFrom EverandAWS Certified Cloud Practitioner Study Guide: CLF-C01 ExamRating: 5 out of 5 stars5/5 (1)

- Computer Systems and Networking Guide: A Complete Guide to the Basic Concepts in Computer Systems, Networking, IP Subnetting and Network SecurityFrom EverandComputer Systems and Networking Guide: A Complete Guide to the Basic Concepts in Computer Systems, Networking, IP Subnetting and Network SecurityRating: 4.5 out of 5 stars4.5/5 (13)

- CCNA: 3 in 1- Beginner's Guide+ Tips on Taking the Exam+ Simple and Effective Strategies to Learn About CCNA (Cisco Certified Network Associate) Routing And Switching CertificationFrom EverandCCNA: 3 in 1- Beginner's Guide+ Tips on Taking the Exam+ Simple and Effective Strategies to Learn About CCNA (Cisco Certified Network Associate) Routing And Switching CertificationNo ratings yet

- ITIL 4: Digital and IT strategy: Reference and study guideFrom EverandITIL 4: Digital and IT strategy: Reference and study guideRating: 5 out of 5 stars5/5 (1)

- The Compete Ccna 200-301 Study Guide: Network Engineering EditionFrom EverandThe Compete Ccna 200-301 Study Guide: Network Engineering EditionRating: 5 out of 5 stars5/5 (4)

- Amazon Web Services (AWS) Interview Questions and AnswersFrom EverandAmazon Web Services (AWS) Interview Questions and AnswersRating: 4.5 out of 5 stars4.5/5 (3)

- The CompTIA Network+ Computing Technology Industry Association Certification N10-008 Study Guide: Hi-Tech Edition: Proven Methods to Pass the Exam with Confidence - Practice Test with AnswersFrom EverandThe CompTIA Network+ Computing Technology Industry Association Certification N10-008 Study Guide: Hi-Tech Edition: Proven Methods to Pass the Exam with Confidence - Practice Test with AnswersNo ratings yet

- The Ultimate Kali Linux Book - Second Edition: Perform advanced penetration testing using Nmap, Metasploit, Aircrack-ng, and EmpireFrom EverandThe Ultimate Kali Linux Book - Second Edition: Perform advanced penetration testing using Nmap, Metasploit, Aircrack-ng, and EmpireNo ratings yet

- Computer Networking: The Complete Beginner's Guide to Learning the Basics of Network Security, Computer Architecture, Wireless Technology and Communications Systems (Including Cisco, CCENT, and CCNA)From EverandComputer Networking: The Complete Beginner's Guide to Learning the Basics of Network Security, Computer Architecture, Wireless Technology and Communications Systems (Including Cisco, CCENT, and CCNA)Rating: 4 out of 5 stars4/5 (4)

- Evaluation of Some Websites that Offer Virtual Phone Numbers for SMS Reception and Websites to Obtain Virtual Debit/Credit Cards for Online Accounts VerificationsFrom EverandEvaluation of Some Websites that Offer Virtual Phone Numbers for SMS Reception and Websites to Obtain Virtual Debit/Credit Cards for Online Accounts VerificationsRating: 5 out of 5 stars5/5 (1)

- Computer Networking: The Complete Guide to Understanding Wireless Technology, Network Security, Computer Architecture and Communications Systems (Including Cisco, CCNA and CCENT)From EverandComputer Networking: The Complete Guide to Understanding Wireless Technology, Network Security, Computer Architecture and Communications Systems (Including Cisco, CCNA and CCENT)No ratings yet

- Designing and Building Security Operations CenterFrom EverandDesigning and Building Security Operations CenterRating: 3 out of 5 stars3/5 (3)

- ITIL® 4 Direct, Plan and Improve (DPI): Your companion to the ITIL 4 Managing Professional and Strategic Leader DPI certificationFrom EverandITIL® 4 Direct, Plan and Improve (DPI): Your companion to the ITIL 4 Managing Professional and Strategic Leader DPI certificationNo ratings yet

- Introduction to Cyber-Warfare: A Multidisciplinary ApproachFrom EverandIntroduction to Cyber-Warfare: A Multidisciplinary ApproachRating: 4.5 out of 5 stars4.5/5 (3)

- AWS Certified Solutions Architect Study Guide: Associate SAA-C02 ExamFrom EverandAWS Certified Solutions Architect Study Guide: Associate SAA-C02 ExamNo ratings yet

- ITIL® 4 Create, Deliver and Support (CDS): Your companion to the ITIL 4 Managing Professional CDS certificationFrom EverandITIL® 4 Create, Deliver and Support (CDS): Your companion to the ITIL 4 Managing Professional CDS certificationRating: 5 out of 5 stars5/5 (2)

- Advanced Antenna Systems for 5G Network Deployments: Bridging the Gap Between Theory and PracticeFrom EverandAdvanced Antenna Systems for 5G Network Deployments: Bridging the Gap Between Theory and PracticeRating: 5 out of 5 stars5/5 (1)