Professional Documents

Culture Documents

Rohini 49230243100

Uploaded by

Jpradha KamalOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Rohini 49230243100

Uploaded by

Jpradha KamalCopyright:

Available Formats

ROHINI COLLEGE OF ENGINEERING AND TECHNOLOGY

Static latches

A latch is an essential component in the construction of an edge-triggered

register. It is level-sensitive circuit that passes the D input to the Q output when

the clock signal is high. This latch is said to be in transparent mode. When the

clock is low, the input data sampled on the falling edge of the clock is held stable

at the output for the entire phase, and the latch is in hold mode. A latch operating

under the above conditions is a positive latch.

Static Latches Principle:

Static memories use positive feedback to create a bistable circuit — a

circuit having two stable states that represent 0 and 1. The basic idea is shown in

below figure which shows two inverters connected in cae along with a voltage-

transfer characteristic typical of such a circuit. Also plotted are the VTCs of the

first inverter, that is,V o1 versus Vi1, and the second inverter (Vo2 versus Vo1).

Fig 3.2.1: Example of H-tree clock distribution

[Source : Jan M. Rabaey ,Anantha Chandrakasan, Borivoje. Nikolic, ‖Digital Integrated

Circuits:A Design perspective …]

The latter plot is rotated to accentuate thatVi2 = Vo1. Assume now that the

EC 8095 VLSI DESIGN

ROHINI COLLEGE OF ENGINEERING AND TECHNOLOGY

output of the second inverter Vo2 is connected to the input of the first Vi1, as

shown by the dotted lines in Figure 7.4a. The resulting circuit has only three

possible operation points (A, B, and C), as demonstrated on the combined VTC.

Multiplexer Based Latches

There are many approaches for constructing latches. One very common

technique involves the use of transmission gate multiplexers. Multiplexer based

latches can provide similar functionality to the SR latch, but has the important

added advantage that the sizing of devices only affects performance and is not

critical to the functionality. Figure 7.11 shows an implementation of static

positive and negative latches based on multiplexers.

For a negative latch, when the clock signal is low, the input 0 of the

multiplexer is selected, and the D input is passed to the output. When the clock

signal is high, the input 1 of the multiplexer, which connects to the output of the

latch, is selected. The feedback holds the output stable while the clock signal is

high. Similarly in the positive latch, the D input is selected when clock is high,

and the output is held (using feedback) when clock is low.

Fig 3.2.2: Negative and Positive latches based on multiplexer

[Source : Jan M. Rabaey ,Anantha Chandrakasan, Borivoje. Nikolic, ‖Digital Integrated

Circuits:A Design perspective …]

EC 8095 VLSI DESIGN

ROHINI COLLEGE OF ENGINEERING AND TECHNOLOGY

A transistor level implementation of a positive latch based on multiplexers

is shown in figure. When CLK is high, the bottom transmission gate ison and the

latch is transparent - that is, the D input is copied to the Q output. During this

phase, the feedback loop is open since the top transmission gate is off.

Fig 3.2.3: Transistor level implementation of a positive latch built using transmission

gates

[Source : Jan M. Rabaey ,Anantha Chandrakasan, Borivoje. Nikolic, ‖Digital Integrated

Circuits:A Design perspective …]

Unlike the SR FF, the feedback does not have to be overridden to write the

memory and hence sizing of transistors is not critical for realizing correct

functionality. The number of transistors that the clock touches is important since

it has an activity factor of 1. This particular latch implementation is not

particularly efficient from this metric as it presents a load of 4 transistors to the

CLK signal.

It is possible to reduce the clock load to two transistors by using implement

multiplexers using NMOS only pass transistor as shown in Figure 3.2.4 The

advantage of this approach is the reduced clock load of only two NMOS devices.

When CLK is high, the latch samples the D input, while a low clock-signal

enables the feedback-loop, and puts the latch in the hold mode.

EC 8095 VLSI DESIGN

ROHINI COLLEGE OF ENGINEERING AND TECHNOLOGY

Low-Voltage Static Latches

The scaling of supply voltages is critical for low power operation.

Unfortunately, certain latch structures don’t function at reduced supply voltages.

For example, without the scaling of device thresholds, NMOS only pass

transistors don’t scale well with supply voltage due to its inherent threshold

drop. At very low power supply voltages, the input to the inverter cannot be raised

above the switching threshold, resulting in incorrect evaluation. Even with the

use of transmission gates, performance degrades significantly at reduced supply

voltages.Scaling to low supply voltages hence requires the use of reduced

threshold

Fig 3.2.4: one solution for the leakage problem in low-voltage operation

using MTCMOS

[Source : Jan M. Rabaey ,Anantha Chandrakasan, Borivoje. Nikolic, ‖Digital Integrated

Circuits:A Design perspective …]

devices. However, this has the negative effect of exponentially increasing

EC 8095 VLSI DESIGN

ROHINI COLLEGE OF ENGINEERING AND TECHNOLOGY

the sub- threshold leakage Power. age energy is typically insignificant compared

to the switching power. However, with the use of conditional clocks, it is possible

that registers are idle for extended periods and the leakage energy expended by

registers can be quite significant.

Many solutions are being explored to address the problem of high leakage

during idle periods. One approach for this involves the use of Multiple Threshold

devices as shown in above figure only the negative latch is shown here. The

shaded inverters and transmission gates are implemented in low-threshold

devices. The low threshold inverters are gated using high threshold devices to

eliminate leakage.

During normal mode of operation, the sleep devices are tuned on. When

clock is low, the D input is sampled and propagates to the output. When clock is

high, the latch is in the hold mode. The feedback transmission gate conducts and

the cross-coupled feedback is enabled. Note there is an extra inverter, needed for

storage of state when the latch is in the sleep state. During idle mode, the high

threshold devices in series with the low threshold inverter are turned off (the

SLEEP signal is high), eliminating leakage. It is assumed that clock is in the high

state when the latch is in the sleep state. The feedback low-threshold transmission

gate is turned on and the cross-coupled high-threshold device maintains the state

of the latch.

EC 8095 VLSI DESIGN

You might also like

- Jeep WJ 2001 Grand Cherokee MOPAR Parts CatalogDocument413 pagesJeep WJ 2001 Grand Cherokee MOPAR Parts Catalogbillh@optonline.net100% (1)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Practical Feedback Loop Design Considerations For Switched Mode Power SuppliesDocument14 pagesPractical Feedback Loop Design Considerations For Switched Mode Power SuppliesDiego PhillipeNo ratings yet

- Gerd Schraner - The Art of Wheel BuildingDocument103 pagesGerd Schraner - The Art of Wheel Buildingwellsy8983% (24)

- 7055-3F - 7070-1F Catalog PDFDocument12 pages7055-3F - 7070-1F Catalog PDFPHÁT NGUYỄN THẾ100% (1)

- Design of An ADC Using High Precision Comparator With Time Domain Offset CancellationDocument4 pagesDesign of An ADC Using High Precision Comparator With Time Domain Offset CancellationijtetjournalNo ratings yet

- Servolectric E 09Document18 pagesServolectric E 09Fahrurrazi HaronNo ratings yet

- DiDocument6 pagesDipani256No ratings yet

- Digitally Controlled Oscillator ReportDocument18 pagesDigitally Controlled Oscillator ReportVinidhra ShivakumarNo ratings yet

- EDN Design Ideas 2009Document144 pagesEDN Design Ideas 2009chag195675% (4)

- C4 Corvette Courtesy Lights Dimmer Module RepairDocument13 pagesC4 Corvette Courtesy Lights Dimmer Module RepairSjoling8211No ratings yet

- Shortage 1Document828 pagesShortage 1Juan Alejandro Gallegos FloresNo ratings yet

- Allen Bradley Catalog Wiring SystemsDocument189 pagesAllen Bradley Catalog Wiring SystemsAlphaNo ratings yet

- Tecnotest Eclod 6430 Service Manual 9206176Document48 pagesTecnotest Eclod 6430 Service Manual 9206176Waqar Waheed67% (3)

- CASAPPA CatalogueDocument1,160 pagesCASAPPA CatalogueEduardNo ratings yet

- Failure Codes Fendt 900 Vario 09 2007Document20 pagesFailure Codes Fendt 900 Vario 09 2007Maureen100% (54)

- EC6601 VLSI Design Model QBDocument44 pagesEC6601 VLSI Design Model QBxperiaashNo ratings yet

- Irjet V8i5487Document3 pagesIrjet V8i5487Sado HusseinYusufNo ratings yet

- A New Subthreshold Current-Mode Four Quadrant MultiplierDocument6 pagesA New Subthreshold Current-Mode Four Quadrant MultiplierEditor IJRITCCNo ratings yet

- Low Power Ring Oscillator at 180nm CMOS Technology: Aman Shivhare M. K. GuptaDocument4 pagesLow Power Ring Oscillator at 180nm CMOS Technology: Aman Shivhare M. K. GuptaRam MNo ratings yet

- PPTDocument20 pagesPPTLita SanduNo ratings yet

- Clock GatingDocument28 pagesClock GatingTANMAY VADHERANo ratings yet

- Low Dynamic Power High Performance Adder: Department of Electronics & Communication Engineering M.Tech Vlsi DesignDocument11 pagesLow Dynamic Power High Performance Adder: Department of Electronics & Communication Engineering M.Tech Vlsi DesignSaranya ChakrabortyNo ratings yet

- CAD LAbDocument27 pagesCAD LAbSuraj KamyaNo ratings yet

- Microchip CLC DescriptionDocument12 pagesMicrochip CLC DescriptionKamlesh YadavNo ratings yet

- Lab2 ASKDocument6 pagesLab2 ASKNasly Realpe100% (2)

- A Fully Differential Switched-Current Delta-Sigma Modulator Using Single 3.347 Power-Supply VoltageDocument4 pagesA Fully Differential Switched-Current Delta-Sigma Modulator Using Single 3.347 Power-Supply VoltageRamakrishnaVakulabharanamNo ratings yet

- Double Tail ComparatorDocument32 pagesDouble Tail ComparatormdlogicsolutionsNo ratings yet

- Ofc Lab Manual 2Document21 pagesOfc Lab Manual 2Shobhit JainNo ratings yet

- Fix3 33333333Document4 pagesFix3 33333333doanminhtien030903No ratings yet

- Switched Capacitor FilterDocument20 pagesSwitched Capacitor FilterArijit ShawNo ratings yet

- A Wide Range Level Shifter Using A Self Biased Cascode Current Mirror With PTL Based BufferDocument5 pagesA Wide Range Level Shifter Using A Self Biased Cascode Current Mirror With PTL Based BufferRaja PosupoNo ratings yet

- Designing A Boost-Switching Regulator With The MCP1650Document0 pagesDesigning A Boost-Switching Regulator With The MCP1650Asad MalikNo ratings yet

- Topic 3 LynchDocument26 pagesTopic 3 Lynchsunil251No ratings yet

- Fast Transient Low-Dropout Voltage Regulator With Hybrid Dynamic Biasing Technique For Soc ApplicationDocument6 pagesFast Transient Low-Dropout Voltage Regulator With Hybrid Dynamic Biasing Technique For Soc ApplicationNguyen Van ToanNo ratings yet

- Wide Tuning Range VCO for Ultrasound TransmitterDocument4 pagesWide Tuning Range VCO for Ultrasound TransmitterEldhose VargheseNo ratings yet

- Connect passive components to logic gates for timing circuitsDocument11 pagesConnect passive components to logic gates for timing circuitsqqazertyNo ratings yet

- Core JavaDocument11 pagesCore JavaGangadharNo ratings yet

- Asynchronous Data Sampling Within Clock-Gated Double Edge Triggered Flip-FlopsDocument6 pagesAsynchronous Data Sampling Within Clock-Gated Double Edge Triggered Flip-Flopsblessysara16No ratings yet

- ZVSDocument28 pagesZVS12BACAUNo ratings yet

- EE215 Lab 4Document6 pagesEE215 Lab 4vhiep195No ratings yet

- Vtu 3RD Sem Cse Logic Design Notes 10CS33Document63 pagesVtu 3RD Sem Cse Logic Design Notes 10CS33EKTHATIGER633590100% (3)

- Vsli Unit 2 Question Bank With AnswersDocument10 pagesVsli Unit 2 Question Bank With AnswersPavani NNo ratings yet

- Design and Implementation of RC OscillatorsDocument11 pagesDesign and Implementation of RC OscillatorsAhmer FarooqNo ratings yet

- Simple automatic-shutoff circuit uses few componentsDocument5 pagesSimple automatic-shutoff circuit uses few componentsJuan Manuel Han MacNo ratings yet

- Resonant DC Link in PWM AC ChopperDocument5 pagesResonant DC Link in PWM AC ChopperMukesh SharmaNo ratings yet

- ReportDocument15 pagesReportGavaine MattisonNo ratings yet

- A Novel Ultra High-Speed Flip-Flop-Based Frequency Divider: Ravindran Mohanavelu and Payam HeydariDocument4 pagesA Novel Ultra High-Speed Flip-Flop-Based Frequency Divider: Ravindran Mohanavelu and Payam Heydarirah0987No ratings yet

- A Low Power, and Low Signal 5-Bit 25msamples/s Pipelined ADC For Monolithic Active PixelsDocument5 pagesA Low Power, and Low Signal 5-Bit 25msamples/s Pipelined ADC For Monolithic Active Pixelstajmjcet_123No ratings yet

- Define memory cell and differentiate RAM and ROMDocument11 pagesDefine memory cell and differentiate RAM and ROMGautam AggarwalNo ratings yet

- 132 - 136 Dinda Fadhya Darmidjas 21060118130105Document8 pages132 - 136 Dinda Fadhya Darmidjas 21060118130105Dinda FadhyaNo ratings yet

- Implementation of Full-Bridge Current-Fed Resonant Boost Converter Using PIC MicrocontrollerDocument6 pagesImplementation of Full-Bridge Current-Fed Resonant Boost Converter Using PIC MicrocontrollerAlonso CoradoNo ratings yet

- Microprocessor Based Impedance Relay: TechnicalsymposiumDocument14 pagesMicroprocessor Based Impedance Relay: TechnicalsymposiumGaurav JaiswalNo ratings yet

- ZvsDocument29 pagesZvsSandy RonaldoNo ratings yet

- EE215: Fundamentals of Electrical Engineering Lab 4 Time Delay CircuitsDocument6 pagesEE215: Fundamentals of Electrical Engineering Lab 4 Time Delay CircuitsÁo ĐenNo ratings yet

- Cmos Inverter As A ComparatorDocument5 pagesCmos Inverter As A ComparatorAnonymous TPVfFif6TONo ratings yet

- 5 Mirzaei TCASI ReceiverDocument14 pages5 Mirzaei TCASI ReceiverkavyaNo ratings yet

- DAC AnalysisDocument19 pagesDAC Analysisమురళీధర్ ఆది ఆంధ్రుడుNo ratings yet

- A 1.8V 12-Bit 230-MS/s Pipeline ADC in 0.18 M CMOS TechnologyDocument4 pagesA 1.8V 12-Bit 230-MS/s Pipeline ADC in 0.18 M CMOS Technologyfaithfully_fatihNo ratings yet

- Tutorial Q and A supplementaryDocument25 pagesTutorial Q and A supplementaryKhadar A. FarahNo ratings yet

- OLTC Dynamic Testing P10Document16 pagesOLTC Dynamic Testing P10Marcio RangelNo ratings yet

- UVLO Circuit Design with Bandgap StructureDocument4 pagesUVLO Circuit Design with Bandgap Structured_niku100% (1)

- Performance of Zeta Converter Based On PWM Technique For High Power ApplicationDocument4 pagesPerformance of Zeta Converter Based On PWM Technique For High Power ApplicationiirNo ratings yet

- Project ReportBIIRECTIONAL VISITOR COUNTERDocument51 pagesProject ReportBIIRECTIONAL VISITOR COUNTERSarvjeet Singh SohalNo ratings yet

- 11 Chapter03 PDFDocument13 pages11 Chapter03 PDFAtulNo ratings yet

- Proposal of A Soft-Switching Single-PhaseDocument7 pagesProposal of A Soft-Switching Single-Phaseayie55No ratings yet

- Fpga IntroDocument10 pagesFpga IntroJpradha KamalNo ratings yet

- FPGA Lecture SERC NISERDocument57 pagesFPGA Lecture SERC NISERJpradha KamalNo ratings yet

- Past, Present or Future Tense?: Grade 3 Verbs WorksheetDocument2 pagesPast, Present or Future Tense?: Grade 3 Verbs WorksheetJoslinNo ratings yet

- EE213 Design RulesDocument10 pagesEE213 Design Rulesmmk431No ratings yet

- Crystal growth and wafer fabrication fundamentalsDocument30 pagesCrystal growth and wafer fabrication fundamentalsJpradha KamalNo ratings yet

- Fault ModelsDocument38 pagesFault ModelsadeNo ratings yet

- BCS Module Leader ContactDocument34 pagesBCS Module Leader ContactJpradha KamalNo ratings yet

- Time Response, ME451: Instructor: Jongeun ChoiDocument84 pagesTime Response, ME451: Instructor: Jongeun ChoiJpradha KamalNo ratings yet

- The Root Locus AnalysisDocument56 pagesThe Root Locus AnalysisJpradha KamalNo ratings yet

- Replace spring in boom logic valve to fix boom issueDocument4 pagesReplace spring in boom logic valve to fix boom issueAparecidaMarquesNo ratings yet

- Pilot Control Unit With End Position Lock For The Remote Control of Directional Valves Type 4THF5, 6THF5Document12 pagesPilot Control Unit With End Position Lock For The Remote Control of Directional Valves Type 4THF5, 6THF5nksiavashNo ratings yet

- Cleaning Services Price List TemplateDocument1 pageCleaning Services Price List TemplateDonatsu AMNo ratings yet

- Product - Information - MI06-S-XX-400 V1.6Document2 pagesProduct - Information - MI06-S-XX-400 V1.6Jorge MorenoNo ratings yet

- ns2584 BollardsDocument1 pagens2584 Bollardscoc verificationNo ratings yet

- V Belt Technical Specification POLYESTER CORD Neoprene Jacketed HIC Manufactured UNIVERSAL BrandDocument5 pagesV Belt Technical Specification POLYESTER CORD Neoprene Jacketed HIC Manufactured UNIVERSAL Brandmonahend100% (1)

- Mechatronics PDFDocument18 pagesMechatronics PDFnirajNo ratings yet

- mc14043b d-1193116Document8 pagesmc14043b d-1193116cesarNo ratings yet

- KAMAI 500: Quick Connect GuideDocument1 pageKAMAI 500: Quick Connect GuideIonNo ratings yet

- Presco: Automatic Capacitance and Power Factor Field Test Set 12 KV - 2.4 kVA Type FT-12Document17 pagesPresco: Automatic Capacitance and Power Factor Field Test Set 12 KV - 2.4 kVA Type FT-12torkoreNo ratings yet

- HUFFY Bicycle Multispeed - ManualDocument44 pagesHUFFY Bicycle Multispeed - ManualottuserNo ratings yet

- PM Cat-10 1031Document2 pagesPM Cat-10 1031RP POWER ELECTRICAL SALEMNo ratings yet

- Dover OPW - Kamlok Autolok Sell SheetDocument2 pagesDover OPW - Kamlok Autolok Sell SheetXavierNo ratings yet

- Elcometer 101: 101 - TMA - 0465 - 00 - 03 (Part Number 2185) .FM Page - 1 Tuesday, August 20, 2013 11:03 AMDocument7 pagesElcometer 101: 101 - TMA - 0465 - 00 - 03 (Part Number 2185) .FM Page - 1 Tuesday, August 20, 2013 11:03 AMDania GomezNo ratings yet

- Study of OPGW Performance against Lightning Strikes in UHV Transmission LinesDocument6 pagesStudy of OPGW Performance against Lightning Strikes in UHV Transmission LinesARCC2030No ratings yet

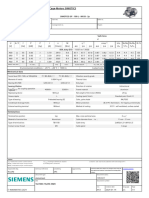

- 1LE1003-1AA43-4AB4 Datasheet enDocument1 page1LE1003-1AA43-4AB4 Datasheet enAhmed Mahmoud AliNo ratings yet

- Bergamont Workbook LJ AccesoiresDocument3 pagesBergamont Workbook LJ Accesoiresapi-652055634No ratings yet

- Parker Steam Boiler Quarterly Inspection Report: QTR 101-5Document2 pagesParker Steam Boiler Quarterly Inspection Report: QTR 101-5Danu KautsarNo ratings yet

- Measuring Viscosity - : Ika RotaviscDocument4 pagesMeasuring Viscosity - : Ika RotaviscMelanyNo ratings yet

- Site Equipment List For TAG GokweDocument8 pagesSite Equipment List For TAG GokwetariroNo ratings yet