Professional Documents

Culture Documents

Assignment I

Assignment I

Uploaded by

win papasanOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Assignment I

Assignment I

Uploaded by

win papasanCopyright:

Available Formats

Assignment I

I. A sequential circuit has one input (X) and two outputs (S and V). X

represents a 4-bit binary number N, which is input least signicant bit rst.

S represents a 4-bit binary number equal to N 1 2, which is output least

signicant bit rst. At the time the fourth input occurs, V 5 1 if N 1 2 is too

large to be represented by 4 bits; otherwise, V = 0. The value of S should

be the proper value, not a don’t care, in both cases. The circuit always

resets after the fourth bit of X is received.

(a) Derive a Mealy state graph and table with a minimum number of

states (6 states).

(b) Try to choose a good state assignment. Realize the circuit using D

-ip--ops and NAND gates. Repeat using NOR gates. (Work this part

by hand.)

II. What is difference between a CPLD and an FPGA?

III. What are the disadvantages of SRAM FPGAs?

IV. What are the disadvantages of antifuse FPGAs?

You might also like

- Chapter 4 Sequential Logic CircuitsDocument50 pagesChapter 4 Sequential Logic Circuitsjuber mulla100% (2)

- Experiment No.1 Aim: Objective:: Not Gate: IC 7404 (HEX Inverter) 14 Pin Supply Voltage:5vDocument10 pagesExperiment No.1 Aim: Objective:: Not Gate: IC 7404 (HEX Inverter) 14 Pin Supply Voltage:5vCharanpreet SinghNo ratings yet

- Combinatorial Algorithms: For Computers and CalculatorsFrom EverandCombinatorial Algorithms: For Computers and CalculatorsRating: 4 out of 5 stars4/5 (2)

- Practice Assignment No-4Document8 pagesPractice Assignment No-4Seemab RamzanNo ratings yet

- Lower Bound For Sorting, Radix Sort: COMP171 Fall 2005Document20 pagesLower Bound For Sorting, Radix Sort: COMP171 Fall 2005ganesh12julyNo ratings yet

- Digital Electronics 3rd SemDocument39 pagesDigital Electronics 3rd SemPriyanshu ThawaitNo ratings yet

- Mods Only ManualDocument12 pagesMods Only Manuallucasrende10No ratings yet

- Prayatna 2019: Ospc (Onsite Programming Contest)Document3 pagesPrayatna 2019: Ospc (Onsite Programming Contest)testNo ratings yet

- Practice TestDocument5 pagesPractice TestAhmedBattarNo ratings yet

- RadixsortDocument20 pagesRadixsortapi-3825915No ratings yet

- Contest 1007Document15 pagesContest 1007Ivan YevtushenkoNo ratings yet

- 8-EED220 Lecture 8Document30 pages8-EED220 Lecture 8as0110967700No ratings yet

- Computer ArchitectureDocument15 pagesComputer ArchitectureNaeghilNo ratings yet

- Basic GatesDocument39 pagesBasic GatesVijay BaraiNo ratings yet

- Prof. Ram Meghe Institute of Technology & Research, Badnera Amravati Department of Electronics & Telecommunication EnggDocument6 pagesProf. Ram Meghe Institute of Technology & Research, Badnera Amravati Department of Electronics & Telecommunication EnggvishalNo ratings yet

- DBS Lecture3Document11 pagesDBS Lecture3Trần QiNo ratings yet

- Lab Mannual For Digital Electronics LabDocument35 pagesLab Mannual For Digital Electronics LabSia ghoshNo ratings yet

- Imosl2014 2022Document781 pagesImosl2014 2022buixuanphong21012008No ratings yet

- DE Exp 1Document8 pagesDE Exp 1Akshat MehrotraNo ratings yet

- Assignment III - B.E. VI Semester: A B A B A B A BDocument3 pagesAssignment III - B.E. VI Semester: A B A B A B A Bsurya kiranNo ratings yet

- UCSB ECE 152a Course ReaderDocument19 pagesUCSB ECE 152a Course Readermuhd220No ratings yet

- ECAD Lab Manual (ECAD and VLSI Lab)Document105 pagesECAD Lab Manual (ECAD and VLSI Lab)Swaminathan Kathirvel0% (1)

- Hidden Markov ModelsDocument41 pagesHidden Markov ModelsmaheshNo ratings yet

- Chapter 6Document16 pagesChapter 6Gébrè SîllãsíêNo ratings yet

- Plu Novice 2011 FinalDocument10 pagesPlu Novice 2011 FinalAmul ChiluveruNo ratings yet

- Home Assignment No-4: Digital Logic Design BEE-1B&CDocument4 pagesHome Assignment No-4: Digital Logic Design BEE-1B&COzi ---No ratings yet

- The 82nd William Lowell Putnam Mathematical Competition Saturday, December 4, 2021Document2 pagesThe 82nd William Lowell Putnam Mathematical Competition Saturday, December 4, 2021Swaraj ShindeNo ratings yet

- Problem S5: Math Homework: 1 N I TH X Y I I IDocument4 pagesProblem S5: Math Homework: 1 N I TH X Y I I ITrần Nhật KhánhNo ratings yet

- Co Lab Manual 1Document72 pagesCo Lab Manual 1Hafza GhafoorNo ratings yet

- Inverse AI Intra Team Contest 2022: 11 Problems 5 HoursDocument15 pagesInverse AI Intra Team Contest 2022: 11 Problems 5 HoursJohn DoeNo ratings yet

- DE EXP ListsDocument34 pagesDE EXP Liststixel62099No ratings yet

- Advanced-Car Parking SystemDocument23 pagesAdvanced-Car Parking SystemKamalesh RjNo ratings yet

- Exam PaperDocument2 pagesExam PaperbookNo ratings yet

- DSA - List of Experiments From Virtual Lab Portal - Additional PracticeDocument6 pagesDSA - List of Experiments From Virtual Lab Portal - Additional PracticeVarsha SinghNo ratings yet

- Verification and Interpretation of Truth Table For AND, OR, NOT, NAND, NOR, Ex-OR, Ex-NOR GatesDocument10 pagesVerification and Interpretation of Truth Table For AND, OR, NOT, NAND, NOR, Ex-OR, Ex-NOR GatesG36Gajanan Purud .No ratings yet

- Experiment 1Document5 pagesExperiment 1Sayan KarmakarNo ratings yet

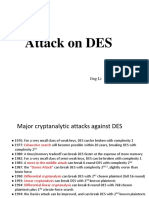

- Atttack On DESDocument33 pagesAtttack On DEStejashwiniNo ratings yet

- EE201: Digital Circuits and Systems: Section 6 - MemoryDocument22 pagesEE201: Digital Circuits and Systems: Section 6 - Memorya sNo ratings yet

- Chapter6b-Combinational Logic Design PracticesDocument38 pagesChapter6b-Combinational Logic Design PracticesZulkarnineNo ratings yet

- Ch3.Block CiphersDocument19 pagesCh3.Block CiphersHemant MahajanNo ratings yet

- E2.11/ISE2.22 - Digital Electronics IIDocument4 pagesE2.11/ISE2.22 - Digital Electronics IIkolhejayantNo ratings yet

- Digital System DesignDocument2 pagesDigital System Designrocky dNo ratings yet

- 65 Mohit Tiwari IT 2 STLD FileDocument78 pages65 Mohit Tiwari IT 2 STLD FileMohit TiwariNo ratings yet

- IS Lab MannualDocument26 pagesIS Lab Mannualvasudha sankpalNo ratings yet

- The 69th William Lowell Putnam Mathematical Competition Saturday, December 6, 2008Document8 pagesThe 69th William Lowell Putnam Mathematical Competition Saturday, December 6, 2008Kamran MehdiyevNo ratings yet

- Chapter 8 Digital ElectronicsDocument15 pagesChapter 8 Digital ElectronicsSai PrintersNo ratings yet

- Multiplexers: Associate Professor Department of ICE, RUDocument77 pagesMultiplexers: Associate Professor Department of ICE, RUAmir AmirNo ratings yet

- Lecture 5Document33 pagesLecture 5hasona272002No ratings yet

- 2018 German Collegiate Programming Contest GCPC 18 enDocument28 pages2018 German Collegiate Programming Contest GCPC 18 enAhmed RezikNo ratings yet

- Digital Logic DesignDocument5 pagesDigital Logic DesignEngr Teerath KumarNo ratings yet

- Problem A: Python File: Time Limit: 1 SecondDocument15 pagesProblem A: Python File: Time Limit: 1 SecondMinhLêHồngĐạiNo ratings yet

- Assignment Submission Details AY-2023-2024 Subject Code:20MAT112 Subject Name: Discrete Mathematic StructureDocument7 pagesAssignment Submission Details AY-2023-2024 Subject Code:20MAT112 Subject Name: Discrete Mathematic Structurekarthi93002No ratings yet

- DE (Exp-4) (251902158)Document19 pagesDE (Exp-4) (251902158)Sahil BharalNo ratings yet

- Anfis (Ai)Document17 pagesAnfis (Ai)Jane Mhel GarciaNo ratings yet

- Chapter 3 Gate-Level MinimizationDocument50 pagesChapter 3 Gate-Level MinimizationGilbert SigalaNo ratings yet

- Sonam Assignment 1Document5 pagesSonam Assignment 1sonams.ec.21No ratings yet

- 19-Module 4 - TELL - ASK Interface, FOL For Various Domains, Knowledge Engineering-06!03!2024Document21 pages19-Module 4 - TELL - ASK Interface, FOL For Various Domains, Knowledge Engineering-06!03!2024zerohero.pvgNo ratings yet

- Problems NCPC2005Document24 pagesProblems NCPC2005Peash Al EhsanNo ratings yet

- Experiment: Verification and Interpretation of Truth Table For AND, OR, NOT, NAND, NOR, Ex-OR, Ex-NOR GatesDocument42 pagesExperiment: Verification and Interpretation of Truth Table For AND, OR, NOT, NAND, NOR, Ex-OR, Ex-NOR GatesMAYANKNo ratings yet

- Bt20ec019 Exp - IiDocument14 pagesBt20ec019 Exp - IiNishant MishraNo ratings yet