Professional Documents

Culture Documents

Quiz 2 Section 2

Quiz 2 Section 2

Uploaded by

baeuknwwhoimOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Quiz 2 Section 2

Quiz 2 Section 2

Uploaded by

baeuknwwhoimCopyright:

Available Formats

North South University

Department of Computer Science & Engineering

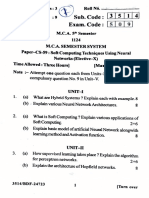

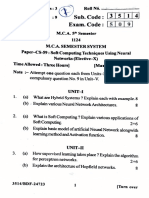

Quiz 2: Fall, 2021, ETE412/EEE411/CSE435- Section 2: VLSI Design Date: Nov 12, 2021

1. a) Show the design path of VLSI design starting from idea to chip as shown in the class.

Indicate how your courses coves the different stages in that path.

b) In brief (any five): (i) Design Team (ii) Design Hierarchy: Top down and Bottom Up (iii)

Logical Design and Physical Design (iv) ASIC and System on Chip (v) Moor’s Law. (vi)

List of Integrated Ckt based on size and years

2. a) Describe: (any 4)

i. Create own ckt using 3 push and 2 pull switches and show the function by Boolean

equation.

ii. Create your own Boolean equation where you have 2 active high and three active

low controls and implement that function using push pull switches.

iii. Complementary Pair

iv. Threshold Voltage: Strong One, Weak One, Strong Zero, Weak Zero

v. Pass Characteristics.

b) Using truth table method design the CMOS circuit that implements following function

g = ab

3. a) What is Transmission Gate? Design XOR or 4-to-1 MUX using TGs.

b) Design a CMOS logic circuit using bubble pushing technique.

g= ab+cd

(Hint: Implement the nFET network and then apply bubble pushing to find the pFET

network).

You might also like

- 2011 Advanced Computer Architecture: CS/B.TECH (CSE) /SEM-4/CS-403/2011Document7 pages2011 Advanced Computer Architecture: CS/B.TECH (CSE) /SEM-4/CS-403/2011Avik MitraNo ratings yet

- Vlsi Vlsi Design Dec 2020Document2 pagesVlsi Vlsi Design Dec 2020Margoob TanweerNo ratings yet

- Question Bank For Mid-2 r13 (Vlsi) .Document6 pagesQuestion Bank For Mid-2 r13 (Vlsi) .rppvchNo ratings yet

- DEC Lab Experiments - 2017aDocument5 pagesDEC Lab Experiments - 2017aManjeet SinghNo ratings yet

- Logic CircuitDocument2 pagesLogic CircuitRaman yadavNo ratings yet

- Time: 3 Hours Full Marks: 70Document3 pagesTime: 3 Hours Full Marks: 70pikluNo ratings yet

- Ecs-301 Digital Logic Design 2010-11Document4 pagesEcs-301 Digital Logic Design 2010-11Satyedra MauryaNo ratings yet

- V Semester B.C.A. Examination, March/April 2021 (CBCS) (F+R) (Y2K14) Computer ScienceDocument2 pagesV Semester B.C.A. Examination, March/April 2021 (CBCS) (F+R) (Y2K14) Computer ScienceNâñè DévrûNo ratings yet

- Important 16 Mark Questions-19!1!2024Document5 pagesImportant 16 Mark Questions-19!1!2024FLOWERNo ratings yet

- B.E. Electronics and Communication Engineering: VLSI LAB (0:0:3) 1.5Document3 pagesB.E. Electronics and Communication Engineering: VLSI LAB (0:0:3) 1.5Amit ShetNo ratings yet

- DesignandAnalysisofAlgorithms March2019 M SC Withcredits RegularJune-2017PatternM ScPart-I D7DEF24FDocument2 pagesDesignandAnalysisofAlgorithms March2019 M SC Withcredits RegularJune-2017PatternM ScPart-I D7DEF24FRizwan AhemadNo ratings yet

- Digital Principles and System DesignDocument76 pagesDigital Principles and System Designraja rNo ratings yet

- 2018 Winter Question Paper (Msbte Study Resources)Document2 pages2018 Winter Question Paper (Msbte Study Resources)Rohit DevrukheNo ratings yet

- SSC JE Syllabus PDFDocument5 pagesSSC JE Syllabus PDFIchigoNo ratings yet

- SEPTEMBERDocument3 pagesSEPTEMBERRocky BobeeNo ratings yet

- Soft ComputingDocument10 pagesSoft ComputingmohitNo ratings yet

- Soft ComputingDocument10 pagesSoft ComputingmohitNo ratings yet

- 3 Hours / 70 Marks: Seat NoDocument3 pages3 Hours / 70 Marks: Seat No916. Saee YadavNo ratings yet

- BCA I I Digital SystemDocument4 pagesBCA I I Digital SystemAmory Sabri AsmaroNo ratings yet

- Hoursl:: Computii (G (I/Eural Logic Ai (D Gei/Etic Algorithm) (Totalmarks:Lq0Document3 pagesHoursl:: Computii (G (I/Eural Logic Ai (D Gei/Etic Algorithm) (Totalmarks:Lq0abhishekNo ratings yet

- L-4rr-lI/CSE Date: 27/0312023: Section-ADocument35 pagesL-4rr-lI/CSE Date: 27/0312023: Section-AQuazi Hasnat IrfanNo ratings yet

- Sample Question Paper Data CommunicationDocument5 pagesSample Question Paper Data CommunicationYash Hartalkar0% (1)

- University Question Papers - VLSIDocument26 pagesUniversity Question Papers - VLSIVijayNo ratings yet

- Government College of Engineering, AmravatiDocument2 pagesGovernment College of Engineering, AmravatiRamRaoNo ratings yet

- IT1020 - Introduction To Computer SystemsDocument6 pagesIT1020 - Introduction To Computer SystemsgepoveNo ratings yet

- B. C. A. (Fifth Semester) EXAMINATION, 2016-17: Note: All Questions Have To Be Attempted. Section-ADocument3 pagesB. C. A. (Fifth Semester) EXAMINATION, 2016-17: Note: All Questions Have To Be Attempted. Section-ARajeev GairolaNo ratings yet

- Guessing Papers 1-2-12th Electronics Sub Code C2Document6 pagesGuessing Papers 1-2-12th Electronics Sub Code C2snigdhagulhane0922No ratings yet

- Digital Electronics Question BankDocument6 pagesDigital Electronics Question BankReshna ShowkathNo ratings yet

- Campusexpress - Co.in: Set No. 1Document8 pagesCampusexpress - Co.in: Set No. 1skssushNo ratings yet

- MCA105Document1 pageMCA105Abhi MittalNo ratings yet

- 2EC6302-Digital Electronics QBDocument12 pages2EC6302-Digital Electronics QBSurendar PNo ratings yet

- Previous Question PapersDocument4 pagesPrevious Question Papersshaker423No ratings yet

- Vlsi QP 21,22Document11 pagesVlsi QP 21,22Arunitha ArulnathanNo ratings yet

- Model Paper Kuru III Cs BtechDocument2 pagesModel Paper Kuru III Cs Btecher_praveshNo ratings yet

- Digital System Component DesignDocument2 pagesDigital System Component DesignNdiawo MusicianNo ratings yet

- Digital Nov 07Document6 pagesDigital Nov 07skssushNo ratings yet

- Personal Project 2023-24Document1 pagePersonal Project 2023-24Ogwang hallanNo ratings yet

- EM506 VLSI ArchitectureDocument5 pagesEM506 VLSI ArchitecturePrakash Velayudham VNo ratings yet

- MCN ADocument148 pagesMCN Aamritanshuu100% (2)

- Jntu MDocument3 pagesJntu MVijay SagarNo ratings yet

- NR-221103 - Digital Circuits Design and ApplictionDocument5 pagesNR-221103 - Digital Circuits Design and ApplictionSrinivasa Rao G100% (1)

- Answer Key CSE 105 II - CIA PART A (10X2 20)Document4 pagesAnswer Key CSE 105 II - CIA PART A (10X2 20)K SriNo ratings yet

- Computer Organization Architecture RCS 302Document2 pagesComputer Organization Architecture RCS 302yugam sainiNo ratings yet

- Cs 60Document80 pagesCs 60Sirsendu RoyNo ratings yet

- March 2008 Paper 2Document2 pagesMarch 2008 Paper 2many1tothe11No ratings yet

- CC1 Class Test (AB-Sir)Document1 pageCC1 Class Test (AB-Sir)Amitava Biswas AB SirNo ratings yet

- Metropolitan University, SylhetDocument1 pageMetropolitan University, SylhetJashon RoyNo ratings yet

- COA Assignment of Unit-1 and Unit-2Document4 pagesCOA Assignment of Unit-1 and Unit-2Shruti JhaNo ratings yet

- EE6006 - ASC Anna University Question Nov Dec 2016Document8 pagesEE6006 - ASC Anna University Question Nov Dec 2016Dr. A.umaraniNo ratings yet

- BCS 11 - June2010 June2023Document91 pagesBCS 11 - June2010 June2023RohitNo ratings yet

- CCN Q BaDocument5 pagesCCN Q Baraghunayak8861No ratings yet

- ASC Independent PU College II PUC Science - Computer Science - Model Paper 3Document2 pagesASC Independent PU College II PUC Science - Computer Science - Model Paper 3yashas yashNo ratings yet

- UNIT WISE QUEST DIGITAL LOGIC DESIGN - GIET 2019 II - I (3rd Sem)Document18 pagesUNIT WISE QUEST DIGITAL LOGIC DESIGN - GIET 2019 II - I (3rd Sem)Deepak NaiduNo ratings yet

- DDCO UPDATED QUESTION BANKttttDocument4 pagesDDCO UPDATED QUESTION BANKttttbrahmareddy.22iseNo ratings yet

- Digital Electronics (CC1) CU Mock Test, 2024 (By AB Sir's Coaching - 8910350813)Document1 pageDigital Electronics (CC1) CU Mock Test, 2024 (By AB Sir's Coaching - 8910350813)Amitava BiswasNo ratings yet

- FALL SEMESTR - 2021-22 ECE3002 - VLSI Systems Design Lab FatDocument5 pagesFALL SEMESTR - 2021-22 ECE3002 - VLSI Systems Design Lab FatAthira VijayanNo ratings yet

- Prevyear QuepaperDocument15 pagesPrevyear Quepapernaveenkumar17081987No ratings yet