Professional Documents

Culture Documents

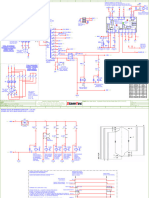

DSP48A1

DSP48A1

Uploaded by

Mohamed AlahmadyCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

DSP48A1

DSP48A1

Uploaded by

Mohamed AlahmadyCopyright:

Available Formats

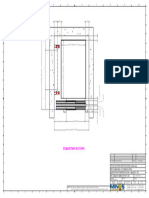

CECARRYIN

BCIN[17..0] CARRYIN_reg_out~0

0

CARRYIN

5 1

CARRYOUTF

RSTCARRYIN CARRYOUT

CARRYIN_reg_out~1 CARRYIN_reg_out CARRYOUT~0

0 0 CARRYOUT~1 CARRYOUT~reg0

0

1'h0 1 D 1

1'h0 1 D

CLK Q

1'h0 CLK Q

SCLR 1'h0

SCLR

CEP

Equal5

3:2 A[1..0]

OUT multiplixer_z_out~[47..0]

2'h2 B[1..0] = 0 P~[47..0]

0

1

1

Equal4 multiplixer_z_out~[95..48]

3:2 A[1..0] 0

OUT

2'h1 B[1..0] = 1 1'h0 CIN Add4 P~[95..48]

48{7}

0

A[48..0] OUT[48..0] post_adder_out[47..0]

PCIN[47..0] + 48:1 0 48'h0 1

47:0

B[48..0]

RSTP 47:0 1

CEC

PCOUT[47..0]

C_stg1~[47..0] Equal0

0 1:0 A[1..0] 1'h0 CIN Add2 1'h0 CIN Add3 P[0]~reg[47..0] P[47..0]

7

47:0

OUT

1 2'h0 B[1..0] = A[48..0] OUT[48..0] A[48..0] OUT[48..0] carryout

C[47..0] + + 49 0 D

C_stg1[47..0] multiplixer_x_out[47..0] B[48..0] B[48..0]

0 48 1 CLK Q

C_stg1~[95..48]

47:0

48'h0

0 D 48'h0 1 SCLR

RSTC 48'h0 1 CLK Q

48'h0 47:0 1'h0 CIN Add5

SCLR

Equal3 48:0 A[49..0] OUT[49..0]

3:2 A[1..0] +

OUT B[49..0]

2'h0 B[1..0] =

RSTA multiplixer_z_out[47..0]

0

A[17..0]

48'h0 1

D_stg1[17..0] Equal1

1:0 A[1..0]

OUT

D 2'h1 B[1..0] = A_stg2[17..0]

CLK Q multiplixer_x_out~[95..48]

18'h0 0 A_stg2~[35..18] D

SCLR 0

1 CLK Q

18'h0 1 18'h0

0:35

SCLR

multiplixer_x_out~[47..0]

0:17

0:11

Equal2

1:0 A[1..0] 0

OUT

0:17

2'h2 B[1..0] = 1

Mult0

B[17..0] A[17..0]

OUT[35..0]

18{6}

CEA B[17..0] x

A_stg2~[17..0] 1'h0 CIN Add0 pre_adder_out[17..0]

CED 0 0

A[17..0] OUT[17..0]

D_stg1~[17..0] 1 + 1

0 B[17..0] M[35..0]

D_stg1~[35..18]

18{4}

1 0 pre_adder_mux_out[17..0] M[0]~reg[35..0]

D[17..0] 0

18'h0 1

1 M~[35..0] D

1'h0 CIN Add1 0 M~[71..36]

17:0

RSTD 0 CLK Q

A[18..0] OUT[18..0] 1 36'h0

17:0

+ 36'h0 1 SCLR

B[18..0]

CEB

CLK B_stg2[17..0]

OPMODE_stg1[7..0]

CEOPMODE B_stg2~[17..0]

0 B_stg2~[35..18] D

OPMODE_stg1~[7..0] D 0

0 1 CLK Q BCOUT[17..0]

CLK Q 18'h0 1 18'h0

1 8'h0 SCLR

OPMODE[7..0] SCLR

RSTB

CEM

RSTOPMODE

OPMODE_stg1~[15..8]

0

8'h0 1

RSTM

You might also like

- Stin Ameriki v1Document2 pagesStin Ameriki v1Klapa RoufasNo ratings yet

- 12 - 3rd Trombone - Οι γερανοίDocument1 page12 - 3rd Trombone - Οι γερανοίblackpianowhitekeys88No ratings yet

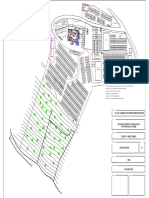

- Plano Redes Huaraz-Layout2Document1 pagePlano Redes Huaraz-Layout2carolay asencio castilloNo ratings yet

- 02 - Solo Clarinet (B Flat) - Οι γερανοίDocument1 page02 - Solo Clarinet (B Flat) - Οι γερανοίblackpianowhitekeys88No ratings yet

- Σονατινα νουμερο 1Document2 pagesΣονατινα νουμερο 1georgia32No ratings yet

- ΤΟ ΤΑΝΓΚΟ ΤΗΣ ΝΕΦΕΛΗΣDocument2 pagesΤΟ ΤΑΝΓΚΟ ΤΗΣ ΝΕΦΕΛΗΣSpyros VakakisNo ratings yet

- 04 - 2nd Clarinet (B Flat) - Οι γερανοίDocument1 page04 - 2nd Clarinet (B Flat) - Οι γερανοίblackpianowhitekeys88No ratings yet

- Koinoxristoi10 10Document1 pageKoinoxristoi10 10Olga LiberteNo ratings yet

- ΚΑΛΗΝ ΕΣΠΕΡΑΝ ΑΡΧΟΝΤΕΣDocument1 pageΚΑΛΗΝ ΕΣΠΕΡΑΝ ΑΡΧΟΝΤΕΣEleni KatsikeaNo ratings yet

- 11 - 2nd Trombone - Οι γερανοίDocument1 page11 - 2nd Trombone - Οι γερανοίblackpianowhitekeys88No ratings yet

- S40 - Excavation of Foundation - Warehouse 01Document1 pageS40 - Excavation of Foundation - Warehouse 01CoralSun CravensickNo ratings yet

- Να 'τανε το 21Document2 pagesΝα 'τανε το 21Argiris MaipasNo ratings yet

- Libro 5T0 PDFDocument132 pagesLibro 5T0 PDFfreyss TaniraNo ratings yet

- ΣΧΟΟΑΠ Δ.Ε. Υπάτης - Α1 Χάρτης Προσαρμογής κ Πληροφόρησης 01Document1 pageΣΧΟΟΑΠ Δ.Ε. Υπάτης - Α1 Χάρτης Προσαρμογής κ Πληροφόρησης 01kaliterilamiaNo ratings yet

- ΜυστικόDocument2 pagesΜυστικόGiannis GrigoriouNo ratings yet

- 13 - Euphonium (C) - Οι γερανοίDocument1 page13 - Euphonium (C) - Οι γερανοίblackpianowhitekeys88No ratings yet

- 14 - Tuba - Οι γερανοίDocument1 page14 - Tuba - Οι γερανοίblackpianowhitekeys88No ratings yet

- ATENISTAS - Αθηνα Σπανια Επαγγελματα PDFDocument2 pagesATENISTAS - Αθηνα Σπανια Επαγγελματα PDFΧάρης ΦραντζικινάκηςNo ratings yet

- 15 - Flute - Οι γερανοίDocument1 page15 - Flute - Οι γερανοίblackpianowhitekeys88No ratings yet

- 10 - 1st Trombone - Οι γερανοίDocument1 page10 - 1st Trombone - Οι γερανοίblackpianowhitekeys88No ratings yet

- Classificados: OportunidadesDocument1 pageClassificados: OportunidadesyasminfelkadriNo ratings yet

- 03 - 1st Clarinet (B Flat) - Οι γερανοίDocument1 page03 - 1st Clarinet (B Flat) - Οι γερανοίblackpianowhitekeys88No ratings yet

- Κοινωνικόν «Ποτήριον», Κ. Πρίγγου, Ήχ. α' από ΧρύσανθοDocument2 pagesΚοινωνικόν «Ποτήριον», Κ. Πρίγγου, Ήχ. α' από ΧρύσανθοIlie NutaNo ratings yet

- PR02-2022 - Arq1 - PL3 - V2 - CurDocument1 pagePR02-2022 - Arq1 - PL3 - V2 - CurCAMILO AGUILARNo ratings yet

- Π3 1 ΛίμνηDocument1 pageΠ3 1 ΛίμνηKaterina PapadopoulouNo ratings yet

- Π3 8 ΡοβιέςDocument1 pageΠ3 8 ΡοβιέςKaterina PapadopoulouNo ratings yet

- Trumpet 3Document1 pageTrumpet 3Nicole christodoulouNo ratings yet

- Άγια ΝύχταDocument1 pageΆγια ΝύχταGiannis NikoloudakisNo ratings yet

- Orz - Kymhs o 2Document1 pageOrz - Kymhs o 2Kostas LazarakisNo ratings yet

- ΑΡΤΟΠΑΡΑΣΚΕΥΑΣΤΗΣDocument30 pagesΑΡΤΟΠΑΡΑΣΚΕΥΑΣΤΗΣTrikala2016No ratings yet

- KLEFER - Katalog PDFDocument12 pagesKLEFER - Katalog PDFkędzierzawyNo ratings yet

- TYΠΙΚΟ ΗΛΕΚΤΡΟΛΟΓΙΚΟ ΔΙΑΓΡΑΜΜΑ ΥΔΡΑΥΛΙΚΟΥ ΑΝΕΛΚΥΣΤΗΡΑDocument8 pagesTYΠΙΚΟ ΗΛΕΚΤΡΟΛΟΓΙΚΟ ΔΙΑΓΡΑΜΜΑ ΥΔΡΑΥΛΙΚΟΥ ΑΝΕΛΚΥΣΤΗΡΑΑντωνία Παπαδήμα Start ElevatorsNo ratings yet

- 08 - Violin I - de Peel in BrandDocument2 pages08 - Violin I - de Peel in BrandViolin_ManNo ratings yet

- Aepp Book YliDocument92 pagesAepp Book Ylisaltas84No ratings yet

- Océano Pacífico: An CashDocument1 pageOcéano Pacífico: An CashMIGUEL EDUARDONo ratings yet

- B KTIRIO ΔΙΠΛΩΜΑΤΙΚΗ ΓΙΑ ΑΠΘ ΑΡΧΙΤΕΚΤΟΝΙΚΗ - ΜΟΥΡΚΑΣ ΔΗΜΗΤΡΙΟΣDocument1 pageB KTIRIO ΔΙΠΛΩΜΑΤΙΚΗ ΓΙΑ ΑΠΘ ΑΡΧΙΤΕΚΤΟΝΙΚΗ - ΜΟΥΡΚΑΣ ΔΗΜΗΤΡΙΟΣDimitrios MourkasNo ratings yet

- ΑΜΕΑ ΜΕ 1 ΑΥΤΟΜΑΤΗ ΘΥΡΑ (ενδεικτική κάτοψη)Document1 pageΑΜΕΑ ΜΕ 1 ΑΥΤΟΜΑΤΗ ΘΥΡΑ (ενδεικτική κάτοψη)Ioannis GkatsisNo ratings yet

- Π3 - 7 - Κουρκουλοί - ΣκεπαστήDocument1 pageΠ3 - 7 - Κουρκουλοί - ΣκεπαστήKaterina PapadopoulouNo ratings yet

- Covid GR Daily Report 20200801Document4 pagesCovid GR Daily Report 20200801Nikos KonstantinouNo ratings yet

- 05 - Piano - Música Dispersa - 2021-12-17Document2 pages05 - Piano - Música Dispersa - 2021-12-17Jorge Pazo SilvaNo ratings yet

- ΑΜΕΑ ΜΕ 2 ΑΥΤΟΜΑΤΕΣ ΘΥΡΕΣ ΔΙΑΜΠΕΡΕΣDocument1 pageΑΜΕΑ ΜΕ 2 ΑΥΤΟΜΑΤΕΣ ΘΥΡΕΣ ΔΙΑΜΠΕΡΕΣIoannis GkatsisNo ratings yet

- Ο Μικρός Τυμπανιστής-ΑκορντεόνDocument1 pageΟ Μικρός Τυμπανιστής-ΑκορντεόνvioloopermanNo ratings yet

- Cod 90826 Elettrovalvola Programmabile 1 FDocument2 pagesCod 90826 Elettrovalvola Programmabile 1 FOscar MoralNo ratings yet

- ΑΣ ΕΡΧΟΣΟΥΝ ΓΙΑ ΛΙΓΟ-scrDocument2 pagesΑΣ ΕΡΧΟΣΟΥΝ ΓΙΑ ΛΙΓΟ-scrThanasis PapathanassiouNo ratings yet

- ΑΠΑΡΝΗΜΕΝΗ PDFDocument1 pageΑΠΑΡΝΗΜΕΝΗ PDFbabisg7No ratings yet

- ΞΥΛΟΤΥΠΟΣ Β' ΥΠΟΓΕΙΟΥDocument1 pageΞΥΛΟΤΥΠΟΣ Β' ΥΠΟΓΕΙΟΥStructuralintegration2020 PapNo ratings yet

- Νοσταλγικό σε 5/8Document2 pagesΝοσταλγικό σε 5/8Thanasis PapathanassiouNo ratings yet

- Η Καλόγρια η ΤσιγγάναDocument4 pagesΗ Καλόγρια η ΤσιγγάναApergisNikeNo ratings yet

- ΠΡΩΤΟΠΟΡΟΣ ΚΑΠΝΕΡΓΑΤΗΣ 1 03-1976Document9 pagesΠΡΩΤΟΠΟΡΟΣ ΚΑΠΝΕΡΓΑΤΗΣ 1 03-1976Evagelos MaligourasNo ratings yet

- Αυτή η νύχτα μένειDocument3 pagesΑυτή η νύχτα μένειNikos TsamaidisNo ratings yet

- Αυτή η νύχτα μένειDocument3 pagesΑυτή η νύχτα μένειNikos TsamaidisNo ratings yet

- P.2a - YA τελικόDocument1 pageP.2a - YA τελικόChristos KozartsisNo ratings yet

- Orz - Kymhs o 1Document1 pageOrz - Kymhs o 1Kostas LazarakisNo ratings yet

- Θεε μου μεγαλοδύναμεDocument2 pagesΘεε μου μεγαλοδύναμεArgiris MaipasNo ratings yet

- 15 - Violins - Ain't NobodyDocument1 page15 - Violins - Ain't NobodyMiguelMongeNo ratings yet

- Esercizi CoroDocument1 pageEsercizi CoroAntonio LambresaNo ratings yet

- H-21 Site Infrastructure (Paper@a1) - 231122 - 113733Document1 pageH-21 Site Infrastructure (Paper@a1) - 231122 - 113733Polis PolikarpouNo ratings yet

- RV17-819 GRDocument1 pageRV17-819 GRkoustasdNo ratings yet

- ΓΕΝΙΚΗ ΔΙΑΤΑΞΗ HotspotDocument1 pageΓΕΝΙΚΗ ΔΙΑΤΑΞΗ HotspotMy Samos Blog100% (1)