Professional Documents

Culture Documents

ENC28J60 Silicon Eratta and Data Sheet Clarification

Uploaded by

Guilherme Favaro SilvaCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

ENC28J60 Silicon Eratta and Data Sheet Clarification

Uploaded by

Guilherme Favaro SilvaCopyright:

Available Formats

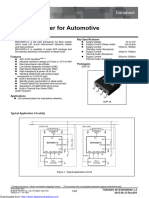

ENC28J60

ENC28J60 Silicon Errata and Data Sheet Clarification

The ENC28J60 devices that you have received conform Note: This document summarizes all silicon

functionally to the current Device Data Sheet errata issues from all revisions of silicon,

(DS39662C), except for the anomalies described in this previous as well as current. Only the

document. issues indicated in the last column of

The silicon issues discussed in the following pages are Table 2 and Table 3 apply to the current

for silicon listed in Table 1. The silicon issues are silicon revision (B7).

summarized in Table 2. Issues specific to technical

The silicon revision level can be retrieved by querying

conformance with IEEE Std. 802.3 are listed in Table 3.

the read-only EREVID register, located at address 12h

Data Sheet clarifications and corrections start on page 9, in Bank 3 of the device’s Control register space. Please

following the discussion of silicon issues. refer to the Device Data Sheet for detailed information

on accessing this register. The values for the various

ENC28J60 silicon revisions are shown in Table 1.

TABLE 1: SILICON EREVID VALUES

Part Number B1 B4 B5 B7

ENC28J60 0000 0010 0000 0100 0000 0101 0000 0110

2010 Microchip Technology Inc. DS80349C-page 1

ENC28J60

TABLE 2: SILICON ISSUE SUMMARY

Affected

Module Feature Issue Issue Summary Revisions

B1 B4 B5 B7

MAC — 1. MAC registers unreliable with slow asynchronous SPI X X

Interface clock

Reset — 2. CLKRDY set early X X X X

Core Operating 3. Industrial (-40C to +85C) temperature range X X

Specifications unsupported

Oscillator CLKOUT pin 4. CLKOUT unavailable in Power Save mode X X X X

Memory Ethernet 5. Receive buffer must start at 0000h X X X X

Buffer

Interrupts — 6. Receive Packet Pending Interrupt Flag (PKTIF) unreliable X X X X

PHY — 7. TPIN+/- automatic polarity detection and correction X X X X

unreliable

PHY — 8. RBIAS resistor value differs between silicon revisions X X

PHY — 9. Internal loopback in half-duplex unreliable X X X X

PHY — 10. Internal loopback in full-duplex unreliable X X X X

PHY LEDs — 11. Combined Collision and Duplex Status mode unavailable X X X X

Transmit — 12. Transmit abort may stall transmit logic X X X X

Logic

PHY — 13. Received link pulses potentially cause collisions X X

Memory Ethernet 14. Even values in ERXRDPT may corrupt receive buffer X X X X

Buffer

Transmit — 15. LATECOL Status bit unreliable X X X X

Logic

PHY LEDs — 16. LED auto-polarity detection unreliable X X X X

DMA — 17. DMA checksum calculations will abort receive packets X X X X

Receive — 18. Pattern match filter allows reception of extra packets X X X X

Filter

SPI — 19. Reset command unavailable in Power Save mode X X X X

Interface

TABLE 3: ETHERNET CONFORMANCE ISSUES

Affected

Issue Issue Summary Revisions

B1 B4 B5 B7

1. TP_IDL transmit waveform violates IEEE STD 802.3™ template X X

2. PHY accepts receive packet in Link Test Fail state X X

3. Collision enforcement is delayed X X

DS80349C-page 2 2010 Microchip Technology Inc.

ENC28J60

Silicon Errata Issues 3. Module: Core (Operating Specifications)

Note: This document summarizes all silicon The device data sheet specifies that industrial

errata issues from all revisions of silicon, operating temperature range (-40C to +85C) is

previous as well as current. Only the supported. However, silicon revisions B1 and B4

issues indicated by the shaded column in only support the commercial temperature range

the following tables apply to the current (0C to +70C).

silicon revision (B7). Work around

Use silicon revision B5 or later.

1. Module: MAC Interface

Affected Silicon Revisions

When the SPI clock from the host microcontroller

is run at frequencies of less than 8 MHz, reading or B1 B4 B5 B7

writing to the MAC registers may be unreliable.

X X

Work around

Two work arounds are presented; others may be

available. 4. Module: Oscillator (CLKOUT Pin)

1. Run the SPI at frequencies of at least 8 MHz.

No output is available on CLKOUT while operating

2. Generate an SPI clock of 25/2 (12.5 MHz), in Power Save mode (ECON2.PWRSV = 0).

25/3 (8.333 MHz), 25/4 (6.25 MHz),

25/5 (5 MHz), etc., and synchronize with the Work around

25 MHz clock entering OSC1 on the If the host controller uses the CLKOUT signal as

ENC28J60. This could potentially be accom- the system clock, do not enable Power Save

plished by feeding the same 25 MHz clock into mode.

the ENC28J60 and host controller. Alterna-

tively, the host controller could potentially be Affected Silicon Revisions

clocked off of the CLKOUT output of the

B1 B4 B5 B7

ENC28J60.

X X X X

Affected Silicon Revisions

B1 B4 B5 B7

X X 5. Module: Memory (Ethernet Buffer)

The receive hardware maintains an internal Write

Pointer which defines the area in the receive buffer

2. Module: Reset where bytes arriving over the Ethernet are written.

This internal Write Pointer should be updated with

After sending an SPI Reset command, the PHY the value stored in ERXST whenever the Receive

clock is stopped but the ESTAT.CLKRDY bit is not Buffer Start Pointer, ERXST, or the Receive Buffer

cleared. Therefore, polling the CLKRDY bit will not End Pointer, ERXND, is written to by the host

work to detect if the PHY is ready. microcontroller. Sometimes, when ERXST or

Additionally, the hardware start-up time of 300 s ERXND is written to, the exact value, 0000h, is

may expire before the device is ready to operate. stored in the internal receive Write Pointer instead

of the ERXST address.

Work around

Work around

After issuing the Reset command, wait at least

1 ms in firmware for the device to be ready. Use the lower segment of the buffer memory for

the receive buffer, starting at address 0000h. For

Affected Silicon Revisions example, use the range (0000h to n) for the

receive buffer and ((n + 1) to 8191) for the transmit

B1 B4 B5 B7

buffer.

X X X X

Affected Silicon Revisions

B1 B4 B5 B7

X X X X

2010 Microchip Technology Inc. DS80349C-page 3

ENC28J60

6. Module: Interrupts 8. Module: PHY

The Receive Packet Pending Interrupt Flag The external resistor value recommended for

(EIR.PKTIF) does not reliably/accurately report RBIAS in the current revision of the data sheet does

the status of pending packets. not apply to certain revisions of silicon. Using an

incorrect resistor value will cause the Ethernet trans-

Work around

mit waveform to violate IEEE 802.3 specification

In the Interrupt Service Routine (ISR), if it is requirements.

unknown if a packet is pending and the source of

the interrupt, switch to Bank 1 and check the value Work around

in EPKTCNT. For silicon revisions, B1 and B4, use a 2.7 k, 1%

If polling to see if a packet is pending, check the external resistor between the RBIAS pin and

value in EPKTCNT. ground. The value shown in the data sheet

(2.32 k,) is correct for revisions B5 and B7.

Note: This errata applies only to the interrupt

flag. If the receive packet pending interrupt Affected Silicon Revisions

is enabled, the INT pin will continue to B1 B4 B5 B7

reliably become asserted when a packet

arrives. The receive packet pending inter- X X

rupt is cleared in the same manner

described in the data sheet.

Affected Silicon Revisions 9. Module: PHY

B1 B4 B5 B7 The PHY Half-Duplex Loopback mode, enabled when

PHCON1.PDPXMD = 0, PHCON2.HDLDIS = 0 and

X X X X PHCON2.FRCLNK = 1, or a link partner is connected,

does not loop packets back to itself reliably.

Work around

7. Module: PHY

Perform loopback diagnostics in full duplex using

The automatic RX polarity detection and correc- an external loopback connector/cable. To avoid

tion features of the PHY layer do not work as looping occasional packets back to one self,

described. When incorrect RX polarity is present, PHCON2.HDLDIS should be set by the host

poor receive network performance, or no receive controller. PHCON2.HDLDIS is clear by default.

activity with some link partners, may occur.

Affected Silicon Revisions

Work around

B1 B4 B5 B7

When designing the application, always verify that

the TPIN+ and TPIN- pins are connected correctly. X X X X

Affected Silicon Revisions

B1 B4 B5 B7 10. Module: PHY

X X X X The PHY Full-Duplex Loopback mode,

enabled when PHCON1.PDPXMD = 1 and

PHCON1.PLOOPBK = 1, does not loop packets

back to itself reliably.

Work around

Perform loopback diagnostics in full duplex using

an external loopback connector/cable.

Affected Silicon Revisions

B1 B4 B5 B7

X X X X

DS80349C-page 4 2010 Microchip Technology Inc.

ENC28J60

11. Module: PHY LEDs 13. Module: PHY

When the PHLCON register is programmed to When transmitting in Half-Duplex mode with some

output the duplex status and collision activity on link partners, the PHY will sometimes incorrectly

the same LED (‘1110’), only the duplex status will interpret a received link pulse as a collision event. If

be displayed (i.e., the LED will be illuminated when less than, or equal to, MACLCON2 bytes have been

in Full-Duplex mode and extinguished when in transmitted when the false collision occurs, the

Half-Duplex mode, regardless of collision activity). MAC will abort the current transmission, wait a ran-

dom back-off delay and then automatically attempt

Work around

to retransmit the packet from the beginning – as it

When Half-Duplex mode is being used, program would for a genuine collision.

the PHLCON register’s LxCFG bits with ‘0011’ to

If greater than MACLCON2 bytes have been

display the collision status. When Full-Duplex mode

transmitted when the false collision occurs, the

is being used, program the PHLCON register’s

event will be considered a late collision by the

LxCFG bits with ‘0101’ to display the duplex status.

MAC and the packet will be aborted without retry-

Affected Silicon Revisions ing. This causes the packet to not be delivered to

the remote node. In some cases, the abort will fail

B1 B4 B5 B7 to reset the transmit state machine.

X X X X Work around

Implement a software retransmit mechanism

whenever a late collision occurs.

12. Module: Transmit Logic

When a late collision occurs, the associated bit in

In Half-Duplex mode, a hardware transmission the transmit status vector will be set. Also, the

abort caused by excessive collisions, a late colli- EIR.TXERIF bit will become set, and if enabled,

sion or excessive deferrals, may stall the internal the transmit error interrupt will occur.

transmit logic. The next packet transmit initiated by If the transmit state machine does not get reset,

the host controller may never succeed the ECON1.TXRTS bit will remain set and no

(ECON1.TXRTS will remain set indefinitely). transmit interrupt will occur (the EIR.TXIF bit will

Work around remain clear).

Before attempting to transmit a packet (setting As a result, software should detect the completion

ECON1.TXRTS), reset the internal transmit logic of a transmit attempt by checking both TXIF and

by setting ECON1.TXRST and then clearing TXERIF. If the Transmit Interrupt (TXIF) did not

ECON1.TXRST. The host controller may wish to occur, software must clear the ECON1.TXRTS bit

issue this Reset before any packet is transmitted to force the transmit state machine into the correct

(for simplicity), or it may wish to conditionally reset state.

the internal transmit logic based on the Transmit The logic in Example 1 (following page) will

Error Interrupt Flag (EIR.TXERIF), which will accomplish a transmission and any necessary

become set whenever a transmit abort occurs. retransmissions with a maximum retry abort.

Clearing ECON1.TXRST may cause a new trans-

mit error interrupt event (EIR.TXERIF will become Affected Silicon Revisions

set). Therefore, the interrupt flag should be cleared

B1 B4 B5 B7

after the Reset is completed.

X X

Affected Silicon Revisions

B1 B4 B5 B7

X X X X

2010 Microchip Technology Inc. DS80349C-page 5

ENC28J60

EXAMPLE 1:

ECON1.TXRST = 1

ECON1.TXRST = 0

EIR.TXERIF = 0

EIR.TXIF = 0

ECON1.TXRTS = 1

while(EIR.TXIF = 0 and EIR.TXERIF = 0)

NOP

ECON1.TXRTS = 0

read tsv

for retrycount = 0 to 15

if (EIR.TXERIF and tsv<Transmit Late Collision>) then

ECON1.TXRST = 1

ECON1.TXRST = 0

EIR.TXERIF = 0

EIR.TXIF = 0

ECON1.TXRTS = 1

while(EIR.TXIF = 0 and EIR.TXERIF = 0)

NOP

ECON1.TXRTS = 0

read tsv

else

exit for

end if

next retrycount

14. Module: Memory (Ethernet Buffer) 15. Module: Transmit Logic

The receive hardware may corrupt the circular If a collision occurs after 64 bytes have been

receive buffer (including the Next Packet Pointer transmitted, the transmit logic may not set the Late

and receive status vector fields) when an even value Collision Error status bit (ESTAT.LATECOL).

is programmed into the ERXRDPTH:ERXRDPTL

Work around

registers.

Whenever a late collision has potentially occurred

Work around (both EIR.TXERIF and ESTAT.TXABRT bits will be

Ensure that only odd addresses are written to the set), read the transmit status vector and check the

ERXRDPT registers. Assuming that ERXND con- transmit late collision bit (bit 29).

tains an odd value, many applications can derive a

Affected Silicon Revisions

suitable value to write to ERXRDPT by subtracting

one from the Next Packet Pointer (a value always B1 B4 B5 B7

ensured to be even because of hardware padding)

and then compensating for a potential ERXST to X X X X

ERXND wrap-around. Assuming that the receive

buffer area does not span the 1FFFh to 0000h mem-

ory boundary, the logic in Example 2 will ensure that

ERXRDPT is programmed with an odd value:

EXAMPLE 2:

if (Next Packet Pointer = ERXST)

then:

ERXRDPT = ERXND

else:

ERXRDPT = Next Packet Pointer – 1

Affected Silicon Revisions

B1 B4 B5 B7

X X X X

DS80349C-page 6 2010 Microchip Technology Inc.

ENC28J60

16. Module: PHY LEDs the enabled filter criteria. This will occur if the

receive packet is less than or equal to 64+EPMO

With some LEDs, the LED auto-polarity detection bytes long. For typical applications using the

circuit misdetects the connected polarity of the Pattern Match and Unicast receive filters simul-

LED upon Reset. As a result, the LED output pin taneously with a zero Pattern Match offset, this

will sink current when it should be sourcing current will result in the reception of unwanted 64-byte

and vice versa. The LED will visually appear Address Resolution Protocol (ARP) broadcast

inverted. For example, an LED configured to dis- frames, among possible others.

play the link status will be illuminated when no link

is present and extinguished when a link has been Work around

established. The likelihood of a misdetection will When using the pattern match receive filter, discard

vary over temperature. If LEDB is misdetected, the any unwanted packets in software.

PHCON1.PDPXMD bit will also reset to the

incorrect state. Affected Silicon Revisions

Work around B1 B4 B5 B7

Place a resistor in parallel with the LED. The X X X X

resistor value needed is not critical. Resistors

between 1 k and 100 k are recommended.

Affected Silicon Revisions 19. Module: SPI Interface

B1 B4 B5 B7 When operating in Power Save mode

(ECON2.PWRSV = 1), issuing the SPI System

X X X X Reset command will have no effect.

Work around

17. Module: DMA Clear the PWRSV bit and wait for the device’s

power regulator to stabilize before issuing an SPI

If the DMA module is operated in Checksum mode System Reset command.

(ECON1.CSUMEN, DMAST = 1) at any time while

a packet is currently being received from the For a device in an unknown state, the recommended

Ethernet (ESTAT.RXBUSY = 1), the packet being Reset sequence is:

received will be aborted. The packet abort will 1. Use the Bit Field Clear command and clear

cause the Receive Error Interrupt Flag ECON2.PWRSV (ECON2<5>).

(EIR.RXERIF) to be set, the interrupt will occur, if 2. Wait at least 300 µs for power to be restored.

enabled, and the Buffer Error status bit 3. Issue the System Reset command.

(ESTAT.BUFER) will also become set. The packet 4. Wait 1 ms for the Reset to complete and to

will be permanently lost. ensure that all modules are ready to be used.

Work around 5. Confirm that the Reset has taken place. This

can be accomplished by reading a register and

Do not use the DMA module to perform checksum

checking for an expected Reset value. For

calculations; perform checksums in software. This

example, read ESTAT and confirm that the

problem does not affect the DMA copy operation

CLKRDY bit (bit 0) is set and the unimplemented

(ECON1.CSUMEN = 0).

bit (bit 3) is clear.

Affected Silicon Revisions If one or both of these conditions are not met,

this may indicate that the ENC28J60 is not

B1 B4 B5 B7 ready yet (e.g., the microcontroller has exited

X X X X POR while ENC28J60 is still powering up). In

this case, repeat the procedure from Step 1.

Affected Silicon Revisions

18. Module: Receive Filter B1 B4 B5 B7

If using the Pattern Match receive filter, some X X X X

packets may be accepted that should be

rejected. Specifically, if ERXFCON.ANDOR = 0,

ERXFCON.PMEN = 1 and at least one of the

Hash Table, Magic PacketTM, Broadcast, Multi-

cast or Unicast receive filters are enabled, then

packets can be accepted that do not meet any of

2010 Microchip Technology Inc. DS80349C-page 7

ENC28J60

Ethernet Conformance Issues In the unlikely event that this situation does occur,

higher layer protocols would protect the system

The following conformance issues were noted in testing from accepting unwanted data. It is unlikely that

the B1 and B4 silicon revisions for compliance with IEEE this failure will have significant impact on a

Standard 802.3. These issues are not present after networked application. No failures have been

Revision B4 and are included for informational purposes. observed due to this issue.

1. Issue: TP_IDL Pattern Work around

Use silicon revision B5 or later.

The observed TP_IDL pattern transmitted by

ENC28J60 was observed to not stay within the Affected Silicon Revisions

standard defined template when using the TPM

(Twisted Pair Model) and TP Test Load 2. B1 B4 B5 B7

Reference: IEEE Std 802.3, §14.3.1.2.1, X X

Figures 14-10 and 14-11

Potential Application Impact

The TP_IDL test requires a total of six separate 3. Issue: Collision Handling

subtests, using three different test loads with and The delay from the collision event to collision

without TPM. The fact that the device consistently enforcement with the jam pattern is approximately

passed five of the six sub tests, while narrowly 50 BT (Bit Times), which is greater than the

missing the sixth, leads to the conclusion that this specified limit of 36 BT.

is a minor issue. No failures have been observed

due to this issue. Reference: IEEE Std 802.3, Annex B, § B.1.2

Potential Application Impact

Work around

A collision in a half-duplex 10Base-T is not an

Use silicon revision B5 or later.

unexpected event. It exists as a normal part of the

Affected Silicon Revisions network operation. The purpose of the jam pattern

is to ensure that the duration of the collision is

B1 B4 B5 B7 sufficient to be noticed by the other transmitting

X X station(s) involved in the collision. A longer delay

between the collision event and the start of jam

pattern would cause the duration of the collision to

be longer.

2. Issue: Exiting Link Test Fail State

After each collision, both transmitting stations

The ENC28J60 was observed to improperly would back off and wait a random amount of time

accept a frame with no preceding LTPs (Link Test before attempting to transmit again. The minimum

Pulse). When a device is in the Link Test Fail state, Idle time between each Ethernet frame is 9.6 s.

it should exit this state when a valid packet is The longer collision duration of 14 BT, or 1.4 s,

received, however, the first packet should not be can be considered as a small fraction of time

accepted. The second and subsequent packets wasted for each collision. It is unlikely that this

should be accepted while the device is in the Link issue will have significant impact on networked

Test Pass state. applications. No failures have been observed due

to this issue.

Reference: IEEE Std 802.3, Figure 14-6

Potential Application Impact Work around

Link Test Pulse is an integral part of every Use silicon revision B5 or later.

10Base-T system. It is used to notify a link partner Affected Silicon Revisions

of the presence of a 10Base-T device. An absence

of LTPs signifies that the Ethernet cable is not con- B1 B4 B5 B7

nected or a link partner is missing. Even when a

X X

cable is not connected, a 10Base-T device would

continuously send out LTPs. This fact makes it

unlikely that there will ever be a situation in which

a device would be receiving valid Ethernet frames

without already being in the Link Test Pass state.

DS80349C-page 8 2010 Microchip Technology Inc.

ENC28J60

Data Sheet Clarifications

The following typographic corrections and clarifications

are to be noted for the latest version of the device data

sheet (DS39662C):

Note: Corrections are shown in bold. Where

possible, the original bold text formatting

has been removed for clarity.

1. Module: Receive Filter

In Section 8.2 “Pattern Match Filter”, it is stated

that the pattern match offset programmed into the

EPMOH:EPMOL registers should be loaded with

the offset from the beginning of the destination

address field. This implies that any value can be

used. In fact, for correct operation, it is required

that the EPMOH:EPMOL registers be

programmed with an even value only (i.e.,

EPMOL<0> must always be ‘0’).

2010 Microchip Technology Inc. DS80349C-page 9

ENC28J60

APPENDIX A: DOCUMENT

REVISION HISTORY

Rev A Document (10/2007)

Original revision. Silicon errata issues 1 (Reset),

2 (Oscillator – CLKOUT Pin), 3 (Memory – Ethernet

Buffer), 4 (Interrupts), 5-8 (PHY), 9 (PHY LEDs),

10 (Transmit Logic), 11 (Memory – Ethernet Buffer),

12 (Transmit Logic), 13-14 (PHY) and 15 (DMA).

Rev B Document (07/2008)

Updated the revision of the referenced data sheet.

Changed the revision identifier for this device as the

previous version contained an error.

Rev C Document (07/2010)

Revises the document to include all released silicon

revisions of the device, starting with revision B1, and

removes “silicon revision B7” from the title. Order of

issues has been re-aligned to better reflect sequential

issue history:

• 1 (MAC Interface)

• 2 (Reset)

• 3 (Core)

• 4 (Oscillator)

• 5 (Memory)

• 6 (Interrupts)

• 7-10 (PHY)

• 11 (PHY LEDs)

• 12 (Transmit Logic)

• 13 (PHY)

• 14 (Memory – Ethernet Buffer)

• 15 (Transmit Logic)

• 16 (PHY)

• 17 (DMA)

Adds new silicon issues 18 (Receive Filter) and

19 (SPI Interface) to all silicon revisions.

Makes minor clarifying changes and typographic

corrections to issues 2, 3, 4, 5, 7, 13 and 14.

Revises issue 8 (PHY) to reflect that the current

revision of the data sheet correctly describes the

current silicon revision.

Adds Ethernet Conformance Issues 1 (TP_IDL

Pattern), 2 (Exiting Link Test Fail State) and 3 (Collision

Handling) from previous revisions B1 and B4.

Adds Data Sheet Clarification 1 (Receive Filters).

This document replaces these errata documents:

• DS80254, “ENC28J60 Revision B1 Silicon Errata”

• DS80257, “ENC28J60 Revision B4 Silicon Errata”

• DS80264, “ENC28J60 Revision B5 Silicon Errata”

DS80349C-page 10 2010 Microchip Technology Inc.

Note the following details of the code protection feature on Microchip devices:

• Microchip products meet the specification contained in their particular Microchip Data Sheet.

• Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the

intended manner and under normal conditions.

• There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our

knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip’s Data

Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

• Microchip is willing to work with the customer who is concerned about the integrity of their code.

• Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as “unbreakable.”

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our

products. Attempts to break Microchip’s code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts

allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device Trademarks

applications and the like is provided only for your convenience

The Microchip name and logo, the Microchip logo, dsPIC,

and may be superseded by updates. It is your responsibility to

KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART,

ensure that your application meets with your specifications.

PIC32 logo, rfPIC and UNI/O are registered trademarks of

MICROCHIP MAKES NO REPRESENTATIONS OR

Microchip Technology Incorporated in the U.S.A. and other

WARRANTIES OF ANY KIND WHETHER EXPRESS OR countries.

IMPLIED, WRITTEN OR ORAL, STATUTORY OR

OTHERWISE, RELATED TO THE INFORMATION, FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor,

INCLUDING BUT NOT LIMITED TO ITS CONDITION, MXDEV, MXLAB, SEEVAL and The Embedded Control

QUALITY, PERFORMANCE, MERCHANTABILITY OR Solutions Company are registered trademarks of Microchip

FITNESS FOR PURPOSE. Microchip disclaims all liability Technology Incorporated in the U.S.A.

arising from this information and its use. Use of Microchip Analog-for-the-Digital Age, Application Maestro, CodeGuard,

devices in life support and/or safety applications is entirely at dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN,

the buyer’s risk, and the buyer agrees to defend, indemnify and ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial

hold harmless Microchip from any and all damages, claims, Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified

suits, or expenses resulting from such use. No licenses are logo, MPLIB, MPLINK, mTouch, Octopus, Omniscient Code

conveyed, implicitly or otherwise, under any Microchip Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit,

intellectual property rights. PICtail, REAL ICE, rfLAB, Select Mode, Total Endurance,

TSHARC, UniWinDriver, WiperLock and ZENA are

trademarks of Microchip Technology Incorporated in the

U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated

in the U.S.A.

All other trademarks mentioned herein are property of their

respective companies.

© 2010, Microchip Technology Incorporated, Printed in the

U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 978-1-60932-370-7

Microchip received ISO/TS-16949:2002 certification for its worldwide

headquarters, design and wafer fabrication facilities in Chandler and

Tempe, Arizona; Gresham, Oregon and design centers in California

and India. The Company’s quality system processes and procedures

are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping

devices, Serial EEPROMs, microperipherals, nonvolatile memory and

analog products. In addition, Microchip’s quality system for the design

and manufacture of development systems is ISO 9001:2000 certified.

2010 Microchip Technology Inc. DS80349C-page 11

WORLDWIDE SALES AND SERVICE

AMERICAS ASIA/PACIFIC ASIA/PACIFIC EUROPE

Corporate Office Asia Pacific Office India - Bangalore Austria - Wels

2355 West Chandler Blvd. Suites 3707-14, 37th Floor Tel: 91-80-3090-4444 Tel: 43-7242-2244-39

Chandler, AZ 85224-6199 Tower 6, The Gateway Fax: 91-80-3090-4123 Fax: 43-7242-2244-393

Tel: 480-792-7200 Harbour City, Kowloon Denmark - Copenhagen

India - New Delhi

Fax: 480-792-7277 Hong Kong Tel: 45-4450-2828

Tel: 91-11-4160-8631

Technical Support: Tel: 852-2401-1200 Fax: 45-4485-2829

Fax: 91-11-4160-8632

http://support.microchip.com Fax: 852-2401-3431

India - Pune France - Paris

Web Address:

Australia - Sydney Tel: 91-20-2566-1512 Tel: 33-1-69-53-63-20

www.microchip.com

Tel: 61-2-9868-6733 Fax: 91-20-2566-1513 Fax: 33-1-69-30-90-79

Atlanta Fax: 61-2-9868-6755

Japan - Yokohama Germany - Munich

Duluth, GA

China - Beijing Tel: 49-89-627-144-0

Tel: 678-957-9614 Tel: 81-45-471- 6166

Tel: 86-10-8528-2100 Fax: 49-89-627-144-44

Fax: 678-957-1455 Fax: 81-45-471-6122

Fax: 86-10-8528-2104 Italy - Milan

Boston Korea - Daegu

China - Chengdu Tel: 39-0331-742611

Westborough, MA Tel: 82-53-744-4301

Tel: 86-28-8665-5511 Fax: 39-0331-466781

Tel: 774-760-0087 Fax: 82-53-744-4302

Fax: 86-28-8665-7889 Netherlands - Drunen

Fax: 774-760-0088 Korea - Seoul

China - Chongqing Tel: 82-2-554-7200 Tel: 31-416-690399

Chicago

Tel: 86-23-8980-9588 Fax: 82-2-558-5932 or Fax: 31-416-690340

Itasca, IL

Tel: 630-285-0071 Fax: 86-23-8980-9500 82-2-558-5934 Spain - Madrid

Fax: 630-285-0075 China - Hong Kong SAR Tel: 34-91-708-08-90

Malaysia - Kuala Lumpur

Tel: 852-2401-1200 Tel: 60-3-6201-9857 Fax: 34-91-708-08-91

Cleveland

Independence, OH Fax: 852-2401-3431 Fax: 60-3-6201-9859 UK - Wokingham

Tel: 216-447-0464 China - Nanjing Tel: 44-118-921-5869

Malaysia - Penang

Fax: 216-447-0643 Tel: 86-25-8473-2460 Fax: 44-118-921-5820

Tel: 60-4-227-8870

Dallas Fax: 86-25-8473-2470 Fax: 60-4-227-4068

Addison, TX China - Qingdao Philippines - Manila

Tel: 972-818-7423 Tel: 86-532-8502-7355 Tel: 63-2-634-9065

Fax: 972-818-2924 Fax: 86-532-8502-7205 Fax: 63-2-634-9069

Detroit China - Shanghai Singapore

Farmington Hills, MI Tel: 86-21-5407-5533 Tel: 65-6334-8870

Tel: 248-538-2250 Fax: 86-21-5407-5066 Fax: 65-6334-8850

Fax: 248-538-2260

China - Shenyang Taiwan - Hsin Chu

Kokomo Tel: 86-24-2334-2829 Tel: 886-3-6578-300

Kokomo, IN Fax: 86-24-2334-2393 Fax: 886-3-6578-370

Tel: 765-864-8360

Fax: 765-864-8387 China - Shenzhen Taiwan - Kaohsiung

Tel: 86-755-8203-2660 Tel: 886-7-536-4818

Los Angeles Fax: 86-755-8203-1760 Fax: 886-7-536-4803

Mission Viejo, CA

Tel: 949-462-9523 China - Wuhan Taiwan - Taipei

Fax: 949-462-9608 Tel: 86-27-5980-5300 Tel: 886-2-2500-6610

Fax: 86-27-5980-5118 Fax: 886-2-2508-0102

Santa Clara

Santa Clara, CA China - Xian Thailand - Bangkok

Tel: 408-961-6444 Tel: 86-29-8833-7252 Tel: 66-2-694-1351

Fax: 408-961-6445 Fax: 86-29-8833-7256 Fax: 66-2-694-1350

Toronto China - Xiamen

Mississauga, Ontario, Tel: 86-592-2388138

Canada Fax: 86-592-2388130

Tel: 905-673-0699 China - Zhuhai

Fax: 905-673-6509 Tel: 86-756-3210040

Fax: 86-756-3210049

01/05/10

DS80349C-page 12 2010 Microchip Technology Inc.

You might also like

- 100 Hacking Tools and Resources - HackerOneDocument10 pages100 Hacking Tools and Resources - HackerOneAfuza Gabriel100% (1)

- Windows Command Line ReferenceDocument11 pagesWindows Command Line ReferenceCSArchive.Net100% (2)

- 100 - 1. Lift Controller ManualDocument41 pages100 - 1. Lift Controller ManualDjordje GavrilovicNo ratings yet

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxFrom EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxRating: 4 out of 5 stars4/5 (1)

- Bnwas 2Document22 pagesBnwas 2gopuNo ratings yet

- Courier Relay Integration Procedure PDFDocument40 pagesCourier Relay Integration Procedure PDFganesh kumarNo ratings yet

- 8051 Microcontroller: An Applications Based IntroductionFrom Everand8051 Microcontroller: An Applications Based IntroductionRating: 5 out of 5 stars5/5 (6)

- Chapter 18 Network Security and ProtocolsDocument62 pagesChapter 18 Network Security and Protocolshclraj406No ratings yet

- CCNA 3 Exploration ESwitching Final Exam Form2 V 4.0Document17 pagesCCNA 3 Exploration ESwitching Final Exam Form2 V 4.0sEcZxNo ratings yet

- Teamlink Fabio-1cx ManualDocument18 pagesTeamlink Fabio-1cx ManualrajasankarNo ratings yet

- WHITE Beet P Datasheet Rev.1.02 20220630Document17 pagesWHITE Beet P Datasheet Rev.1.02 20220630Adarsh100% (1)

- PIC18F87J50 Family Silicon Errata and Data Sheet ClarificationDocument16 pagesPIC18F87J50 Family Silicon Errata and Data Sheet ClarificationErnesto RosalesNo ratings yet

- PIC18F2455/2550/4455/4550: PIC18F2455/2550/4455/4550 Family Silicon Errata and Data Sheet ClarificationDocument26 pagesPIC18F2455/2550/4455/4550: PIC18F2455/2550/4455/4550 Family Silicon Errata and Data Sheet ClarificationqwertyNo ratings yet

- PIC18F46J50 ErrataDocument12 pagesPIC18F46J50 Erratafrank_grimesNo ratings yet

- PIC18F66K80 Family Silicon Errata and Data Sheet ClarificationDocument13 pagesPIC18F66K80 Family Silicon Errata and Data Sheet ClarificationFernando PeixeiroNo ratings yet

- MDocument16 pagesMHugo LoureiroNo ratings yet

- ATmega4208 09 DS80000867CDocument17 pagesATmega4208 09 DS80000867CNeelakanta KallaNo ratings yet

- Specification: 46" HDTV-Panel T460HW01Document27 pagesSpecification: 46" HDTV-Panel T460HW01Matt KuoNo ratings yet

- EY-RC 500: Room Automation Station, Ecos500: FeaturesDocument14 pagesEY-RC 500: Room Automation Station, Ecos500: FeaturesRhizhailNo ratings yet

- Ifx1040 DS 10Document20 pagesIfx1040 DS 10josecente123321No ratings yet

- ENC28J60 Rev. B7 Silicon ErrataDocument8 pagesENC28J60 Rev. B7 Silicon ErrataQabc123456No ratings yet

- MKT3811 Week4 03.11.2021 RDocument62 pagesMKT3811 Week4 03.11.2021 REmirhan AlmaNo ratings yet

- SAK-C167CR-LC Infineon Elenota - PLDocument22 pagesSAK-C167CR-LC Infineon Elenota - PLpiotreNo ratings yet

- Iso Serial Link Interface: Semiconductor Technical DataDocument4 pagesIso Serial Link Interface: Semiconductor Technical Datawramadhani65No ratings yet

- XC7K325TDocument70 pagesXC7K325TmatrixNo ratings yet

- 80C31BH/80C51BH/87C51 MCS 51 Chmos Single-Chip 8-Bit MicrocontrollerDocument16 pages80C31BH/80C51BH/87C51 MCS 51 Chmos Single-Chip 8-Bit MicrocontrollercarlosgnNo ratings yet

- 11 Appendix Troubleshooting FCoEDocument200 pages11 Appendix Troubleshooting FCoESanjeev PatilNo ratings yet

- Pcred 301002 enDocument2 pagesPcred 301002 enLimingDengNo ratings yet

- VIRTEXIIDocument34 pagesVIRTEXIIDhanapackiyam VNo ratings yet

- Ipboxb: Ip - Box B E/001 1/20Document20 pagesIpboxb: Ip - Box B E/001 1/20Claudio SaezNo ratings yet

- Sepam Series 80-Sepd302058enDocument4 pagesSepam Series 80-Sepd302058enDiegoNo ratings yet

- 01 Chapter 1Document50 pages01 Chapter 1uabdulgwadNo ratings yet

- Datasheet GLT725608Document12 pagesDatasheet GLT725608nicinha_No ratings yet

- TU Series Hardware Specification: Itron SMART TFT Modules TU800X480C-RT RangeDocument16 pagesTU Series Hardware Specification: Itron SMART TFT Modules TU800X480C-RT Rangeusman sajidNo ratings yet

- Cop310 410 411Document20 pagesCop310 410 411Riadalg RiadNo ratings yet

- Ipc I 165 Pci Manual EnglishDocument15 pagesIpc I 165 Pci Manual EnglishCHAIRMANNo ratings yet

- TP 1Document13 pagesTP 1Sellami WafaNo ratings yet

- BuR X20 HardwareDocument14 pagesBuR X20 HardwarecelinNo ratings yet

- Fiber Optic Ieee c37.94 g.703 E1 Multiplexer Pdf2 133Document18 pagesFiber Optic Ieee c37.94 g.703 E1 Multiplexer Pdf2 133nnt236No ratings yet

- RBX1 Technical Data ENUDocument21 pagesRBX1 Technical Data ENUJoão Márcio JorgeNo ratings yet

- Cio 116 Data Sheet 4921240524 UkDocument10 pagesCio 116 Data Sheet 4921240524 UkSergio Andres MurilloNo ratings yet

- en 01Document2 pagesen 01Mauro Portugal LagardaNo ratings yet

- BX 2 EN Manual 101112Document50 pagesBX 2 EN Manual 101112Ibrahim ALhaj Gharib100% (2)

- Daewoo Dla32c7lmbd PDFDocument56 pagesDaewoo Dla32c7lmbd PDFJesus PerezNo ratings yet

- Imo Wprowadzenie Do ProgramowaniaDocument15 pagesImo Wprowadzenie Do ProgramowaniaNguyễn VỹNo ratings yet

- Industrial 2-/4-Port RS232/422/485 Serial Device Server: ICS-2200T/ICS-2400TDocument16 pagesIndustrial 2-/4-Port RS232/422/485 Serial Device Server: ICS-2200T/ICS-2400Tharis_fikriNo ratings yet

- 4-Internal Ram, Register Banks & Stack Operations-19-12-2022Document26 pages4-Internal Ram, Register Banks & Stack Operations-19-12-2022BRO CUBIESNo ratings yet

- Sepam1000 20 Technical Short DataDocument2 pagesSepam1000 20 Technical Short DataGelu BordeaNo ratings yet

- NX 3020Document14 pagesNX 3020Ahmed KamalNo ratings yet

- 30 Installation Instructions, PowerFlex DC Field Controller 23pfc-In001 - En-PDocument42 pages30 Installation Instructions, PowerFlex DC Field Controller 23pfc-In001 - En-PМиланNo ratings yet

- DXC Panel Technical PresentationDocument87 pagesDXC Panel Technical PresentationAllen BradleyNo ratings yet

- AA 003823 PB 3 ANX7411 Product BriefDocument2 pagesAA 003823 PB 3 ANX7411 Product BriefChau Nguyen MinhNo ratings yet

- ds187 XC7Z010 XC7Z020 Data SheetDocument72 pagesds187 XC7Z010 XC7Z020 Data SheetAshokNo ratings yet

- Mircroprocessor Systems and InterfacingDocument72 pagesMircroprocessor Systems and InterfacingMuaz ShahidNo ratings yet

- ND-12.007.01 CAMAC CC NORD-10 CAMAC Crate NORD-10 Interface General InformationDocument32 pagesND-12.007.01 CAMAC CC NORD-10 CAMAC Crate NORD-10 Interface General InformationGöran AxelssonNo ratings yet

- Ej070na-01c CmimeiDocument24 pagesEj070na-01c CmimeiИгорь ПлэчинтэNo ratings yet

- Siprotec 5 Configuration Nov 18, 2020 3:09 AMDocument4 pagesSiprotec 5 Configuration Nov 18, 2020 3:09 AMPằngPằngChiuChiuNo ratings yet

- Datasheet - HK bd41030fj-c 9014179Document46 pagesDatasheet - HK bd41030fj-c 9014179dexkezzNo ratings yet

- KM3x - 256 Based Three-Phase Power Meter Hardware Design Reference ManualDocument17 pagesKM3x - 256 Based Three-Phase Power Meter Hardware Design Reference ManualNovik PrviNo ratings yet

- Lab 3.5.1: Basic Frame RelayDocument24 pagesLab 3.5.1: Basic Frame RelaychipomaNo ratings yet

- MC34152, MC33152, NCV33152 High Speed Dual MOSFET Drivers: PDIP 8 P Suffix CASE 626Document12 pagesMC34152, MC33152, NCV33152 High Speed Dual MOSFET Drivers: PDIP 8 P Suffix CASE 626Diego AlejandroNo ratings yet

- Fiber Optic Ieee c37.94 g.703 E1 Multiplexer pdf2 133 PDFDocument18 pagesFiber Optic Ieee c37.94 g.703 E1 Multiplexer pdf2 133 PDFxvehicleNo ratings yet

- P743 CortecDocument5 pagesP743 Cortecajitkalel1986No ratings yet

- Token Ring Technology ReportFrom EverandToken Ring Technology ReportNo ratings yet

- Fatek e 4Document7 pagesFatek e 4Damiana CunhaNo ratings yet

- Data Protection Advisor 6.0 Installation and Administration GuideDocument134 pagesData Protection Advisor 6.0 Installation and Administration GuideCristian CostacheNo ratings yet

- GFL TipsDocument3 pagesGFL TipsMeltyNo ratings yet

- CFRT Data Center Infrastructure MGMTDocument35 pagesCFRT Data Center Infrastructure MGMTmrbubosNo ratings yet

- BSODDocument6 pagesBSODNychi SitchonNo ratings yet

- Code Connect and Deploy in The CloudDocument31 pagesCode Connect and Deploy in The CloudmarkkuimNo ratings yet

- DH-DVR0404 0804 1604hf-ADocument4 pagesDH-DVR0404 0804 1604hf-AMohammad PiraniNo ratings yet

- Lexmark XM1140 XM1145 XM3150 BrochureDocument8 pagesLexmark XM1140 XM1145 XM3150 BrochurebiancaachimNo ratings yet

- 2004 - Airbus - A380 - An Afdx Based Flight Test Computer - Autest.2004.1436931 PDFDocument4 pages2004 - Airbus - A380 - An Afdx Based Flight Test Computer - Autest.2004.1436931 PDFHakan SolmazNo ratings yet

- Ts 128554v160700pDocument37 pagesTs 128554v160700pranbirrathiNo ratings yet

- Securing SDN Southbound and Data Plane CommunicatiDocument13 pagesSecuring SDN Southbound and Data Plane CommunicatiRASHEED YUSUFNo ratings yet

- 58MM MINI Portable Thermal Printer Instruction Manual-20170214Document16 pages58MM MINI Portable Thermal Printer Instruction Manual-20170214Abdul Maghfir Zakir100% (1)

- NGFW Overview Next Generation Firewall 5.8: NGFW Security Engine NGFW Security EngineDocument25 pagesNGFW Overview Next Generation Firewall 5.8: NGFW Security Engine NGFW Security EngineomarptcNo ratings yet

- AMD Processor Performance Evaluation GuideDocument54 pagesAMD Processor Performance Evaluation Guideyogesh55555No ratings yet

- Univerge sv9100Document766 pagesUniverge sv9100RakaPradnyaPutraAditaNo ratings yet

- Punjab College Lahore.: Send Up Exams (2014 15)Document8 pagesPunjab College Lahore.: Send Up Exams (2014 15)Palvisha FarooqNo ratings yet

- Installation Manual VI-505/IC-412: IndexDocument22 pagesInstallation Manual VI-505/IC-412: IndexEdwin CardozoNo ratings yet

- Shortcut KeysDocument3 pagesShortcut KeysNicholas PriceNo ratings yet

- Pcs300 Man Software en 07 08Document32 pagesPcs300 Man Software en 07 08Gustavo VelizNo ratings yet

- IMEI Database VVDocument2 pagesIMEI Database VVazharali4434No ratings yet

- Pxe & Aoe: Preboot Execution Environment ATA Over EthernetDocument19 pagesPxe & Aoe: Preboot Execution Environment ATA Over Ethernetiret retiNo ratings yet

- AzureDocument19 pagesAzureEdgar Orlando Bermudez Aljuri100% (1)

- Meraki Datasheet ms210Document6 pagesMeraki Datasheet ms210Shiva PrasadNo ratings yet

- Network Time Protocol (NTP) Issues Troubleshooting and Debugging GuideDocument20 pagesNetwork Time Protocol (NTP) Issues Troubleshooting and Debugging GuidedinoNo ratings yet

- Sim7022 Spec en 20210611Document2 pagesSim7022 Spec en 20210611rodrigo.verniniNo ratings yet

- OMG! Is Texting Wrecking Our Language?: Sali Tagliamonte University of TorontoDocument2 pagesOMG! Is Texting Wrecking Our Language?: Sali Tagliamonte University of TorontoRiaz Hussain SoomroNo ratings yet