Professional Documents

Culture Documents

PI6C485352

Uploaded by

david.gjeorgevskiCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

PI6C485352

Uploaded by

david.gjeorgevskiCopyright:

Available Formats

PI6C485352

2.5V/3.3V, 500 MHz Twelve 2-to-1 Differential

LVPECL Clock Multiplexer

Features Description

ÎÎPin-to-pin compatible to ICS85352I The PI6C485352 is a high-performance low-skew LVPECL

ÎÎFMAX ≤ 500 MHz fanout buffer. PI6C485352 features two selectable differential

inputs and translates to twelve LVPECL output pairs. The inputs

ÎÎPropagation Delay < 4ns

can also be configured to single-ended with external resistor

ÎÎOutput-to-output skew < 100ps bias circuit. The CLK input accepts LVPECL, LVDS, LVHSTL,

ÎÎ12 pairs of differential LVPECL outputs SSTL or HCSL signals. The PI6C485352 is ideal for differential

to LVPECL translations and/or LVPECL clock distribution.

ÎÎSelectable differential CLK and /CLK inputs

Typical clock translation and distribution applications are data-

ÎÎCLK, /CLK pair accepts LVDS, LVPECL, LVHSTL, SSTL and

communications and telecommunications.

HCSL input level

ÎÎSelect input accept CMOS/LVTTL levels Applications

ÎÎ2.5V/3.3V power supply ÎÎNetworking systems including switches and Routers

ÎÎOperating Temperature: -40°C to +85°C ÎÎHigh frequency backplane based computing and telecom

platforms

ÎÎPackaging (Pb-free & Green):

— 48-pin TQFP (FA)

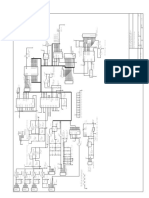

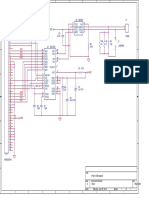

Block Diagram Pin Configuration (48-Pin TQFP)

/CLK1

/CLK0

CLK1

CLK0

SEL2

SEL1

SEL0

SEL6

SEL7

SEL8

VCCO

VCDD

48 47 46 45 44 43 42 41 40 39 38 37

12 Q0 1 36 Q6

SEL [0:11] /Q0 2 /Q6

35

Q1 3 34 Q7

CLK0 /Q1 4 33 /Q7

0

/CLK0

Q0 Q2 5 32 Q8

/Q0 /Q2

CLK1 6 31 /Q8

1

/CLK1 Q3 7 30 Q9

/Q3 8 29 /Q9

Q4 9 28 Q10

/Q4 10 27 /Q10

0

Q11 Q5 11 26 Q11

/Q11 /Q5 12 25

1 /Q11

13 14 15 16 17 18 19 20 21 22 23 24

VEE

VCC

SEL5

SEL4

SEL3

SEL9

SEL10

SEL11

VCC

VEE

VCCO

VCCO

PI6C485352 Rev. A 01/24/13

13-0003 1

PI6C485352

2.5V/3.3V, 500 MHz Twelve 2-to-1 Differential LVPECL Clock Multiplexer

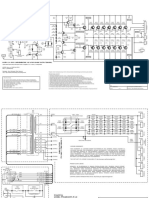

Pinout Table

Pin # Pin Name Type Description

1, 2 Q0, /Q0

3, 4 Q1, /Q1

5, 6 Q2, /Q2

7, 8 Q3, /Q3

9, 10 Q4, /Q4

11, 12 Q5, /Q5 Differential LVPECL Output pairs. LVPECL inter-

Output

25, 26 /Q11, Q11 face levels

27, 28 /Q10, Q10

29, 30 /Q9,Q9

31, 32 /Q8,Q8

33, 34 /Q7,Q7

35, 36 /Q6,Q6

13, 24

VCCO Output supply pins

37, 48

Power

14, 23 VEE Ground pins

15, 22 VCC Core supply pins

16, 17 SEL5, SEL4,

18, 19 SEL3, SEL9,

20, 21 SEL10, SEL11, Clock select inputs. LVCMOS/LVTTL interface

Pulldown

40, 41 SEL8, SEL7, levels

42, 43 SEL6, SEL0,

44, 45 SEL1, SEL2

38 CLK1 Pulldown Non-inverting differential clock input

39 /CLK1 Pullup/Pulldown Inverting differential clock input

46 CLK0 Pulldown Non-inverting differential clock input

47 /CLK0 Pullup/Pulldown Inverting differential clock input

PI6C485352 Rev. A 01/24/13

13-0003 2

PI6C485352

2.5V/3.3V, 500 MHz Twelve 2-to-1 Differential LVPECL Clock Multiplexer

Maximum Ratings (Above which the useful life may be impaired. For user guidelines, not tested)

Symbol Parameter Test Condition Min. Typ. Max. Units

VCC/ VCCo Supply Voltage Referenced to GND 4.6

V

VIN Input voltage Referenced to GND -0.5 VCC+0.5V

Outputs, IO Surge current 100 mA

TSTG Storage temperature -65 150 °C

θjA Package thermal impedence 73 °C/W

Note:

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating

only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this

specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

Pin Characteristics

Symbol Parameter Test Condition Min. Typ. Max. Units

CIN Input Capacitance 4 pF

Rpullup Input Pullup Resistance 50 kΩ

Rpulldown Input Pulldown Resistance 50 kΩ

Control Input Function Table

SELX Selected Clock Inputs

0 CLK0, /CLK0

1 CLK1, /CLK1

PI6C485352 Rev. A 01/24/13

13-0003 3

PI6C485352

2.5V/3.3V, 500 MHz Twelve 2-to-1 Differential LVPECL Clock Multiplexer

Operating Conditions

Symbol Parameter Test Condition Min. Typ. Max. Units

VCC Power Supply Voltage 3.0 3.3 3.6 V

VCCO Output Power Supply Voltage 2.375 3.6 V

TA Ambient Temperature -40 85 °C

IEE Power Supply Current 200 mA

LVCMOS/LVTTL DC Characteristics (TA = -40°C to +85°C, VCC = 3.3V ±10%, VCCO = 2.5V ±5%

to 3.3V ±10%)

Symbol Parameter Conditions Min. Typ. Max. Units

VIH Input High voltage SEL0:SEL11 2 VCC+0.3

V

VIL Input Low voltage SEL0:SEL11 -0.3 0.8

IIH Input High current SEL0:SEL11 VIN = VCC = 3.6V 150 μA

IIL Input Low current SEL0:SEL11 VIN = 0V, VCC = 3.6V -5 μA

Differential DC Characteristics (TA = -40°C to +85°C, VCC = 3.3V ±10%, VCCO = 2.5V ±5% to

3.3V ±10%)

Parameter Description Conditions Min. Typ. Max. Units

CLK0, CLK1 VIN = VCC = 3.6V 150 μA

IIH Input High Current

/CLK0, /CLK1 VIN = VCC = 3.6V 150 μA

CLK0, CLK1 VCC = 3.6V, VIN = 0V -5 μA

IIL Input Low Current

/CLK0, /CLK1 VCC = 3.6V, VIN = 0V -150 μA

VPP Peak-to-peak Voltage 0.15 1.3 V

VCMR Common Mode Input Voltage(1) VEE+0.5 VCC-0.85V V

VOH Output High Voltage (2)

VCCO = 3.3V or 2.5V VCCO -1.4 VCCO -0.9 V

VOL Output Low Voltage(2) VCCO = 3.3V or 2.5V VCCO -2.0 VCCO -1.7 V

Note:

1. Outputs terminated with 50Ω to VCCO -2.0V

PI6C485352 Rev. A 01/24/13

13-0003 4

PI6C485352

2.5V/3.3V, 500 MHz Twelve 2-to-1 Differential LVPECL Clock Multiplexer

AC Characteristics (TA = -40°C to +85°C, VCC = 3.3V ±10%, VCCO = 2.5V ±5% to 3.3V ±10%)

Parameter Description Conditions Min. Typ. Max. Units

fmax Output Frequency 500 MHz

tpd Propagation Delay (1)

4 ns

Tsk Output-to-output Skew(2) 100 ps

Tskpp Part-to-part Skew (3)

500 ps

tr/tf Output Rise/Fall time 20% - 80% 150 700 ps

odc Output duty cycle 45 55 %

Tj Buffer additive jitter RMS 0.05 ps

Note:

1.Measured from the differential input to the differential output crossing point

2 Defined as skew between outputs at the same supply voltage and with equal loads. Measured at the output differential crossing

point.

3. Defined as skew between outputs on different parts operating at the same supply voltage and with equal loads. Measured at the

outputs differential crossing point.

PI6C485352 Rev. A 01/24/13

13-0003 5

PI6C485352

2.5V/3.3V, 500 MHz Twelve 2-to-1 Differential LVPECL Clock Multiplexer

Applications Information

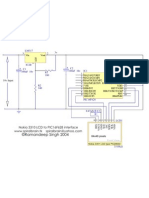

Wiring the differential input to accept single ended levels

Figure 1 shows how the differential input can be wired to accept single-ended levels. The reference voltage V_REF = VCC/2 is gener-

ated by the bias resistors R1, R2 and C1. This bias circuit should be placed as close as possible to the input pin. The ratio of R1 and

R2 should be adjusted to postion the V_REF at the center of the input voltage swing. For example, if the input clock swing is 2.5V

and VCC = 3.3V, V_REF should be 1.25V and R1/R2 = 0.609.

VCC

R1

1KΩ

Single Ended

Clock Input

CLK1

V_REF nCLK1

C1 R2

0.1μF

1KΩ

Figure 1: Single-ended Signal Driving Differential Input

PI6C485352 Rev. A 01/24/13

13-0003 6

PI6C485352

2.5V/3.3V, 500 MHz Twelve 2-to-1 Differential LVPECL Clock Multiplexer

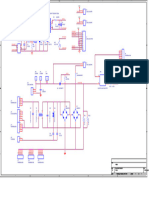

Packaging Mechanical: 48-Pin TQFP (FA)

1

DATE: 02/16/06

Notes:

1) All dimensions are in millimeters, Angles in Degrees DESCRIPTION: 48-pin Thin Quad Flat Package (TQFP)

2) Ref JEDEC: MO-026D, variation ABC

3) Dimensions do not include mold protrusion PACKAGE CODE: FA48

DOCUMENT CONTROL #: PD-2056 REVISION: - -

06-0182

Ordering Information

Ordering Number Package Code Package Description

PI6C485352FAE FA Pb-free & Green, 48-pin, 276-mil wide TQFP

• Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

• E = Pb-free and Green

• X suffix = Tape/Reel

PI6C485352 Rev. A 01/24/13

13-0003 7

You might also like

- Wireless Site SurveyDocument52 pagesWireless Site SurveyMSA Systems100% (1)

- Zero Delay, Differential-to-LVCMOS/ LVTTL Clock Generator: Not Recommended For New DesignsDocument18 pagesZero Delay, Differential-to-LVCMOS/ LVTTL Clock Generator: Not Recommended For New DesignsELLVEE TECHNo ratings yet

- Description Features: 3-Channel High-Performance TCXO/LVCMOS Clock Buffer Family 5PB12xx DatasheetDocument16 pagesDescription Features: 3-Channel High-Performance TCXO/LVCMOS Clock Buffer Family 5PB12xx Datasheetreza_azadNo ratings yet

- Alto A500.2 Power Amp Service Manual PDFDocument22 pagesAlto A500.2 Power Amp Service Manual PDFmundomusicalmeriaNo ratings yet

- SD7500 14x4 LCD Auto-Range 6 Channel Multimeter SoC Datasheet v0.1Document9 pagesSD7500 14x4 LCD Auto-Range 6 Channel Multimeter SoC Datasheet v0.1Alhassan Ahmed OmranNo ratings yet

- 8 Channel Relay BoardDocument4 pages8 Channel Relay Boardtutajos100% (1)

- Schematic Hqeakwg 2023-10-14Document1 pageSchematic Hqeakwg 2023-10-14Claudia De AndradeNo ratings yet

- Lattice PLLDocument21 pagesLattice PLLHoracio DorantesNo ratings yet

- Alto-DPA2500 4000 Service ManualDocument60 pagesAlto-DPA2500 4000 Service ManualChuYurNo ratings yet

- Schematic - Full Protocol Power Bank IP5358 - 2021!02!22Document1 pageSchematic - Full Protocol Power Bank IP5358 - 2021!02!22risirarocksNo ratings yet

- MC100H642 (Clock Driver) ICDocument9 pagesMC100H642 (Clock Driver) ICDwp BhaskaranNo ratings yet

- More Smoky Amp Rev.ADocument3 pagesMore Smoky Amp Rev.AGryf Audio CompanyNo ratings yet

- Clock SchematicDocument1 pageClock SchematicRaja Babu100% (1)

- sd3004 Datasheet v0.2cDocument6 pagessd3004 Datasheet v0.2cBenoit RigoNo ratings yet

- Hard BootDocument1 pageHard BootJairo Andrés Quiñones Buitrago100% (2)

- Alto Mistral 6000 PWR SM PDFDocument33 pagesAlto Mistral 6000 PWR SM PDFmundomusicalmeriaNo ratings yet

- Schematic Digital Kit 2023-03-18 BGR0sI9GQzDocument1 pageSchematic Digital Kit 2023-03-18 BGR0sI9GQzSolomon AkpanNo ratings yet

- An551 PDFDocument16 pagesAn551 PDFwrite2arshad_mNo ratings yet

- RemoteDocument2 pagesRemotejithinraj33100% (1)

- Shift Register: ObjectivesDocument10 pagesShift Register: ObjectivesDinh LâmNo ratings yet

- Atmel 9111 LIN Networking ATA6612C ATA6613C - Datasheet PDFDocument312 pagesAtmel 9111 LIN Networking ATA6612C ATA6613C - Datasheet PDFAnkadi Sikari ReddyNo ratings yet

- CNC-satshakit CNC 20mhz SCHDocument1 pageCNC-satshakit CNC 20mhz SCHTomi OzzyNo ratings yet

- Description Features: PT4452 PLL-based OOK/ASK/FSK Transmitter ICDocument4 pagesDescription Features: PT4452 PLL-based OOK/ASK/FSK Transmitter ICSamerNo ratings yet

- Interfacing The 8051 MicrocontrollerDocument9 pagesInterfacing The 8051 Microcontrollerummulkhulsu100% (1)

- 3.3V Zero Delay Clock Buffer: Features: DescriptionDocument13 pages3.3V Zero Delay Clock Buffer: Features: DescriptionallendohorizontNo ratings yet

- Schematic 12 129005Document1 pageSchematic 12 129005ALFONZO DANIELNo ratings yet

- Pap 8 AumDocument1 pagePap 8 AumjoseNo ratings yet

- 21bec0499 VL2023240100568 Ast05Document4 pages21bec0499 VL2023240100568 Ast05Om PotdarNo ratings yet

- Kru 481 LCD SCHDocument1 pageKru 481 LCD SCHAntonio Fernandes50% (2)

- Schematic Inductor Meter 2022-01-19 FiyoihfdnyDocument1 pageSchematic Inductor Meter 2022-01-19 FiyoihfdnyIpoelNo ratings yet

- M2PJ2500LCD10NSDocument59 pagesM2PJ2500LCD10NSvakri2No ratings yet

- By Sunil Malekar (Elektor Labs India) : March & April 2015Document4 pagesBy Sunil Malekar (Elektor Labs India) : March & April 2015Agnivesh PandeyNo ratings yet

- CXD2861ERDocument30 pagesCXD2861ERZaegorNo ratings yet

- Chapter 4Document28 pagesChapter 4Abo Shaker HaboudalNo ratings yet

- weatherSTAMP - UnknownDocument1 pageweatherSTAMP - UnknownJony DarkoNo ratings yet

- Microprocessors & Interfacing: Tutorial 10 Timers & 8259Document25 pagesMicroprocessors & Interfacing: Tutorial 10 Timers & 8259Hemant DhamijaNo ratings yet

- Clapper CircuitDocument6 pagesClapper Circuitsameed2010No ratings yet

- Index: Circuit Diagram Working Principle Description Comparision With Other Application Disadvantages ReferenceDocument26 pagesIndex: Circuit Diagram Working Principle Description Comparision With Other Application Disadvantages Referenceinfinite2towersNo ratings yet

- REPEATER IDER ISD25xx - Repeater Ider Isd2590 16f877aDocument1 pageREPEATER IDER ISD25xx - Repeater Ider Isd2590 16f877amanuel contrerasNo ratings yet

- Si5338 EVBDocument12 pagesSi5338 EVBreza_azadNo ratings yet

- MX27C1100/27C1024: FeaturesDocument19 pagesMX27C1100/27C1024: FeaturesVictor TruccoNo ratings yet

- ATtiny-RGB MoodlampDocument1 pageATtiny-RGB MoodlampovidiutacheNo ratings yet

- Matrix 1.4 - Dos-V (Implememting Vas With Dynamic Output Sinking)Document4 pagesMatrix 1.4 - Dos-V (Implememting Vas With Dynamic Output Sinking)អំភ្លី សំលេងNo ratings yet

- ©ramandeep Singh 2004: Nokia 3310 LCD To PIC16F628 InterfaceDocument1 page©ramandeep Singh 2004: Nokia 3310 LCD To PIC16F628 InterfaceAnonymous GxeR0L100% (2)

- OLUPS SCR B21 SchematicsDocument1 pageOLUPS SCR B21 SchematicsaananthuajaysNo ratings yet

- 8051 Architecture ?Document62 pages8051 Architecture ?Camilo SilvaNo ratings yet

- Digital CalenderDocument1 pageDigital CalenderGarvitt BhatnagarNo ratings yet

- 3921 Fig 02Document1 page3921 Fig 02Matheus Régis Dias100% (2)

- Interfacing Relay With LPC2148 ARM: Arm How-To GuideDocument12 pagesInterfacing Relay With LPC2148 ARM: Arm How-To GuideRahi Sarkar0% (1)

- X-10 Data-Stream MonitorDocument4 pagesX-10 Data-Stream MonitorGustavo PiaiNo ratings yet

- Iprog Can AdapterDocument1 pageIprog Can AdapterAndrésFelipeCevallos100% (1)

- 27C1024 - EpromDocument20 pages27C1024 - EpromSavo BacicNo ratings yet

- TEX1000-LCD: User ManualDocument60 pagesTEX1000-LCD: User ManualFelipe Quinde100% (2)

- Pre Amplificador de Audi: Jasama SystemDocument1 pagePre Amplificador de Audi: Jasama SystemAlvaro Canaviri MamaniNo ratings yet

- Autorizacion de Retiro Correo Argentino 190520150606Document13 pagesAutorizacion de Retiro Correo Argentino 190520150606Lucas EtchezuriNo ratings yet

- 1500 Watt Peak Class AB Audio Power Amplifier For 2-Ohms Loudspeaker (Core) - Ver. Bc-I-1500-Ls2-2013, Rev. 2Document3 pages1500 Watt Peak Class AB Audio Power Amplifier For 2-Ohms Loudspeaker (Core) - Ver. Bc-I-1500-Ls2-2013, Rev. 2SachinNo ratings yet

- 8051 Microcontroller: An Applications Based IntroductionFrom Everand8051 Microcontroller: An Applications Based IntroductionRating: 5 out of 5 stars5/5 (6)

- 456 16830 0 Tda7212Document4 pages456 16830 0 Tda7212david.gjeorgevskiNo ratings yet

- REN El7202-12-22 DST 20021108Document9 pagesREN El7202-12-22 DST 20021108david.gjeorgevskiNo ratings yet

- RPCF W1B1 7910 o W 001Document4 pagesRPCF W1B1 7910 o W 001david.gjeorgevskiNo ratings yet

- SE8117TADocument7 pagesSE8117TAdavid.gjeorgevskiNo ratings yet

- Butt Sketch LawsuitDocument90 pagesButt Sketch LawsuitDallasObserverNo ratings yet

- Dsa ReportDocument2 pagesDsa Reportmh4070685No ratings yet

- Cod.390S.B: Instruction ManualDocument24 pagesCod.390S.B: Instruction ManualAshrafNo ratings yet

- Google Glass Seminar ReportDocument30 pagesGoogle Glass Seminar ReportShashank Jain79% (33)

- lastCleanException 20220424185711Document19 pageslastCleanException 20220424185711beom choiNo ratings yet

- Desbloqueio Magellan e Instalação Igo8Document2 pagesDesbloqueio Magellan e Instalação Igo8kdlao1969No ratings yet

- RetailManagerUserGuide PDFDocument322 pagesRetailManagerUserGuide PDFJun Vincent CabangNo ratings yet

- Trescientos Uno Flanger: Resistors Trim Pots Parts ListDocument1 pageTrescientos Uno Flanger: Resistors Trim Pots Parts ListYeremia OyaNo ratings yet

- BLEMBA 30 - Syndicate 1 - Financial DetectiveDocument20 pagesBLEMBA 30 - Syndicate 1 - Financial DetectiveDyani Nabyla Widyaputri0% (1)

- SIMATIC S7-300 S7-300 CPU Data: CPU 315T-2 DPDocument127 pagesSIMATIC S7-300 S7-300 CPU Data: CPU 315T-2 DPNguyễn Quang HảoNo ratings yet

- Script Week 5Document2 pagesScript Week 5sabrina batrisyiaNo ratings yet

- Engl393 - Instructions Final SubmissionDocument24 pagesEngl393 - Instructions Final Submissionapi-622526151No ratings yet

- Essbase ASO ImplementationDocument3 pagesEssbase ASO ImplementationAmit SharmaNo ratings yet

- Lista de Precios Consumer Electronics Abril 2023Document6 pagesLista de Precios Consumer Electronics Abril 2023Nadia Chacon ChañiNo ratings yet

- CRM Questions and AnswersDocument163 pagesCRM Questions and AnswersRafael Daboin M100% (1)

- B1 90 TB1200 03 01Document28 pagesB1 90 TB1200 03 01Vivek ChowdhuryNo ratings yet

- XXXX ATM Principle: ISSUE2.0Document30 pagesXXXX ATM Principle: ISSUE2.0anon_164514627No ratings yet

- DWH Question BankDocument9 pagesDWH Question Bankbala swaroopNo ratings yet

- 5th Chapter 5 - C L ProgrammingDocument65 pages5th Chapter 5 - C L ProgrammingoharamatyNo ratings yet

- Assessing The Impact of OnlineDocument17 pagesAssessing The Impact of OnlineMahamud AliNo ratings yet

- Computer Numeric Control: Prof. J. Ramkumar Department of Mechanical Engineering IIT KanpurDocument48 pagesComputer Numeric Control: Prof. J. Ramkumar Department of Mechanical Engineering IIT KanpurHassnain MohdNo ratings yet

- Data Science and Bigdata Analytics: Dr. Ali Imran JehangiriDocument20 pagesData Science and Bigdata Analytics: Dr. Ali Imran Jehangirisyed hamzaNo ratings yet

- Java Programming Question BankDocument7 pagesJava Programming Question Bankshital7028733151No ratings yet

- Service Manual: /rxgvshdnhuer %Document22 pagesService Manual: /rxgvshdnhuer %mechaconkarkaNo ratings yet

- Library Management SystemDocument31 pagesLibrary Management SystemJaiHanumankiNo ratings yet

- High-Wattage General Purpose Relay: Small PCB Relay For Automobile UseDocument3 pagesHigh-Wattage General Purpose Relay: Small PCB Relay For Automobile Usesuan kwang TanNo ratings yet

- Reebok and Adidas Case StudyDocument14 pagesReebok and Adidas Case Studysnowgul100% (1)

- DVDR3570H - SB KL Ex Si - 1221814332Document54 pagesDVDR3570H - SB KL Ex Si - 1221814332olomouc7267No ratings yet

- COMPUTE!'s Beginner's Guide To Assembly Language On The TI-99/4ADocument272 pagesCOMPUTE!'s Beginner's Guide To Assembly Language On The TI-99/4Aremow100% (1)