Professional Documents

Culture Documents

SD7500 14x4 LCD Auto-Range 6 Channel Multimeter SoC Datasheet v0.1

Uploaded by

Alhassan Ahmed OmranOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

SD7500 14x4 LCD Auto-Range 6 Channel Multimeter SoC Datasheet v0.1

Uploaded by

Alhassan Ahmed OmranCopyright:

Available Formats

SD7500

14*4 LCD Auto-range

6 Channel Multimeter SoC

Description

Features The SD7500 is a SoC with built-in 24 bit ADC

and 16k Bytes OTP memory. The IC was designed

6 channels ADC, 4000 counts, auto-range with ultra-low power technology. Operates at 3.3V

measurement supply and internal RC oscillator frequency, the total

AC true RMS output, measurement error<0.5% at

typical operating current is 1.6mA.

2kHz passband corner

Built-in voltage divider, no external resistor divider It has very rich peripheral resources: selectable

needed regulated voltage source, flexible ADC setup, voltage

Programmable multi-functional measurement booster, UART, TIMER with CAPTURE capability,

network,support voltage, current, resistor, diode, PWM, PFD, and LCD driver.

transistor, open/short, temperature, and capacitor The OTP can be programmed in situ and the

measurements 2.4V~3.6V programming voltage is generated

Multi-functional comparator internally. The OTP can be used in place of external

8 bits RISC ultra-low power MCU, 49 instructions EEPROM.

and 6 stack levels. The MCU current consumption is

400uA typically at 3.3V and 2MHz operating clock Three working modes are provided so users can

rate. Standby current is 1.5uA at 32kHz clock, and select the optimum choice between speed and power.

less than 1uA at sleep They are normal mode, standby mode, and sleep mode.

16k Bytes OTP for program storage, 256 Bytes

SRAM for data storage Applications

Low OTP programming voltage, can replace

external EEPROM Manual or auto-range multimeter and similar

Flexible battery voltage detection range 2.0V~ 3.3V measurement applications

Abundant peripheral resources: UART, PWM, PFD,

BUZ, and TIMER Ordering Information

14SEG × 4COM LCD drive, ultra-low power

LQFP44 package

consumption and high driving capability,

programmable boost module to maintain luminance

at low supply voltage, support grey scale adjustment.

Support grey scale adjustment

Every digital I/O port contain Schmitt trigger input

and selectable pull up resistor

Low voltage detection and power on reset circuit

Operating voltage range: 2.4V~ 3.6V

Operating temperature range: -40 ˚C~85 ˚C

Built-in 8MHz and 32kHz RC oscillators

SDIC Microelectronics Rev. 0.1 Apr 2018

http://www.SDICmicro.com

SD7500

Pin Diagram and Descriptions

COM0/P57

COM1/P56

COM2/P55

COM3/P54

SEG0/P53

SEG1/P52

SEG2/P51

RST_B

VLCD

NC

NC

44

43

42

41

40

39

38

37

36

35

34

1 33

VPP SEG3/P50

2 32 SEG4/P47

VDD

3 31 SEG5/P46

VSS

AVDDR 4 30 SEG6/P45

ACM

A0/LBTIN0

5

6

SDIC 29 SEG7/P44

28 SEG8/P43

A1

A2

7

8

XXXXXXX 27 SEG9/P42

26 SEG10/P41

A3

9

10

SD7500 25 SEG11/P40

24

A4 SEG12/P27/PFD/PWM

11 23

A5 SEG13/P26/BUZB

12

13

14

15

16

17

18

19

20

21

22

P23/INT1

P24/INT1

P22/INT1

P25/BUZ

P21/INT1

P20/INT1

P11/LBTIN1/INT0

P12/LBTIN2/INT0

P13/INT0/RXD

P14/INT0/TXD

COM

Figure 1. Pin out diagram

SDIC Microelectronics Rev. 0.1 Apr 2018 2 of 9

http://www.SDICmicro.com

SD7500

Table 1. Pin Descriptions

Pin No. Pin Name Attribute Descriptions

1 VPP Analog OTP high voltage programming pin, connect 1uF capacitor to VSS

2 VDD Power Power supply voltage, connect 0.1uF capacitor to VSS

3 VSS Ground

Power ground

Internal LDO output for IC’s analog module, connect 0.1uF to 10uF filter capacitor to

4 AVDDR Analog

VSS

5 ACM Analog ADC common mode voltage output, connect 0.1uF cap to VSS

Analog signal inputs, each port has an independent register controlled pull-down

6 A0/LBTIN0 Analog resistor (default OFF), should set to ON for unused port. A0 can be set as LBTIN0

input input

Analog Analog signal inputs, each port has an independent register controlled pull-down

7-11 A1--A5

input resistor (default OFF), should set to ON for unused port.

12 COM Analog Measurement circuit common ground, connect 0.1uF cap to VSS

13 P11/INT0/LBTIN1 I/O Digital port P11, external interrupt INT0, or low battery detect LBTIN1 input

14 P12/INT0/LBTIN2 I/O Digital port P12, external interrupt INT0, or low battery detect LBTIN2 input

15 P13/INT0/RXD I/O Digital port P13, external interrupt INT0, or UART’s RXD port

16 P14/INT0/TXD I/O Digital port P14, external interrupt INT0, or UART’s TXD port

P20/INT1--

17-21 I/O Digital ports P20-24 or external interrupt INT1

P24/INT1

22 P25/BUZ I/O Digital port P25 or buzzer BUZ output

23 P26/SEG13/BUZB I/O Digital port P26, LCD segment SEG13, or buzzer BUZB output

P27/SEG12/PFD/P

24 I/O Digital port P27, LCD segment SEG12, or PFD/PWM output

WM

P40/SEG11--

25-32 I/O Digital port P40-47 or LCD segment SEG11-4

P47/SEG4

P50/SEG3--

33-36 I/O Digital port P50-53 or LCD segment SEG3-0

P53/SEG0

Digital port P54-57 or LCD COM3-0

P54/COM3--

37-40 I/O During serial programming, Pin 37-40 serve as Data output, 2MHz clock input, Data

P57/COM0

input, and Data clock

41 RST_B I External reset input, active low, internal 200k pull up resistor

LCD driver power supply, internally connect to VDD or

42 VLCD Analog

booster output through register setting, connect 1uF filter capacitor to VDD

43-44 NC NC Leave floating, do not connect to any circuit

Remark: All I/O ports Pnn have internal pull-up option (default OFF) and input hysteresis at 0.3VDD/0.7VDD.

SDIC Microelectronics Rev. 0.1 Apr 2018 3 of 9

http://www.SDICmicro.com

SD7500

Functional Block

AVDDR

RC OSC RC OSC

POR/LVD VDD

(32kHz) (8MHz) Power management

VSS

Timing control generator COM

WDT

OTP

VPP

16K Bytes

8Bits Sigma M

RISC MCU Delta IA U A0-5

RST_B ADC X

Special SRAM

registers 256 Bytes

CMPH Reference

ACM

voltage

VLCD

LCD Battery LBTIN0-2

SEG13-0

Driver CMPL detect

COM3-0

External

INT1-0

interrupts

PWM

PWM/ IO control Timer/Counter

PFD BUZZER

T0/T2/TA/TB

PFD

BUZ

P14-11

P47-40

P57-50

BUZB

P27-20

Figure 2. Functional block diagram

SDIC Microelectronics Rev. 0.1 Apr 2018 4 of 9

http://www.SDICmicro.com

SD7500

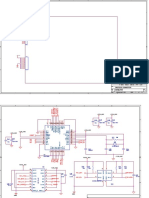

Typical Application

Use one of the two

Ω/mV/V/uA/mA/Cap/Temp/Diode/Cont

10A(20A)

power supply circuit

COM

VDD

NCV circuit

1

F1

Use≤1kΩ PTC

Power

S1

10A/250V

4.5V-9V

NCVIn

200mA/ 1000V

0.01Ω 1%

BT1

F2

1

uA

mA

PTC-1K

S6

S7

1M R4

R3

R17

COM

47uF/16V

C1

0.99 Ω/1 %

R10

R9

99 Ω/1 %

R16

1K

1K

Ω/mV/Cap/Temp/Diode/Cont

Ω/mV/Cap/Temp/Diode/Cont

R2

uA/mA/A

NCV

VCC

S3

S4

S5

S8

0.1uF

22M R5

C2

1N4004 1 N 4004

1

D1

Vin

22M

R6

R18

100K

COM

S9

hFE

7133

D2

2

GND

47uF/16V

NPN

Vout

10 Ω

R11

100K

R19

B

C

E

VPP

1uF

C8

E

3

VDD

COM

AVDDR

C3

E

E

VDD

Q1

Q2

100K

8050

8050

0.1uF

C9

R20

B

0.1uF

C4

PNP

AVDDR

1K Ω R8

C10

1uF

10M R7

BT2

100pF

3V

Power

S2

47uF/16V

C14

C11

0.1uF

P1

P2

P0

A0

A2

C12

C5

10 27nF

VDD VCC

C13

1uF

11

1

2

3

4

5

Hold/BL

K1

K2

K3

Range

Select

VPP

VSS

VDD

AVDDR

ACM

A1

A2

A3

A4

A5

A0/LBTIN0

12

COM

VDD COM

44

NC

C6

1uF

43

NC

42 13 P0

VLCD P11/ INT0/ LBTIN1

RSTB 41

LCD

SD7500

K4

K5

K6

RSTB 14 P1

Max/Min

BL

Hold

P12/ INT0/ LBTIN2

1 P57 40

C4 P57/ COM0

2 P56 39 15 P2

C3 P56/ COM1 P13/ INT0/ RXD

3 P55 38

C2 P55/ COM2

4 P54 37 16

C1 P54/ COM3 P14/ INT0/ TXD

5 36

S1 P53/ SEG0

6 35

S2 P52/ SEG1

7 34 17 1 10

S3 P51/ SEG2 P20/ INT1

8 33 18 2 9

S4 P50/ SEG3 P21/ INT1

P27/SEG12/PFD/PWM

9 32 19 3 8

S5 P47/ SEG4 P22/ INT1

10 31 20 4 7

P26/SEG13/BUZB

S6 P46/ SEG5 P23/ INT1

11 30 21 5 6

S7 P45/ SEG6 P24/ INT1

12 29

S8 P44/ SEG7

28

P40/SEG11

P41/SEG10

S9 13 P43/ SEG8

P42/SEG9

P25/BUZ

14 Function selection

S10

S11 15 Open:1

S12 16

Close:0

27

26

25

24

23

22

10K

R23

VDD

Programming

47 Ω

R12

8050

Q4

External low voltage detect setup terminal

Remove R22 when supply=3V

BUZZER

P54

VCC 1

VDD P55

2

P56

J1

3

P57

4

VPP

R21 5

VDD

5.1M R1 6 Use one of the two indicator circuits

10K 7

A2

8

A0 9

47Ω

Backlight

R13

RSTB

COM

R22 C7

1M

0.1uF

10K

R14

VCC

47 Ω

R15

Backlight

Q3

8050

Figure 3. Multimeter typical application diagram

SDIC Microelectronics Rev. 0.1 Apr 2018 5 of 9

http://www.SDICmicro.com

SD7500

ADC Characteristics

Table 2. ENOB and voltage noise Vn rms

(Gain=1, SINC3,VDD=3.3V,AVDDR=2.4V,VREF=1.2V,BUF1/BUF2 on)

ADC sampling rate = 512kHz

OSR 128 256 512 1024 2048 4096 8192 16384

ENOB 16.75 17.76 18.23 18.86 19.21 19.44 19.52 19.71

Vn rms (uV) 22.13 9.89 7.38 5.23 3.95 3.38 3.18 2.80

ADC sampling rate = 1MHz

OSR 128 256 512 1024 2048 4096 8192 16384

ENOB 16.53 17.58 18.38 18.68 19.33 19.45 19.56 19.70

Vn rms (uV) 23.77 11.24 6.89 5.65 4.47 3.64 3.10 2.82

Remark:

The above data are averages based on multiple ICs’ measured results. Each IC contributes 1024 data points.

ENOB = FRS , FRS is the Full Scale Voltage Range (2 * Vref / Gain), Vrms is the rms Noise.

log 2 ( )

Vrms

SDIC Microelectronics Rev. 0.1 Apr 2018 6 of 9

http://www.SDICmicro.com

SD7500

Electrical Specifications

Table 3. Absolute Maximum Ratings

Symbol Parameter Minimum Maximum Unit

TA Operating temperature -40 +85 °C

TS Storage temperature -55 +150 °C

V DD Supply voltage -0.2 +4.0 V

Vpp Programming voltage -0.2 +7.5 V

V IN , V OUT Digital input/output voltage -0.2 V DD +0.3 V

TL Reflow temperature profile Per IPC/JEDECJ-STD-020C °C

Remarks:

1. CMOS device can easily be damaged by electrostatics. It must be stored in conductive foam, and careful not to exceed the

operating voltage range.

2. Turn off power before insert or remove the device.

Table 4. Electrical Specifications(VDD=3.3V, T A=25℃)

Symbol Parameter Minimum Typical Maximum Unit Conditions/Remarks

2.4 3.3 3.6 V Analog modules operating voltage

VDD Supply voltage Digital modules and MCU operating

2.0 3.3 3.6 V

voltage

FOSC must be 2MHz when read/write

FOSC Operating frequency 0.016 2 4 MHz

tables in OTP

Internal high frequency

IHRC 7.9 8 8.1 MHz Frequency after calibration

RC oscillator

Internal low frequency

ILRC 24 32 40 kHz Frequency after calibration

RC oscillator

Internal RC oscillator frequency

IDD1 Operating current 1 -- 1.6 2 mA quartered for MCU

Analog modules active

32kHz internal RC oscillator for MCU

IDD2 Operating current 2 -- 1.5 2 uA MCU at standby mode

Analog modules inactive

MCU at sleep mode

IDD3 Operating current 3 -- 0.2 1 uA

Analog modules inactive

Fsam ADC sampling rate -- 500 1000 kHz

OSR Over sampling rate 128 -- 16384

NFbit Noise free bits 1 -- 16 -- bits Gain=128,input FSR=±4mV

AC measurement

BW 2 kHz Measurement error<0.5%

bandwidth

-Vref/ -- Vref/ 1X gain

-Vref/2 -- Vref/2 2X gain

-Vref/4 -- Vref/4 4X gain

-Vref/8 -- Vref/8 8X gain

PGIA differential -- 16X gain

VINdif -Vref/16 Vref/16 mV

input range

-Vref/32 -- Vref/32 32X gain

-Vref/64 -- Vref/64 64X gain

-Vref/128 -- Vref/128 128X gain

-Vref/256 -- Vref/256 256X gain

SDIC Microelectronics Rev. 0.1 Apr 2018 7 of 9

http://www.SDICmicro.com

SD7500

-0.3 -- AVDDR 1X gain and buffer is off

VIN PGIA input voltage range2

0.3 -- AVDDR-0.7 1X gain and buffer is on, or gain≠1

Vn rms RMS noise -- 2.80 -- uVrms 1X gain and OSR=16384

Vacm ACM voltage output -- 1.2 -- V

IacmSour ACM current source -- 1 -- mA

IacmSink ACM current sink -- 1 -- mA

PSRacm ACM PSR -- 100 -- uV/V

-- 2.4 -- AVDDRX[1:0]=00

AVDDR -- VDD -- AVDDRX[1:0]=01

Vavddr voltage output V

-- 2.9 -- AVDDRX[1:0]=10

-- 2.7 -- AVDDRX[1:0]=11

Iavddr AVDDR current -- 10 -- mA

POR Power On Reset voltage -- 2.0 -- V

Low Voltage Detect

LVD reset voltage -- 1.9 -- V

THlbt LVD hysteresis -- 200 -- mV

-- 2.1 -- VLCDX[2:0]=000

-- 2.3 -- VLCDX[2:0]=001

-- 2.5 -- VLCDX[2:0]=010

LCD charge pump output -- 2.7 -- VLCDX[2:0]=011

Vlcd voltage V

-- 2.9 -- VLCDX[2:0]=100

-- 3.1 -- VLCDX[2:0]=101

-- 3.3 -- VLCDX[2:0]=110

-- 3.5 -- VLCDX[2:0]=111

3

Ilcd LCD charge pump current -- -- 500 uA

Digital I/O parameter

High output -- 3 -- VOL=VDD-0.3V, PTxSR=0

IOH mA

current source -- 12 -- VOL=VDD-0.3V, PTxSR=1

Output low -- 3 -- VOH=0.3V, PTxSR=0

IOL mA

current sink -- 12 -- VOH=0.3V, PTxSR=1

VIH Input high voltage 0.7VDD -- -- V

VIL Input low voltage -- -- 0.3VDD V

VOH Output high voltage VDD-0.3 -- -- V

VOL Output low voltage -- -- VSS+0.3 V

Rpu Pin pull up resistance -- 200 -- kΩ VDD = 3.0

Note:

1. Noise free bits and effective resolution are both related to the signal’s full scale range. Its peak to peak or rms noise plays the decisive role.

2. The signal input range is limited by the differential signal input range and the absolute voltage at the input terminals. The first one is the

real signal input range. It is affected by the PGIA gain and the ADC voltage reference choice. The second one includes both differential

and common mode components and is mainly limited by the circuit.

3. The charge pump driving capability is related to the choice of capacitor and the operating frequency.

SDIC Microelectronics Rev. 0.1 Apr 2018 8 of 9

http://www.SDICmicro.com

SD7500

Packaging Information

D

D1

33 23

34 22

E1 E

C

L

L1 F

44 12

1

b e 11

A3

A2 A

θ A1

F

Dimensions: mm

Symbol Min. Nom. Max.

A —— —— 1.60

A1 0.05 —— 0.15

A2 1.35 1.40 1.45

A3 0.59 0.64 0.69

b 0.28 —— 0.36

b1 0.27 0.30 0.33

c 0.13 —— 0.17

c1 0.12 0.13 0.14

D 11.80 12.00 12.20

D1 9.90 10.00 10.10

E 11.80 12.00 12.20

E1 9.90 10.00 10.10

e 0.80BSC

eB 11.25 —— 11.45

L 0.45 —— 0.75

L1 1.00BSC

θ 0 —— 7

Figure 4. LQFP44 mechanical specification

SDIC Microelectronics Rev. 0.1 Apr 2018 9 of 9

http://www.SDICmicro.com

You might also like

- Subject: Use of Multi-Core Processors Date: XXX AC No: AC 20-193 Initiated By: AIR-622Document17 pagesSubject: Use of Multi-Core Processors Date: XXX AC No: AC 20-193 Initiated By: AIR-622rdpereir100% (1)

- The Ultimate Big Data Masters Program (Cloud Focused)Document9 pagesThe Ultimate Big Data Masters Program (Cloud Focused)arbimbbNo ratings yet

- RTD2120LDocument37 pagesRTD2120LNeha WadyalkarNo ratings yet

- Atmel 7766 8 Bit AVR ATmega16U4 32U4 Datasheet-1315135Document439 pagesAtmel 7766 8 Bit AVR ATmega16U4 32U4 Datasheet-1315135Pretty TrapNo ratings yet

- sd3004 Datasheet v0.2cDocument6 pagessd3004 Datasheet v0.2cBenoit RigoNo ratings yet

- Atmega 32U4Document408 pagesAtmega 32U4Ahmad SubkhanNo ratings yet

- WISTRON P1 P15 91.4H701.001 07254 REV - 1 - Fujitsu-Siemens Amilo Pa 3553Document56 pagesWISTRON P1 P15 91.4H701.001 07254 REV - 1 - Fujitsu-Siemens Amilo Pa 3553OlegNo ratings yet

- Low Speed USB Micro-Controller: FeaturesDocument54 pagesLow Speed USB Micro-Controller: FeaturesPadmajan YesodharanNo ratings yet

- BAI 3 - Sensor - ADC - UARTDocument9 pagesBAI 3 - Sensor - ADC - UARTTrần Ngọc Thiên DiNo ratings yet

- Microchiptechnology Atf1500a10ju Datasheets 9781Document19 pagesMicrochiptechnology Atf1500a10ju Datasheets 9781Elisson GalvãoNo ratings yet

- AT89S53Document31 pagesAT89S53Dhiya Uddin RNo ratings yet

- NEJE KZ Board SchematicDocument1 pageNEJE KZ Board Schematicvictor Sanmiguel0% (1)

- ST16C550CQ8Document35 pagesST16C550CQ8saberNo ratings yet

- Compatible With MCS®-51 Products - 12K Bytes of In-SystemDocument56 pagesCompatible With MCS®-51 Products - 12K Bytes of In-Systemwm53No ratings yet

- EL4583, 84, 85 Demo Board Tb430 Data SheetDocument3 pagesEL4583, 84, 85 Demo Board Tb430 Data SheetvideoengrNo ratings yet

- AtmelDocument86 pagesAtmelYusuf FamilyNo ratings yet

- 8-Bit Microcontroller With 16/32K Bytes of Isp Flash and Usb Controller Atmega16U4 Atmega32U4Document433 pages8-Bit Microcontroller With 16/32K Bytes of Isp Flash and Usb Controller Atmega16U4 Atmega32U4andreyNo ratings yet

- AVR and C Programming FinalDocument58 pagesAVR and C Programming Finalzbhp zNo ratings yet

- BAI 2 - Timer - Counter - Interrupt - LCDDocument11 pagesBAI 2 - Timer - Counter - Interrupt - LCDTrần Ngọc Thiên DiNo ratings yet

- PI6C485352Document7 pagesPI6C485352david.gjeorgevskiNo ratings yet

- Slaa 115Document4 pagesSlaa 115api-3744762No ratings yet

- Wistron Morar RSB SchematicsDocument41 pagesWistron Morar RSB SchematicsНиколай СтупниковNo ratings yet

- ATMEGA16U4Document23 pagesATMEGA16U4Muhammad ImranNo ratings yet

- Amd S1G2 Cpu: Vramx4 Gddr3 512MBDocument56 pagesAmd S1G2 Cpu: Vramx4 Gddr3 512MBحسن علي نوفلNo ratings yet

- P89V51RB2/RC2/RD2: 1. General DescriptionDocument78 pagesP89V51RB2/RC2/RD2: 1. General DescriptionShah RonakNo ratings yet

- 74HC164 74HCT164: 1. General DescriptionDocument16 pages74HC164 74HCT164: 1. General DescriptionteomondoNo ratings yet

- 3 Intro+to+MB90F387S PDFDocument29 pages3 Intro+to+MB90F387S PDFMarc Neil ApasNo ratings yet

- Course No: MTE 3104 Course Name: Microcontroller & Interfacing SessionalsDocument7 pagesCourse No: MTE 3104 Course Name: Microcontroller & Interfacing SessionalsChetona DasNo ratings yet

- Alto-DPA2500 4000 Service ManualDocument60 pagesAlto-DPA2500 4000 Service ManualChuYurNo ratings yet

- Acer TravelMate C310 Canary2 Laptop SchematicsDocument55 pagesAcer TravelMate C310 Canary2 Laptop SchematicsDeadMikeNo ratings yet

- Esy MPDocument17 pagesEsy MP10 Durvesh PathakNo ratings yet

- PIC16F882/883/884/886/887: 28/40/44-Pin Flash-Based, 8-Bit CMOS MicrocontrollersDocument78 pagesPIC16F882/883/884/886/887: 28/40/44-Pin Flash-Based, 8-Bit CMOS Microcontrollersfranklin monteroNo ratings yet

- Acer Aspire 7551 - 7551G Wistron JE70-DN, SJV71-DN, HM72-DN RevSB SchematicDocument63 pagesAcer Aspire 7551 - 7551G Wistron JE70-DN, SJV71-DN, HM72-DN RevSB SchematicBuen DiaNo ratings yet

- An 14Document5 pagesAn 14zvaNo ratings yet

- MicrocontrollerDocument56 pagesMicrocontrollerSai Harun Kumar ReddyNo ratings yet

- ATF1502ASDocument18 pagesATF1502ASAline X Arthur FrancoNo ratings yet

- 74HC164 74HCT164: 1. General DescriptionDocument17 pages74HC164 74HCT164: 1. General DescriptionTDFRIOGRANDENo ratings yet

- WISTRON JE71-DN 09945-1 48 4JN01 011 Rev - 1 PDFDocument61 pagesWISTRON JE71-DN 09945-1 48 4JN01 011 Rev - 1 PDFКирилNo ratings yet

- 8-Bit Microcontroller With 8K Bytes Flash AT89S8252: FeaturesDocument31 pages8-Bit Microcontroller With 8K Bytes Flash AT89S8252: Featuresapi-3808344No ratings yet

- Wistron Jm70-Pu r-2 Schematics PDFDocument57 pagesWistron Jm70-Pu r-2 Schematics PDFКирилNo ratings yet

- MPC89x52A: 8-Bit Micro-ControllerDocument38 pagesMPC89x52A: 8-Bit Micro-ControllerBA BIaNo ratings yet

- Y210 (8685) 原理图Document36 pagesY210 (8685) 原理图WalterNo ratings yet

- Datasheet EN29LV800BDocument41 pagesDatasheet EN29LV800BJackson de Oliveira SilvaNo ratings yet

- Banana Pi BPI-F2S-SCH - V3.0Document14 pagesBanana Pi BPI-F2S-SCH - V3.0Tuan AnhNo ratings yet

- Features Description: CMOS Programmable Peripheral InterfaceDocument22 pagesFeatures Description: CMOS Programmable Peripheral Interfacekhawar mukhtarNo ratings yet

- MS-16811 Rev0bDocument43 pagesMS-16811 Rev0bJonathan BiondiNo ratings yet

- Dell Inspiron 1525 - PP29L Spears-Intel 07211-3Document47 pagesDell Inspiron 1525 - PP29L Spears-Intel 07211-3Tiberio RafaelNo ratings yet

- Microprocessor Lab Project EC - 316: Made ByDocument19 pagesMicroprocessor Lab Project EC - 316: Made ByJani ServiniNo ratings yet

- FDR AnalogDocument13 pagesFDR AnalogSree VBroNo ratings yet

- MODEM Schematic Baseband SchematicDocument60 pagesMODEM Schematic Baseband SchematicSnaked514No ratings yet

- Wistron GodzillaDocument61 pagesWistron Godzillarodrigootavio5No ratings yet

- Digitronik CPL Communication SDC40A/40G User's ManualDocument66 pagesDigitronik CPL Communication SDC40A/40G User's ManualnarkomanizcaNo ratings yet

- Project Name: I4XIXX Platform: Montevina Merom (CPU) +cantiga (NB) +ICH9M (SB)Document37 pagesProject Name: I4XIXX Platform: Montevina Merom (CPU) +cantiga (NB) +ICH9M (SB)sousalrNo ratings yet

- Tribhuvan University Institute of Engineering Pulchowk, Lalipur A Lab Report On Embedded SystemDocument24 pagesTribhuvan University Institute of Engineering Pulchowk, Lalipur A Lab Report On Embedded SystemSaroj Katwal0% (1)

- PIC16C773Document202 pagesPIC16C773Luis Oliveira SilvaNo ratings yet

- 8-Bit Microcontroller With 12K Bytes Flash AT89S53: FeaturesDocument32 pages8-Bit Microcontroller With 12K Bytes Flash AT89S53: Featuresapi-3808344No ratings yet

- 8-Bit Microcontroller With 12K Bytes Flash AT89S53: FeaturesDocument32 pages8-Bit Microcontroller With 12K Bytes Flash AT89S53: FeaturesJOSEPH GOMEZ SAENZNo ratings yet

- 8085 PRJ Schematic 1Document44 pages8085 PRJ Schematic 1Jani ServiniNo ratings yet

- The Engineering of Microprocessor Systems: Guidelines on System DevelopmentFrom EverandThe Engineering of Microprocessor Systems: Guidelines on System DevelopmentNo ratings yet

- 8051 Microcontroller: An Applications Based IntroductionFrom Everand8051 Microcontroller: An Applications Based IntroductionRating: 5 out of 5 stars5/5 (6)

- ECO2201 - Slides - 0.1 Class IntroductionDocument22 pagesECO2201 - Slides - 0.1 Class Introductionjokerightwegmail.com joke1233No ratings yet

- Guidelines of PBL - MBA (22-24) Sem IIDocument8 pagesGuidelines of PBL - MBA (22-24) Sem IIShivnath KarmakarNo ratings yet

- Copy of البيانات المفتوحة - المنتجات الصناعية - صناعات المعدات والآلات - 01Document83 pagesCopy of البيانات المفتوحة - المنتجات الصناعية - صناعات المعدات والآلات - 01mohammed sohsahNo ratings yet

- ASTM C806-12 Restrained Expansion of Expansive Cement MortarDocument4 pagesASTM C806-12 Restrained Expansion of Expansive Cement MortarAlonso SojoNo ratings yet

- Data Sheet: NPN General Purpose TransistorDocument8 pagesData Sheet: NPN General Purpose TransistorNewsUPdateNo ratings yet

- A. Levitin "Introduction To The Design & Analysis of Algorithms," 3rd EdDocument70 pagesA. Levitin "Introduction To The Design & Analysis of Algorithms," 3rd EdAmro AbosaifNo ratings yet

- Linking Your Thinking - Idea EmergenceDocument1 pageLinking Your Thinking - Idea EmergenceLee NamNo ratings yet

- Standards For Email SecurityDocument2 pagesStandards For Email SecurityPeng GuinNo ratings yet

- KerosDocument9 pagesKerosMarius Mihail BențaNo ratings yet

- READ ME - InfoDocument2 pagesREAD ME - InfoSalih AktaşNo ratings yet

- Omarlift Brochure - HM Pump UnitDocument1 pageOmarlift Brochure - HM Pump UnitKhaled ZakariaNo ratings yet

- Globalsat Gps Module: Hardware Data Sheet Product No: EM-506Document21 pagesGlobalsat Gps Module: Hardware Data Sheet Product No: EM-506Svaruu SectaNo ratings yet

- SSP 370 Crafter Electrical SystemDocument84 pagesSSP 370 Crafter Electrical SystemJavier GarciaNo ratings yet

- Circular Queue Program Using PointerDocument9 pagesCircular Queue Program Using Pointerpbasu2011No ratings yet

- Chapter 1-Introduction: Online Shopping (Sometimes Known As E-Tail From "Electronic Retail" or E-Shopping) Is A FormDocument32 pagesChapter 1-Introduction: Online Shopping (Sometimes Known As E-Tail From "Electronic Retail" or E-Shopping) Is A FormdevilsharmaNo ratings yet

- 19 Gear Wheel Lubrication Solutuion ENGDocument3 pages19 Gear Wheel Lubrication Solutuion ENGhaftu gideyNo ratings yet

- 47Lm7600 Interconnect Diagram: P702 N/C Backlight B+ 60V LD701 ErrorDocument1 page47Lm7600 Interconnect Diagram: P702 N/C Backlight B+ 60V LD701 Errorruben mapaloNo ratings yet

- Ex Booster PumpDocument20 pagesEx Booster PumpNelson P. ColoNo ratings yet

- UGC Net StatisticsDocument47 pagesUGC Net StatisticsSumant SharmaNo ratings yet

- Protocompiler WPDocument13 pagesProtocompiler WPajaysimha_vlsiNo ratings yet

- SAP CO-PC Material Cost Estimate - EUGDocument38 pagesSAP CO-PC Material Cost Estimate - EUGLantNo ratings yet

- Aircon Heat Load Calculation Sheet: Project Name: GO TAN HIEP Address: Bien Hoa Dong NaiDocument6 pagesAircon Heat Load Calculation Sheet: Project Name: GO TAN HIEP Address: Bien Hoa Dong NaiNGUYEN THANH LUANNo ratings yet

- TrussDocument43 pagesTrussTanuj Bhardwaj75% (4)

- My Daily Routine UNIT 3Document5 pagesMy Daily Routine UNIT 3Francisco EricesNo ratings yet

- Week 4 (Educational Technology) Answer KeyDocument4 pagesWeek 4 (Educational Technology) Answer KeyChristian PadillaNo ratings yet

- M5300 - Data SheetDocument2 pagesM5300 - Data SheetKaren IsananNo ratings yet

- Intro To Software Quality AssuranceDocument30 pagesIntro To Software Quality AssuranceMarneil Allen SanchezNo ratings yet

- Handbook of Metal Injection MoldingDocument3 pagesHandbook of Metal Injection MoldingPk Jha0% (2)