Professional Documents

Culture Documents

Apl6012 Anpec

Uploaded by

Александр ОсадчийOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Apl6012 Anpec

Uploaded by

Александр ОсадчийCopyright:

Available Formats

APL6012

Low-Power, 8-bit, 15-Channel Analog to Digital Converters

Features General Description

• Supply Input Voltages Range: 2.8V to 5.5V The APL6012 is a precision analog-to-digital converters

• 100uA Low Support Current (ADCs) with 8 bits of resolution, which designed with

• 15-Ch Analog Voltage Input: AIN1, AIN2, AIN3, precision, low power and ease of implementation in mind.

Data are transferred via an I2C-compatible serial interface.

• AIN4, AIN5, AIN6, AIN7, AIN8, AIN9, AIN10, AIN11,

Three voltage sensing inputs are available for monitor-

AIN12, AIN13, AIN14, AIN15.

ing the temperature of the system. It measures voltage

• High Accuracy Nonlinearity: +1.5LSB

form the monitor place to GND by NTC resistor divider

• High Accuracy A/D Resolution: 10mV

voltages. The sensed voltages are digitized and inter-

• High Accuracy A/D Full Scale Range: 1~3.56V faced with microprocessor by I2C bus for advanced power

• Built-in Alert Flag Functions management procedures.

• Built-in I2C Address Programming Functions The APL6012 operates from a single power supply rang-

ing from 2.8V to 5.5V.

Pin Configurations This APL6012 is available in TQFN3x3-20P package.

APL6012

AIN15

AIN14

AIN13

AIN12

AIN11

20 19 18 17 16

Applications

SDA 1 15 AIN10

SCL

• Phone & NB Application

2 14 AIN9

• Temperature Measurement

VDD 3

GND 13 AIN8

• Portable Instrumentation

GND AIN7

•

4 12

Consumer Goods

ADD/ALT 5 11 AIN6

6 7 8 9 10

AIN1

AIN2

AIN3

AIN4

AIN5

TQFN 3x3-20P

(Top View)

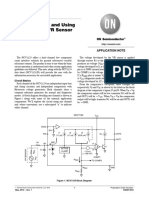

Simplified Application Circuit

R1 R1

Alert/ADDR VDD VDD Alert/ADDR VDD VDD

R2

CVDD CVDD

GND GND

RIN1 RIN1

VIN AIN1 VIN AIN1

RNTC1 C1 APL6012 RNTC1 C1 APL6012

RSCL RSDA RSCL RSDA

SCL SCL

RIN15 RIN15

AIN15 SDA AIN15 SDA

RNTC15 C15 RNTC15 C15

ANPEC reserves the right to make changes to improve reliability or manufacturability without notice, and

advise customers to obtain the latest version of relevant information to verify before placing orders.

Copyright ANPEC Electronics Corp. 1 www.anpec.com.tw

Rev. A.3 - Jun., 2019

APL6012

Ordering and Marking Information

APL6012 Package Code

QB : TQFN 3x3-20P

Operating Ambient Temperature Range

I : -40 to 85°C

Assembly Material

Handling Code

Handling Code

TR : Tape & Reel

Temperature Range Assembly Material

Package Code G : Halogen and Lead Free Device

APL

APL6012 QBI 6012 X : Date Code

XXXXX

Note : ANPEC lead-free products contain molding compounds/die attach materials and 100% matte tin plate termination finish; which

are fully compliant with RoHS. ANPEC lead-free products meet or exceed the lead-free requirements of IPC/JEDEC J-STD-020D for

MSL classification at lead-free peak reflow temperature. ANPEC defines “Green” to mean lead-free (RoHS compliant)and halogen

free (Br or Cl does not exceed 900ppm by weight in homogeneous material and total of Br and Cl does not exceed 1500ppm by

weight).

Absolute Maximum Ratings (Note 1)

Symbol Param eter Rating Unit

VDD V DD Sup ply Voltag e, VDD to GND -0.3 ~ 6.0 V

Inpu t & Outpu t or I/O (A lert/ADDR, S CL , SDA, AIN1, AIN2, AIN3 ,A IN4, AIN5,

VI/O -0 .3 ~ V DD V

A IN6, AIN7, AIN8 , A IN9 , AIN10, AIN11 , AIN1 2, A IN13 , A IN14 , A IN1 5.) voltages

PD P owe r Dissipa tion Interna lly Limi ted W

TJ Junction Tempera tu re 15 0 °C

T STG Storag e Temp erature -65 ~ 15 0 °C

TSD R Maximum Lea d Solde ring Temperature (10 Se co nds) 26 0 °C

(Hum an Body Mode) ±2

VESD Minim um ES D Rating (Machi ne Mode) 0 .2 kV

(Cha rged -De vice Mod e) +1.5

Note1: Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are

stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recom-

mended operating conditions" is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device

reliability.

Thermal Characteristics

Symbol P arame ter Typical Va lue Unit

θJA Ju nctio n-to-Ambi ent Resista nce in fre e a ir (Note 2 ) 65 °C/W

Note 2 : θJA is measured with the component mounted on a high effective thermal conductivity test board in free air.

Recommended Operating Conditions (Note 3)

Symbol Param eter Range Unit

VDD V DD Sup ply Voltag e, VDD to GND 2 .8 ~ 5.5 V

VI/O Inpu t & Outpu t pins (Ale rt/ADDR, SCL, SDA) volta ge 0 ~ VDD V

Inpu t pins (AIN1, AIN2 , AIN3,AIN4, AIN5, A IN6 , AIN7, AIN8, AIN9, AIN10 ,

VAIN 1 ~ 3.56 V

A IN11, A IN1 2, AIN13 , AIN1 4, AIN15 .) voltage

TA Amb ient Temp erature - 40 ~ 85 °C

TJ Junction Tempera tu re -40 ~ 12 5 °C

Copyright ANPEC Electronics Corp. 2 www.anpec.com.tw

Rev. A.3 - Jun., 2019

APL6012

Electrical Characteristics

Unless otherwise specified, these specifications apply over VDD=5V, and TJ= -40 to 85oC. Typical values are at TJ=25oC.

Specification

Symbol Param eter Te st condition Unit

Min. Typ. Ma x.

SUPPLY CURRENT

I VDD VDD Input Cu rrent - 80 100 uA

POWER-ON RESET (PO R)

V POR VDD POR Threshold Voltage VDD Risin g 2.35 2 .5 2.6 V

VPOR_Hys VDD POR Hysteresis Vo ltag e VDD Falling - 0 .3 - V

Voltage Monitor

A/D A/D Reso lution - 10 - mV/LSB

A/D Fu ll Sca le Range 1 - 3.5 6 V

Diffe rential non linea rity - - 1.5 LSB

Diffe rential non linea rity VDD=3.6 V - - 2.5 LSB

Integra l n onlin earity - - 1.5 LSB

Integra l n onlin earity VDD=3.6 V - - 2.5 LSB

Inpu t Bia s Curren t - - 10 nA

AIN1, AIN2, AIN3 , AIN4, AIN5,

AIN6, AIN7, AIN8 , AIN9, AIN10,

0.48 0 .6 0.7 2 ms

AIN11, AIN1 2, AIN13 , AIN14 , A IN15 .

Moni to r Time

Address Setting and Ale rt Output

ADDR Address Latch Time - - 10 ms

Address 1 Vol tag e Ra nge Ad dress = 0x7 E (Hex) 92 95 100 %VDD

Address 2 Vol tag e Ra nge Ad dress = 0x7 C (Hex) 82 85 88 %VDD

Address 3 Vol tag e Ra nge Ad dress = 0x7 A (Hex) 72 75 78 %VDD

Address 4 Vol tag e Ra nge Ad dress = 0x7 8 (Hex) 63 65 68 %VDD

Address 5 Vol tag e Ra nge Ad dress = 0x7 6 (Hex) 52 55 58 %VDD

Address 6 Vol tag e Ra nge Ad dress = 0x7 4 (Hex) 42 45 48 %VDD

Address 7 Vol tag e Ra nge Ad dress = 0x7 2 (Hex) 32 35 38 %VDD

Address 8 Vol tag e Ra nge Ad dress = 0x7 0 (Hex) 22 25 28 %VDD

Whe n Ale rt/ADDR p in pull low, IALT =10 mA - - 0.2 V

Al ert Alert O utput L ow Voltage

Whe n Ale rt/ADDR p in pull low, IALT =50 mA - - 0.8 V

Alert P ull Low Pulse Time Whe n Ale rt/ADDR p in Ale rt 40 50 60 us

Alert P ull Low cycle Time Whe n Ale rt/ADDR p in Ale rt - 2 - s

Alert/A DDR Leaka ge Cu rrent VAl ert/AD DR=5V - - 100 nA

2

I C Interfac e

2

F I2C I C Cl ock Rate Ra nge 1 40 0 440 kHz

I 2C In put High Voltage 1.4 - - V

2

I C In put L ow Voltage - - 0.4 V

2

I C Leakag e Cu rrent VSC L=V SDA=5 V - - 100 nA

Copyright ANPEC Electronics Corp. 3 www.anpec.com.tw

Rev. A.3 - Jun., 2019

APL6012

Electrical Characteristics (Cont.)

Timing characteristics for I2C Interface signals over recommended operating conditions (unless otherwise noted)

Fast Spee d

Symbol Parame ter Unit

Min. Ma x.

f SCL Fr eque ncy, SCL - 400 kHz

t W(H ) Pul se Dura tio n, SCL High 600 - ns

t W(L) Pu lse Dura ti on, S CL Low 13 00 - ns

tr Rise Time , SCL and SDA 20+0.1 C L(pF) 300 ns

tf Fal l Time, SCL and SDA 20+0.1 C L(pF) 300 ns

t setup1 Setup Time , SCL to SDA 100 - ns

th old 1 Hold Time, SCL to S DA 100 - ns

t (b uf) Bus Free Time Between Stop and Start Con dition 13 00 - ns

t setup2 S etup Time, SCL to Start Co ndition 600 - ns

th old 2 Hold Time , Star t condition to SCL 600 - ns

t setup3 Setup Time , SCL to Sto p Co ndition 600 - ns

CL Lo ad Ca pacitance fo r E ach Bus L ine - 400 pF

SDA

tsetup1 thold1

SCL

tW(H) tW(L) tf tr

SDA and SCL Timing

SDA

tsetup2 thold2 tsetup3 t(buf)

SCL

Start Condition Stop Condition

Start and Stop Condition Timing

Copyright ANPEC Electronics Corp. 4 www.anpec.com.tw

Rev. A.3 - Jun., 2019

APL6012

Typical Operating Characteristics

AIN1~15 vs. Reg0x0F~1D Quiescent Current vs. VDD

5.0 120

4.5

100

4.0

Quiescent Current (µA)

AINx Input Voltage (V)

3.5

80

3.0

2.5 60

2.0

40

1.5

1.0

20

0.5

0.0 0

0 25 50 75 100 125 150 175 200 225 250 275 3.0 3.5 4.0 4.5 5.0 5.5 6.0

Read Reg0x0F~1D (Dec.) VDD Input Voltage (V)

Quiescent Current vs. Temperature Alert Low Pulse Time vs. VDD

120 60

ALT/ADD Pull Low Time (µs)

100 50

Quiescent Current (µA)

80 40

60 30

40 20

20 10

0 0

-50 -25 0 25 50 75 100 125 150 3 3.5 4 4.5 5 5.5 6

o

Junction Temperature ( C) VDD Input Voltage (V)

Alert Low Pulse Time vs.

Temperature

60

55

ALT/ADD Pull Low Time (µs)

50

45

40

35

30

25

20

15

10

5

0

-50 -25 0 25 50 75 100 125 150

o

Junction Temperature ( C)

Copyright ANPEC Electronics Corp. 5 www.anpec.com.tw

Rev. A.3 - Jun., 2019

APL6012

Pin Description

PIN

FUNCTION

NO. NA ME

1 SDA I2 C interface Data I/O pin. Con nect this pin to I 2C bus data sign al.

2 SCL I2 C interface Clock I/O p in. Conn ect this p in to I 2C bus clock sign al.

3 VDD De vice po we r sup ply p in. Con nect this p in with 0.1uF capacitor.

4 GND Sign al and Po wer Ground . All th e voltage l eve ls a re me asured by reference to th is pin .

Addr ess Sel ectio n and Th ermal Alert. Conn ect a vo lta ge divider to sel ect the APL601 2 I 2C add ress.

5 Aler t/ADDR When an yon e of VAINx is lo we r tha n se tting voltage, i t will pull low and send a lert sign al to the system

. Conn ect th is pin withou t any ca pacitor. Do not leav e NC(ADDR) pin floating.

6 AIN1 Anal og Volta ge In put 1 .

7 AIN2 Anal og Volta ge In put 2 .

8 AIN3 Anal og Volta ge In put 3 .

9 AIN4 Anal og Volta ge In put 4 .

10 AIN5 Anal og Volta ge In put 5 .

11 AIN6 Anal og Volta ge In put 6 .

12 AIN7 Anal og Volta ge In put 7 .

13 AIN8 Anal og Volta ge In put 8 .

14 AIN9 Anal og Volta ge In put 9 .

15 AIN10 Anal og Volta ge In put 1 0.

16 AIN11 Anal og Volta ge In put 11.

17 AIN12 Anal og Volta ge In put 1 2.

18 AIN13 Anal og Volta ge In put 1 3.

19 AIN14 Anal og Volta ge In put 1 4.

20 AIN15 Anal og Volta ge In put 1 5.

Copyright ANPEC Electronics Corp. 6 www.anpec.com.tw

Rev. A.3 - Jun., 2019

APL6012

Block Diagram

VDD POR Reference

Alert/ADDR SCL

I2C Interface

SDA

Control Logic

GND

A/D Converter AIN1

AIN2

AIN3

Timing Control AIN4

AIN5

AIN6

AIN15

AIN14

AIN13

AIN12

AIN11

AIN10

AIN9

AIN8

AIN7

Copyright ANPEC Electronics Corp. 7 www.anpec.com.tw

Rev. A.3 - Jun., 2019

APL6012

Typical Application Circuit

The I2C Address Programming and Alert Flag functions are used.

R1

Alert/ADDR VDD VDD

R2

CVDD

GND

RIN1

VIN AIN1

RNTC1 C1 APL6012

RSCL RSDA

SCL

RIN15

AIN15 SDA

RNTC15 C15

The I2C Address is used as default and Alert Flag function is unused.

R1

Alert/ADDR VDD VDD

CVDD

GND

RIN1

VIN AIN1

RNTC1 C1 APL6012

RSCL RSDA

SCL

RIN15

AIN15 SDA

RNTC15 C15

VAINx = 1~3.56V is recommended.

RINx and RNTCx = 10kΩ~10MΩ is recommended.

CVDD, C1, C2 and C3 > 0.1uF is recommended.

RSCL and RSDA = 1kΩ~10kΩ is recommended.

Copyright ANPEC Electronics Corp. 8 www.anpec.com.tw

Rev. A.3 - Jun., 2019

APL6012

Function Description

Input Voltage and Power-On-Reset

The APL6012 can work normally and start monitoring the AINx voltage, when the supply voltage VDD is greater than the

POR. The POR threshold is 2.5V typically when the VDD rising.

SDA stable Data change

I2C Interface Data Validity

The SCL voltage level can only be changed to Low to High, SDA

when the SDA is stable unless the START and STOP status.

The SDA can only be changed the voltage level when the

SCL

SCL voltage is Low.

Data valid SCL level Low

I2C Start and Stop Conditions

The START (S) condition is the SDA transient from High to SDA

Low, when SCL is High. The STOP (P) condition is the SDA

transient from Low to High, when SCL is High. The STOP SCL

condition must send before each START condition.

START (S) STOP (P)

I2C Acknowledge Slave SDA pull Low

Each Address and Data are transmitted by using 8 clock

pulses with 1 clock pulse Acknowledge (A). The Acknowl- SDA Bit 1 Bit 0 ACK

edge is used for two purposes: one is the device that recog-

nizes its own address. Another one is all of the master and

SCL

slave to acknowledge receipt the register address or data.

The SDA will pull Low to acknowledge. Master SDA pull Low

Read and Write Protocol

MSB to LSB MSB to LSB MSB to LSB

0

SDA 7-Bit Slave Address

(W)

A 8-Bit Register Address A 8-Bit Register Data for Address A

SCL

S P

Master Write to a Slave Register Example

MSB to LSB MSB to LSB MSB to LSB MSB to LSB

0 1

SDA 7-Bit Slave Address

(W)

A 8-Bit Register Address A 7-Bit Slave Address

(R)

A 8-Bit Register Data for Address NA

SCL

S S P

Master Read from a Slave Register Example

(S=START, P=STOP, A=ACK from Slave, NA=Non-ACK)

Copyright ANPEC Electronics Corp. 9 www.anpec.com.tw

Rev. A.3 - Jun., 2019

APL6012

Function Description (Cont.)

I2C Address Programming

Alert/ADDR I2C

VDD

The APL6012 I2C address is programmable, which can Interface

R1 R2

be selected from 0x70h to 0x7Eh by the 7-bit slave ad-

dress with one R/W bit. The slave device compares the Alert

7-bit slave address with its address and matches. The Control

Logic

programmable address is selected by a voltage divider

R1 and R2. The Alert/ADDR pin voltage is compared with

8 addresses available internal reference voltage for ad-

Address 0x70 0x72 0x74 0x76 0x78 0x7A 0x7C 0x7E

dress programming.

R1 (kOhm) 6 5.1 4.3 3.9 3.6 2 1.5 10

Note: If the address programming function is not used,

R2 (kOhm) 2 2.7 3.6 4.7 6.8 6.2 8.2 Open

the Alert/ADDR pin must be connected to VDD via a resis-

ALT/ADDR

25 35 45 55 65 75 85 100

tor and the I2C address is used as default value 0x7Eh. (% of VDD)

Voltage Monitoring and I2C Programming Interface 0x7E

The AINx voltages are digitized directly by high precision Address Selection (Hex) 0x7C

A/D converter and interfaced to the I2C bus. The AINx volt- 0x7A

ages are sensed alternately and take 0.6ms every 0x78

channel. 0x76

When the VDD supply voltage range from 2.8 to 5.5V, the 0x74

A/D converter have 10mV of resolution, and 1 to 3.56V of

0x72

full scale range. The A/D converter sensing results are

0x70

stored in the internal register that shows as follow: 0 10 20 30 40 50 60 70 80 90 100

ADDR Input Voltage (% of VDD)

AIN1 A/D data store (TD1): Reg0x0F[7] (MSB) ~ Reg0x0F

[0] (LSB) AINx A/D

VDD

AIN2 A/D data store (TD2): Reg0x10[7] (MSB) ~ Reg0x10 Converter

RINx RNTCx Cx

[0] (LSB)

.................. I2C

AIN14 A/D data store (TD14): Reg0x1C[7] (MSB) ~ Interface

Reg0x1C[0] (LSB)

AIN15 A/D data store (TD15): Reg0x1D[7] (MSB) ~

Reg0x1D[0] (LSB)

If the internal register code is read as CodeX in integer decimal format, the AINx voltage transition to the internal

register Reg0x03, Reg0x04 and Reg0x05 calculation as follows:

VAINx − 1V

Code X = or VAINx = (10mV × Code X ) + 1V

10mV

The voltage divider at VIN-RINx-RNTCx-GND sets the voltage AINx is calculated as:

R NTCx

VAINx = VIN ×

RINx + RNTCx

According to the above equation:

RNTCx

VIN × R + R − 1V

Code X = INx NTCx

10mV

Note: If the AINx pin is not used, that must be pulled to the high level. And the CX is recommended to bypass the AINx pin.

Copyright ANPEC Electronics Corp. 10 www.anpec.com.tw

Rev. A.3 - Jun., 2019

APL6012

Function Description (Cont.)

Alert Flag

The Alert Flag is used to indicate the system state.

When the setting condition is established at the AINx voltage, the APL6012 will make the internal MOS in the Alert pin

turns on and pull low 50us every 2s cycle time.

Alert Threshold Level Setting

The Alert levels are set in the internal register by I2C interface shows as follows:

AIN1 Alert level set-up (TL1): Reg0x00[7] (MSB) ~ Reg0x00[0] (LSB)

AIN2 Alert level set-up (TL2): Reg0x01[7] (MSB) ~ Reg0x01[0] (LSB)

....................

AIN14 Alert level set-up (TL14): Reg0x0D[7] (MSB) ~ Reg0x0D[0] (LSB)

AIN15 Alert level set-up (TL15): Reg0x0E[7] (MSB) ~ Reg0x0E[0] (LSB)

If one of conditions is established include TL1>TD1, TL2>TD2 ... TL14>TD14, TL15>TD15 the Alert function will be

enabled, and the Alert Indication of internal resistor Reg0x1E[7:0] and Reg0x1F[6:0] will be set to 1 that shows as

below:

If the Reg0x00 (TL1) > Reg0x0F (TD1), than the bit Reg0x1E [0] = 1, else the bit Reg0x1E [0] = 0

If the Reg0x01 (TL2) > Reg0x10 (TD2), than the bit Reg0x1E [1] = 1, else the bit Reg0x1E [1] = 0

..................

If the Reg0x0D (TL14) > Reg0x1C (TD14), than the bit Reg0x1F [5] = 1, else the bit Reg0x1F [5] = 0

If the Reg0x0E (TL15) > Reg0x1D (TD15), than the bit Reg0x1F [6] = 1, else the bit Reg0x1F [6] = 0

Chip ID: Reg0xB2[7:0] = 0x1A

I2C Registers Summary

Re gister Re gister Bi ts Re ad/ De fa ult

Add ress Na me D7 D6 D5 D4 D3 D2 D1 D0 Write Value

0x00 TL1 TL 1[7:0 ] R/W 00h

0x01 TL2 TL 2[7:0 ] R/W 00h

0x02 TL3 TL 3[7:0 ] R/W 00h

0x03 TD1 TD1 [7:0] R 00h

0x04 TD2 TD2 [7:0] R 00h

0x05 TD3 TD3 [7:0] R 00h

0x06 ALT Re ve rsed AM3 AM2 AM1 Reversed R 00h

0xB2 Chi p ID Chip ID = 0 x1A R 1Ah

Copyright ANPEC Electronics Corp. 11 www.anpec.com.tw

Rev. A.3 - Jun., 2019

APL6012

Function Description (Cont.)

I2C Registers Summary

Reg ister Re gister Bits Rea d/ Default

Addr ess Na me D7 D6 D5 D4 D3 D2 D1 D0 Write Valu e

0x00 TL1 TL1 [7 :0] R/W 8'h00

0x01 TL2 TL2 [7 :0] R/W 8'h00

0x02 TL3 TL3 [7 :0] R/W 8'h00

0x03 TL4 TL4 [7 :0] R/W 8'h00

0x04 TL5 TL5 [7 :0] R/W 8'h00

0x05 TL6 TL6 [7 :0] R/W 8'h00

0x06 TL7 TL7 [7 :0] R/W 8'h00

0x07 TL8 TL8 [7 :0] R/W 8'h00

0x08 TL9 TL9 [7 :0] R/W 8'h00

0x09 TL 10 TL 10[7:0] R/W 8'h00

0x0A TL11 TL11[7:0] R/W 8'h00

0x0B TL 12 TL 12[7:0] R/W 8'h00

0x0C TL 13 TL 13[7:0] R/W 8'h00

0x0D TL 14 TL 14[7:0] R/W 8'h00

0x0E TL 15 TL 15[7:0] R/W 8'h00

0 x0 F TD1 TD1[7:0] R 8'h00

0x10 TD2 TD2[7:0] R 8'h00

0x11 TD3 TD3[7:0] R 8'h00

0x12 TD4 TD4[7:0] R 8'h00

0x13 TD5 TD5[7:0] R 8'h00

0x14 TD6 TD6[7:0] R 8'h00

0x15 TD7 TD7[7:0] R 8'h00

0x16 TD8 TD8[7:0] R 8'h00

0x17 TD9 TD9[7:0] R 8'h00

0x18 TD1 0 TD10[7:0] R 8'h00

0x19 TD11 TD11 [7 :0] R 8'h00

0x1A TD1 2 TD12[7:0] R 8'h00

0x1B TD1 3 TD13[7:0] R 8'h00

0x1C TD1 4 TD14[7:0] R 8'h00

0x1D TD1 5 TD15[7:0] R 8'h00

0x1E ALT ALT_AM8 ALT_A M7 A LT_AM6 ALT_AM5 ALT_AM4 ALT_AM3 ALT_AM2 ALT_AM1 R 8'h00

0 x1 F ALT Rese rve d ALT_ AM15 ALT_A M14 A LT_A M1 3 A LT_AM1 2 ALT_AM11 A LT_AM1 0 ALT_AM9 R 8'h00

0xB2 Ch ip ID VE NDOR_ID _ Chip ID = 0x1A R 1Ah

Copyright ANPEC Electronics Corp. 12 www.anpec.com.tw

Rev. A.3 - Jun., 2019

APL6012

Recommended Minimum Footprint

TQFN3x3-20

3mm

20 19 18 17 16

0.5mm *

0.2mm 1 15

2 14

1.66

mm

3 13

3mm

4 12

0.4mm

5 11

0.17

1.66 mm mm

0.5mm 6 7 8 9 10

* Just Recommend

Copyright ANPEC Electronics Corp. 13 www.anpec.com.tw

Rev. A.3 - Jun., 2019

APL6012

Manufature Information

APL6012 manufaturing information. Including wafer fab and assembly location.

ANP EC Device Man ufature Assembly

APL 6012 TSMC G TK / A SE

ANPEC Electronic Corp.

Account manager

Kevin Chang

Copyright ANPEC Electronics Corp. 14 www.anpec.com.tw

Rev. A.3 - Jun., 2019

APL6012

Package Information

TQFN3x3-20P

D A

b

E

Pin 1

A1

A3

D2 NX

aaa C

20 19 18 17 16

1 15

2 14

3 Pin 1 Corner 13

E2

4 12

5 11

K

L

6 7 8 9 10

S TQFN3x3-20

Y

M MILLIMETERS INCHES

B

O

L MIN. MAX. MIN. MAX.

A 0.70 0.80 0.028 0.031

A1 0.00 0.05 0.000 0.002

A3 0.20 REF 0.008 REF

b 0.15 0.25 0.006 0.010

D 2.90 3.10 0.114 0.122

D2 1.50 1.80 0.059 0.071

E 2.90 3.10 0.114 0.122

E2 1.50 1.80 0.059 0.071

e 0.40 BSC 0.016 BSC

L 0.30 0.50 0.012 0.020

K 0.20 0.008

aaa 0.08 0.003

Note : 1. Followed from JEDEC MO-220 WEEE

Copyright ANPEC Electronics Corp. 15 www.anpec.com.tw

Rev. A.3 - Jun., 2019

APL6012

Carrier Tape & Reel Dimensions

OD0 P0 P2 P1 A

E1

F

W

B0

K0 A0 A

OD1 B

B

SECTION A-A

T

SECTION B-B

d

H

A

T1

Application A H T1 C d D W E1 F

330±2.00 50 MIN. 12.4+2.00 13.0+0.50 1.5 MIN. 20.2 MIN. 12.0±0.30 1.75±0.10 5.5±0.05

-0.00 -0.20

TQFN 3x3 P0 P1 P2 D0 D1 T A0 B0 K0

1.5+0.10 0.6+0.00

4.0±0.10 8.0±0.10 2.0±0.05 -0.00 1.5 MIN. -0.40 3.30±0.20 3.30±0.20 1.00±0.20

(mm)

Devices Per Unit

Package Type Unit Quantity

TQFN3x3-20 Tape & Reel 3000

Copyright ANPEC Electronics Corp. 16 www.anpec.com.tw

Rev. A.3 - Jun., 2019

APL6012

Taping Direction Information

TQFN3x3-20P

USER DIRECTION OF FEED

Copyright ANPEC Electronics Corp. 17 www.anpec.com.tw

Rev. A.3 - Jun., 2019

APL6012

Classification Profile

Classification Reflow Profiles

Profile Feature Sn-Pb Eutectic Assembly Pb-Free Assembly

Preheat & Soak

100 °C 150 °C

Temperature min (Tsmin)

150 °C 200 °C

Temperature max (Tsmax)

60-120 seconds 60-120 seconds

Time (Tsmin to Tsmax) (ts)

Average ramp-up rate

3 °C/second max. 3°C/second max.

(Tsmax to TP)

Liquidous temperature (TL) 183 °C 217 °C

Time at liquidous (tL) 60-150 seconds 60-150 seconds

Peak package body Temperature

See Classification Temp in table 1 See Classification Temp in table 2

(Tp)*

Time (tP)** within 5°C of the specified

20** seconds 30** seconds

classification temperature (Tc)

Average ramp-down rate (Tp to Tsmax) 6 °C/second max. 6 °C/second max.

Time 25°C to peak temperature 6 minutes max. 8 minutes max.

* Tolerance for peak profile Temperature (Tp) is defined as a supplier minimum and a user maximum.

** Tolerance for time at peak profile temperature (tp) is defined as a supplier minimum and a user maximum.

Copyright ANPEC Electronics Corp. 18 www.anpec.com.tw

Rev. A.3 - Jun., 2019

APL6012

Classification Reflow Profiles (Cont.)

Table 1. SnPb Eutectic Process – Classification Temperatures (Tc)

3 3

Package Volume mm Volume mm

Thickness <350 ≥350

<2.5 mm 235 °C 220 °C

≥2.5 mm 220 °C 220 °C

Table 2. Pb-free Process – Classification Temperatures (Tc)

3 3 3

Package Volume mm Volume mm Volume mm

Thickness <350 350-2000 >2000

<1.6 mm 260 °C 260 °C 260 °C

1.6 mm – 2.5 mm 260 °C 250 °C 245 °C

≥2.5 mm 250 °C 245 °C 245 °C

Reliability Test Program

Test item Method Description

SOLDERABILITY JESD-22, B102 5 Sec, 245°C

HOLT JESD-22, A108 1000 Hrs, Bias @ Tj=125°C

PCT JESD-22, A102 168 Hrs, 100%RH, 2atm, 121°C

TCT JESD-22, A104 500 Cycles, -65°C~150°C

HBM MIL-STD-883-3015.7 VHBM≧2KV

MM JESD-22, A115 VMM≧200V

Latch-Up JESD 78 10ms, 1tr≧100mA

Customer Service

Anpec Electronics Corp.

Head Office :

No.6, Dusing 1st Road, SBIP,

Hsin-Chu, Taiwan, R.O.C.

Tel : 886-3-5642000

Fax : 886-3-5642050

Taipei Branch :

2F, No. 11, Lane 218, Sec 2 Jhongsing Rd.,

Sindian City, Taipei County 23146, Taiwan

Tel : 886-2-2910-3838

Fax : 886-2-2917-3838

Copyright ANPEC Electronics Corp. 19 www.anpec.com.tw

Rev. A.3 - Jun., 2019

You might also like

- Beginning Digital Electronics through ProjectsFrom EverandBeginning Digital Electronics through ProjectsRating: 5 out of 5 stars5/5 (1)

- M012/M013 Service ManualDocument201 pagesM012/M013 Service ManualJean AlmeidaNo ratings yet

- IP2312 English VersionDocument11 pagesIP2312 English VersionWawan Aris0% (1)

- MATHEMATICS 4 Quarter 1 Week 5: CompetencyDocument10 pagesMATHEMATICS 4 Quarter 1 Week 5: CompetencyJhenzNo ratings yet

- Teaching Intership Learning Task 13 PDFDocument6 pagesTeaching Intership Learning Task 13 PDFKristine Joyce Nodalo83% (6)

- EGPM10-H2S-I-DAT-001 H2S DetectorsDocument1 pageEGPM10-H2S-I-DAT-001 H2S DetectorsdrkongalaNo ratings yet

- Method Statement For InstallationDocument5 pagesMethod Statement For Installationsamsul maarifNo ratings yet

- TLC 2543Document40 pagesTLC 2543Hoii ClarkNo ratings yet

- K Type Thermocouple Meseurement Circuit With Precision ADCDocument9 pagesK Type Thermocouple Meseurement Circuit With Precision ADCmehdi.bzinebNo ratings yet

- AD7175 2模块说明书Document7 pagesAD7175 2模块说明书rakibul hasanNo ratings yet

- Circuito Conversor A-D Cy100 BoschDocument5 pagesCircuito Conversor A-D Cy100 BoschAlberto MiglinoNo ratings yet

- REN Isl6292 DST 20031205Document23 pagesREN Isl6292 DST 20031205123No ratings yet

- Dna-Stp-Ai-U: General DescriptionDocument2 pagesDna-Stp-Ai-U: General DescriptionnpcopeNo ratings yet

- 8-/10-Channel, Low Voltage, Low Power,: - AdcsDocument44 pages8-/10-Channel, Low Voltage, Low Power,: - AdcsjuenkkinNo ratings yet

- O 4 YBAFoc UKSAXSva AAJs 0 QD OJg Q291Document7 pagesO 4 YBAFoc UKSAXSva AAJs 0 QD OJg Q291Ryan LeisNo ratings yet

- Embedded ASIC Macrocell: Power Management RE028 Fixed 4.5V 30 Ma LDO Voltage RegulatorDocument9 pagesEmbedded ASIC Macrocell: Power Management RE028 Fixed 4.5V 30 Ma LDO Voltage RegulatorHILLNo ratings yet

- Datasheet AP7175Document14 pagesDatasheet AP7175Edwin SorianoNo ratings yet

- Isl 6561Document27 pagesIsl 6561PristisNo ratings yet

- Adc 78 H 90Document26 pagesAdc 78 H 90moacirmenezes51No ratings yet

- BOSCH CJ135 Product Information 101201Document2 pagesBOSCH CJ135 Product Information 101201Wang Zheng Feng100% (1)

- +2.7 V To +5.5 V, 350 KSPS, 10-Bit 4-/8-Channel Sampling AdcsDocument1 page+2.7 V To +5.5 V, 350 KSPS, 10-Bit 4-/8-Channel Sampling AdcsAntonio HerreraNo ratings yet

- Description Features: LTC4555 SIM Power Supply and Level TranslatorDocument8 pagesDescription Features: LTC4555 SIM Power Supply and Level TranslatorIoana TecuceanuNo ratings yet

- An5092 Ais328dq Highperformance Ultralowpower 3axis Digital Output Accelerometer For Automotive Nonsafety Applications StmicroelectronicsDocument30 pagesAn5092 Ais328dq Highperformance Ultralowpower 3axis Digital Output Accelerometer For Automotive Nonsafety Applications Stmicroelectronicstomislav_darlicNo ratings yet

- Iw248 Datasheet-3075945Document19 pagesIw248 Datasheet-3075945hussamNo ratings yet

- Manual LAN Controller V30 LANKON-008 enDocument36 pagesManual LAN Controller V30 LANKON-008 enoctavvvianNo ratings yet

- Adc128s022 PDFDocument20 pagesAdc128s022 PDFThiagoNo ratings yet

- CS1124 Dual Variable-Reluctance Sensor Interface IC: FeaturesDocument8 pagesCS1124 Dual Variable-Reluctance Sensor Interface IC: FeaturesJose M PeresNo ratings yet

- NE/SA/SE5521 LVDT Signal Conditioner: Description Pin ConfigurationsDocument5 pagesNE/SA/SE5521 LVDT Signal Conditioner: Description Pin ConfigurationsAriel SanusiNo ratings yet

- An 7851Document13 pagesAn 7851MultiAbderrahmaneNo ratings yet

- Sky65171-11: 1930 - 1990 MHZ, 0.5 W High Power Power AmplifierDocument10 pagesSky65171-11: 1930 - 1990 MHZ, 0.5 W High Power Power AmplifiercopslockNo ratings yet

- AWINIC Shanghai Awinic Tech AW9120QNR - C506177 1Document33 pagesAWINIC Shanghai Awinic Tech AW9120QNR - C506177 1asdNo ratings yet

- DatasheetDocument14 pagesDatasheetsamaya egNo ratings yet

- Max 31865Document26 pagesMax 31865Văn CôngNo ratings yet

- AL8860EV2 User GuideDocument8 pagesAL8860EV2 User GuideHans ClarinNo ratings yet

- REN Isl8014a DST 20030828Document16 pagesREN Isl8014a DST 20030828cer cerNo ratings yet

- AL8861EV1 User GuideDocument8 pagesAL8861EV1 User GuideHans ClarinNo ratings yet

- IDT ZMID520x Short Form Datasheet SDS 20170524Document2 pagesIDT ZMID520x Short Form Datasheet SDS 20170524dineshNo ratings yet

- 1581 DatasheetDocument17 pages1581 Datasheettekchan2002No ratings yet

- Standard Air-Conditioning Units: EpstdeczuaDocument36 pagesStandard Air-Conditioning Units: Epstdeczuaمحمد عليNo ratings yet

- TDI TDO ISP Connector Target Device Target SystemDocument2 pagesTDI TDO ISP Connector Target Device Target SystembrahimNo ratings yet

- High Performance Digital MEMS Microphone Simple2Document6 pagesHigh Performance Digital MEMS Microphone Simple2LeonardusNo ratings yet

- HX711 Avia SemiconductorDocument9 pagesHX711 Avia SemiconductorAnjar Bangsa MimpiNo ratings yet

- Ne5521 Sa5521 2Document11 pagesNe5521 Sa5521 2José AdelinoNo ratings yet

- Adns 2030Document34 pagesAdns 2030Mandy AbaszadeNo ratings yet

- Ina 168Document27 pagesIna 168Merlin SithNo ratings yet

- GP Controller Data Sheet: Description Mounting InstructionsDocument2 pagesGP Controller Data Sheet: Description Mounting Instructionsdima65No ratings yet

- Features: High Efficiency Display Power and LED Driver For Smart PhonesDocument2 pagesFeatures: High Efficiency Display Power and LED Driver For Smart PhonesCenter ElectronicNo ratings yet

- Features Description: Micropower Inverting DC/DC ConverterDocument6 pagesFeatures Description: Micropower Inverting DC/DC ConverterJosé FariaNo ratings yet

- 163-Glove Control Car (TX)Document1 page163-Glove Control Car (TX)zulNo ratings yet

- Application Note Atmel-46004-SE-M90E36A-DatasheetDocument87 pagesApplication Note Atmel-46004-SE-M90E36A-DatasheetHafi UddinNo ratings yet

- Riga, Latvia WWW - Alfarzpp.lv Alfa@alfarzpp - LV: +IN1 - IN1 I A1 E +VDocument4 pagesRiga, Latvia WWW - Alfarzpp.lv Alfa@alfarzpp - LV: +IN1 - IN1 I A1 E +VHama AieaNo ratings yet

- Interfacing - ADC & DAC: ADC (Analog To Digital Converter)Document8 pagesInterfacing - ADC & DAC: ADC (Analog To Digital Converter)Jagan VNo ratings yet

- Schematic PrintsDocument1 pageSchematic Printsthong lyNo ratings yet

- Service Manual: Panel Assy (A64-2962-08)Document26 pagesService Manual: Panel Assy (A64-2962-08)Ербол ЖакуповNo ratings yet

- High Voltage 8-CH LED Driver: Features General DescriptionDocument13 pagesHigh Voltage 8-CH LED Driver: Features General DescriptionSetiawan Abdul RochimNo ratings yet

- 4.5V To 25V Input, 1ch Synchronous Buck DC/DC Controller: DatasheetDocument24 pages4.5V To 25V Input, 1ch Synchronous Buck DC/DC Controller: DatasheetYnejjamNo ratings yet

- Datasheet Ic CE DEDocument15 pagesDatasheet Ic CE DEBersama UkhuwahNo ratings yet

- Sky65170-11: 860 - 900 MHZ, 0.5 W High Power Power AmplifierDocument10 pagesSky65170-11: 860 - 900 MHZ, 0.5 W High Power Power AmplifiercopslockNo ratings yet

- Instrukcja Home ENDocument24 pagesInstrukcja Home ENN. P.No ratings yet

- Apl 5920Document18 pagesApl 5920Las Dus100% (1)

- Aprea 2002Document14 pagesAprea 2002VIKNESWARAN S KNo ratings yet

- Denver Developmental Screening Test InterpretationDocument1 pageDenver Developmental Screening Test InterpretationJames PanlaanNo ratings yet

- SOPDocument2 pagesSOPwingwiryawanNo ratings yet

- Titan T200 Spec SheetDocument2 pagesTitan T200 Spec SheetKim JunNo ratings yet

- Solution Manual For Introductory Econometrics A Modern Approach 6Th Edition Wooldridge 130527010X 9781305270107 Full Chapter PDFDocument29 pagesSolution Manual For Introductory Econometrics A Modern Approach 6Th Edition Wooldridge 130527010X 9781305270107 Full Chapter PDFlois.payne328100% (18)

- CV Adinda Putri MDocument1 pageCV Adinda Putri MVeena GamingNo ratings yet

- Transfer Learning PDFDocument10 pagesTransfer Learning PDFajaytiwari2779No ratings yet

- Valve EnglishDocument4 pagesValve English唐志康No ratings yet

- Iso 27018 CertificateDocument5 pagesIso 27018 CertificateJose antolin CoriaNo ratings yet

- Pythagoras School of MathematicsDocument4 pagesPythagoras School of Mathematicssulys SimanjuntakNo ratings yet

- Accenture G20 YEA 2015 Open Innovation Executive Summary PDFDocument24 pagesAccenture G20 YEA 2015 Open Innovation Executive Summary PDFJulian Dario Combariza GonzalezNo ratings yet

- COMM 400 Assignment #1 My StoryDocument4 pagesCOMM 400 Assignment #1 My StoryMegan 'Hall' AdamsNo ratings yet

- 06 Introduction To Philosophy PDFDocument8 pages06 Introduction To Philosophy PDFRhue DadorNo ratings yet

- Self-Accelerated Corrosion of Nuclear Waste Forms at Material InterfacesDocument9 pagesSelf-Accelerated Corrosion of Nuclear Waste Forms at Material InterfacesMuhammad Adnan HafeezNo ratings yet

- Restructuring of L TDocument11 pagesRestructuring of L TRahul BhatiaNo ratings yet

- Variability in The Project Completion DateDocument12 pagesVariability in The Project Completion DateNguyễn Quốc ViệtNo ratings yet

- The Translation of Serious Literature & Authoritative Statements - Poetry - Patricia Iris v. RazonDocument20 pagesThe Translation of Serious Literature & Authoritative Statements - Poetry - Patricia Iris v. RazonPatricia Iris Villafuerte RazonNo ratings yet

- CSS 211Document173 pagesCSS 211Adikwu Anyebe OwoichoNo ratings yet

- Whole Digital Communication PPT-libreDocument319 pagesWhole Digital Communication PPT-librePiyush GuptaNo ratings yet

- Part 1 Picture Description Theme NotesDocument46 pagesPart 1 Picture Description Theme Notesrichard0% (1)

- Types of SoilDocument9 pagesTypes of SoilNilima Aparajita SahuNo ratings yet

- Hydrotech Company ProfileDocument46 pagesHydrotech Company ProfileBOBANSO KIOKONo ratings yet

- Project Report On Business Eco Magazine - Vivek Kumar ShawDocument36 pagesProject Report On Business Eco Magazine - Vivek Kumar ShawAnand shawNo ratings yet

- LimnaiosG Final ReportDocument11 pagesLimnaiosG Final ReportGiorgos LakemanNo ratings yet

- 6599892Document127 pages6599892Dino Martin Mercado QuispeNo ratings yet