0% found this document useful (0 votes)

107 views53 pagesModule 4 Intel 80386DX Processor New

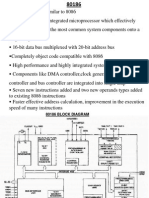

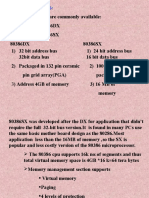

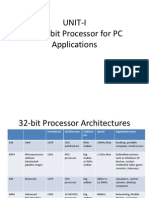

The Intel 80386 processor comes in two versions, the 80386DX and 80386SX, with different data and address bus capabilities. It features a 32-bit architecture that allows for advanced memory management, multitasking, and compatibility with older processors, while operating in Real, Protected, and Virtual 8086 modes. The processor includes a complex internal architecture with dedicated units for execution, memory management, and instruction decoding, enhancing performance through pipelining and prefetching mechanisms.

Uploaded by

priyasiri0120Copyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

107 views53 pagesModule 4 Intel 80386DX Processor New

The Intel 80386 processor comes in two versions, the 80386DX and 80386SX, with different data and address bus capabilities. It features a 32-bit architecture that allows for advanced memory management, multitasking, and compatibility with older processors, while operating in Real, Protected, and Virtual 8086 modes. The processor includes a complex internal architecture with dedicated units for execution, memory management, and instruction decoding, enhancing performance through pipelining and prefetching mechanisms.

Uploaded by

priyasiri0120Copyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd