Professional Documents

Culture Documents

Electrical Validation For DDR Io Interface

Uploaded by

Yeshoda MallikarjunaOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Electrical Validation For DDR Io Interface

Uploaded by

Yeshoda MallikarjunaCopyright:

Available Formats

ELECTRICAL

VALIDATION FOR

DDR IO INTERFACE

Under the Guidance

of

Prof. M. S. Bhat Bhide Amruta A

NITK Surathkal Intel Technology India Pvt. Ltd.

Presented by

Dipak Prakash Bankar

09VL07F

12/09/21 M. Tech. VLSI Design NITK Surathkal. 1

Agenda :

What is EV In general?

Importance.

What is DDR Interface?

Brief About DDR RAM.

Evolution Of DDR.

DDR3 Signals.

DDR3 protocol.

EV for DDR.

Flyby Topology.

Delay Locked Loop

Characterization of DLL.

References.

12/09/21 M. Tech. VLSI Design NITK Surathkal. 2

What is EV in general?

• It comes under post silicon Validation.

• Done over Process, Voltage and Temperature

variations.

• Done at

» Platform Level

» Component Level

12/09/21 M. Tech. VLSI Design NITK Surathkal. 3

Importance.

12/09/21 M. Tech. VLSI Design NITK Surathkal. 4

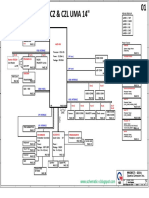

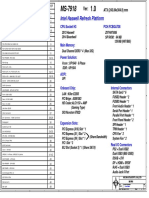

What is DDR interface? SATA/

USB/

PCIe/AG Other LAN

P(Graphic Devices HDMIPORTS

s)

DDR Interface

APM/ PCI/P AC97/HD

Memory Slots

ACPI CIe (AUDIO)

Bus

12/09/21 M. Tech. VLSI Design NITK Surathkal. 5

What is DDR interface? SATA/

USB/

PCIe/AG

P(Graphic Other LAN

s) Devices HDMIPORTS

Two Die

one package

DDR Interface

APM/ PCI/P AC97/HD

DDR ACPI CIe (AUDIO)

Slots Bus

12/09/21 M. Tech. VLSI Design NITK Surathkal. 6

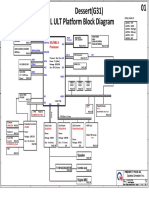

What is DDR interface?

PCIe/AG

VGA HDMI P(Graphic

s)

Other

APM/

Devices

ACPI

PCI/P SATA/

CIe USB/

Bus LAN

PORTS

DDR Interface

DDR Slots

12/09/21 M. Tech. VLSI Design NITK Surathkal. 7

Brief about DDR(RAM).

• Evolution of DDR.

• DDR3 Signals.

• DDR3 protocol.

– READ

– WRITE

12/09/21 M. Tech. VLSI Design NITK Surathkal. 8

Evolution of DDR.

• Evolved from SDR

12/09/21 M. Tech. VLSI Design NITK Surathkal. 9

Evolution of DDR.

• DDR1.

Additional

Stubs and Stub

Lengths

12/09/21 M. Tech. VLSI Design NITK Surathkal. 10

Evolution of DDR.

• DDR2.

Additional

Stubs and Stub

Lengths

12/09/21 M. Tech. VLSI Design NITK Surathkal. 11

Evolution of DDR.

• DDR3.

12/09/21 M. Tech. VLSI Design NITK Surathkal. 12

DDR3 Signals Groups.

• Command group

WE# : Write Enable

RAS# : Row Address Select

CAS# : Column Address Select

12/09/21 M. Tech. VLSI Design NITK Surathkal. 13

DDR3 Signals Groups.

• Clock

CK/CK# :

- Differential.

- Free running.

- all data, address, command and control signals are sampled on the

crossing of clock.

12/09/21 M. Tech. VLSI Design NITK Surathkal. 14

DDR3 Signals Groups.

• Control group

CKE : Clock Enable

- Activate and deactivate internal clock signals and device input buffers and

output drivers.

- CKE LOW provides Pre-charge Power-Down and Self

Refresh operation.

CS : Chip Select

- CS provides for external

Rank selection on systems with multiple Ranks.

- All commands are masked when CS is registered HIGH.

ODT : On Die Termination

- ODT (registered HIGH) enables termination resistance internal to the

DDR3 SDRAM.

- Allows the DRAM to turn on/off termination resistance for each DQ,

DQS, DQS#.

12/09/21 M. Tech. VLSI Design NITK Surathkal. 15

DDR3 Signals Groups.

• Data group

DQS/DQS# [7:0] : Data Strobe

- Differential.

- Acts as clock for data.

- Starts from Tristate.

DQ[63:0]

- Single ended Bi-directional.

- Center aligned w.r.t. DQS during write.

- Edge aligned w.r.t. DQS during read.

- 1 DQS is associated with each 8-bit data(DQ)

DM[7:0] : Write Data Mask

- 1 for each 8-bit data (DQ).

12/09/21 M. Tech. VLSI Design NITK Surathkal. 16

DDR3 Protocol.

• WRITE

• READ

12/09/21 M. Tech. VLSI Design NITK Surathkal. 17

DDR3 Protocol.

• WRITE

12/09/21 M. Tech. VLSI Design NITK Surathkal. 18

DDR3 Protocol.

• READ

12/09/21 M. Tech. VLSI Design NITK Surathkal. 19

EV For DDR.

• Platform Level - Signal Integrity

Addresses two concerns in the electrical design aspects

- the timing and

- the quality of the signal

The goal of signal integrity analysis is to ensure reliable high-speed data

transmission.

12/09/21 M. Tech. VLSI Design NITK Surathkal. 20

EV For DDR.

• Platform Level - Signal Integrity

Main issues of SI

• Reflection Noise

• Due to impedance mismatch, stubs, vias and other interconnect

discontinuities.

• Crosstalk Noise

• Due to electromagnetic coupling between signal traces and vias.

• Power/Ground Noise

• Due to paracitic of the power/ground delivery system during drivers’

simultaneous switching output (SSO). It is sometimes also called

Ground Bounce, Delta-I Noise or Simultaneous Switching Noise (SSN).

12/09/21 M. Tech. VLSI Design NITK Surathkal. 21

EV for DDR.

• Platform Level - Signal Integrity

1. Clk to DQS Skew

2. Clk VIX

3. Clock Jitter characterization

4. Dq-Dqs timing

5. Clk-Control timing

6. Clk-Command timing

12/09/21 M. Tech. VLSI Design NITK Surathkal. 22

EV for DDR.

• Platform Level - Signal Integrity

1. Clk to DQS Skew

12/09/21 M. Tech. VLSI Design NITK Surathkal. 23

EV for DDR.

• Platform Level - Signal Integrity

2. Clk VIX

12/09/21 M. Tech. VLSI Design NITK Surathkal. 24

EV for DDR.

• Platform Level - Signal Integrity

2. Clk VIX

12/09/21 M. Tech. VLSI Design NITK Surathkal. 25

EV for DDR.

• Platform Level - Signal Integrity

4. Dq-Dqs timing

12/09/21 M. Tech. VLSI Design NITK Surathkal. 26

EV for DDR.

• Platform Level - Signal Integrity

5. Clk-Control(CS#) timing

12/09/21 M. Tech. VLSI Design NITK Surathkal. 27

EV for DDR.

• Platform Level - Signal Integrity

6. Clk-Command (WE#) timing

12/09/21 M. Tech. VLSI Design NITK Surathkal. 28

EV for DDR.

• Component Level

Characterization Of AC timings

- Slew Rate

- Duty Cycle

- Noise Margins

- Set up and Hold check

12/09/21 M. Tech. VLSI Design NITK Surathkal. 29

EV For DDR.

Process Temperature Voltage

(˚C) (V)

Board Component (Processor)

LOW-Z Slow Low Low

High-Z Fast High High

Typical typical Typical Typical

12/09/21 M. Tech. VLSI Design NITK Surathkal. 30

Flyby topology.

Flyby topology.

• Clock gets skewed

• DQS should be skewed accordingly

• Uses programmable Delay element

known as Delay Locked Loop(DLL).

Delay Locked Loop(DLL)

Phase Fast/Slow

Clk in Detector Control

Delay Line

12/09/21 M. Tech. VLSI Design NITK Surathkal. 33

Characterization of DLL(My

Work).

• Code Vs Delay

Characterization of DLL.

• DNL

Characterization of DLL.

• INL

References

•JEDEC

•www.csee.umbc.edu/research/vlsi/reports/si_chapter.pdf

•“Clocking in Modern VLSI System” by Thucydides Xanthopoulos, Spinger.

•Intel Internal Reference Documents

12/09/21 M. Tech. VLSI Design NITK Surathkal. 37

12/09/21 M. Tech. VLSI Design NITK Surathkal. 38

You might also like

- GV451 GV551 NM-D151 Rev 1.0 PDFDocument65 pagesGV451 GV551 NM-D151 Rev 1.0 PDFПавел В. (Bis Nival - IrBis Snow)No ratings yet

- DDR Design Part 1 PCB-May2011Document4 pagesDDR Design Part 1 PCB-May2011Mudassar SaeedNo ratings yet

- RS-232 Cabling TutorialDocument13 pagesRS-232 Cabling TutorialAlvin CheangNo ratings yet

- ASIC Tape Out: Designers' Perspective: C-DAC All Rights Reserved C-DAC/TVM/HDG/Aug'12Document62 pagesASIC Tape Out: Designers' Perspective: C-DAC All Rights Reserved C-DAC/TVM/HDG/Aug'12Gopakumar GnairNo ratings yet

- Block DiagramDocument12 pagesBlock DiagramDavid LópezNo ratings yet

- VLSI Design MethodologyDocument72 pagesVLSI Design MethodologyMandovi BorthakurNo ratings yet

- ASIC Interview Question & Answer: Memory Interface QuestionsDocument5 pagesASIC Interview Question & Answer: Memory Interface QuestionsRajendra PrasadNo ratings yet

- Day 1Document25 pagesDay 1Abdul SatharNo ratings yet

- PCB Design Techniques For DDR, DDR2 & DDR3: (Part 1)Document3 pagesPCB Design Techniques For DDR, DDR2 & DDR3: (Part 1)Praveen KumarNo ratings yet

- HW and Layout Design Consideration For DDR3 SDRAM Memory InterfacesDocument14 pagesHW and Layout Design Consideration For DDR3 SDRAM Memory InterfacesZoltán BaranyaiNo ratings yet

- Vector IRAM: A Microprocessor Architecture For Media ProcessingDocument15 pagesVector IRAM: A Microprocessor Architecture For Media ProcessingNoman Ali ShahNo ratings yet

- RTP DDR2 DDR3 PCBDocument80 pagesRTP DDR2 DDR3 PCBVăn LinNo ratings yet

- Hardware and Layout Design Considerations For DDR2 SDRAM Memory InterfacesDocument16 pagesHardware and Layout Design Considerations For DDR2 SDRAM Memory Interfacesreza_azadNo ratings yet

- 13 Applications XilinxDocument23 pages13 Applications Xilinxaksh26No ratings yet

- Msi MS-7137 - Rev 1.3Document33 pagesMsi MS-7137 - Rev 1.3Mauro CamiloNo ratings yet

- CZC Digital Technologies Co.,LTD: CPL S01 (R48)Document54 pagesCZC Digital Technologies Co.,LTD: CPL S01 (R48)Joaquin Koki VenturaNo ratings yet

- SD Card Specification: Model NameDocument10 pagesSD Card Specification: Model NameVishwanath RmNo ratings yet

- Xilinx Spartan-6 FPGA DDR3 Signal Integrity Analysis and PCB Layout GuidelinesDocument19 pagesXilinx Spartan-6 FPGA DDR3 Signal Integrity Analysis and PCB Layout GuidelinesSanjay SharmaNo ratings yet

- Cat24c208 DDocument11 pagesCat24c208 Dreza_azadNo ratings yet

- RoverBook Laptop Motherboard Schematic Diagram PDFDocument51 pagesRoverBook Laptop Motherboard Schematic Diagram PDFDelwar Hossain100% (1)

- CS 252 Graduate Computer Architecture Lecture 1 - IntroductionDocument41 pagesCS 252 Graduate Computer Architecture Lecture 1 - IntroductionGusti ArsyadNo ratings yet

- Tms 320 LC 203Document88 pagesTms 320 LC 203valtercleyton.martinsNo ratings yet

- Digital Axle CountersDocument20 pagesDigital Axle Counterssagar tanejaNo ratings yet

- The Fpga As A Flexible and Low-Cost Digital Solution For Wireless Base StationsDocument16 pagesThe Fpga As A Flexible and Low-Cost Digital Solution For Wireless Base StationsozgurNo ratings yet

- Forum Digital Design and Programming ASIC Design Methodologies and Tools (Digital)Document9 pagesForum Digital Design and Programming ASIC Design Methodologies and Tools (Digital)kishoreroy88No ratings yet

- 6050A2357502-MB-A02 T1-CT10 Toshiba Satellite C600 C640Document56 pages6050A2357502-MB-A02 T1-CT10 Toshiba Satellite C600 C640Yetawa GuaviareNo ratings yet

- Satellite c640 c600 6050a2357502mba02t1 Ct10 Laptop SchematicsDocument56 pagesSatellite c640 c600 6050a2357502mba02t1 Ct10 Laptop SchematicsDuy Tan20% (5)

- Introduction To VLSI DesignDocument24 pagesIntroduction To VLSI DesignRajesh PylaNo ratings yet

- MemoriesDocument7 pagesMemoriesanushaNo ratings yet

- Mr. A. B. Shinde: Assistant Professor, Electronics Engineering, PVPIT, BudhgaonDocument34 pagesMr. A. B. Shinde: Assistant Professor, Electronics Engineering, PVPIT, BudhgaonpremkumarNo ratings yet

- HP Elitebook 8460pDocument62 pagesHP Elitebook 8460pFerreira da Cunha0% (1)

- VLSI FPGA Projects Topics Using VHDL - Verilog - VLSI EncyclopediaDocument4 pagesVLSI FPGA Projects Topics Using VHDL - Verilog - VLSI EncyclopediaGunapalli venkata saikiranNo ratings yet

- 1 Introduction To VLSI DesignDocument42 pages1 Introduction To VLSI Designawan gamingNo ratings yet

- Protable Computer Group HW Department: First International Computer, IncDocument54 pagesProtable Computer Group HW Department: First International Computer, IncEduardoSobrinhoNo ratings yet

- IC Design & Low Power TechniquesDocument11 pagesIC Design & Low Power TechniquesMohamed AliNo ratings yet

- Report On: "Library Cell Implementation of RHBDDocument7 pagesReport On: "Library Cell Implementation of RHBDTasmiyaNo ratings yet

- Msi ms-7204 Rev 30 SCHDocument33 pagesMsi ms-7204 Rev 30 SCHТарас ІщакNo ratings yet

- Imec Reveals Sub-1nm Transistor Roadmap, 3D-Stacked CMOS 2.0 Plans - Tom's HardwareDocument10 pagesImec Reveals Sub-1nm Transistor Roadmap, 3D-Stacked CMOS 2.0 Plans - Tom's Hardwareandresgarcia500No ratings yet

- HP TouchSmart 310 (Quanta ZN2) PDFDocument49 pagesHP TouchSmart 310 (Quanta ZN2) PDFJuan Carlos Anguiano NegreteNo ratings yet

- Dell Inspiron 5370 Armani13 MBDocument75 pagesDell Inspiron 5370 Armani13 MBtech kitabNo ratings yet

- Msi Ms-168a R0a SchematicsDocument52 pagesMsi Ms-168a R0a SchematicsAlexMAXNo ratings yet

- DCCT SyllabusDocument11 pagesDCCT SyllabusmkmaithalNo ratings yet

- Cadence PPTDocument18 pagesCadence PPTSatyanarayan PadhyNo ratings yet

- TDC VerifiedDocument8 pagesTDC VerifiedeejlnyNo ratings yet

- Brkarc 1001Document87 pagesBrkarc 1001fezzfezzNo ratings yet

- Sony Vaio Vgn-Ns Series Foxconn m790!1!01 Rev 1.0 SCHDocument54 pagesSony Vaio Vgn-Ns Series Foxconn m790!1!01 Rev 1.0 SCHCarlos Henrique RibasNo ratings yet

- Toshiba Satellite L300 - L305 INVENTEC PS10S 6050A2170401-MB-A03 SchematicDocument63 pagesToshiba Satellite L300 - L305 INVENTEC PS10S 6050A2170401-MB-A03 SchematicMohammed AbdullahNo ratings yet

- Hardware and Layout Design Considerations For DDRDocument48 pagesHardware and Layout Design Considerations For DDRmuralikonathamNo ratings yet

- Null Modem WikiDocument5 pagesNull Modem WikiSantiago CorderoNo ratings yet

- C600 - C640 Inventec Insyde 6050A2357502Document56 pagesC600 - C640 Inventec Insyde 6050A2357502Orbit IdtechNo ratings yet

- Sony Vaio VGN-AW Series MBX-194 M780 SD FOXCONN M780 CantigaP WPCE775LDocument77 pagesSony Vaio VGN-AW Series MBX-194 M780 SD FOXCONN M780 CantigaP WPCE775LChetin TekinNo ratings yet

- ASIC Technology: A Brief Introduction To The ASIC Technology and It's Design FlowDocument54 pagesASIC Technology: A Brief Introduction To The ASIC Technology and It's Design FlowmayurNo ratings yet

- Microcontrollers and Embedded SystemsDocument49 pagesMicrocontrollers and Embedded SystemsTarek BarhoumNo ratings yet

- 13-1 CH05.Hardware Implementation For Fast EncryptionDocument54 pages13-1 CH05.Hardware Implementation For Fast EncryptionSai PNo ratings yet

- Know The Common IT Acronyms: June 2014Document7 pagesKnow The Common IT Acronyms: June 2014the deanNo ratings yet

- Satellite C640 - PSC02G-01400G. 6050A2357502-MB-A02-TI PDFDocument56 pagesSatellite C640 - PSC02G-01400G. 6050A2357502-MB-A02-TI PDFDanielle DDNo ratings yet

- Fujitsu Siemens Amilo Pro v2030 Fic Lm7r Rev 0.1 SCHDocument55 pagesFujitsu Siemens Amilo Pro v2030 Fic Lm7r Rev 0.1 SCHBogumiła SzmydtNo ratings yet

- Scaling & EconomicsDocument29 pagesScaling & EconomicsRoshdy AbdelRassoulNo ratings yet

- Seminar and Workshop: D.B.Rajesh Application EngineerDocument56 pagesSeminar and Workshop: D.B.Rajesh Application EngineerKama Raj KrNo ratings yet

- Gain-Cell Embedded DRAMs for Low-Power VLSI Systems-on-ChipFrom EverandGain-Cell Embedded DRAMs for Low-Power VLSI Systems-on-ChipNo ratings yet

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- CCNA 200-301 Day 21Document49 pagesCCNA 200-301 Day 21renjithkalaNo ratings yet

- Quanta G51A Rev 1ADocument41 pagesQuanta G51A Rev 1Acamilo jimenez catañoNo ratings yet

- SFP - SF Passport DatasheetDocument2 pagesSFP - SF Passport Datasheetjorge fonsecaNo ratings yet

- Msi MS-7137 - Rev 1.3Document33 pagesMsi MS-7137 - Rev 1.3Mauro CamiloNo ratings yet

- Quanta G31a Dag31amb6d0 Y61x-6l Rev 1aDocument49 pagesQuanta G31a Dag31amb6d0 Y61x-6l Rev 1aKrystian PalaciosNo ratings yet

- LAN Cabling: CCNA Instructor Training Course October 12-17, 2009 Department of Computer Engineering Kasetsart UniversityDocument23 pagesLAN Cabling: CCNA Instructor Training Course October 12-17, 2009 Department of Computer Engineering Kasetsart Universityxích longNo ratings yet

- Acopladores e Adaptadores Thunderbolt 3Document6 pagesAcopladores e Adaptadores Thunderbolt 3Carlos Eduardo CastroNo ratings yet

- Comparisson Wifi 6 D-Link Vs Unifi AP and Watchguard APDocument21 pagesComparisson Wifi 6 D-Link Vs Unifi AP and Watchguard APyazi adityasNo ratings yet

- RJ11 RJ12 RJ45Document2 pagesRJ11 RJ12 RJ45Hassan ChaoukiNo ratings yet

- Ekinops PM - Lc2-Mp2-B: 200G Line Module For ETS Compact ChassisDocument2 pagesEkinops PM - Lc2-Mp2-B: 200G Line Module For ETS Compact ChassisBhargav SomepalliNo ratings yet

- Acer A515-56 - FH4AT - LA-K091PDocument102 pagesAcer A515-56 - FH4AT - LA-K091PDude JonesNo ratings yet

- Eletro-X - GA-H61M-DS2 (REV 2.1)Document30 pagesEletro-X - GA-H61M-DS2 (REV 2.1)Tomy Aditya PratamaNo ratings yet

- Acer Aspire V5-551G 1 Quanta ZRP - RevA1ADocument44 pagesAcer Aspire V5-551G 1 Quanta ZRP - RevA1ATom ArcillaNo ratings yet

- Gigabyte 8simlh - Rev 3.02Document32 pagesGigabyte 8simlh - Rev 3.02Denis MartinsNo ratings yet

- Afs Gigabyte Ga-H110m-S2h-Ddr3-1.0 (PDF Boardview)Document2 pagesAfs Gigabyte Ga-H110m-S2h-Ddr3-1.0 (PDF Boardview)Евгений КуценкоNo ratings yet

- POS-PIQ170U - POS-PIB150DT SchematicsDocument75 pagesPOS-PIQ170U - POS-PIB150DT SchematicsAmilcar SilvaNo ratings yet

- Chapter 6 ExercisesDocument3 pagesChapter 6 ExercisesarrgantenNo ratings yet

- Msi MS-7918 1.0Document53 pagesMsi MS-7918 1.0Antonio C C manzanoNo ratings yet

- Full Size PICMG 1.3Document2 pagesFull Size PICMG 1.3Warr SteelNo ratings yet

- Usb 3.0 DriverDocument11 pagesUsb 3.0 DriverAlex GmimNo ratings yet

- Gigabyte Ga-h81m-Ds2 Rev. 3.0 - EditDocument29 pagesGigabyte Ga-h81m-Ds2 Rev. 3.0 - Editvandung100% (1)

- HP Ahl50 Abl52 La-C701pDocument61 pagesHP Ahl50 Abl52 La-C701pmohammadsajjad sedqiNo ratings yet

- IEEE802 11WLAN-slidesDocument32 pagesIEEE802 11WLAN-slidesshaik shariffNo ratings yet

- Lista de Precios 20 - 11Document172 pagesLista de Precios 20 - 11yamilchabezpNo ratings yet

- Acer Swift SF713-51 BoxsterDino Da0zdsmbaf0 ZDS ZDV - MB - RAMP 1Document42 pagesAcer Swift SF713-51 BoxsterDino Da0zdsmbaf0 ZDS ZDV - MB - RAMP 1Antonio García MartínezNo ratings yet

- Amilo M1450GDocument35 pagesAmilo M1450Gali takbirNo ratings yet

- P50-2831TV5.0原理图 20180625Document12 pagesP50-2831TV5.0原理图 20180625Juan David GonzalezNo ratings yet

- Absolut - MV2 Build 6050a2162301 A04-1Document61 pagesAbsolut - MV2 Build 6050a2162301 A04-1CiprianIfrimNo ratings yet