Professional Documents

Culture Documents

RL4 1 4

Uploaded by

Pooja SOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

RL4 1 4

Uploaded by

Pooja SCopyright:

Available Formats

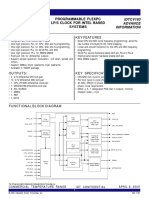

LPC 23XX- TIMER

M3: Embedded Architectures- 2: ARM based LPC23xx

Features

• Four Timer/Counters

• 4 channels/Timer

• A minimum of 2 capture i/ps & 2 Match o/ps are pinned out for all 4

timers

• Choice of several pins for each

• 32 bit Timer/Counter with programmable 32 bit Prescaler

• Counter / Timer operation

RL4.1.4 Embedded System Design © K.R.Anupama &

2

Meetha.V.shenoy

Example

• Program LPC 23xx to count the no. of objects crossing a particular

point within a period of 1 second. Also find the time interval

between two objects

RL4.1.4 Embedded System Design © K.R.Anupama &

3

Meetha.V.shenoy

INPUT CAPTURE

RL4.1.4 Embedded System Design © K.R.Anupama &

4

Meetha.V.shenoy

Channel 0 CAP0.0

Channel 1 CAP0.1

Channel 2

Channel 3

Timer 0

RL4.1.4 Embedded System Design © K.R.Anupama &

5

Meetha.V.shenoy

Input Capture EDGB:EDGA

CLK

000A

0005

32-bit Counter

H PT

Edge

000A

0005HReg

Capture Detector

CF

CI Interrupt Logic

Interrupt Request

RL4.1.4 Embedded System Design © K.R.Anupama &

6

Meetha.V.shenoy

Program for Input Capture

Turn on Timer 0/1/2/3

PCONP

Bit1 :PCTIM0

Enabled on Reset

Bit2 :PCTIM1

Bit22 :PCTIM2

Bit23 :PCTIM3

PINSEL Registers

RL4.1.4 Embedded System Design © K.R.Anupama &

7

Meetha.V.shenoy

Input Capture 0.0 P1.26 AltF3, P3.23 AltF2

Input Capture 0.1 P1.27 AltF3, P3.24 AltF2

Input Capture 1.0 P1.18 AltF3

Input Capture 1.1 P1.19 AltF3

Input Capture 2.0 P0.4 AltF3

Input Capture 2.1 P0.5 AltF3

Input Capture 3.0 P0.23 AltF3

Input Capture 3.1 P0.24 AltF3

RL4.1.4 Embedded System Design © K.R.Anupama &

8

Meetha.V.shenoy

Program for Input Capture

Clock for Timer 0/1/2/3

PCLK Selection Register 0

0 0 CCLK/4

Bit2-3 :PCLK_TIMER0

Bit4-5 :PCLK_TIMER1 0 1 CCLK

PCLK Selection Register 1

1 0 CCLK/2

Bit12-13 :PCLK_TIMER2

Bit14-15 :PCLK_TIMER3 1 1 CCLK/8

RL4.1.4 Embedded System Design © K.R.Anupama &

9

Meetha.V.shenoy

Program for Input Capture

Pre Scale for Timer 0/1/2/3

TxPR

TxPC

TxC

RL4.1.4 Embedded System Design © K.R.Anupama &

10

Meetha.V.shenoy

Select Clock for Timer/Counter

Counter Control Register for Timer 0/1/2/3

CCxR

CIS1 CIS0 CM1 CMO

CAP x.0 0 0 0 0 Rising Edge

PCLK

CAP x.1 1 0 0 1 Rising edge

CAP

Resv 0 1 1 0 Falling edge

CAP

Resv 1 1 1 1 Both edges

CAP

RL4.1.4 Embedded System Design © K.R.Anupama &

11

Meetha.V.shenoy

PCLK SEL 0:1 CPR

1/2/4/8 Pre-Scale+1

CCLK

Counter

CAP

CCR

RL4.1.4 Embedded System Design © K.R.Anupama &

12

Meetha.V.shenoy

Program for Input Capture

Capture Registers for Timer 0/1/2/3

TxCCR

CA1I CAP1FE CAP1RE CA0I CAP0FE CAP0RE

Program Interrupt Unit

RL4.1.4 Embedded System Design © K.R.Anupama &

13

Meetha.V.shenoy

Program for Input Capture

TxCR

TR TE

RL4.1.4 Embedded System Design © K.R.Anupama &

14

Meetha.V.shenoy

Program for Input Capture

TxIR

IC3 IC2 IC1 IC0 IM3 IM2 IM1 IM0

Ack Interrupt

RL4.1.4 Embedded System Design © K.R.Anupama &

15

Meetha.V.shenoy

Program for Input Capture

Capture Registers for Timer 0/1/2/3

TxCR0-TxCR3

RL4.1.4 Embedded System Design © K.R.Anupama &

16

Meetha.V.shenoy

OUTPUT COMPARE

RL4.1.4 Embedded System Design © K.R.Anupama &

17

Meetha.V.shenoy

Features

4 32 bit match registers that allow

Continuous op with optional int generation on match

Stop timer on match with optional int generation

Reset timer on match with optional int generation

Up to 4 external o/ps corresponding to match regs

Set low on match

Set high on match

Toggle on match

Do nothing on match

RL4.1.4 Embedded System Design © K.R.Anupama &

18

Meetha.V.shenoy

Output Compare Reset/Continue/Stop

on Match

CLK

32-bit

0005

0004

0003

0002

0000

0001

counter

OL0

OL1 PT

PTx

32-bit comparator CF Logic

Match

0005Reg

CI INT

Logic

RL4.1.4 Embedded System Design © K.R.Anupama &

Interrupt

Meetha.V.shenoy

19

Output Compare 0.0 P1.28 AltF3, P3.25 AltF2

Output Compare 0.1 P1.29 AltF3, P3.26 AltF2

Output Compare 1.0 P1.22 AltF3

Output Compare 1.1 P1.25 AltF3

Output Compare 2.0 P0.6 AltF3, P4.28 AltF2

Output Compare 2.1 P0.7 AltF3, P4.29 AltF2

Output Compare 2.2 P0.8 AltF3

Output Compare 2.3 P0.9 AltF3

Output Compare 3.0 P0.10 AltF3

Output Compare 3.1 P0.11 AltF

RL4.1.4 Embedded System Design © K.R.Anupama &

3

Meetha.V.shenoy

20

Program for Output Compare

Match Registers for Timer 0/1/2/3

TxMR0-TxMR3

TxMCR

MR2S MR2R MR2I MR1S MR1R MR1I MR0S MR0R MR0I

MR3S MR3R MR3I

RL4.1.4 Embedded System Design © K.R.Anupama &

21

Meetha.V.shenoy

Program for Output Compare

External Match Registers for Timer 0/1/2/3

TxEMCR

EMC1 EMC0 EM3 EM2 EM1 EMO

EMC3 EMC2

RL4.1.4 Embedded System Design © K.R.Anupama &

22

Meetha.V.shenoy

Program LPC 23xx to count the no. of

objects crossing a particular point within a

period of 1 second. Also find the time

interval between two objects.

RL4.1.4 Embedded System Design © K.R.Anupama &

23

Meetha.V.shenoy

You might also like

- 8051 Microcontroller: An Applications Based IntroductionFrom Everand8051 Microcontroller: An Applications Based IntroductionRating: 5 out of 5 stars5/5 (6)

- Timers and InterruptDocument38 pagesTimers and Interrupt21146387No ratings yet

- ARM Microcontrollers Programming for Embedded SystemsFrom EverandARM Microcontrollers Programming for Embedded SystemsRating: 5 out of 5 stars5/5 (1)

- 3 Channel IR Remote ControlDocument47 pages3 Channel IR Remote ControlMehmet GüçyetmezNo ratings yet

- Atmel 8-Bit AVR Microcontroller With 512/1024 Bytes In-System Programmable FlashDocument170 pagesAtmel 8-Bit AVR Microcontroller With 512/1024 Bytes In-System Programmable Flashlumix345-web1802No ratings yet

- RECON 0xa Hardware Assisted Rootkits ARM SpisakDocument81 pagesRECON 0xa Hardware Assisted Rootkits ARM Spisakjames wrightNo ratings yet

- 8-Bit Microcontroller With 2/4/8K Bytes In-System Programmable Flash Attiny25/V Attiny45/V Attiny85/V PreliminaryDocument16 pages8-Bit Microcontroller With 2/4/8K Bytes In-System Programmable Flash Attiny25/V Attiny45/V Attiny85/V PreliminaryLourencosud SudNo ratings yet

- Pe 194802B Philips Manual DatasheetDocument14 pagesPe 194802B Philips Manual DatasheetMárcio FernandesNo ratings yet

- Programmazione - AssemblerDocument36 pagesProgrammazione - AssemblerArthNo ratings yet

- An Introduction To PIC Microcontrollers: Unit 2: Microcontroller ArchitectureDocument40 pagesAn Introduction To PIC Microcontrollers: Unit 2: Microcontroller Architecturehimanshumal100% (2)

- Electrical Engineering Department ACADEMIC SESSION: - Dec40053 - Embedded System ApplicationsDocument13 pagesElectrical Engineering Department ACADEMIC SESSION: - Dec40053 - Embedded System ApplicationsKeerthigaNo ratings yet

- Introduction To LPC 23XXDocument9 pagesIntroduction To LPC 23XXPooja SNo ratings yet

- Microprocessors and Microcontrollers Lab: Title: ComponentsDocument8 pagesMicroprocessors and Microcontrollers Lab: Title: ComponentsGhulam E Muhammad UsmanNo ratings yet

- Imm Design PDFDocument76 pagesImm Design PDFsamsularief03No ratings yet

- Hardware Components - CPU: M1: Introduction To Embedded SystemsDocument13 pagesHardware Components - CPU: M1: Introduction To Embedded SystemsvithyaNo ratings yet

- ECE3620Unit 8Document98 pagesECE3620Unit 8ed85201No ratings yet

- Lesson: Embedded Systems I/O TimersDocument9 pagesLesson: Embedded Systems I/O TimersPuspala ManojkumarNo ratings yet

- Unit 2 - ARM7 Based MicrocontrollerDocument112 pagesUnit 2 - ARM7 Based Microcontrollermadhura sNo ratings yet

- Microprocessors and Microcontrollers Lab: Title: ComponentsDocument8 pagesMicroprocessors and Microcontrollers Lab: Title: ComponentsGhulam E Muhammad UsmanNo ratings yet

- Attiny 13 Datasheet PDFDocument169 pagesAttiny 13 Datasheet PDFTed SunNo ratings yet

- 1.1 Introduction To PIC Microcontroller: Embedded System DesignDocument33 pages1.1 Introduction To PIC Microcontroller: Embedded System DesignMinh HoangNo ratings yet

- General Description: P. 1 2003/5 Ver. 1.7Document14 pagesGeneral Description: P. 1 2003/5 Ver. 1.7yeni biriNo ratings yet

- Chapt7 1Document43 pagesChapt7 1Prasanna KumarNo ratings yet

- PIC1Document183 pagesPIC1Gokul GocoolNo ratings yet

- 054 07431 0 At89c51ed2Document131 pages054 07431 0 At89c51ed2Thirtha PrasadNo ratings yet

- 1 PIC Evaluation Board User ManualDocument22 pages1 PIC Evaluation Board User ManualKavin Sengodan100% (1)

- Flashflex Microcontroller Using The Programmable Counter Array (Pca)Document17 pagesFlashflex Microcontroller Using The Programmable Counter Array (Pca)Darshan ValaNo ratings yet

- Iub TX Configuration Recommendation - ATM RAN14 V1.1Document94 pagesIub TX Configuration Recommendation - ATM RAN14 V1.1BegumKarabatakNo ratings yet

- Microcontroller With 16/32/64K Bytes In-System Programmable FlashDocument23 pagesMicrocontroller With 16/32/64K Bytes In-System Programmable FlashTho HaNo ratings yet

- 4-Analog InputDocument21 pages4-Analog InputTam PhamNo ratings yet

- Tata 1Document20 pagesTata 1vamsidhar999No ratings yet

- PIC16F877 Timer Modules Tutorials - PIC Timer0 TutorialDocument4 pagesPIC16F877 Timer Modules Tutorials - PIC Timer0 Tutorialsaid larguetNo ratings yet

- ATtiny 24Document238 pagesATtiny 24cbkulatungeNo ratings yet

- DatasheetDocument29 pagesDatasheetProfesor RosokNo ratings yet

- Datasheet ATmega 2560 Engl (162-338) (001-055)Document55 pagesDatasheet ATmega 2560 Engl (162-338) (001-055)Виктор ПоздняковNo ratings yet

- Atmel 2586 AVR 8 Bit Microcontroller ATtiny25 ATtiny45 ATtiny85 DatasheetDocument234 pagesAtmel 2586 AVR 8 Bit Microcontroller ATtiny25 ATtiny45 ATtiny85 DatasheetcrocomodxNo ratings yet

- ARDUINO Processor - ATMEL Microntroller DatashetDocument420 pagesARDUINO Processor - ATMEL Microntroller DatashetMauricio Rezende de OliveiraNo ratings yet

- At 90 Can 128Document428 pagesAt 90 Can 128Mahmoud AlNo ratings yet

- Sistem Monitoring Volume Tangki Solar MenggunakanDocument9 pagesSistem Monitoring Volume Tangki Solar Menggunakanrifki wahyudiNo ratings yet

- ATtiny44A DatasheetDocument286 pagesATtiny44A DatasheetPaul CuevaNo ratings yet

- Institute of Technology: Ec8711-Embedded Laboratory ManualDocument87 pagesInstitute of Technology: Ec8711-Embedded Laboratory ManualKamal Cruz LeNo ratings yet

- Mezzah 2019Document10 pagesMezzah 2019alexanderfortis8628No ratings yet

- Programmable Flexpc LP/S Clock For Intel Based Systems: Features: Key FeaturesDocument21 pagesProgrammable Flexpc LP/S Clock For Intel Based Systems: Features: Key FeaturesMaikel Borges IglesiasNo ratings yet

- So Do Chan ICDocument305 pagesSo Do Chan ICManh NguyenvanNo ratings yet

- AT89C51Document137 pagesAT89C51naveenkumar1407No ratings yet

- Product Overview: Ks88-Series MicrocontrollersDocument32 pagesProduct Overview: Ks88-Series MicrocontrollersCesar JakobyNo ratings yet

- PIC MicrocontrollerDocument28 pagesPIC MicrocontrollerANITHA KALAKONDANo ratings yet

- EM78P153SDocument53 pagesEM78P153SWillNo ratings yet

- IntroductionDocument23 pagesIntroductionArryshah Dahmia100% (4)

- Unit IV PPTDocument73 pagesUnit IV PPTR R DeshmukhNo ratings yet

- MM Lab ManualDocument53 pagesMM Lab ManualDev SejvaniNo ratings yet

- Pic 14000Document153 pagesPic 14000MarkoStankovicNo ratings yet

- Atmega 644Document376 pagesAtmega 644binhminhmoiNo ratings yet

- Atmega 380Document420 pagesAtmega 380Prem Sharma100% (1)

- ESD Merged RL All 803pgDocument803 pagesESD Merged RL All 803pgRahamtulla MohammadNo ratings yet

- At Mega 48Document359 pagesAt Mega 48Gina WengNo ratings yet

- My Lecture15 DeviceDriversDocument37 pagesMy Lecture15 DeviceDriversPooja SNo ratings yet

- ClassTest Part5Document2 pagesClassTest Part5Pooja SNo ratings yet

- ClassTest Part3Document6 pagesClassTest Part3Pooja SNo ratings yet

- Class Test MergedDocument22 pagesClass Test Mergedsantosh vighneshwar hegdeNo ratings yet

- ClassTest Part1Document3 pagesClassTest Part1Pooja SNo ratings yet

- ClassTest Part6 1643292524057Document2 pagesClassTest Part6 1643292524057eadaladarenuNo ratings yet

- ClassTest Part4Document2 pagesClassTest Part4Pooja SNo ratings yet

- Introduction To LPC 23XXDocument9 pagesIntroduction To LPC 23XXPooja SNo ratings yet

- ClassTest Part2Document11 pagesClassTest Part2bondultimateNo ratings yet

- RL4 1 5Document4 pagesRL4 1 5Pooja SNo ratings yet

- RL4 1 3Document9 pagesRL4 1 3Pooja SNo ratings yet

- M4: Embedded Architectures-2: ARM Based LPC23xxDocument6 pagesM4: Embedded Architectures-2: ARM Based LPC23xxPooja SNo ratings yet

- The ARM Cores: M3: Embedded Architectures-1: RISC Architecture - ARMDocument12 pagesThe ARM Cores: M3: Embedded Architectures-1: RISC Architecture - ARMPooja SNo ratings yet

- ARM-Instruction Set - 2 & Pipelining: M3: Embedded Architectures - 1: RISC Architecture - ARMDocument12 pagesARM-Instruction Set - 2 & Pipelining: M3: Embedded Architectures - 1: RISC Architecture - ARMPooja SNo ratings yet

- ARM-Programmer's Model & Operating Modes: M3: Embedded Architectures - 1: RISC Architecture - ARMDocument9 pagesARM-Programmer's Model & Operating Modes: M3: Embedded Architectures - 1: RISC Architecture - ARMPooja SNo ratings yet

- Design Process & Soc: M1: Introduction To Embedded SystemsDocument8 pagesDesign Process & Soc: M1: Introduction To Embedded SystemsPooja SNo ratings yet

- ARM-Instruction Set - 1: M3: Embedded Architectures - 1: RISC Architecture - ARMDocument9 pagesARM-Instruction Set - 1: M3: Embedded Architectures - 1: RISC Architecture - ARMPooja SNo ratings yet

- Software Components - The Application & The OS: M1: Introduction To Embedded SystemsDocument12 pagesSoftware Components - The Application & The OS: M1: Introduction To Embedded SystemsPooja SNo ratings yet

- ARM-Exceptions: M3: Embedded Architectures - 1: RISC Architecture - ARMDocument10 pagesARM-Exceptions: M3: Embedded Architectures - 1: RISC Architecture - ARMPooja SNo ratings yet

- Huffman Coding Using MATLAB (PoojaS)Document20 pagesHuffman Coding Using MATLAB (PoojaS)Pooja S75% (4)

- Space Mouse (Pooja S)Document30 pagesSpace Mouse (Pooja S)Pooja S100% (1)

- Dyneema Vs SteelDocument5 pagesDyneema Vs SteelSaurabh KumarNo ratings yet

- Project: Study On Building Construction Using Foam ConcreteDocument5 pagesProject: Study On Building Construction Using Foam ConcreteAzhagesanNo ratings yet

- Chapter8 SwitchingDocument60 pagesChapter8 SwitchingSalah AL-HakimiNo ratings yet

- A Framework For Developing and Evaluating Utility Substation Cyber Security - Schneider ElectricDocument10 pagesA Framework For Developing and Evaluating Utility Substation Cyber Security - Schneider ElectricHugh cabNo ratings yet

- Hardware Catalog No Prices (PTHW0208.1C) PDFDocument11 pagesHardware Catalog No Prices (PTHW0208.1C) PDFAhmed TahaNo ratings yet

- DimensionsDocument103 pagesDimensionslaurariton100% (1)

- DIO 20. ZAŠTITA PRI RADU I SMJEŠTAJ POSADE Jan 2015Document44 pagesDIO 20. ZAŠTITA PRI RADU I SMJEŠTAJ POSADE Jan 2015Samo SpontanostNo ratings yet

- Consumer Studies GR 11 Revision Term 1 2023 FinalDocument20 pagesConsumer Studies GR 11 Revision Term 1 2023 FinalCerboh MazibukoNo ratings yet

- Journal of Experimental Biology and Agricultural Sciences: Anitha KC, Rajeshwari YB, Prasanna SB and Shilpa Shree JDocument5 pagesJournal of Experimental Biology and Agricultural Sciences: Anitha KC, Rajeshwari YB, Prasanna SB and Shilpa Shree Jkristel amadaNo ratings yet

- Gerus Air Driven Hydraulic PumpDocument7 pagesGerus Air Driven Hydraulic Pumpmahmoudayoub173No ratings yet

- Aircraft Performance NPTELDocument538 pagesAircraft Performance NPTELShabbir Ali100% (2)

- Hyundai D4FB Diesel Fuel System 2Document727 pagesHyundai D4FB Diesel Fuel System 2Alexey Koshelnik100% (1)

- Deepwater Horizon Oil SpillDocument26 pagesDeepwater Horizon Oil Spilleddy9881100% (2)

- Bioresource TechnologyDocument11 pagesBioresource TechnologyShaik HussainNo ratings yet

- Aiwa CX jn5 ETDocument78 pagesAiwa CX jn5 ETluzmarospiNo ratings yet

- Operator PanelDocument11 pagesOperator PanelMostafa AlakhliNo ratings yet

- Magic HRC Scarf 1: by Assia BrillDocument6 pagesMagic HRC Scarf 1: by Assia BrillEmily HouNo ratings yet

- Frequency Adverbs Worksheet - Basic 02 IntensiveDocument2 pagesFrequency Adverbs Worksheet - Basic 02 IntensiveMorelia AlfaroNo ratings yet

- Start Up Slug Catcher and Train 1Document43 pagesStart Up Slug Catcher and Train 1Larbi HammounNo ratings yet

- Engrave-O-Matic Custom Laser Engraving CatalogDocument32 pagesEngrave-O-Matic Custom Laser Engraving Catalogds8669No ratings yet

- Synthesis and Recrystallization of Dibenzalacetone: Experiment - 4Document2 pagesSynthesis and Recrystallization of Dibenzalacetone: Experiment - 4ARYAN CHAVANNo ratings yet

- MSDS Matrix Diluent-2 LISSDocument4 pagesMSDS Matrix Diluent-2 LISSLaboratorium RSI PekajanganNo ratings yet

- Weapon Type Code Range L M H Traits Category: Wong Rong Jing (Order #7811643)Document1 pageWeapon Type Code Range L M H Traits Category: Wong Rong Jing (Order #7811643)John SmithNo ratings yet

- Aircraft StructureDocument11 pagesAircraft StructureVagesh VagesNo ratings yet

- Ma2 - Acca - Chapter 1Document24 pagesMa2 - Acca - Chapter 1leducNo ratings yet

- Plant InvitroDocument219 pagesPlant InvitroMD Nassima100% (4)

- TNSTCDocument1 pageTNSTCMohamed MNo ratings yet

- 1822 B.E Cse Batchno 154Document53 pages1822 B.E Cse Batchno 154maniuyyala65No ratings yet

- UHF and 5 Gigahertz (60 MM) SHF ISM Radio BandsDocument3 pagesUHF and 5 Gigahertz (60 MM) SHF ISM Radio BandsAnandhu cNo ratings yet

- Dharma: Basis of Human LifeDocument4 pagesDharma: Basis of Human LifeEstudante da Vedanta100% (1)