0% found this document useful (0 votes)

60 views42 pages8085 Microprocessor Instruction Set Guide

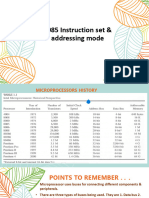

This document discusses the instruction set of the 8085 microprocessor. It describes the different types of instructions based on word size and function. It provides examples of data transfer, arithmetic, logic and other types of instructions. It explains the format and coding of instructions.

Uploaded by

Vishal GaurCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PPTX, PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

60 views42 pages8085 Microprocessor Instruction Set Guide

This document discusses the instruction set of the 8085 microprocessor. It describes the different types of instructions based on word size and function. It provides examples of data transfer, arithmetic, logic and other types of instructions. It explains the format and coding of instructions.

Uploaded by

Vishal GaurCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PPTX, PDF, TXT or read online on Scribd