Professional Documents

Culture Documents

Lab 02 Submitted To

Uploaded by

Bilal Ahmad0 ratings0% found this document useful (0 votes)

8 views5 pagesOriginal Title

Lab 02

Copyright

© Attribution Non-Commercial (BY-NC)

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

8 views5 pagesLab 02 Submitted To

Uploaded by

Bilal AhmadCopyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 5

Name: Reg no.

Section

Bilal Ahmad EE 307-165r A

Lab Submitted To :

02

SIR FAHAD ISLAM CHEEMA

DDl

Lab

1 bit full adder :

module onebitfulladder(s,cout,a,b,cin); input a,b,cin; output s,cout; assign {cout,sim}=a+b+cin; endmodule

Data Flow Modeling

4 bit full adder : Data Flow Modeling

Code: module fourbitfulladder(s,cout,a,b,cin); input[3:0] a,b; input cin; output[3:0]s; output cout; wire[2:0] c; onebitfulladder fa1(s[0],c[0],a[0],b[0],cin); onebitfulladder fa2(s[1],c[1],a[1],b[1],c[0]); onebitfulladder fa3(s[2],c[2],a[2],b[2],c[1]); onebitfulladder fa4(s[3],cout,a[3],b[3],cout); endmodule

2 into 4 bit decoder using an array: Data flow

Modeling

Code: module TwointoFourbitdecoderusinganarray(o,a); input[1:0]a; output[3:0]o; wire [1:0]w; not n1(w[0],a[0]); not n2(w[1],a[1]); and a1(o[0],a[0],a[1]); and a2(o[1],a[1],w[0]); and a3(o[2],w[1],a[0]); and a4(o[3],w[1],w[0]); endmodule

You might also like

- IEEE-754 Floating Point Multipler in VerilogDocument8 pagesIEEE-754 Floating Point Multipler in VerilogShyam Shankar55% (11)

- Full Adder Design Using Verilog HDL in Three Modeling StylesDocument8 pagesFull Adder Design Using Verilog HDL in Three Modeling Stylesvijayseshu100% (1)

- New Text DocumentDocument1 pageNew Text Documentnguyen hungNo ratings yet

- Eda LabrecordDocument71 pagesEda Labrecordteja roopNo ratings yet

- Lab 01 Submitted ToDocument4 pagesLab 01 Submitted ToBilal AhmadNo ratings yet

- Verilog Tutorial: 1-Bit Full AdderDocument8 pagesVerilog Tutorial: 1-Bit Full AdderLe HieuNo ratings yet

- Lab 3 DSDDocument8 pagesLab 3 DSDRohaidNo ratings yet

- Carry Save AdderDocument5 pagesCarry Save AdderMohan Babu ANo ratings yet

- Ver I Log ExamplesDocument22 pagesVer I Log ExamplesDayanand Gowda KrNo ratings yet

- Verilog 1 - Fundamentals: 6.375 Complex Digital Systems ArvindDocument36 pagesVerilog 1 - Fundamentals: 6.375 Complex Digital Systems ArvindVIJAYPUTRANo ratings yet

- Experiment No. 6Document5 pagesExperiment No. 6Hrishikesh UgleNo ratings yet

- Vlsi 1Document17 pagesVlsi 1Sudeep KrishnappaNo ratings yet

- Verilog Updated ProgramsDocument47 pagesVerilog Updated Programsanand_duraiswamy100% (1)

- Vlsi Lab ProgramsDocument14 pagesVlsi Lab ProgramsThirumalai TrendchaserNo ratings yet

- Lab Assignment 1:: Design IssuesDocument6 pagesLab Assignment 1:: Design IssuesAbdul Wasay JawaidNo ratings yet

- Verilog - Combinational CircuitDocument47 pagesVerilog - Combinational CircuitSharan ChaitanyaNo ratings yet

- Dataflow ModellingDocument30 pagesDataflow ModellingMayur NayakaNo ratings yet

- Exp 4 and 5Document5 pagesExp 4 and 5Mohan Babu ANo ratings yet

- Combinational Logic Design - Ripple Carry Adder, Carry Look Ahead AdderDocument25 pagesCombinational Logic Design - Ripple Carry Adder, Carry Look Ahead Adderdarlachantisaideepthi450No ratings yet

- Verilog Code For Fir FilterDocument58 pagesVerilog Code For Fir FilterKishore KumarNo ratings yet

- 4-Bit Array Multiplier (Unsigned)Document7 pages4-Bit Array Multiplier (Unsigned)rajap102No ratings yet

- Verilog Assignment1Document14 pagesVerilog Assignment1AlfiyaNo ratings yet

- Structural Level Modeling: - : Fulladd Fa3 (Sum (3), Carry - Out, A (3), x4, c3)Document6 pagesStructural Level Modeling: - : Fulladd Fa3 (Sum (3), Carry - Out, A (3), x4, c3)Satyam GovilaNo ratings yet

- Module 1 - Part 5 - Behavioural & DataflowDocument31 pagesModule 1 - Part 5 - Behavioural & DataflowJaspar Vinitha Sundari TNo ratings yet

- VLSI Lab Manual Exercise ProblemsDocument38 pagesVLSI Lab Manual Exercise ProblemsPrakhar Kumar100% (1)

- DIGITAL SYSTEM DESIGN Manual 2Document7 pagesDIGITAL SYSTEM DESIGN Manual 2Muhammad shehr yarNo ratings yet

- Fulladd 4 BitDocument1 pageFulladd 4 BitPorferioNo ratings yet

- Newcsa2 0Document2 pagesNewcsa2 0darshanNo ratings yet

- 2A AddersDocument22 pages2A AddersShalini KammalamNo ratings yet

- Internship Training Program Day18Document29 pagesInternship Training Program Day18Uma RamadassNo ratings yet

- Ec6612 Vlsi Design Lab - Exact Record DetailsDocument54 pagesEc6612 Vlsi Design Lab - Exact Record DetailsBharat RohanNo ratings yet

- F Pga Chan de AssignmentDocument38 pagesF Pga Chan de AssignmentSubbuNaiduNo ratings yet

- Lab1 2Document6 pagesLab1 2karnikrathva200No ratings yet

- 9.four Bit Multiplier: AIM:To Design and Simulate Four Bit Multiplier Using Modelsim. TOOL:Modelsim. Logic DiagramDocument4 pages9.four Bit Multiplier: AIM:To Design and Simulate Four Bit Multiplier Using Modelsim. TOOL:Modelsim. Logic DiagramJhansiJhanuNo ratings yet

- FALLSEM2023-24 MVLD503L TH VL2023240107475 2023-11-22 Reference-Material-IDocument23 pagesFALLSEM2023-24 MVLD503L TH VL2023240107475 2023-11-22 Reference-Material-IGunner 14No ratings yet

- ASIC Design Lab ReportsDocument16 pagesASIC Design Lab ReportsNisar Ahmed RanaNo ratings yet

- Error Tolerant AdderDocument21 pagesError Tolerant AdderGnrajesh RajeshNo ratings yet

- HW 1Document11 pagesHW 1vanloc12No ratings yet

- List of Experiments: Expt. No. Date Name of The Experiment Page No. RemarksDocument55 pagesList of Experiments: Expt. No. Date Name of The Experiment Page No. RemarksRakesh KumarNo ratings yet

- Verilog ReviewDocument78 pagesVerilog ReviewsubbuNo ratings yet

- Combinational - Circuits-Verilog CodesDocument6 pagesCombinational - Circuits-Verilog CodesTheVerseNo ratings yet

- HDL Model Combinational CircuitDocument24 pagesHDL Model Combinational CircuitsaidaraoNo ratings yet

- 22BCP367 DECO Assignment 5Document11 pages22BCP367 DECO Assignment 5Smit PatelNo ratings yet

- Verilog Tutorial: Chin-Lung SuDocument42 pagesVerilog Tutorial: Chin-Lung Suajay_kr931No ratings yet

- All VerilogLabsDocument74 pagesAll VerilogLabssamruthNo ratings yet

- Lab 1Document23 pagesLab 1Santosh KumarNo ratings yet

- HDL (Repaired)Document104 pagesHDL (Repaired)Vikas PakhretiaNo ratings yet

- Parallel Block-Oriented Matrix MultiplicationDocument5 pagesParallel Block-Oriented Matrix Multiplicationpreethy27No ratings yet

- Lab Results VlsiDocument18 pagesLab Results Vlsipankaj rangareeNo ratings yet

- Logic Design Lab Verilog 101Document49 pagesLogic Design Lab Verilog 101杜岳No ratings yet

- Verilog HDL Lab CodesDocument30 pagesVerilog HDL Lab CodesImrannkhanNo ratings yet

- Vlsi 1Document48 pagesVlsi 1Prasanna ECE 46No ratings yet

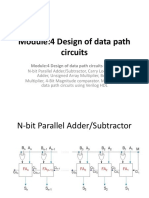

- Module:4 Design of Data Path Circuits 6 HoursDocument44 pagesModule:4 Design of Data Path Circuits 6 HoursSahana MecheriNo ratings yet

- Verilog HDL Lab CodesDocument30 pagesVerilog HDL Lab CodesImrannkhanNo ratings yet

- Aditya K MDocument10 pagesAditya K MADITYA MEENANo ratings yet

- Verilog Modules For Common Digital FunctionsDocument30 pagesVerilog Modules For Common Digital Functionselle868No ratings yet

- Untitled8 IpynbDocument2 pagesUntitled8 IpynbNitesh TiwariNo ratings yet

- 9709 w09 QP 11Document4 pages9709 w09 QP 11Bilal AhmadNo ratings yet

- Answer Any Six Parts From The Following. (2×13 26) I. II. Iii. IV. V. VI. Vii. Viii. IX. X. XI. Xii. XiiiDocument1 pageAnswer Any Six Parts From The Following. (2×13 26) I. II. Iii. IV. V. VI. Vii. Viii. IX. X. XI. Xii. XiiiBilal AhmadNo ratings yet

- Amir Raza Bsee 01083100 Section C Psa LabDocument5 pagesAmir Raza Bsee 01083100 Section C Psa LabBilal AhmadNo ratings yet

- Bilal Ahmad EE307165 Section C Lab AssignmentDocument5 pagesBilal Ahmad EE307165 Section C Lab AssignmentBilal AhmadNo ratings yet

- Name: Bilal Ahmad Reg No. EE 307-165 Name: Mubashar Azam Reg No. Ee 307-221 Section ADocument4 pagesName: Bilal Ahmad Reg No. EE 307-165 Name: Mubashar Azam Reg No. Ee 307-221 Section ABilal AhmadNo ratings yet