Professional Documents

Culture Documents

Response To Ideal Square Wave Signal: Capacitor

Response To Ideal Square Wave Signal: Capacitor

Uploaded by

Atul SotiOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Response To Ideal Square Wave Signal: Capacitor

Response To Ideal Square Wave Signal: Capacitor

Uploaded by

Atul SotiCopyright:

Available Formats

Response to ideal square wave signal

Capacitor:

Consider a simple RC circuit which all of us must have seen before. By simply applying Kirchoffs Law we can find out the relationship between applied voltage, current and voltage across capacitor ( Vc ) , Where Therefore,

dq (t ) q (t ) V (t ) + = dt RC R

dt To solve the above differential equation multiply both sides by e RC = et / RC . We get 1

V (t ) i (t ) R Vc (t ) = 0 q (t ) dq(t ) and i = Vc (t ) = C dt

q (t )et / RC =

1 V (t )et / RC dt R

For V (t ) = V0 with initial condition Vc (t = t0 ) = Vc 0 , we get

Vc (t ) = V0 1 e ( t t0 )/ RC + Vc 0 e (t t0 )/ RC

For V (t ) = mt with initial condition q (t = 0) = 0 , we have

q (t ) = CV (t ) ( mRC 2 ) (1 e t / RC )

Vc (t ) = V (t ) (mRC ) (1 e t / RC )

This is the response of capacitor for a linear wave. Now consider a pulse with very high value of m which rises to some finite value, say V0 , in very short interval t0 . Putting the series form of exponential, 1 1 Vc (t0 ) = V (t0 ) (mRC ) 1 1 t0 / RC + (t0 / RC ) 2 (t0 / RC )3 + ... 2! 3!

1 t0 1 t0 2 Vc (t0 ) = V0 + ... 2 3 2! ( RC ) 3! ( RC ) By taking the limit m tending to infinite and therefore t0 tending to zero one finds Vc (t0 ) = 0 .

Now consider an ideal square wave of 50% duty cycle with time period 2T. By ideal we mean that the time for switching from one voltage level to another is zero (infinite m).

As shown above, capacitor doesnt respond to such pulse of infinite m. Therefore we can think of square wave as a DC source with voltage

V V (t ) = 0 V0

For n = 0, 2, 4..

for nT < t (n + 1)T for (n + 1)T <t (n + 2)T

Vc [( n + 1)T ] = V0 (1 e T / RC ) + Vc [nT ]e T / RC Vc [(n + 2)T ] = V0 (1 e T / RC ) + Vc [(n + 1)T ]e T / RC

By combining above two equations we get,

Vc [(n + 2)T ] = V0 (1 e T / RC ) 2 + Vc [ nT ]e 2T / RC Putting n = n-2, n-4 ...2, 0 in equation (0) Vc [ nT ] = V0 (1 e T / RC ) 2 + Vc [( n 2)T ]e 2T / RC

T / RC 2 2T / RC

..0

.1

.2 Vc [(n 2)T ] = V0 (1 e ) + Vc [( n 4)T ]e ............... .. Vc [( n 2k + 2)T ] = V0 (1 e T / RC ) 2 + Vc [( n 2k )T ]e 2T / RC .k

Vc [2T ] = V0 (1 e T / RC ) 2 + Vc [0]e 2T / RC

n/2

Multiplying kth equation by e 2 kT / RC and adding

Vc [( n + 2)T ] = V0 (1 e T / RC ) 2 {1 + e 2T / RC + e 4T / RC + ... + e nT / RC } + Vc [0]e ( n + 2)T / RC

(1 eT / RC ) 2 Vc [(n + 2)T ] = V0 (1 e ( n + 2)T / RC ) + Vc [0]e ( n + 2)T / RC 2T / RC (1 e ) For the limit n

(1 e T / RC )2 (1 e2T / RC ) This is the steady-state peak voltage across capacitor. Now, Vc [] = V0 d Vc [] 2e T / RC (1 eT / RC ) 2 = dT V0 RC (1 e2T / RC ) 2 = +ve T > 0 Therefore Vc [] increases with T. Also,

Vc [] = V0 / 2 for T = RC ln 3

You might also like

- Tes P 119.25 R0Document18 pagesTes P 119.25 R0asifaliabid100% (1)

- Electrical and Information Engineering University of Sydney: ELEC3405/5738 Communications Electronics and PhotonicsDocument29 pagesElectrical and Information Engineering University of Sydney: ELEC3405/5738 Communications Electronics and PhotonicssakilakumaresanNo ratings yet

- Electronics - and - Telecommunications - Noise, F R CONNOR PDFDocument143 pagesElectronics - and - Telecommunications - Noise, F R CONNOR PDFAjay VarmaNo ratings yet

- Body of The Book - FinalDocument95 pagesBody of The Book - FinalCoup De GráceNo ratings yet

- 01 - SRV02 QUARC Integration - Instructor ManualDocument21 pages01 - SRV02 QUARC Integration - Instructor ManualFernando Her R0% (2)

- Hoja Caracteristicas 7476Document5 pagesHoja Caracteristicas 7476GroplyNo ratings yet

- RL RC CircuitDocument8 pagesRL RC CircuitDavex GwapoNo ratings yet

- 49 Processes 6Th EdDocument1 page49 Processes 6Th EdYeojan88No ratings yet

- Manual HidrigeneradoraDocument170 pagesManual HidrigeneradoraLividodj NirvanakcobainNo ratings yet

- 2-Dieu Che Tuong TuDocument136 pages2-Dieu Che Tuong TuAnhTưNo ratings yet

- Experimenting With The Picbasic Pro CompilerDocument188 pagesExperimenting With The Picbasic Pro Compilerjfg8721100% (2)

- Lab Assignment 8: 1 Sequential Circuit DesignDocument2 pagesLab Assignment 8: 1 Sequential Circuit DesignRehan bhattiNo ratings yet

- Cs Imp QuestDocument3 pagesCs Imp QuestLordwin MichealNo ratings yet

- Lecture 5 - Biopotential MeasurementsDocument59 pagesLecture 5 - Biopotential Measurementsapi-27535945100% (2)

- VHDL Codes For Various Combinational CircuitsDocument6 pagesVHDL Codes For Various Combinational CircuitsKaranNo ratings yet

- SolutionsDocument9 pagesSolutionsdavid_benavidez_3No ratings yet

- 12 Bit Spi Adc: Adc Pin Spartan3E FPGA LinesDocument6 pages12 Bit Spi Adc: Adc Pin Spartan3E FPGA LineskaankandemirrrNo ratings yet

- Basic Circuit of Op-Amp: KNJ2463 Mohd Syahmi JamaludinDocument18 pagesBasic Circuit of Op-Amp: KNJ2463 Mohd Syahmi JamaludinPetrus Petz WtzNo ratings yet

- Examen Corto 1Document4 pagesExamen Corto 1David GarciaNo ratings yet

- Chapter 6 Digital Transmission PDFDocument45 pagesChapter 6 Digital Transmission PDFmaharaniayulestari100% (1)

- Cuaderno InstrumentacionDocument25 pagesCuaderno InstrumentacionDavid GarciaNo ratings yet

- Schematic Capture - D - Recent Project in Desktop - Embedded Project - Coin Box - Coinbox - PDSPRJ PDFDocument1 pageSchematic Capture - D - Recent Project in Desktop - Embedded Project - Coin Box - Coinbox - PDSPRJ PDFsathish100% (2)

- PH METER WITH PIC PDFDocument1 pagePH METER WITH PIC PDFk_n_sreekumar100% (2)

- Circuits in MatlabDocument38 pagesCircuits in MatlabRana UsmanNo ratings yet

- N5625Document286 pagesN5625Feliscio Ascione FelicioNo ratings yet

- VHDL Code For Clock Divider (Frequency Divider)Document17 pagesVHDL Code For Clock Divider (Frequency Divider)Ashok kumarNo ratings yet

- Op Amp NotesDocument34 pagesOp Amp NotesUma ShankarNo ratings yet

- Mux DeMuxDocument8 pagesMux DeMuxTalha KhanNo ratings yet

- Diseño de Letras, Numero y Simbolos para Matriz 8x8Document2 pagesDiseño de Letras, Numero y Simbolos para Matriz 8x8Jose Luis Yarleque Rivera100% (1)

- mq2 - Pic16f877aDocument1 pagemq2 - Pic16f877aJose Luis Yarleque Rivera100% (2)

- Dynamic Logic CircuitsDocument38 pagesDynamic Logic Circuitssreekanthreddy peramNo ratings yet

- Ecl 203 MCQDocument3 pagesEcl 203 MCQresham k vNo ratings yet

- TTL Ic 7448Document3 pagesTTL Ic 7448haseeb ahmad ch.0% (1)

- VLSI & Embedded Systems Lab ManualDocument137 pagesVLSI & Embedded Systems Lab Manualganga avinash reddyNo ratings yet

- Quanser Coupled Tanks Modeling and Parameter PDFDocument7 pagesQuanser Coupled Tanks Modeling and Parameter PDFAnonymous rTRz30fNo ratings yet

- LCD 4 BitsDocument5 pagesLCD 4 BitsLuckens St Fleur100% (1)

- IRM 01 Kinematics Dynamics PDFDocument109 pagesIRM 01 Kinematics Dynamics PDFSexy macho Bon bonNo ratings yet

- Solution QuizDocument3 pagesSolution Quizdjun033No ratings yet

- Signals & Systems - Chapter 4: T U e eDocument14 pagesSignals & Systems - Chapter 4: T U e eAlgerian AissaouiNo ratings yet

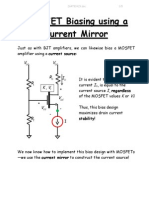

- MOSFET Biasing Using A Current MirrorDocument5 pagesMOSFET Biasing Using A Current MirrorshastryNo ratings yet

- 3.1 Analog MultipliersDocument17 pages3.1 Analog MultipliersMarykutty CyriacNo ratings yet

- Control Manual LCD VHDLDocument1 pageControl Manual LCD VHDLDanNo ratings yet

- Datasheet 74hc45Document10 pagesDatasheet 74hc45aleallenderNo ratings yet

- Experiment No.3 Carry Lookahead Adders: Computer EngineeringDocument7 pagesExperiment No.3 Carry Lookahead Adders: Computer EngineeringIn Fee Knee TeaNo ratings yet

- PCM ProjectDocument7 pagesPCM Projectsuresh NamgiriNo ratings yet

- Power Electronics Tutorial ExercisesDocument656 pagesPower Electronics Tutorial Exercisesqfcjagu865No ratings yet

- Opa An AssDocument8 pagesOpa An Assgvkreddyg100% (1)

- Generating PWM With PIC Microcontroller - MikroC ProDocument3 pagesGenerating PWM With PIC Microcontroller - MikroC Proemilfrancu100% (1)

- Programming DsPIC in CDocument86 pagesProgramming DsPIC in CHassaan Shah100% (1)

- Escuela Superior Politécnica De Chimborazo: D= P P U sin (θ) dθ d ∅ PDocument7 pagesEscuela Superior Politécnica De Chimborazo: D= P P U sin (θ) dθ d ∅ PJorge SaNo ratings yet

- RC Differentiator & IntegratorDocument6 pagesRC Differentiator & IntegratorMatt Imri100% (1)

- Lab1 VHDLDocument9 pagesLab1 VHDLGautam GowdaNo ratings yet

- DSP Practical FileDocument18 pagesDSP Practical FileDivyaNo ratings yet

- 40 Ei 4p2-Lic Lab ManualDocument94 pages40 Ei 4p2-Lic Lab ManualsoundsisterNo ratings yet

- ES-1 Natural and Forced ResponseDocument39 pagesES-1 Natural and Forced ResponseGanesh DharmireddyNo ratings yet

- Electrical Circuit Analysis-1Document34 pagesElectrical Circuit Analysis-1sriyalakshmi005No ratings yet

- Electrical Circuit AnalysisDocument41 pagesElectrical Circuit Analysissriyalakshmi005No ratings yet

- Ac CircuitDocument22 pagesAc CircuitfreeziyNo ratings yet

- Transients DerivationsDocument18 pagesTransients DerivationsWendell NiveraNo ratings yet

- R-L-C AC Circuits: P PP RMS RMS PP RMSDocument10 pagesR-L-C AC Circuits: P PP RMS RMS PP RMShiren_powerNo ratings yet

- 07NANO107 Transient Analysis of RC-RL CircuitsDocument20 pages07NANO107 Transient Analysis of RC-RL CircuitsJames Hyun Wook ParkNo ratings yet

- Special Topics in Power - 1Document38 pagesSpecial Topics in Power - 1sumayamsNo ratings yet

- RC Circuit Response Introduction & TheoryDocument6 pagesRC Circuit Response Introduction & TheoryMuhammad FarooqNo ratings yet

- Feynman Lectures Simplified 2C: Electromagnetism: in Relativity & in Dense MatterFrom EverandFeynman Lectures Simplified 2C: Electromagnetism: in Relativity & in Dense MatterNo ratings yet

- Design of Monorail BeamDocument6 pagesDesign of Monorail BeamMahata Priyabrata100% (2)

- 0908-0101 I2 200910 PDFDocument28 pages0908-0101 I2 200910 PDFAnonymous z0m7zUPir100% (1)

- Rework Production OrderDocument24 pagesRework Production Orderbalu4indiansNo ratings yet

- Integrisana Kola: Sn74Xx SelekcijaDocument10 pagesIntegrisana Kola: Sn74Xx SelekcijaСрећко Минић100% (1)

- Code of Practice BS 7072 1989Document16 pagesCode of Practice BS 7072 1989Adel Jeddi100% (1)

- Technical Data Index: DescriptionDocument16 pagesTechnical Data Index: DescriptionReza PahleviNo ratings yet

- Non Slip Surface Australian StandardsDocument6 pagesNon Slip Surface Australian StandardsDevy Refina IndrianiNo ratings yet

- Solderer Performance Qualification (SPQ) - Sample Form: Qualification, AWS B2.3/B2.3MDocument1 pageSolderer Performance Qualification (SPQ) - Sample Form: Qualification, AWS B2.3/B2.3MBernardo LeorNo ratings yet

- Free Hand Sketching - Free Hand Drawing Lecture NotesDocument14 pagesFree Hand Sketching - Free Hand Drawing Lecture NotesMollaNo ratings yet

- Machine Tool Design 1Document57 pagesMachine Tool Design 1rrhoshackNo ratings yet

- TDS Acronal 7079 PDFDocument3 pagesTDS Acronal 7079 PDFWahid Karol100% (1)

- Me 605CDocument4 pagesMe 605CmkbNo ratings yet

- Solved Exercise MassDocument3 pagesSolved Exercise MassMalak HindiNo ratings yet

- 2.lab Techniques (Repaired) PDFDocument52 pages2.lab Techniques (Repaired) PDFSomu Yashawant ChaudhariNo ratings yet

- Estimate of Bajaj NagarDocument18 pagesEstimate of Bajaj NagarRohit BawaNo ratings yet

- Parapet CapacityDocument4 pagesParapet CapacityJemicah YumenaNo ratings yet

- Tutorial Install Zimbra WebMail Admin Server EnglishDocument274 pagesTutorial Install Zimbra WebMail Admin Server Englishnanangspeed100% (2)

- Manual MedlabqcDocument29 pagesManual MedlabqcKarito Plaza MNo ratings yet

- DHOLAVIRADocument5 pagesDHOLAVIRAuday aggarwalNo ratings yet

- Nvidia insideBigData Guide To Deep Learning and AI PDFDocument9 pagesNvidia insideBigData Guide To Deep Learning and AI PDFfolioxNo ratings yet

- Omega T TutorialDocument3 pagesOmega T TutorialErick TrilloNo ratings yet

- UsbFix ReportDocument37 pagesUsbFix ReportMohammad YazidNo ratings yet

- Service VRVIV Non Continuous Heating Service Manual ESiE 1301Document208 pagesService VRVIV Non Continuous Heating Service Manual ESiE 1301Doan Tien DoNo ratings yet

- 10867-0 Neoss Anatomical Healing Abutment Manual Hi Res 2009-05-19Document4 pages10867-0 Neoss Anatomical Healing Abutment Manual Hi Res 2009-05-19Nate TaylorNo ratings yet

- Engineering M12 Solutions Chapter 03 MSEDocument5 pagesEngineering M12 Solutions Chapter 03 MSEmelbaz1No ratings yet

- Numbers Sheet Name Numbers Table NameDocument15 pagesNumbers Sheet Name Numbers Table NameAcua RioNo ratings yet