Professional Documents

Culture Documents

Microsoft PowerPoint - ECE 334-Lecture 21nMOS - Currentand Transmission Gates

Uploaded by

Fatmir KelmendiOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Microsoft PowerPoint - ECE 334-Lecture 21nMOS - Currentand Transmission Gates

Uploaded by

Fatmir KelmendiCopyright:

Available Formats

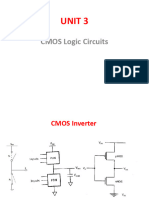

CMOS Transmission Gate

A CMOS transmission gate can be constructed by parallel combination of NMOS and PMOS transistors, with complementary gate signals. The main advantage of the CMOS transmission gate compared to NMOS transmission gate is to allow the input signal to be transmitted to the output without the threshold voltage attenuation.

CMOS transmission gate

Characteristics of a CMOS Transmission gate

Charging path

If =VDD,

Case I:

= 0 , VI=VDD, and VO is initially zero.

Drain

source

In NMOS transistor, under above Condition, terminal a acts as the drain and terminal b acts as the source. For the PMOS, device terminal c acts as the drain and terminal d acts as the source. In order to charge the load capacitor, current enters the NMOS drain and the PMOS source. The NMOS gate to source voltage is,

source

Drain

VGSN=-VO=VDD-VO this implies that VGSN continuously change.

And for PMOS source-to-gate voltage is

VGSP = VI - = VDD 0 = VDD This implies that VGSP remains constant.

Characteristics of a CMOS Transmission gate (Cont.)

When VO=VDD-VTN, VGSN=VTN,

source

Characteristics of a CMOS Transmission gate (Cont.)

Case II: If VI = 0, = VDD,

the NMOS transmission gate cuts off and IDN=0. However, PMOS transistor continue to conduct, because VGSP of the PMOS is a constant (VGSP=VDD). In PMOS transistor

=0

VO=VDD

initially.

discharging path

Drain

terminal a acts as a source and terminal b acts as a drain. For the PMOS transistor terminal c acts as a source and terminal d acts as a drain. In order to discharge the capacitors current enter the NMOS drain and PMOS source. The NMOS gate to source voltage is,

source

drain

IDP=0, when VSDP=0, which would be possible only, if,

source

Drain

VO = VI = 5V This implies that a logic 1 is transmitted unattenuated through the CMOS transmission gate in contrast to the NMOS transmission gate.

vGSN = vI = vDD 0 = VDD

drain

source

And PMOS source to gate voltage is

vSGP = vO = vO 0 = vO

When VSGP=VO=|VTP|, PMOS transistor cutoff and iDP=o However, since VGSN=VDD, the NMOS transistor continue conducting and capacitor completely discharge to zero. Finally, VO=0, which is a good logic 0.

G NMOS transmission gate

CMOS transmission gate remains in a dynamic condition.

If VO=VDD and =0, then NMOS substrate to terminal b pn junction is reverse biased and capacitor CL can discharge. If VO=0, then the PMOS terminal c-to-substrate pn junction is reverse biased and capacitance CL can be charge to a positive voltage. This implies that the output high

Exercise 16.29 (a)

Given that VTN=0.8V, VTP= 1.2V. When = 5V, input VI varies with time as VI=0.5tV for 0 t 10s. Let VO=0 and CL=1pF. Determine the range of the times that the NMOS and PMOS devices are conducting or cutoff. Sol: NMOS conducting for 0 VI 4.2V NMOS conducting 0 t 8.4s NMOS cutoff : 8.4 t 10s

or low of CMOS transmission gate circuit do not remain constant with time (dynamic

behavior).

Sequential Logic circuits

The logic circuits considered thus far are called combinational logic circuits. Their output depend only on the present value of input. This implies that these circuit do not have memory. Another class of the logic circuit that incorporate memory are called sequential logic circuits; that is, their output depend not only the present value of the input, but also on the previous history of inputs. Shift registers and flip-flops are typical examples of such circuits.

nMOS Dynamic Shift Registers

A shift register can be constructed by the combination of transmission gates and inverters. If VI=VDD and 1=VDD, then a logic 1=VDD-VTN would exist at VO1. The CL charges through MN1. As VO1 goes high, VO2 goes low. If 2 is high low will transmitted through MN2 and VO4 would be at logic 1. Thus logic 1 shifted from input to output.

In shift register the input signal is transmitted, or shifted, from the input to the output during one clock cycle.

Dynamic Shift Registers at various times

Suppose VDD=5V and VTN=1V. At t=t1 , V1=1=5V, vO2 goes low At this time MN2 is still in cutoff (2=0) even though input of MN2 has been changed. This implies that vO3 and vO4 depend on the previous history. Similarly at t=t3, 2 is high, and logic 0 at vO2 is transmitted to vO3, which force vO4 to 5V. Thus the input information is transmitted to output during one clock cycle.

Dynamic Shift Registers at Various Times (cont.)

Consider when t=t4, vI=0, and 1=5V, so VO1=0 and VO2=5V.Vo3 and Vo4 depend on previous history At t=t5, 2=5V, vO3 charges to VDDVTN=4V and VO4 goes low. Thus logic 0 is shifted (transmitted) from input to output.

Transparent mode Hold mode

Also note that vO3 and vO4 are depend on previous history of their inputs instead of current inputs (they are having memory).

NMOS shift register is also dynamic (why?)

The output charged capacitor does not remain constant with time because it is discharge through the transmission gate transistor. In order to prevent logic errors, the clock signal period T must be small compared to effective RC discharge time constant.

CMOS Dynamic Shift Registers

The operation of the CMOS shift register is similar to the NMOS register except for the voltage levels. For example, when vI=1=VDD. Then vO1=VDD and vO2=0. when 2 goes high, then vo3 switch to zero, vo4=vDD. Thus input signal is shifted to the output during one clock cycle.

For example at t = t2, VO1=4V, 1=0 and MN1 is cutoff.VO1 will start to to decay and VO2 will begin to increase.

NMOS R-S Flip Flop

Flip- flops are bistable circuits usually formed by cross-coupling two NOR gates. The output of the two NOR circuits are connected back to the inputs of the opposite NOR gates.

NMOS R-S Flip Flop (cont.)

When R=logic 1 and S=logic 0 Then M4 turn on so output goes low. With S=Q=Logic 0, both M1 and M2 are cutoff and goes high. The flip-flop is now in reset state. If both S and R inputs go high. Then both outputs Q and Q would go low, which implies that output is not complementary. This condition is forbidden or nonallowed condition.

When S=logic 1 and R=logic 0 Q =logic 0 and Q=logic 1=VDD Transistor M2 is then also biased in conducting state.

If S returns to logic 0, nothing in the

circuit can force a change and flip flop stores the previous logic states, although M1 turned off (but M2 remains tuned on).

CMOS R-S Flip-Flop

The operation sequence of CMOS R-S flip flop is same as NMOS. For example: If S = logic 1 and R = logic 0, then MN1, is turned on, Mp1, is cut off, and Q goes low. With Q = R = logic 0, then both MN3 and MN4 are cut off, both MP3 and Mp4 are biased in a conducting state so that the output Q goes high. With Q = logic 1, MN2 is biased on, Mp2 is biased off, and the flip-flop is in a set condition. When S goes low, MN1, turns off, but MN2 remains conducting, so the state of the flip-flop does not change.

CMOS R-S Flip-Flop (cont.)

When S = logic 0 and R = logic 1, then output Q is forced low, outputQ goes high, and the flip-flop is in a reset condition. Again, a logic 1 at both S and R is considered to be a forbidden or a nonallowed condition, since the resulting outputs are not complementary.

Static vs Dynamic Storage

Static storage preserve state as long as the power is on have positive feedback (regeneration) with an internal connection between the output and the input useful when updates are infrequent (clock gating) Dynamic storage store state on parasitic capacitors only hold state for short periods of time (milliseconds) require periodic refresh usually simpler, so higher speed and lower power

Static D-type Flip-Flop

A D-type flip-flop is used to provide a delay. The logic bit on the D input is transferred to the output at the next clock pulse.

When the CMOS transmission gate turn off (=0), the pn junction in the MN1 transmission gate transistor is reverse biased.

You might also like

- Chap16 2 CMOS Inverter ModifiedDocument14 pagesChap16 2 CMOS Inverter ModifiedSai Kiran OrugantiNo ratings yet

- Unit 3Document59 pagesUnit 3bhupendra1977No ratings yet

- Lecture 9 - CMOS Delay IDocument28 pagesLecture 9 - CMOS Delay IWambi DanielcollinsNo ratings yet

- Arjun PL Vlsi2Document73 pagesArjun PL Vlsi2Tony StarkNo ratings yet

- UNIT 3 & 4Document63 pagesUNIT 3 & 4Indrajeet GautamNo ratings yet

- Chapter 1 Combinational CMOS Logic Circuits Lecture # 4 Pass Transistors andDocument34 pagesChapter 1 Combinational CMOS Logic Circuits Lecture # 4 Pass Transistors andJacques HaNo ratings yet

- UNIT 3Document24 pagesUNIT 3Indrajeet GautamNo ratings yet

- CMOS Logic Circuits: Inverter 2 Input NOR 2 Input NAND Other FunctionsDocument23 pagesCMOS Logic Circuits: Inverter 2 Input NOR 2 Input NAND Other FunctionsKumar Amit VermaNo ratings yet

- Combination Logic CircuitsDocument21 pagesCombination Logic Circuitsamitssaksena100% (1)

- Electronics - Basic CMOS Digital Circuits: Prof. M Arta Rencz, Gergely NagyDocument30 pagesElectronics - Basic CMOS Digital Circuits: Prof. M Arta Rencz, Gergely NagyMuhammad NasirNo ratings yet

- Advance CMOS LogicDocument31 pagesAdvance CMOS LogicRaja VidyaNo ratings yet

- Unit 3Document18 pagesUnit 3sparsh kaudinyaNo ratings yet

- Unit 5Document6 pagesUnit 5Tarun SinghalNo ratings yet

- Combinational Mos Logic Circuits: Basic ConceptsDocument41 pagesCombinational Mos Logic Circuits: Basic Conceptsflampard24No ratings yet

- Chapter STA For Nanometer DesignsDocument33 pagesChapter STA For Nanometer Designsfahad ghazali1No ratings yet

- Introduction to CMOS technology and logic gate fundamentalsDocument39 pagesIntroduction to CMOS technology and logic gate fundamentalsvenkateshNo ratings yet

- Dynamic Logic Circuits: Kang and Leblebicic, Chapter 9Document34 pagesDynamic Logic Circuits: Kang and Leblebicic, Chapter 9Lovey SalujaNo ratings yet

- Dynamic CMOS DesignDocument30 pagesDynamic CMOS DesignAllwyn Anand SNo ratings yet

- Ακολουθιακά Κυκλώματα MosDocument31 pagesΑκολουθιακά Κυκλώματα MosmallikaNo ratings yet

- Design and Performance Analysis of The Cmos InverterDocument14 pagesDesign and Performance Analysis of The Cmos InverterssNo ratings yet

- Lec 11 Sequential Logic CircuitsDocument49 pagesLec 11 Sequential Logic CircuitsDeependra NigamNo ratings yet

- MOSFET Digital Circuits and NMOS Logic GatesDocument50 pagesMOSFET Digital Circuits and NMOS Logic Gatesvlsijp100% (1)

- Dynamic Logic Circuits: A. MarzukiDocument25 pagesDynamic Logic Circuits: A. Marzukisreekanthreddy peramNo ratings yet

- U 3Document13 pagesU 3Maheshwar Reddy100% (1)

- Curs5 Engl PDFDocument16 pagesCurs5 Engl PDFVinodChauhanNo ratings yet

- Digital Integrated CircuitsDocument10 pagesDigital Integrated CircuitsshahanisubhashNo ratings yet

- Philip-Power Dissipation in CMOS CircuitDocument20 pagesPhilip-Power Dissipation in CMOS CircuitPhilip AustinNo ratings yet

- VLSI Design Lecture NotesDocument117 pagesVLSI Design Lecture NotesRaji SharmiNo ratings yet

- WINSEM2020-21 ECE1002 ETH VL2020210506889 Reference Material I 25-Jun-2021 MOSFET-circuits-ApplicationsDocument19 pagesWINSEM2020-21 ECE1002 ETH VL2020210506889 Reference Material I 25-Jun-2021 MOSFET-circuits-Applicationsrisith royNo ratings yet

- Introduction To CMOS: Complementary Metal-Oxide SemiconductorDocument19 pagesIntroduction To CMOS: Complementary Metal-Oxide SemiconductorHarikeshHarryNo ratings yet

- ECT 304: VLSI Circuit Design - Dynamic and Domino LogicDocument87 pagesECT 304: VLSI Circuit Design - Dynamic and Domino LogicTony StarkNo ratings yet

- Transmission Gate Based CircuitsDocument43 pagesTransmission Gate Based CircuitsParul TrivediNo ratings yet

- Vsli Unit 2 Question Bank With AnswersDocument10 pagesVsli Unit 2 Question Bank With AnswersPavani NNo ratings yet

- How CMOS Circuits Implement LogicDocument20 pagesHow CMOS Circuits Implement Logicaleph13experienceNo ratings yet

- Unit 2 - CMOS Logic, Fabrication and LayoutDocument34 pagesUnit 2 - CMOS Logic, Fabrication and LayoutphillipNo ratings yet

- Advanced Techniques in CMOS Logic Circuits: Introduction To VLSI Circuits and SystemsDocument45 pagesAdvanced Techniques in CMOS Logic Circuits: Introduction To VLSI Circuits and SystemsraviNo ratings yet

- Revisit: Resistance and Capacitance MOSFET Model For Digital CircuitsDocument33 pagesRevisit: Resistance and Capacitance MOSFET Model For Digital Circuitsdilshan singhNo ratings yet

- Mosfet Using Tanner ToolDocument20 pagesMosfet Using Tanner ToolParmeet SinghNo ratings yet

- Lecture 3 - MOS and ECL TechnologyDocument27 pagesLecture 3 - MOS and ECL TechnologyGhostNo ratings yet

- Max Clock Frequency D-FF Circuit Buffer Design Latchup Prevention State Machines 2's Complimenter/TITLEDocument27 pagesMax Clock Frequency D-FF Circuit Buffer Design Latchup Prevention State Machines 2's Complimenter/TITLERui ChenNo ratings yet

- Vlsi Design Basics - OdpDocument26 pagesVlsi Design Basics - OdpganapathiNo ratings yet

- Electrical Properties of MOS CircuitDocument13 pagesElectrical Properties of MOS CircuitPuneetNo ratings yet

- ECE 334: CMOS Digital Circuits Lecture on CMOS Technology and Logic GatesDocument28 pagesECE 334: CMOS Digital Circuits Lecture on CMOS Technology and Logic GatesAhmedTarekNo ratings yet

- Topic 5 - Cmos InverterDocument34 pagesTopic 5 - Cmos InverterjebonNo ratings yet

- Unit-Ii Cmos CircuitsDocument34 pagesUnit-Ii Cmos CircuitsgnitsiceNo ratings yet

- Introduction to CMOS logic and gate designDocument45 pagesIntroduction to CMOS logic and gate designNishanth Nish0% (1)

- C3.0 Operational Amplifiers II: Jeng-Han TsaiDocument12 pagesC3.0 Operational Amplifiers II: Jeng-Han Tsailinux14No ratings yet

- TN 423: Vlsi Circuits: Lecture 7aDocument24 pagesTN 423: Vlsi Circuits: Lecture 7aBernard Mkumbwa Jr.No ratings yet

- Unit 1 Q ADocument31 pagesUnit 1 Q AADEPOJU AyobamiNo ratings yet

- CMOS INVERTER-WPS OfficeDocument15 pagesCMOS INVERTER-WPS OfficekusumaNo ratings yet

- CMOS Logic: Sudhanshu Janwadkar, Teaching Assistant, SVNIT, Surat Lecture Notes 16-17 February 2017Document33 pagesCMOS Logic: Sudhanshu Janwadkar, Teaching Assistant, SVNIT, Surat Lecture Notes 16-17 February 2017baditakaliNo ratings yet

- Logic Gate Delay and Transition Time AnalysisDocument24 pagesLogic Gate Delay and Transition Time AnalysisKarthick NpNo ratings yet

- Lecture 1. CMOS Logic: Dr. Zhaohui WangDocument39 pagesLecture 1. CMOS Logic: Dr. Zhaohui WangRajendraNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- How To Clear A Green PoolDocument12 pagesHow To Clear A Green PoolFatmir KelmendiNo ratings yet

- Freshwater Fish FarmingDocument79 pagesFreshwater Fish FarmingMasthankhan PatanNo ratings yet

- Brochure Fish For FarmingDocument2 pagesBrochure Fish For FarmingFatmir KelmendiNo ratings yet

- PracticalAquaponicsForEveryone3, Muy InteresanteDocument12 pagesPracticalAquaponicsForEveryone3, Muy InteresanteCarlos Perez GarciaNo ratings yet

- Pond ConstructionDocument96 pagesPond Constructionmike_pilar100% (3)

- Build small dams safelyDocument4 pagesBuild small dams safelyMetuq Tudela QuispeNo ratings yet

- How To Clear A Green PoolDocument12 pagesHow To Clear A Green PoolFatmir KelmendiNo ratings yet

- Stick FloatsDocument3 pagesStick FloatspikemanserbiaNo ratings yet

- How To Produce Mirror Carp FryDocument1 pageHow To Produce Mirror Carp FryFatmir KelmendiNo ratings yet

- Stick FloatsDocument3 pagesStick FloatspikemanserbiaNo ratings yet

- How To Clear A Green PoolDocument12 pagesHow To Clear A Green PoolFatmir KelmendiNo ratings yet

- Stick FloatsDocument3 pagesStick FloatspikemanserbiaNo ratings yet

- Extra Prob PeriodicityDocument11 pagesExtra Prob PeriodicityFatmir KelmendiNo ratings yet

- How To Clear A Green PoolDocument12 pagesHow To Clear A Green PoolFatmir KelmendiNo ratings yet

- What Is A Computer Network?Document9 pagesWhat Is A Computer Network?Fatmir KelmendiNo ratings yet

- Assignment PracticalDocument2 pagesAssignment PracticalFatmir KelmendiNo ratings yet

- The Concept of System': - Discrete-Time SystemsDocument19 pagesThe Concept of System': - Discrete-Time SystemsFatmir KelmendiNo ratings yet

- Take Me FishingDocument52 pagesTake Me FishingAnonymous AlhzFE9EVNNo ratings yet

- Dsphw3 SolDocument7 pagesDsphw3 SolFatmir KelmendiNo ratings yet

- Reference Solution of DSP Test 2Document14 pagesReference Solution of DSP Test 2Khuram ShahzadNo ratings yet

- Extra ProblemsDocument15 pagesExtra ProblemsFatmir KelmendiNo ratings yet

- Homework 2Document4 pagesHomework 2Fatmir KelmendiNo ratings yet

- Extra ProblemsDocument15 pagesExtra ProblemsFatmir KelmendiNo ratings yet

- In Summary ContinuousDocument55 pagesIn Summary ContinuousFatmir KelmendiNo ratings yet

- Homework 2Document4 pagesHomework 2Fatmir KelmendiNo ratings yet

- Reference Solution of DSP Test 2Document14 pagesReference Solution of DSP Test 2Khuram ShahzadNo ratings yet

- Z-Transform: e N X e XDocument61 pagesZ-Transform: e N X e XFatmir KelmendiNo ratings yet

- Dsphw3 SolDocument7 pagesDsphw3 SolFatmir KelmendiNo ratings yet

- Dsphw3 SolDocument7 pagesDsphw3 SolFatmir KelmendiNo ratings yet

- X (N) Cos (H (N) 2Document2 pagesX (N) Cos (H (N) 2Fatmir KelmendiNo ratings yet