Professional Documents

Culture Documents

Fundamental of MIcroelectronics Bahzad Razavi Chapter 8 Solution Manual

Uploaded by

mkmkmkmk2Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Fundamental of MIcroelectronics Bahzad Razavi Chapter 8 Solution Manual

Uploaded by

mkmkmkmk2Copyright:

Available Formats

8.

1

5 4 3 2 1 0 1 2 3 4 5

V

in

(mV)

2

1

0

1

2

V

o

u

t

(

V

)

8.11

V

= V

+

= V

in

V

=

R

4

(R

2

+R

3

)

R

1

+R

4

(R

2

+R

3

)

R

2

R

2

+R

3

V

out

= V

in

V

out

V

in

=

R

4

(R

2

+R

3

)

R

1

+R

4

(R

2

+R

3

)

R

2

R

2

+R

3

1

=

(R

2

+R

3

) [R

1

+R

4

(R

2

+ R

3

)]

R

2

[R

4

(R

2

+R

3

)]

If R

1

0, we expect the result to be:

V

in

=

R

2

R

2

+R

3

V

out

V

out

V

in

R1=0

=

R

2

+R

3

R

2

= 1 +

R

3

R

2

Taking limit of the original expression as R

1

0, we have:

lim

R10

(R

2

+R

3

) [R

1

+R

4

(R

2

+R

3

)]

R

2

[R

4

(R

2

+R

3

)]

=

(R

2

+R

3

) [R

4

(R

2

+R

3

)]

R

2

[R

4

(R

2

+R

3

)]

= 1 +

R

3

R

2

This agrees with the expected result. Likewise, if R

3

0, we expect the result to be:

V

in

=

R

2

R

4

R

1

+R

2

R

4

V

out

V

out

V

in

R3=0

=

R

1

+R

2

R

4

R

2

R

4

= 1 +

R

1

R

2

R

4

Taking the limit of the original expression as R

3

0, we have:

lim

R30

(R

2

+R

3

) [R

1

+R

4

(R

2

+R

3

)]

R

2

[R

4

(R

2

+R

3

)]

=

R

2

(R

1

+R

2

R

4

)

R

2

(R

2

R

4

)

=

R

1

+R

2

R

4

R

2

R

4

= 1 +

R

1

R

2

R

4

This agrees with the expected result.

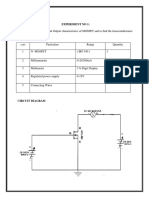

8.14 We need to derive the closed-loop gain of the following circuit:

v

in

+

R

2

+

v

X

R

1

v

out

R

out

A

0

v

X

+

v

X

= (v

out

v

in

)

R

2

R

1

+R

2

+v

in

v

out

= (A

0

v

X

v

in

)

R

1

+R

2

R

out

+R

1

+R

2

+v

in

=

A

0

(v

out

v

in

)

R

2

R

1

+R

2

+v

in

v

in

R

1

+R

2

R

out

+R

1

+R

2

+v

in

Grouping terms, we have:

v

out

1 +A

0

R

2

R

1

+R

2

R

1

+R

2

R

out

+R

1

+R

2

= v

in

R

1

+R

2

R

out

+R

1

+R

2

A

0

R

2

R

1

+R

2

A

0

1 +

R

out

+R

1

+R

2

R

1

+R

2

= v

in

R

1

+R

2

R

out

+R

1

+R

2

R

out

+R

1

+R

2

R

1

+R

2

A

0

R

1

R

1

+R

2

1

= v

in

1

R

out

+R

1

+R

2

[R

out

+R

1

+R

2

A

0

R

1

R

1

R

2

]

= v

in

1

A

0

R

1

+R

1

+R

2

R

out

+R

1

+R

2

v

out

v

in

=

1

A0R1+R1+R2

Rout+R1+R2

1 +

A0R2

Rout+R1+R2

=

R

out

+R

1

+R

2

A

0

R

1

R

1

R

2

R

out

+R

1

+R

2

+A

0

R

2

=

R

out

A

0

R

1

R

out

+R

1

+ (1 +A

0

) R

2

To nd the output impedance, we must nd Z

out

=

vt

it

for the following circuit:

R

2

+

v

X

R

1

i

t

v

t

+

R

out

A

0

v

X

+

i

t

=

v

t

+A

0

v

X

R

out

+

v

t

R

1

+R

2

v

X

=

R

2

R

1

+R

2

v

t

i

t

=

v

t

+A

0

R2

R1+R2

v

t

R

out

+

v

t

R

1

+R

2

= v

t

1

R

out

+

A

0

R

2

R

out

(R

1

+R

2

)

+

1

R

1

+R

2

= v

t

R

1

+ (1 +A

0

) R

2

+R

out

R

out

(R

1

+R

2

)

Z

out

=

v

t

i

t

=

R

out

(R

1

+R

2

)

R

1

+ (1 +A

0

) R

2

+R

out

8.15 Refer to the analysis for Fig. 8.42.

V

out

V

in

=

R

1

R

2

= 4

R

in

R

2

= 10 k

R

1

= 4R

2

= 40 k

From Eq. (8.99), we have

E = 1

A

0

Rout

R1

1 +

Rout

R2

+A

0

+

R1

R2

A

0

= 1000

R

out

= 1 k

E = 0.51 %

8.17

V

+

= V

(since A

0

= )

V

in

R

2

=

V

out

R

3

R

3

R

4

R

1

+R

3

R

4

V

out

V

in

=

R

3

R

2

R

1

+R

3

R

4

R

3

R

4

If R

1

0 or R

3

0, we expect the amplier to reduce to the standard inverting amplier.

V

out

V

in

R10

=

R

3

R

2

V

out

V

in

R30

=

R

1

R

2

The gain reduces to the expected expressions.

8.18

V

+

= V

(since A

0

= )

V

X

=

R

3

R

3

+R

4

V

out

=

R

2

R

1

+R

2

(V

out

V

in

) +V

in

V

out

R

3

R

3

+R

4

R

2

R

1

+R

2

= V

in

1

R

2

R

1

+R

2

V

out

R

3

(R

1

+R

2

) R

2

(R

3

+R

4

)

(R

1

+R

2

) (R

3

+R

4

)

= V

in

R

1

R

1

+R

2

V

out

V

in

=

R

1

(R

3

+R

4

)

R

3

(R

1

+R

2

) R

2

(R

3

+R

4

)

8.22 We must nd the transfer function of the following circuit:

v

in

+

R

1

R

in

+

v

X

C

1

v

out

A

0

v

X

+

v

out

= A

0

v

X

v

X

= v

out

1

sC

1

v

X

R

in

+

v

X

v

in

R

1

v

X

1 +

1

sR

in

C

1

+

1

sR

1

C

1

= v

out

+

v

in

sR

1

C

1

v

X

=

sR

1

R

in

C

1

v

out

+R

in

v

in

sR

1

R

in

C

1

+R

1

+R

in

v

out

= A

0

sR

1

R

in

C

1

v

out

+R

in

v

in

sR

1

R

in

C

1

+R

1

+R

in

v

out

1 +A

0

sR

1

R

in

C

1

sR

1

R

in

C

1

+R

1

+R

in

= A

0

v

in

R

in

sR

1

R

in

C

1

+R

1

+R

in

v

out

v

in

=

A

0

R

in

sR

1

R

in

C

1

+R

1

+R

in

sR

1

R

in

C

1

+R

1

+R

in

sR

1

R

in

C

1

+R

1

+R

in

+sR

1

R

in

C

1

A

0

=

A

0

R

in

sR

1

R

in

C

1

+R

1

+R

in

+sR

1

R

in

C

1

A

0

=

A

0

R

in

sR

1

R

in

C

1

(1 +A

0

) + R

1

+R

in

=

A

0

R

in

1 +s

R1RinC1(1+A0)

R1+Rin

=

A

0

R

in

/ (R

1

+R

in

)

1 +s (R

1

R

in

) C

1

(1 +A

0

)

s

p

=

1

(R

1

R

in

) C

1

(1 +A

0

)

Comparing this to the result in Eq. (8.37), we can see that we can simply replace R

1

with R

1

R

in

,

eectively increasing the pole frequency (since R

1

R

in

< R

1

for nite R

in

).

We can also write the result as

s

p

=

1

R

1

C

1

(1 +A

0

)

1 +

R

1

R

in

In this form, its clear that the pole frequency increases by 1 +R

1

/R

in

.

8.23 We must nd the transfer function of the following circuit:

v

in

+

R

1

+

v

X

C

1

v

out

R

out

A

0

v

X

+

v

out

= A

0

v

X

+

v

in

v

out

R

1

+

1

sC1

R

out

v

X

= v

in

+

R

1

R

1

+

1

sC1

(v

out

v

in

)

v

out

= A

0

v

in

+

R

1

R

1

+

1

sC1

(v

out

v

in

)

+

v

in

v

out

R

1

+

1

sC1

R

out

v

out

1 +

A

0

R

1

+R

out

R

1

+

1

sC1

= v

in

A

0

+

A

0

R

1

+R

out

R

1

+

1

sC1

v

out

R

1

+

1

sC1

+A

0

R

1

+R

out

R

1

+

1

sC1

= v

in

A

0

R

1

A

0

1

sC1

+A

0

R

1

+R

out

R

1

+

1

sC1

v

out

{1 +sC

1

[(1 +A

0

) R

1

+R

out

]} = v

in

{A

0

sC

1

R

out

}

v

out

v

in

=

A

0

sC

1

R

out

1 +sC

1

[(1 +A

0

) R

1

+R

out

]

s

p

=

1

C

1

[(1 + A

0

) R

1

+R

out

]

Comparing this to the result in Eq. (8.37), we can see that the pole gets reduced in magnitude due to

R

out

.

8.26 We must nd the transfer function of the following circuit:

v

in

+

C

1

R

in

+

v

X

R

1

v

out

A

0

v

X

+

v

out

= A

0

v

X

v

X

=

_

(v

in

v

X

) sC

1

v

X

v

out

R

1

_

R

in

v

X

_

1 +sR

in

C

1

+

R

in

R

1

_

= v

in

sR

in

C

1

+v

out

R

in

R

1

v

X

=

v

in

sR

in

C

1

+v

out

Rin

R1

1 +sR

in

C

1

+

Rin

R1

v

out

= A

0

v

in

sR

in

C

1

+v

out

Rin

R1

1 +sR

in

C

1

+

Rin

R1

v

out

_

1 +

A

0

Rin

R1

1 +sR

in

C

1

+

Rin

R1

_

= v

in

sR

in

C

1

A

0

1 +sR

in

C

1

+

Rin

R1

v

out

_

1 +sR

in

C

1

+ (1 +A

0

)

Rin

R1

1 +sR

in

C

1

+

Rin

R1

_

= v

in

sR

in

C

1

A

0

1 +sR

in

C

1

+

Rin

R1

v

out

_

1 +sR

in

C

1

+ (1 +A

0

)

R

in

R

1

_

= v

in

sR

in

C

1

A

0

v

out

v

in

=

sR

1

R

in

C

1

A

0

R

1

+sR

1

R

in

C

1

+ (1 +A

0

) R

in

lim

A0

v

out

v

in

= sR

1

C

1

Comparing this to Eq. (8.42), we can see that if we let A

0

, the result actually reduces to Eq.

(8.42).

8.27 We must nd the transfer function of the following circuit:

v

in

+

C

1

+

v

X

R

1

v

out

R

out

A

0

v

X

+

v

out

= A

0

v

X

+

v

in

v

out

R

1

+

1

sC1

R

out

v

X

= v

in

+

1

sC1

R

1

+

1

sC1

(v

out

v

in

)

v

out

= A

0

_

v

in

+

1

sC1

R

1

+

1

sC1

(v

out

v

in

)

_

+

v

in

v

out

R

1

+

1

sC1

R

out

v

out

_

1 +

A

0

1

sC1

+R

out

R

1

+

1

sC1

_

= v

in

_

A

0

+

A

0

1

sC1

+R

out

R

1

+

1

sC1

_

v

out

R

1

+

1

sC1

+A

0

1

sC1

+R

out

R

1

+

1

sC1

= v

in

A

0

R

1

A

0

1

sC1

+A

0

1

sC1

+ R

out

R

1

+

1

sC1

v

out

{1 +A

0

+sC

1

(R

1

+R

out

)} = v

in

{sC

1

(A

0

R

1

R

out

)}

v

out

v

in

=

sC

1

(A

0

R

1

R

out

)

1 +A

0

+sC

1

(R

1

+R

out

)

lim

A0

v

out

v

in

= sR

1

C

1

Comparing this to Eq. (8.42), we can see that if we let A

0

, the result actually reduces to Eq.

(8.42).

8.28

v

out

= A

0

v

= v

in

+ (v

out

v

in

)

1

sC1

R

1

_

1

sC1

R

1

_

+

_

1

sC2

R

2

_

v

out

= A

0

_

_

v

in

+ (v

out

v

in

)

1

sC1

R

1

_

1

sC1

R

1

_

+

_

1

sC2

R

2

_

_

_

v

out

_

_

1 +A

0

1

sC1

R

1

_

1

sC1

R

1

_

+

_

1

sC2

R

2

_

_

_

= v

in

A

0

_

_

1

1

sC1

R

1

_

1

sC1

R

1

_

+

_

1

sC2

R

2

_

_

_

v

out

_

1

sC1

R

1

_

+

_

1

sC2

R

2

_

+A

0

_

1

sC1

R

1

_

_

1

sC1

R

1

_

+

_

1

sC2

R

2

_ = v

in

A

0

_

1

sC1

R

1

_

+

_

1

sC2

R

2

_

_

1

sC1

R

1

_

_

1

sC1

R

1

_

+

_

1

sC2

R

2

_

v

out

_

(1 +A

0

)

_

1

sC

1

R

1

_

+

_

1

sC

2

R

2

__

= v

in

A

0

_

1

sC

2

R

2

_

v

out

v

in

= A

0

1

sC2

R

2

(1 +A

0

)

_

1

sC1

R

1

_

+

_

1

sC2

R

2

_

Unity gain occurs when the numerator and denominator are the same (note that we can drop the

negative sign since we only care about the magnitude of the gain):

A

0

_

1

sC

2

R

2

_

= (1 +A

0

)

_

1

sC

1

R

1

_

+

_

1

sC

2

R

2

_

(A

0

1)

_

1

sC

2

R

2

_

= (1 +A

0

)

_

1

sC

1

R

1

_

_

1

sC2

R

2

_

_

1

sC1

R

1

_ =

A

0

+ 1

A

0

1

It is possible to obtain unity gain by choosing the resistors and capacitors according to the above

formula.

8.31

v

out

= A

0

v

X

v

1

v

X

R

2

+

v

2

v

X

R

1

=

v

X

v

out

R

F

v

out

R

F

+

v

1

R

2

+

v

2

R

1

=

v

X

R

1

R

2

R

F

v

out

= A

0

(R

1

R

2

R

F

)

v

out

R

F

+

v

1

R

2

+

v

2

R

1

v

out

1 +A

0

(R

1

R

2

R

F

)

R

F

= A

0

(R

1

R

2

R

F

)

v

1

R

2

+

v

2

R

1

v

out

= A

0

(R

1

R

2

R

F

)

v1

R2

+

v2

R1

1 +A

0

(R1R2RF )

RF

= A

0

R

F

(R

1

R

2

R

F

)

v1

R2

+

v2

R1

R

F

+A

0

(R

1

R

2

R

F

)

=

v

1

R

2

+

v

2

R

1

[R

F

A

0

(R

1

R

2

R

F

)]

8.32 For A

0

= , we know that v

+

= v

, meaning that no current ows through R

P

. Thus, R

P

will have

no eect on v

out

.

v

out

= R

F

v

1

R

2

+

v

2

R

1

, A

0

=

For A

0

< , we have to include the eects of R

P

.

v

out

= A

0

v

X

v

X

=

v

1

v

X

R

2

+

v

2

v

X

R

1

+

v

out

v

X

R

F

R

P

v

X

1

R

P

+

1

R

1

+

1

R

2

+

1

R

F

=

v

1

R

2

+

v

2

R

1

+

v

out

R

F

v

X

=

v

1

R

2

+

v

2

R

1

+

v

out

R

F

(R

1

R

2

R

F

R

P

)

v

out

= A

0

v

1

R

2

+

v

2

R

1

+

v

out

R

F

(R

1

R

2

R

F

R

P

)

v

out

1 +

A

0

R

F

(R

1

R

2

R

F

R

P

)

= A

0

v

1

R

2

+

v

2

R

1

(R

1

R

2

R

F

R

P

)

v

out

= A

0

v

1

R

2

+

v

2

R

1

(R

1

R

2

R

F

R

P

)

1 +

A0

RF

(R

1

R

2

R

F

R

P

)

=

v

1

R

2

+

v

2

R

1

R

F

A

0

(R

1

R

2

R

F

R

P

)

R

F

+A

0

(R

1

R

2

R

F

R

P

)

=

v

1

R

2

+

v

2

R

1

[R

F

A

0

(R

1

R

2

R

F

R

P

)] , A

0

<

8.33 We must nd v

out

for the following circuit:

v

1

R

2

v

2

R

1

+

v

X

R

F

v

out

R

out

A

0

v

X

+

v

out

= A

0

v

X

+

v

1

v

X

R

2

+

v

2

v

X

R

1

R

out

= v

X

A

0

+

R

out

R

1

+

R

out

R

2

+R

out

v

1

R

2

+

v

2

R

1

v

X

= v

out

+

v

1

v

X

R

2

+

v

2

v

X

R

1

R

F

v

X

1

R

F

+

1

R

1

+

1

R

2

=

v

out

R

F

+

v

1

R

2

+

v

2

R

1

v

X

=

v

out

R

F

+

v

1

R

2

+

v

2

R

1

(R

1

R

2

R

F

)

v

out

=

v

out

R

F

+

v

1

R

2

+

v

2

R

1

(R

1

R

2

R

F

)

A

0

+

R

out

R

1

+

R

out

R

2

+R

out

v

1

R

2

+

v

2

R

1

Grouping terms, we have:

v

out

1 +

(R

1

R

2

R

F

)

A

0

+

Rout

R1R2

R

F

v

1

R

2

+

v

2

R

1

(R

1

R

2

R

F

)

A

0

+

R

out

R

1

R

2

+R

out

v

1

R

2

+

v

2

R

1

v

1

R

2

+

v

2

R

1

(R

1

R

2

R

F

)

A

0

+

R

out

R

1

R

2

+R

out

v

out

= R

F

v

1

R

2

+

v

2

R

1

R

out

+ (R

1

R

2

R

F

)

A

0

+

Rout

R1R2

R

F

+ (R

1

R

2

R

F

)

A

0

+

Rout

R1R2

8.34 We must nd v

out

for the following circuit:

v

1

R

2

v

2

R

1

R

in

+

v

X

R

P

R

F

v

out

A

0

v

X

+

v

out

= A

0

v

X

v

X

=

v

1

v

X

1 +

RP

Rin

R

1

+

v

2

v

X

1 +

RP

Rin

R

2

+

v

out

v

X

1 +

RP

Rin

R

F

R

in

Grouping terms, we have:

v

X

1

R

in

+

1 +

R

P

R

in

1

R

1

R

2

R

F

=

v

1

R

2

+

v

2

R

1

+

v

out

R

F

v

X

(R

1

R

2

R

F

) +R

P

+R

in

R

in

(R

1

R

2

R

F

)

=

v

1

R

2

+

v

2

R

1

+

v

out

R

F

v

X

=

v

1

R

2

+

v

2

R

1

+

v

out

R

F

R

in

(R

1

R

2

R

F

)

(R

1

R

2

R

F

) +R

P

+R

in

v

out

= A

0

v

1

R

2

+

v

2

R

1

+

v

out

R

F

R

in

(R

1

R

2

R

F

)

(R

1

R

2

R

F

) +R

P

+R

in

Grouping terms, we have:

v

out

1 +

A

0

R

F

R

in

(R

1

R

2

R

F

)

(R

1

R

2

R

F

) +R

P

+R

in

v

1

R

2

+

v

2

R

1

A

0

R

in

(R

1

R

2

R

F

)

(R

1

R

2

R

F

) +R

P

+R

in

v

out

R

F

[(R

1

R

2

R

F

) +R

P

+R

in

] +A

0

R

in

(R

1

R

2

R

F

)

R

F

[(R

1

R

2

R

F

) +R

P

+R

in

]

v

1

R

2

+

v

2

R

1

A

0

R

in

(R

1

R

2

R

F

)

(R

1

R

2

R

F

) +R

P

+R

in

Simplifying, we have:

v

out

=

v

1

R

2

+

v

2

R

1

A

0

R

F

R

in

(R

1

R

2

R

F

)

R

F

[(R

1

R

2

R

F

) +R

P

+R

in

] +A

0

R

in

(R

1

R

2

R

F

)

8.35

I

D1

=

Vin

R1

V

in

> 0

0 V

in

< 0

Plotting I

D1

(t), we have

0

V

0

/R

1

I

D

1

(

t

)

/ 0 /

t

V

0

0

V

0

V

i

n

(

t

)

=

V

0

c

o

s

(

t

)

(

D

o

t

t

e

d

)

8.36

I

D1

=

Vin

R1

V

in

> 0

0 V

in

< 0

Plotting I

D1

(t), we have

0

V

0

/R

1

I

D

1

(

t

)

/ 0 /

t

V

0

0

V

0

V

i

n

(

t

)

=

V

0

c

o

s

(

t

)

(

D

o

t

t

e

d

)

8.37

V

Y

=

V

in

V

D,on

V

in

< 0

V

DD

V

in

> 0

V

out

=

V

in

V

in

< 0

0 V

in

> 0

I

D1

=

Vin

R1

V

in

< 0

0 V

in

> 0

Plotting V

Y

(t) and V

out

(t), we have

/ 0 /

t

V

0

0

V

0

V

DD

V

in

(t) = V

0

cos(t)

V

Y

(t)

V

out

(t)

Plotting I

D1

(t), we have:

0

V

0

/

R

1

I

D1

(t)

V

0

0 V

0

V

in

(t) = V

0

cos(t) (Dotted)

8.38 Since the negative feedback loop is never broken (even when the diode is o, R

P

provides negative

feedback), V

+

= V

will always hold, meaning V

X

= V

in

.

We must determine when D

1

turns on/o to determine V

Y

. We know that for V

in

< 0, the diode will

be o, and V

X

will follow V

in

. As V

in

begins to go positive, the diode will remain o until

V

in

R

P

R

1

> V

D,on

Once the diode turns on, V

Y

will be xed at V

in

+V

D,on

. Thus, we can write:

V

X

= V

in

V

Y

=

V

in

1 +

RP

R1

V

in

< V

D,on

R1

RP

V

in

+V

D,on

V

in

> V

D,on

R1

RP

Plotting V

Y

(t) and V

out

(t), we have

/ 0 /

t

V

0

(1 + R

P

/R

1

)

V

0

0

V

0

V

0

+ V

D,on

V

in

(t) = V

0

cos(t)

V

X

(t)

V

Y

(t)

8.40 Note that although in theory the output is unbounded (i.e., by Eq. (8.66), we can take the logarithm

of an arbitrarily small positive number), in reality the output will be limited by the positive supply

rail, as shown in the following plot.

1 0 R

1

I

S

1

V

in

(V)

V

DD

0

1

V

out

V

X

8.42 When V

in

> 0, the feedback loop will be broken, and the output will go to the positive rail.

When V

in

< 0, we have:

I

C

=

V

in

R

1

= I

S

e

VBE/VT

= I

S

e

Vout/VT

V

out

= V

T

ln

V

in

R

1

I

S

This gives us the following plot of V

out

vs. V

in

:

1 0 R

1

I

S

1

V

in

(V)

V

DD

0

V

o

u

t

(

V

)

Note that this circuit fails to behave as a non-inverting logarithmic amplier.

8.44 (a)

V

out

= V

T

ln

V

in

R

1

I

S

0.2 V = V

T

ln

1 V

R

1

I

S

R

1

I

S

= 456 V

(b)

A

v

=

dV

out

dV

in

Vin=1 V

=

V

T

V

in

Vin=1 V

= 0.026

8.45 When V

in

< V

TH

, the output goes to the positive rail. When V

in

> V

TH

, we have:

I

D

=

V

in

V

TH

R

1

V

GS

= V

out

= V

TH

+

2I

D

W

L

n

C

ox

V

out

= V

TH

2 (V

in

V

TH

)

R

1

W

L

n

C

ox

dV

out

dV

in

=

1

2

R

1

W

L

n

C

ox

2 (V

in

V

TH

)

2

R

1

W

L

n

C

ox

=

1

2R

1

W

L

n

C

ox

(V

in

V

TH

)

, V

in

> V

TH

8.46 When V

in

> 0, the output goes to the negative rail. When V

in

< 0, we have:

I

D

=

V

in

R

1

V

SG

= V

out

= |V

TH

| +

2 |I

D

|

W

L

p

C

ox

V

out

= V

TH

+

2V

in

R

1

W

L

p

C

ox

, V

in

< 0

8.49 We model an input oset with a series voltage source at one of the inputs.

+

V

os

R

2

+

V

in

R

1

V

out

V

out

= V

in

V

in

V

os

R

2

(R

1

+R

2

)

= V

in

1

R

1

+R

2

R

2

+V

os

R

1

+R

2

R

2

=

R

1

R

2

V

in

+

1 +

R

1

R

2

V

os

Note that even when V

in

= 0, V

out

= (1 +R

1

/R

2

) V

os

.

8.54 Let V

in

= 0.

V

+

= I

B1

(R

1

R

2

) = (I

B2

+ I) (R

1

R

2

) = V

V

out

= V

I

B2

+

V

R

2

R

1

= (I

B2

+ I) (R

1

R

2

) +

I

B2

(I

B2

+ I) (R

1

R

2

)

R

2

R

1

= (I

B2

+ I) (R

1

R

2

)

1 +

R

1

R

2

+I

B2

R

1

= IR

1

If the magnitude of the error must be less than V , we have:

IR

1

< V

R

1

<

V

I

Note that this does not depend on R

2

.

8.57

V

out

=

A

0

1 +

s

0

V

= V

in

+

V

out

V

in

R

1

+

1

sC1

R

1

V

out

=

A

0

1 +

s

0

V

in

+

V

out

V

in

R

1

+

1

sC1

R

1

V

out

1 +

A

0

1 +

s

0

R

1

R

1

+

1

sC1

=

A

0

1 +

s

0

V

in

R

1

R

1

+

1

sC1

1

V

out

1 +

s

0

R

1

+

1

sC1

+A

0

R

1

1 +

s

0

R

1

+

1

sC1

= V

in

A

0

1

sC1

1 +

s

0

R

1

+

1

sC1

V

out

V

in

=

A

0

1

sC1

1 +

s

0

R

1

+

1

sC1

+A

0

R

1

=

A

0

1 +

s

0

(1 +sR

1

C

1

) +sA

0

R

1

C

1

=

A

0

1 +s

R

1

C

1

+

1

0

+A

0

R

1

C

1

+s

2

R1C1

0

=

A

0

1 +s

(1 +A

0

) R

1

C

1

+

1

0

+s

2

R1C1

0

If

0

1

R1C1

, we have:

V

out

V

in

=

1

1

A0

+s

1 +

1

A0

R

1

C

1

+

1

0

+s

2

R1C1

A00

=

1

1

A0

+s

1 +

1

A0

R

1

C

1

+s

2

R1C1

A00

1

sR

1

C

1

+s

2

R1C1

A00

(assuming A

0

1)

=

1

sR

1

C

1

1 +

s

A00

8.61 Let E refer to the gain error.

R

1

R

2

= 8

R

1

= 8 k

R

2

= 1 k

v

out

v

in

=

R

1

R

2

A

0

Rout

R1

1 +

Rout

R2

+ A

0

+

R1

R2

(Eq. 8.99)

=

R

1

R

2

(1 E)

E = 1

A

0

Rout

R1

1 +

Rout

R2

+ A

0

+

R1

R2

= 0.1 %

A

0

= 9103

Note that we can pick any R

1

, R

2

such that their ratio is 8 (i.e., this solution is not unique). However,

A

0

will change depending on the values chosen.

8.66

V

out

= V

T

ln

V

in

R

1

I

S

dV

out

dV

in

= V

T

R

1

I

S

V

in

1

R

1

I

S

=

V

T

V

in

No, it is not possible to satisfy both requirements. As shown above,

dVout

dVin

=

VT

Vin

, meaning for a

specied temperature and input, the gain is xed. Assuming we could x the temperature as part of

the design, we could still only meet one of the two constraints, since the temperatures at which the

constraints are met are not equal.

You might also like

- Solns 2cmosDocument18 pagesSolns 2cmosramprakash_rampelliNo ratings yet

- Semiconductor Device CalculationsDocument37 pagesSemiconductor Device Calculationsbhasin_hemantNo ratings yet

- Chap005 - CH5 Solution of Power Electronics by Daniel W.Hart Chap005 - CH5 Solution of Power Electronics by Daniel W.HartDocument13 pagesChap005 - CH5 Solution of Power Electronics by Daniel W.Hart Chap005 - CH5 Solution of Power Electronics by Daniel W.HarthassanNo ratings yet

- Access Full Complete Solution Manual Here: Chapter 1 SolutionsDocument8 pagesAccess Full Complete Solution Manual Here: Chapter 1 SolutionsAlexander AndersonNo ratings yet

- Calculus of Residue and Contour IntegrationDocument78 pagesCalculus of Residue and Contour IntegrationPrateekKumarJaysinghaniNo ratings yet

- DIGITAL SIGNAL PROCESSING LAB REPORTDocument8 pagesDIGITAL SIGNAL PROCESSING LAB REPORTHAMZA ALINo ratings yet

- Capitulo 09Document16 pagesCapitulo 09Tamires MarianeNo ratings yet

- Power Electronics Solution Manual Chapter 3 Daniel Hart PDFDocument33 pagesPower Electronics Solution Manual Chapter 3 Daniel Hart PDFRobiul Islam FarhadNo ratings yet

- Solucionario CAP 5 RAZAVIDocument112 pagesSolucionario CAP 5 RAZAVIBenjaminJimenezNo ratings yet

- Solns - 5 CmosDocument12 pagesSolns - 5 Cmosramprakash_rampelliNo ratings yet

- Solns - 1 CmosDocument15 pagesSolns - 1 Cmosramprakash_rampelliNo ratings yet

- Chapter 7 of Fundamentals of MicroelectronicsDocument33 pagesChapter 7 of Fundamentals of MicroelectronicsjenellaneNo ratings yet

- Solns 9Document66 pagesSolns 9ramprakash_rampelliNo ratings yet

- Chapter 05Document14 pagesChapter 05Johnny Lee Worthy IIINo ratings yet

- Chapter 04Document13 pagesChapter 04Johnny Lee Worthy IIINo ratings yet

- 470 39 Solutions-Instructor-Manual SM Chapter-9 PDFDocument3 pages470 39 Solutions-Instructor-Manual SM Chapter-9 PDFSerajNo ratings yet

- N D Av V V DN V Bi A VDR VD I A LF I I I A I I I A VD C V RCF V V VDocument28 pagesN D Av V V DN V Bi A VDR VD I A LF I I I A I I I A VD C V RCF V V VhassanNo ratings yet

- Chap17 Frequency ResponseDocument61 pagesChap17 Frequency ResponseMạnh Cường TrầnNo ratings yet

- Circuit Analysis Chapter 6 Exercises SolutionsDocument13 pagesCircuit Analysis Chapter 6 Exercises SolutionsJohnny Lee Worthy IIINo ratings yet

- Vlsi Lab AssignmentDocument5 pagesVlsi Lab AssignmentRahul Saxena100% (1)

- L18 FET DC Analysis 2 and Common Source S2 18 19Document42 pagesL18 FET DC Analysis 2 and Common Source S2 18 19MANI SINGHNo ratings yet

- Chapter 2Document15 pagesChapter 2Abd Alkader Alwer100% (1)

- Chapter 02Document22 pagesChapter 02Andres A. TabuyoNo ratings yet

- Assignment 1Document9 pagesAssignment 1Taslima Rahman MiliNo ratings yet

- 2016 Ch2-MOS TransistorsDocument47 pages2016 Ch2-MOS Transistorsជើងកាង ភូមិNo ratings yet

- Tutorial 5 SolutionsDocument11 pagesTutorial 5 SolutionsbarneyNo ratings yet

- Chapter3 Rabaey MOS Capacitances OnlyDocument19 pagesChapter3 Rabaey MOS Capacitances OnlyRaheetha AhmedNo ratings yet

- Full-Wave RectifierDocument7 pagesFull-Wave Rectifiermohdshujaat100% (2)

- Solutions Manual Microelectronic Circuits Analysis and Design 2nd Edition RashidDocument10 pagesSolutions Manual Microelectronic Circuits Analysis and Design 2nd Edition RashidOrlando Ernesto Abreu CruzNo ratings yet

- Access Full Complete Solution Manual Here: Chapter 1 SolutionsDocument8 pagesAccess Full Complete Solution Manual Here: Chapter 1 SolutionsKevin Carpio0% (1)

- Unit Vii Fet AmplifiersDocument14 pagesUnit Vii Fet AmplifiersAadarsha timilsinaNo ratings yet

- MOSFET circuit analysis and design techniquesDocument85 pagesMOSFET circuit analysis and design techniquesTaís LaurindoNo ratings yet

- Signal Generator Project StatementDocument16 pagesSignal Generator Project StatementHussain Bin AliNo ratings yet

- Circuit Simulation Using X CosDocument16 pagesCircuit Simulation Using X Cosmcardinot12No ratings yet

- Microelectronic Circuits 8 Edition: A. Sedra, K.C. Smith T. Chan Carusone, V. GaudetDocument14 pagesMicroelectronic Circuits 8 Edition: A. Sedra, K.C. Smith T. Chan Carusone, V. Gaudetgain xing GuoNo ratings yet

- Elmore DelayDocument3 pagesElmore DelaySaad Bin TariqNo ratings yet

- Wave Equations and SolutionsDocument34 pagesWave Equations and SolutionsAllas JonyNo ratings yet

- Pspice Lab ManualDocument30 pagesPspice Lab ManualSrinivasarao ThumatiNo ratings yet

- Mosfet CharacteristicsDocument10 pagesMosfet CharacteristicsAnonymous eWMnRr70qNo ratings yet

- EE 174 Fall 2019: Operational AmplifiersDocument36 pagesEE 174 Fall 2019: Operational AmplifiersKavyashreeMNo ratings yet

- R-C and Wien Bridge OscillatorsDocument8 pagesR-C and Wien Bridge Oscillatorsলাজ মাহমুদNo ratings yet

- 15.1 (A) For Example:: Problem SolutionsDocument46 pages15.1 (A) For Example:: Problem SolutionsLuis AntonioNo ratings yet

- Position and Orientation of Rigid Bodies: Robotics 1Document20 pagesPosition and Orientation of Rigid Bodies: Robotics 1Bharath KumarNo ratings yet

- ECE 550 Lecture Notes 1Document181 pagesECE 550 Lecture Notes 1haroutuonNo ratings yet

- 30 + 0,6V o Io I1: Baøi Taäp Chöông 5 5 - 15Document19 pages30 + 0,6V o Io I1: Baøi Taäp Chöông 5 5 - 15Vu VanNo ratings yet

- Correlation and Autocorrelation of AR ProcessesDocument20 pagesCorrelation and Autocorrelation of AR ProcessesEngr Kamran JavedNo ratings yet

- Control FormulasDocument7 pagesControl FormulasBeto GuapiNo ratings yet

- Ohmmeters: A Meter A Meter I IDocument7 pagesOhmmeters: A Meter A Meter I IBright BreezeNo ratings yet

- The Phase-Shift Oscillator:: V R) C j / 1 R (− ω + − − ω +Document3 pagesThe Phase-Shift Oscillator:: V R) C j / 1 R (− ω + − − ω +ashik ahmedNo ratings yet

- Statika i dinamika tranzistorskog pojačalaDocument13 pagesStatika i dinamika tranzistorskog pojačalaAmar HodzicNo ratings yet

- Files-3-Lesson Notes Lecture 31Document8 pagesFiles-3-Lesson Notes Lecture 31Eyad Abozyd100% (1)

- Eel 3303L-Electronics I Lab: Second ACTIVITY: Basic Differential Amplifier and Summing AmplifierDocument16 pagesEel 3303L-Electronics I Lab: Second ACTIVITY: Basic Differential Amplifier and Summing Amplifiermasood ahmadNo ratings yet

- Note 4 Transmission Lines (Bounce Diagram)Document31 pagesNote 4 Transmission Lines (Bounce Diagram)Charan Macharla'sNo ratings yet

- Oe Been OscDocument13 pagesOe Been Oscdarex77No ratings yet

- Amplifiers Circuits, & Ilters of Asics: Ohm's LawDocument42 pagesAmplifiers Circuits, & Ilters of Asics: Ohm's LawĐinh Mỹ Huyền ViNo ratings yet

- Esc201: Introduction To Electronics: Operational Amplifier Operational Amplifier Part 2Document26 pagesEsc201: Introduction To Electronics: Operational Amplifier Operational Amplifier Part 2egupta1No ratings yet

- The BJT Differential Amplifier Circuit and AnalysisDocument4 pagesThe BJT Differential Amplifier Circuit and AnalysisAswathi MVNo ratings yet

- Elec1111 02b Series Parallel PDocument4 pagesElec1111 02b Series Parallel PuploadingpersonNo ratings yet

- Note On DesmoothingDocument2 pagesNote On DesmoothingAbhishek VermaNo ratings yet

![Mathematical Tables: Tables of in G [z] for Complex Argument](https://imgv2-2-f.scribdassets.com/img/word_document/282615796/149x198/febb728e8d/1699542561?v=1)