Professional Documents

Culture Documents

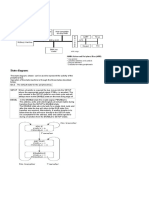

APB Bridge Module Connects AXI and APB

Uploaded by

Vikas ZurmureOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

APB Bridge Module Connects AXI and APB

Uploaded by

Vikas ZurmureCopyright:

Available Formats

Apb Bridge `timescale 1ns / 1ps module apb_bridge_cha(input Aclk, input Pclk, input Rst, input Awvalid, input

[31:0]Awaddr, input Wvalid, input [31:0] Wdata, input [3:0] Wstrb, input Bready, input Arvalid, input [31:0] Araddr, input Rready, input Pready, input [31:0] Prdata, input Pslverr, output reg Awready, output reg Wready, output reg Bvalid, output reg Bresp, output reg Arready, output reg Rvalid, output reg[31:0] Rdata, output reg Rresp, output reg [31:0] Paddr, output reg Psel, output reg Penable, output reg Pwrite, output reg [31:0] Pwdata , output reg [3:0] Pstrb) ; ///********************************Signals Of the Internal********************** ********* ///INTERNAL SIGNALS ///INTERCONNCTES SIGNALS reg [1:0] awvalid_s,wvalid_s,arvalid_s; reg bvalid_s; reg awvalid_initial,arvalid_initial; reg [31:0] awaddr_s,araddr_s; reg pready_s,pslverr_s; reg rready_s; reg [31:0] prdata_s,wdata_s; reg a_wr_s,a_rd_s,p_wr_s,p_rd_s; wire [31:0] pwdata_s_w,rdata_s_w; reg rd_addr,wr_addr; reg [31:0]paddr_s; wire [31:0]paddr_s2; reg bvalid1,bvalid2; reg rready_s1,rready_s2,rready_s3; ---- Address logic for the interface -----Addresss Selection -----Assgining the signal AXI Signal to a Signal -----Later the signal is conncted to the FIFO Input Signal ---------------------------------------------------------------------------------*/

always@(Arvalid,araddr_s,awaddr_s,Awvalid) begin if(Arvalid) paddr_s<= araddr_s; else paddr_s <= awaddr_s; end /*----------------Completed The Address Logic Signals----------------------------------*/ A read and write request are asserted on same time then give a priority signal ---for the read signal than write signal. always@(Awvalid,Arvalid) begin if((Awvalid == 1'b1)&(Arvalid==1'b1)) begin awvalid_initial = 1'b0; arvalid_initial = 1'b1; end else if((Awvalid == 1'b1)&(Arvalid==1'b0)) begin awvalid_initial = 1'b1; arvalid_initial = 1'b0; end else if((Awvalid == 1'b0)&(Arvalid==1'b1)) begin awvalid_initial = 1'b0; arvalid_initial = 1'b1; end else begin awvalid_initial = 1'b0; arvalid_initial = 1'b0; end end /*----------------------Priority Of the signals is completed-------------------------------Write Signals For AW signals-----------------------Awvalid Should be High For The Address Transfer ---Awready Should get High For the Pready is High signal ---If Pready is low and Awvalid is hign signal then the signals ---incidacte that the AXI(Master) is ready but Apb(Slave) is not ready to recevi ce. ---If Pready is High and Awvalid is Low signals then the signals that ---incidacet that the AXI(Master) is not ready but ABP(Slvae) is ready. ---If Pready is high than Awready signal will be High. ---When Pready and Awvalid is Both are High,We make one enable signal that will be HIgh ---when both signals will be high. always@(posedge Aclk) begin if(~Rst) begin awvalid_s <= 2'b0; Awready <= 1'b0; awaddr_s <= 32'h0; end else if((awvalid_initial==1'b1)&(pready_s==1'b1)) begin awvalid_s <= 2'b11; awaddr_s <= Awaddr;

Awready <= 1'b1; end else if((awvalid_initial==1'b0)&(pready_s==1'b1)) begin awvalid_s <= 2'b01; Awready <= 1'b1; // awaddr_s <= 32'h0; end else if((awvalid_initial==1'b1)&(pready_s==1'b0)) begin awaddr_s <= Awaddr; awvalid_s <= 2'b10; Awready <= 1'b0; end else begin // awaddr_s <= 32'h0; awvalid_s <= 2'b0; Awready <= 1'b0; end end //----------------------------------------------------------------------In this process Wdata tranfter Takes Place Here ---Wdata signal & Wready signals Pready. ---Wdata is take from when Wvalid is High. ---Wready is high if Pready Signal is High if not it will be Low. ---I have take One Enable signal .The enable Signal will be High both ---Signal(Wvalid,Pready,AWenable)should be high. ---Wready will be High if Pready is High. ---Wvalid is high then only my Data will Taken from input ----------------------------------------------------------------------always@(po sedge Aclk) begin if(~(Rst)) begin wvalid_s <= 2'b0; wdata_s <= 32'h0; Wready <= 1'b0; Pstrb <= 4'h0; end else if(awvalid_s==2'b11) begin if((Wvalid==1'b1)&(pready_s==1'b1)) begin wdata_s <= Wdata; wvalid_s <= 2'b11; Wready <= 1'b1; Pstrb <= Wstrb; end else if((Wvalid==1'b0)&(pready_s==1'b1)) begin wvalid_s <=2'b01; Wready <= 1'b1; Pstrb <= 4'h0; end else if((Wvalid==1'b1)&(pready_s==1'b0)) begin wdata_s <= Wdata; wvalid_s <= 2'b10; Wready <= 1'b0;

Pstrb <= Wstrb; end else begin wvalid_s <= 2'b00; Wready <= 1'b0; Pstrb <= 4'h0; end end else if((awvalid_s==2'b01)|(awvalid_s==2'b10)|(awvalid_s==2'b0)) begin wdata_s <= 32'h0; wvalid_s <= 2'b0; Wready <=0; Pstrb <= 0; end end **********************Response Signals on the AXI side************************** ** ---Bvalid,Pslverr ---Bvalid is Resopse signal Of Axi Data . ---It will respond That when slave have receviced the data from Master reg p_rd_ss; ///I have made Regters Logic when we are Changing from One clock Domain to Other Clock Domain always@(posedge Aclk) begin if(~Rst) begin Bvalid<= 1'b0; bvalid1<=1'b0; bvalid2<= 1'b0; end else if(p_rd_ss) begin bvalid1 <=bvalid_s; bvalid2 <=bvalid1; Bvalid <= bvalid2; end else begin bvalid1<=bvalid_s; bvalid2 <=bvalid1; Bvalid <= bvalid2; end end always@(posedge Aclk) begin if(~Rst) begin bvalid_s<= 1'b0; end else if((awvalid_s==2'b11)&(pslverr_s==1'b0)) begin if((wvalid_s==2'b11)&(pready_s==1'b1)) begin bvalid_s<= 1'b1; end

else begin bvalid_s<= 1'b0; end end else begin bvalid_s<= 1'b0; end end --- Bresp from to AXI signals from APB . ---INtially We have Bvalid signal then Axi will Send Bready signal to Abp ---If Bready is HIgh than Bresp will be High. always@(posedge Aclk) begin if(~Rst) begin Bresp <= 1'b0; end else if(bvalid_s) begin if(Bready) begin Bresp <= 1'b1; end else begin Bresp <= 1'b0; end end else begin Bresp <= 1'b0; end end ****************************** Read Signals on the AXI side ******************** ---Arvalid Should be High For The Address Transfer ---Arready Should get High For the Pready is High signal ---If Pready is low and Arvalid is hign signal then the signals ---incidacte that the AXI(Master) is ready but Apb(Slave) is not ready to recevi ce. ---If Pready is High and Arvalid is Low signals then the signals that ---incidacet that the AXI(Master) is not ready but ABP(Slvae) is ready. ---If Pready is high than Arready signal will be High. ---When Pready and Arvalid is Both are High,We make one enable signal that will be HIgh ---when both signals will be high. ----------------------------------------------------------------------always@(po sedge Aclk) begin if(~Rst) begin Arready <=1'b0; arvalid_s <= 2'b00; araddr_s <= 32'h0; end else if((arvalid_initial==1'b1)&(pready_s==1'b1)) begin arvalid_s <= 2'b11;

araddr_s <= Araddr; Arready <= 1'b1; end else if((arvalid_initial==1'b1)&(pready_s==1'b0)) begin arvalid_s <= 2'b10; araddr_s <= Araddr; Arready <= 1'b0; end else if((arvalid_initial==1'b0)&(pready_s==1'b1)) begin arvalid_s <= 2'b01; araddr_s <= 32'h0; Arready <= 1'b1; end else begin arvalid_s <= 2'b00; araddr_s <= 32'h0; Arready <= 1'b0; end end --Read Data Signal . ---In The process Slave will be sending the Data for particular Addresss ---which is send by AXI(Master). ---In this process we will be writing Only the enable signals. always@(posedge Aclk) begin if(~Rst) begin Rvalid <= 1'b0; rready_s<=1'b0; end else if(arvalid_s == 2'b11) begin if((pready_s==1'b1)&(Rready==1'b1)) begin Rvalid <= 1'b1; rready_s <= 1'b1; end else if((pready_s==1'b0)&(Rready==1'b1)) begin Rvalid <= 1'b0; rready_s <= 1'b1; end else if((pready_s==1'b1)&(Rready==1'b0)) begin Rvalid <= 1'b1; rready_s <= 1'b0; end else begin Rvalid <= 1'b0; rready_s <= 1'b0; end end else begin Rvalid <= 1'b0;

rready_s <= 1'b0; end end --- Read Resopse Singal always@(posedge Aclk ) begin if(~Rst) begin Rresp <= 1'b0; end else if((pslverr_s==1'b0)&(rready_s1==1'b1)) begin Rresp <= 1'b1; end else begin Rresp <= 1'b0; end end ---It internal Signa for the Enabling ---a_rd_s: Incidates that AXI READ SIGNAL FOR THE FIFO ---LOGIC THAT WHEN FIFO SHOULD READ THE DATA FROM FIFO OUT . always@(posedge Aclk) begin if(~Rst) begin a_rd_s <= 1'b0; end else if((pready_s==1'b1)&(arvalid_s==2'b11)) begin if((rready_s)) begin a_rd_s <= 1'b1; end else begin a_rd_s <= 1'b0; end end end ---INTERNAL SIGNAL PURPOSE ---PREADY SIGNAL :IT REPRESENT THAT SLAVE IS READY NOT TO RECEVICE THE DATA SIGN AL ---ANY CONTROL SIGNALS always@(posedge Pclk) begin if(~Rst) begin pready_s <= 1'b0; end else if(Pready) begin pready_s <= 1'b1; end else begin pready_s <= 1'b0; end end

---PLSVERR SIGNAL ---THIS IS SHOWS ERROR INCIDATION ---IF THERE IS ERROR IT IS HIGH IF NOT LOW always@(posedge Pclk) begin if(~Rst) begin pslverr_s <= 1'b0; end else begin if(Pslverr) begin pslverr_s <= 1'b1; end else begin pslverr_s <= 1'b0; end end end --- IN THIS PRO0ESS ---WHEN SHOULD READ DATA SHOULD BE TAKEN IN always@(posedge Pclk) begin if(~Rst) begin prdata_s <= 32'h0; end else if((arvalid_initial==1'b1)&(Pready==1'b1)&(Rready==1'b1)) begin prdata_s <= Prdata; end else if((arvalid_initial==1'b1)&(Pready==1'b0)&(Rready==1'b1)) begin prdata_s <= Prdata; end else if((arvalid_initial==1'b0)&(Pready==1'b1)&(Rready==1'b0)) begin prdata_s <= 32'h0; end else begin prdata_s <= 32'h0; end end ---P_WR_S:INCIDATES THAT ABP SIDE WRITE SIGNAL FOR THE READ FIFO always@(posedge Pclk) begin if(~Rst) begin p_wr_s <= 1'b0; end else if((rready_s==1'b1)&(pready_s==1'b1)) begin p_wr_s <= 1'b1; end else begin p_wr_s <= 1'b0;

end end ---PENABLE SIGNAL reg penable1,penable2,penable3,penable4; always@(posedge Pclk) begin if(~Rst) begin Penable <= 1'b0; penable1<= 1'b0; penable2<= 1'b0; penable3<= 1'b0; penable4<= 1'b0; end else if((Wready)) begin penable1<= 1'b1; penable2 <=penable1; penable3<= penable2; penable4<= penable3; Penable <= penable4; end else begin penable1<= 1'b0; penable2<= penable1; penable3<= penable2; penable4<= penable3; Penable <= penable4; end end ---PWDATA : IT IS SOUTPUT SIGNAL ---TAKING DATA FROM WRITE FIFO always@(posedge Pclk) begin if(~Rst) begin Pwdata<= 32'h0; end else if((Penable==1'b1)|(pready_s==1'b1)) begin Pwdata <= pwdata_s_w; end else begin Pwdata <= 32'h0; end end ---RDATA SIGNAL ON AXI SIDE ---THIS SIGNAL TAKE DATA FROM ABP SLAVE GIVE IT TO AXI always@(posedge Aclk) begin if(~Rst) Rdata <= 32'h0; else if(a_rd_s) Rdata <= rdata_s_w;

else Rdata <= 32'h0; end /***************************FIFO Interfacing Logic****************************** ***************/ //ENABLE SIGNAL FOR FIFO SIGNAL reg wready_s; always@(posedge Aclk) begin if(~Rst) begin wready_s <= 1'b0; end else if(Wready) begin wready_s <= 1'b1; end else begin wready_s <= 1'b0; end end reg p_rd_en; always@(posedge Aclk) begin if(~Rst) begin a_wr_s <=1'b0; p_rd_en <=1'b0; end else if((pslverr_s==1'b0)&(Wready==1'b1)) begin p_rd_en <= 1'b1; a_wr_s <= 1'b1; end else begin a_wr_s <=1'b0; p_rd_en <=1'b0; end end reg rd_a; always@(posedge Pclk) begin if(~Rst) begin p_rd_s <= 1'b0; end else if((p_rd_en==1'b1)|(rd_a==1'b1)) begin p_rd_s <= 1'b1; end else p_rd_s <= 1'b0;

end reg p_rd_ss1,p_rd_ss2; always@(posedge Pclk) begin if(~Rst) begin p_rd_ss <= 1'b0; p_rd_ss1 <= 1'b0; p_rd_ss2 <= 1'b0; end else begin p_rd_ss <= p_rd_s; p_rd_ss1 <= p_rd_ss; p_rd_ss2 <=p_rd_ss1; end end //---WRITE FIFO INTERFACING MODULE fifo_code wr_fifo(.Data_in(wdata_s), .RClk(Pclk), .ReadEn_in(p_rd_ss2), .Clear_in(Rst), .WClk(Aclk), .WriteEn_in(a_wr_s), .Data_out(pwdata_s_w) // empty, //full ); //---READ FIFO INTERFACING MODULE fifo_code rd_fifo(.Data_in(prdata_s), .RClk(Aclk), .ReadEn_in(a_rd_s), .Clear_in(Rst), .WClk(Pclk), .WriteEn_in(p_wr_s), .Data_out(rdata_s_w) //empty, //full ); //-------------- Pwrite Sognal For the reg pwrite1,pwrite2; always@(posedge Pclk) begin if(~Rst) begin Pwrite <= 1'b0; pwrite1<= 1'b0; pwrite2<= 1'b0; end

else if((wready_s))//|(Wready==1'b1)) begin pwrite1<= 1'b1; pwrite2 <=pwrite1; Pwrite <= pwrite2; end else begin pwrite1<= 1'b0; pwrite2<= pwrite1; Pwrite <= pwrite2; end end /*The Address fifo have tochange*/ reg rd_en; always@(posedge Aclk) begin if(~Rst) begin wr_addr = 1'b0; rd_en =1'b0; end else if(((Awready==1'b1)|(Arready==1'b1))&(pslverr_s==1'b0)&(pready_s==1'b1)&((awva lid_s==2'b11)|(arvalid_s==2'b11))) begin wr_addr = 1'b1; rd_en =1'b1; end else begin rd_en =1'b0; wr_addr = 1'b0; end end always@(posedge Pclk) begin if(~Rst) rd_addr <= 1'b0; else if((rd_en==1'b1)) rd_addr <= 1'b1; else rd_addr <= 1'b0; end always@(posedge Pclk) begin if(~Rst) rd_a <= 1'b0; else if(( rd_addr==1'b1)) rd_a <= 1'b1; else rd_a <= 1'b0; end fifo_code addr(.Data_in(paddr_s), .RClk(Pclk), .ReadEn_in(rd_addr),

.Clear_in(Rst), .WClk(Aclk), .WriteEn_in(wr_addr), .Data_out(paddr_s2) ); ---SLECTION OF SLAVE always@(posedge Pclk) begin if(~Rst) begin Psel <= 1'b0; end else if((rd_addr==1'b1)&(pslverr_s==1'b0)) begin if(pready_s==1'b1) begin Psel <= 1'b1; end else begin Psel <= 1'b0; end end end //---ADDRESS ON ABP SIDE always@(posedge Pclk) begin if(~Rst) Paddr <= 32'h0; else Paddr <= paddr_s2; end //ENABLE FOR READ READY SIGNAL always@(posedge Aclk) begin if(~Rst) rready_s1 <=1'b0; else rready_s1 <=rready_s3; end always@(posedge Aclk) begin if(~Rst) rready_s2 <= 1'b0; else begin rready_s2 <= rready_s; rready_s3 <= rready_s2; end end //------------------------------------------------------------------------------endmodule

//--------------Completed Code For the Apb Bridge--------------------------------// `timescale 1ns / 1ps //-----------------------------------------------------------------------------module apb_uart_top ( //APB Interface input PCLK, input PRESETn, input PSEL, input PENABLE, input PWRITE, input [31:0] PWDATA, input [31:0] PADDR, output [31:0] PRDATA, ///UART output tx, input rx ); wire [7:0]uart_rx_data,uart_tx_data; wire uart_rd,uart_wr; wire txrdy,rxrdy; //----------------------------------------------------------------------------// Input/Output Declaration //----------------------------------------------------------------------------//Instantiation of UART Controller Register module APB Interface apb_interface APB_IF(.PCLK(PCLK), .PRESETn(PRESETn), .PSEL(PSEL), .PENABLE(PENABLE), .PWRITE(PWRITE), .PWDATA(PWDATA), .PADDR(PADDR), .PRDATA(PRDATA), .uart_rx_data(uart_rx_d ata), .uart_tx_data(uart_tx_d ata), .rxrdy(rxrdy), .txrdy(txrdy), .uart_rd(uart_rd), .uart_wr(uart_wr) ); uart UART_TOP(.clk(PCLK), .rst(PRESETn), .wr(uart_wr), .rd(uart_rd), .rx(rx), .tx(tx), .din(uart_tx_data), .rdata_out(uart_rx_data), .txrdy(txrdy),

.rxrdy(rxrdy) );

endmodule //<<UART_cntrl>> FIFO MODULE module fifo_code #(parameter DATA_WIDTH ADDRESS_WIDTH //FIFO_DEPTH //Reading port (output reg [31:0] output reg input wire input wire //Writing port. input wire [31:0] output reg input wire input wire input wire

= 32, = 7) = (1 << ADDRESS_WIDTH)) Data_out, Empty_out, ReadEn_in, RClk, Data_in, Full_out, WriteEn_in, WClk, Clear_in);

/////Internal connections & variables////// reg [31:0] Mem [0:255]; wire [7:0] pNextWordToWrite, pNextWordToRead; wire EqualAddresses; wire NextWriteAddressEn, NextReadAddressEn; wire Set_Status, Rst_Status; reg Status; wire PresetFull, PresetEmpty; //////////////Code/////////////// //Data ports logic: //(Uses a dual-port RAM). //'Data_out' logic: always @ (posedge RClk,negedge Clear_in) begin if(~Clear_in) Data_out <= 32'h0; else if (ReadEn_in && !Empty_out) Data_out <= Mem[pNextWordToRead]; end reg pt; //'Data_in' logic: always @ (posedge WClk,negedge Clear_in) begin if(~Clear_in) pt <= 1'b0; else if (WriteEn_in & !Full_out) Mem[pNextWordToWrite] <= Data_in; end //Fifo addresses support logic: //'Next Addresses' enable logic: assign NextWriteAddressEn = WriteEn_in & ~Full_out; assign NextReadAddressEn = ReadEn_in & ~Empty_out; //Addreses (Gray counters) logic:

GrayCounter GrayCounter_pWr (.GrayCount_out(pNextWordToWrite), .Enable_in(NextWriteAddressEn), .Clear_in(Clear_in), .Clk(WClk) ); GrayCounter GrayCounter_pRd (.GrayCount_out(pNextWordToRead), .Enable_in(NextReadAddressEn), .Clear_in(Clear_in), .Clk(RClk) ); //'EqualAddresses' logic: assign EqualAddresses = (pNextWordToWrite[ADDRESS_WIDTH:0] == pNextWordToRea d[ADDRESS_WIDTH:0])?1'b1:1'b0; //'Quadrant selectors' logic: assign Set_Status = (pNextWordToWrite[ADDRESS_WIDTH-1] ~^ pNextWordToRead[AD DRESS_WIDTH]) & (pNextWordToWrite[ADDRESS_WIDTH] ^ pNextWordToRead[ADD RESS_WIDTH-1])?1'b1:1'b0; assign Rst_Status = ((pNextWordToWrite[ADDRESS_WIDTH-1] ^ pNextWordToRead[A DDRESS_WIDTH]) & (pNextWordToWrite[ADDRESS_WIDTH] ~^ pNextWordToRead[ADD RESS_WIDTH-1]))?1'b1:1'b0; //'Status' latch logic: always @ (Set_Status, Rst_Status, Clear_in) //D Latch w/ Asynchronous Clear & Preset. begin if (Rst_Status | !Clear_in) Status = 0; //Going 'Empty'. else if (Set_Status) Status = 1; //Going 'Full'. end //'Full_out' logic for the writing port: assign PresetFull = Status & EqualAddresses; //'Full' Fifo. always @ (posedge WClk, posedge PresetFull) //D Flip-Flop w/ Asynchronous Pr eset. begin // if(~Clear_in) // Full_out <= 1'b0; // else if (PresetFull) Full_out <= 1; else Full_out <= 0; end //'Empty_out' logic for the reading port: assign PresetEmpty = ~Status & EqualAddresses; //'Empty' Fifo. always @ (posedge RClk, posedge PresetEmpty) //D Flip-Flop w/ Asynchronous Preset.

begin if (PresetEmpty) Empty_out <= 1; else Empty_out <= 0; end endmodule GRAY COUNTER MODULE module GrayCounter#(parameter COUNTER_WIDTH =8) (output reg [COUNTER_WIDTH-1:0] GrayCount_out, //'Gray' code count outp ut. input wire input wire input wire Enable_in, //Count enable. Clear_in, //Count reset. Clk);

/////////Internal connections & variables/////// reg [COUNTER_WIDTH-1:0] BinaryCount; /////////Code/////////////////////// always @ (posedge Clk,negedge Clear_in) begin if (~Clear_in) begin BinaryCount <= {COUNTER_WIDTH{1'b 0}} + 1; //Gray count begins @ '1' with GrayCount_out <= {COUNTER_WIDTH{1'b 0}}; // first 'Enable_in'. end else if (Enable_in) begin BinaryCount <= BinaryCount + 1; GrayCount_out <= {BinaryCount[COUNTER_WIDTH-1], BinaryCount[COUNTER_WIDTH-2:0] ^ BinaryCount[COUNT ER_WIDTH-1:1]}; end end endmodule UART module uart( input clk,rst,wr,rd,rx, output tx, input [7:0] din, output [7:0] rdata_out, output txrdy, rxrdy); wire parityerr; wire rxrdy1,txrdy1; assign rxrdy=(rst==1'b1)?(rxrdy1):1'bZ; assign txrdy=(rst==1'b1)?(txrdy1):1'bZ; uart_transmitter u4( .clk(clk), .rst_n(rst), .wr(wr), .data(din), .txrdy(txrdy1), .tx(tx)); uart_receiver u5( .clk(clk), .rst_n(rst), .rd(rd), .rx(rx),

.parityerr(parityerr), .rxrdy(rxrdy1), .det_rx(det_rx), .rd_clk(rd_clk), .flag(flag), .data(rdata_out)); endmodule UART_RECEIVER module uart_receiver(input clk, rst_n, rd, rx, output reg parityerr, output output output output output integer count, countrx; //reg [7:0] temp_rhr; reg rbaud_clk; reg [10:0] rsr; reg [7:0] rhr; // This module is to detect the receiving bit i.e., startbit always@(posedge clk) begin if(rst_n ==1'b0) begin det_rx <=1'b0; // On reset, we assume that, det _rx is not activated. countrx <=1'b0; end else if(rx ==1'b0) begin det_rx <=1'b1; /// If a start bit is received, det_rx control signal is enabled. countrx <= countrx+1; end else if (flag ==1'b1) ///and (countrx < 100)) det_rx <=1'b0; ///If start bit occupies the first bit of RSR i.e., all the bits are received into receiver end ///This module is to keep track of the count, which will be helpfull in generating baud clocks always@(posedge clk) begin if(rst_n ==1'b0) count <= 0; else if((det_rx ==1'b1)&&(count == 9)) count <= 0; else if(det_rx ==1'b1) count <= count+1; else count <= 0; end reg reg reg reg reg rxrdy, det_rx, rd_clk, flag, [7:0]data);

/// This module is for generation of baud clk always@(posedge clk) begin if(rst_n ==1'b0) rbaud_clk <=1'b0; else if(count == 1) rbaud_clk <=1'b1; else rbaud_clk <=1'b0; end //This module is for receiving data from transmitter line to receiver i. e, to RSR always@(posedge rbaud_clk ) begin if(rst_n ==1'b0) rsr <=11'b11111111111; else begin rsr[9:0] <= rsr[10:1]; //Receiving bits bit b y bit rsr[10] <= rx; if(flag ==1'b1) //If start bit reaches the first position, then, it is reset rsr <= 11'b11111111111; end end //This module is to assign value to the flag always@(posedge clk) begin if(rst_n ==1'b0) flag <=1'b0; else begin if(rsr[0] ==1'b0) flag <=1'b1; else if(det_rx ==1'b1) flag <=1'b0; end end ///This module is to receive data from RSR to RHR always@(posedge clk) begin if(rst_n ==1'b0) rhr <= 8'b11111111; else rhr <= rsr[8:1]; end

always@(posedge clk) begin if(rst_n ==1'b0) rd_clk <=1'b0; else begin if(flag ==1'b1) rd_clk <=1'b1; else rd_clk <=1'b0; end end //This module is to shift data from RHR to Dataline with the help of rea d rd signal always@(posedge flag) begin if(rst_n ==1'b0) data <= 8'b0; else data <= rhr; end /// This module is to monitor, whether Receiver is ready or not always@(posedge clk) begin if(rst_n ==1'b0) rxrdy <=1'b0; else if(flag ==1'b1) rxrdy <=1'b1; else if(rd ==1'b1) rxrdy <=1'b0; end ///This module is for parity error always@(posedge clk) begin if(rst_n ==1'b0) parityerr <=1'b0; else if(rd ==1'b1) parityerr <=1'b0; else if (rsr[0] ==1'b0) begin if(((rsr[8] ^ rsr[7] ^ rsr[6] ^ rsr[5] ^ rsr[4] ^ rsr[3] ^ rsr[2] ^ rsr[1]) &(rsr[9])) ==1'b1) parityerr <=1'b0; else parityerr <= 1'b1; end end endmodule UART_TRANSMITTER module uart_transmitter(input clk, rst_n, wr, input[7:0] data, output reg txrdy

, output reg tx); integer count; reg[7:0] tbr; reg [10:0]tsr; reg baud_clk; reg tx_sts; /*This module is to keep tx_status to be 1 or not - i.e, to monitor tx is busy o r not -- tx_sts indicates transmitter status, tx_sts = 1 means transmitter is busy; tx_sts = 0 means transmitter is free*/ always@(posedge clk) begin if(rst_n == 1'b0) tx_sts <= 1'b0; //Transmitter is free else if((wr == 1'b1)&(txrdy ==1'b1)) tx_sts <= 1'b1; //Transmitter is busy else if(txrdy ==1'b1) tx_sts <= 1'b0; //Transmitter is free end ///This module is to load data from dataline to tbr always@(posedge clk) begin if(rst_n ==1'b0) tbr <= 8'b0; else if(txrdy ==1'b1) //If transmitter is ready, the n we need to load data from dataline to data buffer register tbr <= data; end ///This module is to generate baud clock always@(posedge clk) begin if(rst_n ==1'b0) count <= 0; else if((tx_sts== 1'b1)&(count ==9)) count <= 0; else if(tx_sts ==1'b1) count <= count+1; else count<=0; end ///This module is used, to trigger the baud clock always@(posedge clk) begin if(rst_n ==1'b0) baud_clk <=1'b0; else if(count == 1) baud_clk <=1'b1; else baud_clk <=1'b0; end /// This module is for shifing bit by bit always@(posedge clk)

begin if(rst_n ==1'b0) begin tx<=1; tsr <= 10'b0; txrdy <=1'b1; end else if((wr ==1'b1)& (txrdy ==1'b1)) /// and ((tbr(0) or tbr(1) or tbr(2) or tbr(3) or tbr(4) or tbr(5) or tbr(6)) = '1') ///This piece of code is to load data from TBR to TSR(with Start , Stop and Parity) begin tsr[10] <=1'b1; tsr[9] <= (tbr[0]^ tbr[1] ^ tbr[2] ^ tbr[3]^ tbr[4]^ tbr[5] ^ tbr[6]^ tbr[7]); tsr[8:1] <= tbr; tsr[0] <=1'b0; end if((tsr[0] | tsr[1] | tsr[2] | tsr[3] | tsr[4] | tsr[5]| tsr[6]| tsr[7] | tsr[8]| tsr[9] | tsr[10])==1'b0) txrdy <=1'b1; //txrdy is 1, when TSR h as finished sending data. else txrdy <=1'b0; //txrdy is 0, when TSR has data to be sent if((txrdy ==1'b0)&(baud_clk ==1'b1)) begin tx <= tsr[0]; tsr <={1'b0 , tsr[10:1]}; end end endmodule AXI_INTERFACING_UART module axi_interfacing_uart( input Aclk, input Pclk, input Rst, input Awvalid, input [31:0]Awaddr, input Wvalid, input [31:0] Wdata, input [3:0] Wstrb, input Bready, input Arvalid, input [31:0] Araddr, input Rready, output Awready, output Wready, output Bvalid, output Bresp, output Arready, output Rvalid, output [31:0] Rdata, output Rresp, input uart_rx, output uart_tx );

wire[31:0] prdata_from_uart; wire[31:0] paddr_from_apb; wire[31:0] pwdata_from_apb; wire psel_from_apb;

wire penable_from_apb; wire pwrite_from_apb; wire[3:0] pstrb_s; ///Internal Signals reg psel_s; reg pwrite_s; reg penable_s; always@(posedge Pclk) begin if(~Rst) psel_s <= 1'b0; else psel_s <= psel_from_apb; end reg pwrite_s1,pwrite_s2,pwrite_s3,pwrite_s4; always@(posedge Pclk) begin if(~Rst) begin pwrite_s <= 1'b0; pwrite_s1 <= 1'b0; pwrite_s2 <= 1'b0; pwrite_s3 <= 1'b0; pwrite_s4 <= 1'b0; end else if(pwrite_from_apb) begin pwrite_s1 <= 1'b1; pwrite_s2 <= pwrite_s1; pwrite_s3 <= pwrite_s2; pwrite_s <= pwrite_s3; end else begin pwrite_s1 <= 1'b0; pwrite_s2 <= pwrite_s1; pwrite_s3 <= pwrite_s2; pwrite_s <= pwrite_s3; end end reg penable_s1, penable_s2,penable_s3; always@(posedge Pclk) begin if(~Rst) begin penable_s1 <= 1'b0; penable_s2 <= 1'b0; penable_s3 <= 1'b0; penable_s <= 1'b0; end else if(penable_from_apb) begin penable_s1 <= 1'b1; penable_s2 <= penable_s1; penable_s3 <= penable_s2; penable_s <= penable_s3; end else begin

penable_s1 <= 1'b0; penable_s2 <= penable_s1; penable_s3 <= penable_s2; penable_s <= penable_s3; end end apb_bridge_cha axi_2_apb(.Aclk(Aclk), .Pclk(Pclk), .Rst(Rst), .Awvalid(Awvali d), .Awaddr(Awaddr) , .Wvalid(Wvalid) , .Wdata(Wdata), .Wstrb(Wstrb), .Bready(Bready) , .Arvalid(Arvali d), .Araddr(Araddr) , .Rready(Rready) , .Pready(1'b1), .Prdata(prdata_ from_uart), .Pslverr(1'b0), .Awready(Awread y), .Wready(Wready) , .Bvalid(Bvalid) , .Bresp(Bresp), .Arready(Arread y), .Rvalid(Rvalid) , .Rdata(Rdata), .Rresp(Rresp), .Paddr(paddr_fr om_apb), .Psel(psel_from _apb), .Penable(penabl e_from_apb), .Pwrite(pwrite_ from_apb), .Pwdata(pwdata_ from_apb), .Pstrb(pstrb_s) ); apb_uart_top apb_2_uart(.PCLK(Pclk), .PRESETn(Rst), .PSEL(psel_s),

.PENABLE(penable _s), .PWRITE(pwrite_s ), .PWDATA(pwdata_f rom_apb), .PADDR(paddr_fro m_apb), .PRDATA(prdata_f rom_uart), .tx(uart_tx), .rx(uart_rx)

You might also like

- APB protocol on EMACSDocument3 pagesAPB protocol on EMACSviswanath SomanchiNo ratings yet

- Uart VHDDocument5 pagesUart VHDSujatha desikanNo ratings yet

- I2c - Master CodeDocument4 pagesI2c - Master CodeLikourgos LeisosNo ratings yet

- AMBA APB UVM Testbench FrameworkDocument19 pagesAMBA APB UVM Testbench FrameworkDivya srivastavaNo ratings yet

- rs232 RXDocument7 pagesrs232 RXHarish KumarNo ratings yet

- MOD 4-I Simple Computer - Bottom Up ImplementationDocument11 pagesMOD 4-I Simple Computer - Bottom Up ImplementationJohn DoeNo ratings yet

- Lab - VHDL Multiplexer With A ClockDocument3 pagesLab - VHDL Multiplexer With A ClockIulia PopescuNo ratings yet

- VHDL - Practical Example - Designing An UARTDocument18 pagesVHDL - Practical Example - Designing An UARTPrabakaran EllaiyappanNo ratings yet

- Anomie's SPC700Document11 pagesAnomie's SPC700picolo789No ratings yet

- Listing Program: Lampiran 1Document12 pagesListing Program: Lampiran 1Shabrina RaedyNo ratings yet

- Vlsi AssigDocument13 pagesVlsi AssigArham SyedNo ratings yet

- LCD Display Programming GuideDocument39 pagesLCD Display Programming GuidesscetrajivNo ratings yet

- Degree 0 String Words Servo Servo1 : #Include //include The Servo Library IntDocument5 pagesDegree 0 String Words Servo Servo1 : #Include //include The Servo Library IntElver Ramirez LopezNo ratings yet

- UART Communication Design with Transmitter and Receiver ModulesDocument7 pagesUART Communication Design with Transmitter and Receiver ModulesHoàng Long Nguyễn BùiNo ratings yet

- Aimp Verilog - NotesDocument31 pagesAimp Verilog - NotesUllas FarmNo ratings yet

- 12 Bit Spi Adc: Adc Pin Spartan3E FPGA LinesDocument6 pages12 Bit Spi Adc: Adc Pin Spartan3E FPGA LineskaankandemirrrNo ratings yet

- Interfacing A VOR/LOC/Glideslope Indicator byDocument17 pagesInterfacing A VOR/LOC/Glideslope Indicator byeumesmo222No ratings yet

- AS Meped Spider Robot - 3Document12 pagesAS Meped Spider Robot - 3Aqeel AhmedNo ratings yet

- CCNP ROUTE Skills Based Assessment NotesDocument4 pagesCCNP ROUTE Skills Based Assessment NotesRyu WatanabeNo ratings yet

- Cisco IOS SPAN and RSPANDocument16 pagesCisco IOS SPAN and RSPANKiki NetNo ratings yet

- Arduino - Auto Range Analog InputDocument7 pagesArduino - Auto Range Analog InputbarbosiNo ratings yet

- Bus ArbiterDocument4 pagesBus ArbiterHugo TorresNo ratings yet

- VhdlcodesDocument9 pagesVhdlcodesPrashant Singh JadonNo ratings yet

- Lab 5 Firna FrilanisaDocument18 pagesLab 5 Firna FrilanisaFirna FrilanisaNo ratings yet

- NoteDocument1 pageNotesyahmiaminin99No ratings yet

- Spi Slave v10Document6 pagesSpi Slave v10Luis AuquillaNo ratings yet

- UARTDocument19 pagesUARTErick LoolNo ratings yet

- PrecedenceDocument5 pagesPrecedenceAlok kumarNo ratings yet

- ParcialesteDocument5 pagesParcialesteJeffersonNo ratings yet

- Name: Nguyen Nhat Duy ID: EEEEIU18025 Homework 5 Embedded Real-Time System Master CodeDocument6 pagesName: Nguyen Nhat Duy ID: EEEEIU18025 Homework 5 Embedded Real-Time System Master CodeNhất Duy NguyễnNo ratings yet

- Design NeedsDocument10 pagesDesign NeedsMekonnen GetnetNo ratings yet

- Arduino - Serial Peripheral InterfaceDocument3 pagesArduino - Serial Peripheral Interfacewillingcoder.billionaireNo ratings yet

- Hexapod Master Slave CommunicationDocument22 pagesHexapod Master Slave CommunicationDigvijay MaheshwariNo ratings yet

- Access Point Ap1 Access Point Bss (Modo Infraestructura) Autenticacion AbiertaDocument24 pagesAccess Point Ap1 Access Point Bss (Modo Infraestructura) Autenticacion AbiertapcdeviceNo ratings yet

- Drone Obstacle Avoidance CodeDocument5 pagesDrone Obstacle Avoidance CodeAjay YadavNo ratings yet

- Drone Obstacle Avoidance Code-2Document5 pagesDrone Obstacle Avoidance Code-2Ajay YadavNo ratings yet

- DC Motor Interface With Robot Operating System ROSDocument30 pagesDC Motor Interface With Robot Operating System ROSMuhammad SaleemNo ratings yet

- Configuring VLANs and interfaces on an Allied Telesis switchDocument32 pagesConfiguring VLANs and interfaces on an Allied Telesis switchangelmauriciormzNo ratings yet

- Raspberry Pi and Arduino Connected Using I2C - Oscar LiangDocument13 pagesRaspberry Pi and Arduino Connected Using I2C - Oscar LiangStellaEstelNo ratings yet

- CodingDocument43 pagesCodingbhawnaNo ratings yet

- Si4703 - Example Code Si4703 FM TunerDocument10 pagesSi4703 - Example Code Si4703 FM TunerHotel WijayaNo ratings yet

- SPI ModuleDocument5 pagesSPI Moduleleduclebk93No ratings yet

- Pico AluDocument2 pagesPico Aluapi-547507672No ratings yet

- ADT AVL Tree V3Document4 pagesADT AVL Tree V3RishiGuptaNo ratings yet

- VHDL Codes for Flip Flops, Counters, MuxesDocument9 pagesVHDL Codes for Flip Flops, Counters, MuxesYogesh KhollamNo ratings yet

- Moore FSM sequence detector verificationDocument13 pagesMoore FSM sequence detector verificationSanjanaNo ratings yet

- D Micro BoludaDocument27 pagesD Micro BoludaJose Alberto Damian QuirozNo ratings yet

- Enhanced Dual Axis ProgramDocument12 pagesEnhanced Dual Axis ProgramLENKAI—254No ratings yet

- VHDL CodesDocument6 pagesVHDL Codesapi-27099960100% (4)

- Full AdderDocument2 pagesFull AdderAkshay KhaladkarNo ratings yet

- SwitchingDocument3 pagesSwitchingzrjeebonNo ratings yet

- AHB AMBA Protocol - Verification CodeDocument39 pagesAHB AMBA Protocol - Verification CodeMonik Monaa100% (1)

- XBee relay code for outlets and LEDsDocument3 pagesXBee relay code for outlets and LEDsJonathanNo ratings yet

- Apb ProtocolDocument6 pagesApb ProtocolSUDHEER SNo ratings yet

- Function: TestbenchDocument27 pagesFunction: TestbenchY AmulyaNo ratings yet

- Assignment-3: Name: Humna Zaheer Arid No 19-Arid-1191Document9 pagesAssignment-3: Name: Humna Zaheer Arid No 19-Arid-1191HumnaZaheer muhmmadzaheerNo ratings yet

- 3 Flip-Flops: 3.1 RS LatchesDocument28 pages3 Flip-Flops: 3.1 RS LatchesMiguel Valera MartinezNo ratings yet

- STATISTICAL COUNTERS REPORTDocument6 pagesSTATISTICAL COUNTERS REPORTEngr_Faiz_Akram100% (1)

- Userexit Userxits Allow Us To Add Our Own Functionality To SAP Standard ProgramDocument4 pagesUserexit Userxits Allow Us To Add Our Own Functionality To SAP Standard ProgramSreelu123No ratings yet

- Book 1Document1 pageBook 1Vikas ZurmureNo ratings yet

- LSMW FinalDocument1 pageLSMW FinalVikas ZurmureNo ratings yet

- Mass Upload of Master DataDocument31 pagesMass Upload of Master DataVikas Zurmure100% (4)

- Sap R3 SD Overview SisDocument19 pagesSap R3 SD Overview SisVikas ZurmureNo ratings yet

- FI MM SDintegration PDFDocument25 pagesFI MM SDintegration PDFGopa Kambagiri SwamyNo ratings yet

- FI&SDIntegration (1) 20120529132458.211 XDocument66 pagesFI&SDIntegration (1) 20120529132458.211 XVikas ZurmureNo ratings yet

- SD Process FlowDocument9 pagesSD Process FlowVikas ZurmureNo ratings yet

- Sap SD Advanced Pricing 120604011043 Phpapp02Document59 pagesSap SD Advanced Pricing 120604011043 Phpapp02Vikas Zurmure100% (1)

- SD Process FlowDocument9 pagesSD Process FlowVikas ZurmureNo ratings yet

- MagnetDocument1 pageMagnetVikas ZurmureNo ratings yet

- ConsignmentDocument3 pagesConsignmentVikas ZurmureNo ratings yet

- Rebate NotesDocument2 pagesRebate NotesVikas ZurmureNo ratings yet

- SD Question AnswersDocument37 pagesSD Question Answersanon-850305100% (1)

- Adobe ProDocument1 pageAdobe ProVikas ZurmureNo ratings yet

- Enterprise StructureDocument17 pagesEnterprise StructureVikas ZurmureNo ratings yet

- Enterprise StructureDocument17 pagesEnterprise StructureVikas ZurmureNo ratings yet

- An Introduction To SAPDocument1 pageAn Introduction To SAPVikas ZurmureNo ratings yet

- Expresscache x64 100Document2 pagesExpresscache x64 100Vikas ZurmureNo ratings yet

- FWSB 20 enDocument3 pagesFWSB 20 enVikas ZurmureNo ratings yet

- Sap SD ScenariosDocument15 pagesSap SD ScenariosVikas Zurmure67% (3)

- Sad SD PricingDocument1 pageSad SD PricingVikas ZurmureNo ratings yet

- Enterprise StructureDocument2 pagesEnterprise StructureVikas ZurmureNo ratings yet

- TSCMDocument1 pageTSCMVikas ZurmureNo ratings yet

- SDDocument1 pageSDVikas ZurmureNo ratings yet

- TSCM 12Document1 pageTSCM 12Vikas ZurmureNo ratings yet

- Enterprise StructureDocument2 pagesEnterprise StructureVikas ZurmureNo ratings yet

- Enterprise StructureDocument2 pagesEnterprise StructureVikas ZurmureNo ratings yet

- Sad SD PricingDocument1 pageSad SD PricingVikas ZurmureNo ratings yet

- 28901cpt Fa SM Cp7 Part2Document0 pages28901cpt Fa SM Cp7 Part2Vikas ZurmureNo ratings yet

- IOKit LibDocument30 pagesIOKit LibBrayan VillaNo ratings yet

- Distributed Operating System Concepts and DesignDocument2 pagesDistributed Operating System Concepts and DesignNirali DutiyaNo ratings yet

- GFK 2460 CDocument259 pagesGFK 2460 CKunal AvhadNo ratings yet

- Networking Essentials Exam NotesDocument5 pagesNetworking Essentials Exam NotesKevin H PhamNo ratings yet

- ASG Software Compatibility Guide: For ASG-Time Navigator 4.3 Enterprise EditionDocument42 pagesASG Software Compatibility Guide: For ASG-Time Navigator 4.3 Enterprise EditionFabrice PLATELNo ratings yet

- Scan Results.150608-1026Document5 pagesScan Results.150608-1026Victor EmanuelNo ratings yet

- How To Install Encs On Furuno Ecdis-Step by Step GuideDocument22 pagesHow To Install Encs On Furuno Ecdis-Step by Step GuidePanagiotis Mouzenidis100% (1)

- Versa FlexVNF Release Notes 20.1.0Document6 pagesVersa FlexVNF Release Notes 20.1.0bike9915No ratings yet

- Fax 283Document3 pagesFax 283gary476No ratings yet

- Booth MultiplierDocument5 pagesBooth Multiplierrahul rNo ratings yet

- Css-Grade 11 - Finals-Module - Lesson 4Document7 pagesCss-Grade 11 - Finals-Module - Lesson 4Cathleen BethNo ratings yet

- Toshiba Tecra M9 and Tecra A9: Two New Laptop With Santa Rosa UnveiledDocument11 pagesToshiba Tecra M9 and Tecra A9: Two New Laptop With Santa Rosa UnveiledocchityaNo ratings yet

- IFIX Getting StartedDocument75 pagesIFIX Getting StartedRicardo AlvaradoNo ratings yet

- Manual-AN5516-04 FiberHomeDocument101 pagesManual-AN5516-04 FiberHomeSergio SanchezNo ratings yet

- UNIT-1 Embedded Computing Two Marks: 2. in What Ways CISC and RISC Processors Differ?Document23 pagesUNIT-1 Embedded Computing Two Marks: 2. in What Ways CISC and RISC Processors Differ?rajeshkumardhandapanNo ratings yet

- Connect GNS3 To The Internet (Local Server)Document19 pagesConnect GNS3 To The Internet (Local Server)Manuel GomesNo ratings yet

- Complements (Lec4)Document13 pagesComplements (Lec4)hatemalshandoli1No ratings yet

- NGFW in FW/VPN Role and Clustering TechnologyDocument37 pagesNGFW in FW/VPN Role and Clustering TechnologyomarptcNo ratings yet

- lastCleanException 20210817070418Document156 pageslastCleanException 20210817070418dannyrachmad123No ratings yet

- Note On Operating System and KernelDocument3 pagesNote On Operating System and Kernelobinna benjaminNo ratings yet

- OBIA 12c Implementation PlanningDocument5 pagesOBIA 12c Implementation PlanningGCNo ratings yet

- Akka.NET dispatchers guide under 40 charsDocument4 pagesAkka.NET dispatchers guide under 40 charsCristian RodriguezNo ratings yet

- AT-S114 V2.0.2 (1.00.035) AT-GS950/16 Gigabit Ethernet Smart Switch Software Release NotesDocument4 pagesAT-S114 V2.0.2 (1.00.035) AT-GS950/16 Gigabit Ethernet Smart Switch Software Release Notesstefan.mirceaNo ratings yet

- HP 3PAR StoreServ 7000 Storage Service GuideDownload 2Document64 pagesHP 3PAR StoreServ 7000 Storage Service GuideDownload 2amirbahramNo ratings yet

- HCIA-Routing and Switching V2.2 Intermediate Lab GuideDocument172 pagesHCIA-Routing and Switching V2.2 Intermediate Lab Guidebayron100% (1)

- QA Hardware Development - 310519Document5 pagesQA Hardware Development - 310519Joker JrNo ratings yet

- Test Bank For Network Guide To Networks 8th Edition by WestDocument20 pagesTest Bank For Network Guide To Networks 8th Edition by Westeirlysphoebe0qf67No ratings yet

- CYB 220 Project One Virtual Systems and Network Concept Brief Abu AlamDocument9 pagesCYB 220 Project One Virtual Systems and Network Concept Brief Abu AlamAbu AlamNo ratings yet

- DsPIC33F Family Reference Manual AllDocument4 pagesDsPIC33F Family Reference Manual AllVlad MizeffNo ratings yet

- Revised Student Guide Quick HashDocument4 pagesRevised Student Guide Quick HashsparklelabjewelleryNo ratings yet