Professional Documents

Culture Documents

CH 10

CH 10

Uploaded by

chittajitsarkarsterOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

CH 10

CH 10

Uploaded by

chittajitsarkarsterCopyright:

Available Formats

Topics 2102440 Introduction to Microprocessors Chapter 10 8253 Programmable Interval Timer/Counter

Suree Pumrin, Ph.D.

1

2102440 Introduction to Microprocessors

Interfacing with 8086/8088 Programming Mode

8253/54 Timer (I)

The 8253/54 Programmable interval timer is used to generate a lower frequency for various uses, e.g., the beep sound CS 0 0 0 0 1 A1 0 0 1 1 x A0 0 1 0 1 x Port Counter 0 Counter 1 Counter 2 Control register 8253/54 is not selected

8253/54 Timer (II)

There are three counters. The input frequency can be divided from 1 to 65536. Input clock frequency is 00-2 MHz for 8253, up to 8 MHz for 8254, and up to 10 MHz for 82548254-2. Shape of the output frequency:

z z z

SquareSquare-wave OneOne-shot SquareSquare-wave with various duty cycles.

Gate is used to enable (High) or disable (Low) the counter. Bidirectional bus D0D0-D7 is connected to D0D0-D7 of the system bus.

2102440 Introduction to Microprocessors

2102440 Introduction to Microprocessors

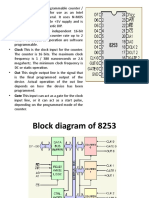

Architecture of the 8253/54

8253/54 Control Word Format

2102440 Introduction to Microprocessors

2102440 Introduction to Microprocessors

Control Word (I)

Control Word (II)

D0

z

Binary number divisor 00000000-FFFFH

Divisor = 65536 if the counter is loaded with 0 for both the low and the high bytes.

D4 and D5 for RL0 and RL1

z

RL0 and RL1 indicate the size of the divisor.

Read/write the least significant byte (LSB) only Read/write the most significant byte (MSB) only Read/write the LSB first then followed by the MSB

BCD divisor 00000000-9999H

Divisor = 10000 if the counter is loaded with 0 for both the low and the high bytes.

z

D1, D2, and D3: Mode selection

z z z z z z

Mode 0: Interrupt on terminal count Mode 1: Programmable oneone-shot Mode 2: Rate generator Mode 3: Square wave rate generator Mode 4: Software triggered strobe Mode 5: Hardware triggered strobe

We can write the value of the divisor into 8253/54 timer and read the contents of the counter at any time.

D6 and D7 are used to select which of the three counters: counter 0 (00), counter 1 (01), and counter 2 (10).

2102440 Introduction to Microprocessors

2102440 Introduction to Microprocessors

Mode 0: Interrupt on terminal count

Mode 1: Programmable one-shot

It is used to generate an interrupt to the microprocessor after a certain interval of time. The output is initially low after the mode is set. The output remains remains LOW after the count value is loaded in the counter. The process of decrementing the counter continues till the terminal terminal count is reached, i.e., the count become zero and the output goes HIGH. The The output remains high until it reloads a new mode of operation or new count. count. The GATE signal is high for normal counting. When GATE goes low counting is terminated and the current count is latched till the GATE goes high high again.

2102440 Introduction to Microprocessors

The 8253/54 can be used as a monostable multivibrator. multivibrator. The gate input is used as trigger input in this mode. Normally, the output remains high until the count is loaded and a trigger is applied. The duration of the quasistable of the monostable multivibrator is decided by the count loaded in the count register.

9

2102440 Introduction to Microprocessors

10

Mode 2: Rate generator

Mode 3: Square wave rate generator

Divide by N counter. The output is normally high after initialization. If N is loaded as the count value, after N pulses, the output becomes low for one clock cycle. Whenever the count becomes zero another low pulse is generated at the output.

2102440 Introduction to Microprocessors

It is similar to mode 2. When, the count N loaded is EVEN, half of the count will be high and half of the count will be low. When, the count N loaded is ODD, the first clock pulse decrements it by 1. Then half of the remaining count will be high and half of the remaining count will be low.

11

2102440 Introduction to Microprocessors

12

Mode 4: Software triggered strobe

Mode 5: Hardware triggered strobe

After the mode is set, the output goes high. The counter automatically begins to decrement (count down) one clock clock pulse after it is loaded with the initial value through software. software. When the GATE signal goes low the count is latched. On the terminal count, the output goes low for one clock cycle, and then again goes high. This low pulse can be used as a strobe.

2102440 Introduction to Microprocessors

This mode generates a strobe in response to an externally generated generated signal. It is similar to mode 4 except that the counting is initiated by a signal at the gate input, i.e., it is hardware triggered instead of software triggered. triggered. After it is initialized, the output goes high. The counter starts counting after the rising edge of the trigger input (GATE). When the terminal count is reached, the output goes low for one clock cycle.

2102440 Introduction to Microprocessors

13

14

Example 1

Example 2

Pin CS of a given 8253/54 is activated by binary address A7A7-A2 = 100101.

z

Find the port addresses assigned to this 8253/54.

Counter 0 Port address = 1001 01 00 = 94H Counter 1 Port address = 1001 01 01 = 95H Counter 2 Port address = 1001 01 10 = 96H Control register Port address = 1001 01 11 = 97H

Use the port addresses in Ex. 1 to program counter 2 for binary count of mode 3 (square wave) to divide CLK2 by number C26AH and find the frequency of OUT2 if CLK2 = 1.8 MHz.

z

Find the configuration for this 8253/54 if the control register is programmed as follows.

MOV AL, 00110110 OUT 97H, AL D7D7-D6 = 00 select counter 0 D5D5-D4 = 11 the low byte read/write is followed by the high byte. D3D3-D1 = 011 select mode 3 (square wave) D0 = 0 select the binary counting

2102440 Introduction to Microprocessors

The control word = 10110110 MOV AL, B6H ; counter 2, mode 3, binary OUT 97H, AL ; send it to control register MOV AX,C26AH ; load the divisor OUT 96H, AL ; send the low byte to counter 2 MOV AL, AH OUT 96H, AL ; send the high byte to counter 2 The output frequency for OUT2 = 1.8 MHz is divided by C26AH (49770 D). OUT 2 frequency is a square wave of 36 Hz.

16

15

2102440 Introduction to Microprocessors

Example 3

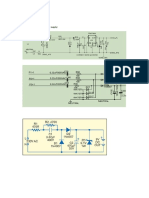

8253 Chip Connections in the PC

Using the port address in Ex.1, show the programming of counter 1 to divide CLK1 by 10,000, producing the mode 3 square wave. Use the BCD option in the control byte.

MOV AL, 77H OUT 97H, AL SUB AL, AL OUT 95H, AL OUT 95H, AL ; counter 1, mode 3, BCD ; send it to control register ; AL = 0 load the divisor for 10,000 ; send the low byte ; send the high byte

2102440 Introduction to Microprocessors

17

2102440 Introduction to Microprocessors

18

You might also like

- Lecture 7Document48 pagesLecture 7tecleador1No ratings yet

- By K. Vijay Kumar Assistant Professor Dept. of ECEDocument31 pagesBy K. Vijay Kumar Assistant Professor Dept. of ECEsignjpcoeNo ratings yet

- Unit III 8254Document29 pagesUnit III 8254Sahil SinghNo ratings yet

- PIT: Programmable Interval Timer: Introduction To 8253/8254Document34 pagesPIT: Programmable Interval Timer: Introduction To 8253/8254Sayan GhoshNo ratings yet

- 8254 AnniDocument43 pages8254 AnniCSE7 NDUBNo ratings yet

- 8253Document17 pages8253Parv SharmaNo ratings yet

- 8254 Programmable Interval TimerDocument4 pages8254 Programmable Interval Timerapi-26100966100% (1)

- Interfacing With TimerDocument12 pagesInterfacing With TimerSunil AcharyaNo ratings yet

- All-In-One PLC: KV Nano Application Guide Vol. 7Document12 pagesAll-In-One PLC: KV Nano Application Guide Vol. 7Phạm Thế HiệpNo ratings yet

- Unit 4 - Microprocessor & Its Application - WWW - Rgpvnotes.inDocument9 pagesUnit 4 - Microprocessor & Its Application - WWW - Rgpvnotes.inJayesh JoshiNo ratings yet

- Rangkaian Jam Digital MikrokontrolerDocument26 pagesRangkaian Jam Digital MikrokontrolerRahmad van BoschNo ratings yet

- Programmable Interval Timer - 8254Document27 pagesProgrammable Interval Timer - 8254ShazidNo ratings yet

- 8254-Programmable Interval TimerDocument21 pages8254-Programmable Interval TimerSanthosh SandyNo ratings yet

- The 8253Document29 pagesThe 8253Soumya Ranjan PandaNo ratings yet

- 8254 MICROPROCESSOR (Driste)Document13 pages8254 MICROPROCESSOR (Driste)CSE7 NDUBNo ratings yet

- Digital ApplicationsDocument14 pagesDigital Applications22e132No ratings yet

- TOPCNC TC55V Instruction ManualDocument13 pagesTOPCNC TC55V Instruction Manualanhthong3kNo ratings yet

- DATA ACQUISTION-: It Is The Process of Sampling The Signals That Measure Real WorldDocument6 pagesDATA ACQUISTION-: It Is The Process of Sampling The Signals That Measure Real WorldSV MNo ratings yet

- 2003apr25 Id MPR AnDocument12 pages2003apr25 Id MPR AnMohamedSalahNo ratings yet

- Microcontrollers LabDocument19 pagesMicrocontrollers LabAMARNATHNAIDU77No ratings yet

- Clock This Is The Clock Input For The CounterDocument22 pagesClock This Is The Clock Input For The CounterSri NikethanNo ratings yet

- 8155 Is An Integrated RamDocument22 pages8155 Is An Integrated RamVipan SharmaNo ratings yet

- Lecture Slide 4Document48 pagesLecture Slide 4Sunil SahooNo ratings yet

- Exp 12) Prbs Generator and Shift RegisterDocument5 pagesExp 12) Prbs Generator and Shift RegisterMani BharathiNo ratings yet

- Programmable Interval Timer: T.Shakeel, Lovely Professional UniversityDocument25 pagesProgrammable Interval Timer: T.Shakeel, Lovely Professional UniversityFaiz RahmanNo ratings yet

- 8254 Micro ProcessorDocument16 pages8254 Micro Processornishukaushal100% (2)

- TOPCNC TC55V Instruction ManualDocument13 pagesTOPCNC TC55V Instruction ManualLuis Otavio TrindadeNo ratings yet

- Mpa Question Bank1Document16 pagesMpa Question Bank1Sharon FrancisNo ratings yet

- 174-183-ReportDocument32 pages174-183-ReportashishNo ratings yet

- TTL Digital ClockDocument5 pagesTTL Digital Clockyampire100% (1)

- New TOPCNC TC55V Instruction ManualDocument14 pagesNew TOPCNC TC55V Instruction ManualCarlos SerranoNo ratings yet

- TOPCNC TC55V Instruction Manual: TOPCNC Automation Technology Co., Ltd. Felicia JiaDocument13 pagesTOPCNC TC55V Instruction Manual: TOPCNC Automation Technology Co., Ltd. Felicia Jiaanhthong3kNo ratings yet

- Experiment 11 - UpdatedDocument2 pagesExperiment 11 - UpdatedVivek Varma IndukuriNo ratings yet

- The 8253 Data Sheets Are List in The Following: Functional DescriptionDocument13 pagesThe 8253 Data Sheets Are List in The Following: Functional Descriptionharijai26No ratings yet

- Timer Counter ArduinoDocument8 pagesTimer Counter ArduinoKietDangNo ratings yet

- Segment 7: Rogrammable Nterval ImerDocument36 pagesSegment 7: Rogrammable Nterval ImerDOUNIANo ratings yet

- Course On MicrocontrollersDocument115 pagesCourse On MicrocontrollersKorom ChandNo ratings yet

- Siren Project With Pic MicrocontrollerDocument12 pagesSiren Project With Pic MicrocontrollerMatthew Hunter100% (1)

- Adc0808 and 8253Document35 pagesAdc0808 and 8253Avanish NiranjanNo ratings yet

- Adc0808 and 8253Document35 pagesAdc0808 and 8253Avanish NiranjanNo ratings yet

- Motor ControlDocument5 pagesMotor ControlnooriusefNo ratings yet

- Chapter 5.2interfacing To 8086Document33 pagesChapter 5.2interfacing To 8086cudarunNo ratings yet

- Interfacing Techniques: The 8254 Programmable Interval Timer (PIT)Document11 pagesInterfacing Techniques: The 8254 Programmable Interval Timer (PIT)yaseen jobaNo ratings yet

- 4-Modes of 8253 and Control Word-12-09-2022Document7 pages4-Modes of 8253 and Control Word-12-09-2022Arnav BansalNo ratings yet

- M4 Micro OneNoteDocument6 pagesM4 Micro OneNoteAryan RaiNo ratings yet

- MP Module 4 8254Document15 pagesMP Module 4 8254Lekshmi SasidharanNo ratings yet

- MP3 Player FPGA ReportDocument11 pagesMP3 Player FPGA ReportDang DuyNo ratings yet

- Input Output Operations Using AVR Studio: Atmega-16/32 Pin DescriptionDocument26 pagesInput Output Operations Using AVR Studio: Atmega-16/32 Pin Descriptionbala8350No ratings yet

- 8253 PitDocument23 pages8253 PitDharani ChinnaNo ratings yet

- 3 - Counters PPT (DLP-2021-22)Document16 pages3 - Counters PPT (DLP-2021-22)SohneaNo ratings yet

- 05 AVR Timer-Counter AVRDocument95 pages05 AVR Timer-Counter AVRPriscillaNo ratings yet

- DSEP100 Installation InstructionsDocument2 pagesDSEP100 Installation InstructionsedgarcooNo ratings yet

- 4 Experiment 4 Interrupt and I/O InterfacingDocument17 pages4 Experiment 4 Interrupt and I/O InterfacingSuhas NipaneNo ratings yet

- Digital Pulse Counter - Two Digits: DescriptionDocument7 pagesDigital Pulse Counter - Two Digits: DescriptionAsgher KhattakNo ratings yet

- Beginning Digital Electronics through ProjectsFrom EverandBeginning Digital Electronics through ProjectsRating: 5 out of 5 stars5/5 (1)

- The PIC Microcontroller: Your Personal Introductory CourseFrom EverandThe PIC Microcontroller: Your Personal Introductory CourseRating: 1 out of 5 stars1/5 (2)

- Projects With Microcontrollers And PICCFrom EverandProjects With Microcontrollers And PICCRating: 5 out of 5 stars5/5 (1)

- 3.5B Enumeration: Department of CSEDocument9 pages3.5B Enumeration: Department of CSEKeerthi Vasan SNo ratings yet

- 1.6 FunctionDocument49 pages1.6 FunctionKeerthi Vasan SNo ratings yet

- Candle Sticks: Support Level HammerDocument8 pagesCandle Sticks: Support Level HammerKeerthi Vasan SNo ratings yet

- 1.4 SelectionDocument51 pages1.4 SelectionKeerthi Vasan SNo ratings yet

- Algorithms 3: CTPS 2018Document16 pagesAlgorithms 3: CTPS 2018Keerthi Vasan SNo ratings yet

- 1.1 Introduction To CDocument57 pages1.1 Introduction To CKeerthi Vasan SNo ratings yet

- 3.2 String FunctionsDocument20 pages3.2 String FunctionsKeerthi Vasan SNo ratings yet

- Using If ElseDocument5 pagesUsing If ElseKeerthi Vasan SNo ratings yet

- Three-Phase Asymmetry and Phase-Sequence Phase-Loss Relay: K8Ab-PaDocument7 pagesThree-Phase Asymmetry and Phase-Sequence Phase-Loss Relay: K8Ab-PaKeerthi Vasan SNo ratings yet

- RM17TE00 DATASHEET NG en-GBDocument6 pagesRM17TE00 DATASHEET NG en-GBKeerthi Vasan SNo ratings yet

- Three-Phase Asymmetry and Phase-Sequence Phase-Loss Relay: K8Ab-PaDocument12 pagesThree-Phase Asymmetry and Phase-Sequence Phase-Loss Relay: K8Ab-PaKeerthi Vasan SNo ratings yet

- 3.3 StructuresDocument24 pages3.3 StructuresKeerthi Vasan SNo ratings yet

- 1.7 RecursionDocument23 pages1.7 RecursionKeerthi Vasan SNo ratings yet

- 3.7 Command-Line ArgumentsDocument18 pages3.7 Command-Line ArgumentsKeerthi Vasan SNo ratings yet

- Transformerless R-C Power SupplyDocument4 pagesTransformerless R-C Power SupplyKeerthi Vasan SNo ratings yet

- Economical Test of Internal Adc in Embedded Systems: Josef Vedral, Jakub Svatoš, Pavel FexaDocument4 pagesEconomical Test of Internal Adc in Embedded Systems: Josef Vedral, Jakub Svatoš, Pavel FexaKeerthi Vasan SNo ratings yet

- AC Current Measurements Using Hall-Effect Sensors - Engineer Experiences PDFDocument10 pagesAC Current Measurements Using Hall-Effect Sensors - Engineer Experiences PDFKeerthi Vasan SNo ratings yet

- Bitwise Operations in Embedded Programming - Detail ExplanationDocument6 pagesBitwise Operations in Embedded Programming - Detail ExplanationKeerthi Vasan SNo ratings yet

- V-Guard Industries Limited Code of Conduct For Directors and Senior ManagementDocument4 pagesV-Guard Industries Limited Code of Conduct For Directors and Senior ManagementKeerthi Vasan SNo ratings yet

- Valid Documents List PDFDocument2 pagesValid Documents List PDFAnoop DubeyNo ratings yet

- Interfacing Stepper Motor With 8051 Using Keil C - AT89C51Document10 pagesInterfacing Stepper Motor With 8051 Using Keil C - AT89C51Keerthi Vasan SNo ratings yet

- Market Radar: Traders' CornerDocument5 pagesMarket Radar: Traders' CornerKeerthi Vasan SNo ratings yet