Professional Documents

Culture Documents

Experiment 11 - Updated

Uploaded by

Vivek Varma IndukuriOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Experiment 11 - Updated

Uploaded by

Vivek Varma IndukuriCopyright:

Available Formats

11.

Interfacing Program Of Timer [8254] Using Microcontroller

11.1 Introduction:

To interface a programmable timer interface with a 8086 trainer kit and to operate it

in various modes.

11.2 Hardware requirement

The 8051 Microprocessor kit, Programmable Timer interface add on card,

interface cable, Power Supply.

11.3 Theory

The main features of 8253 are as follows:

1. Three independent 16 bit counters

2. Input clock

3. Programmable counter modes

The clk0 can be connected either to the pclk or to the debounce circuit. Using the debounce

circuit we can generate a pulse and clock the timer. Similarly clock1 can be connected to pclk

and clock2 can be connected to either pclk or out0. In a microprocessor based application,

interrupting the processor after a time delay is essential which is achieved using a timer.

11.3.1 Mode 0 – Interrupt on terminal count

The output will be initially low after mode set operation. After loading the counter,

the output will remain low while counting and on terminal count the output will become high,

until reloaded again. Channel 0 is in mode 0 and the program is executed. Output is observed

through a CRO.

11.3.2 Mode 1 – Programmable one shot

After loading the counter, the output will remain low following the rising edge of the

gate input. The output will go high on the terminal count. It is retriggerable, hence the output

will remain low for the full count after the rising edge of the gate input.

Execute the program, give the clock pulses through the debounce logic and observe the

output at the CRO.

11.3.3 Mode 2 – Rate generator

It is a divide by N counter. The output will be low for for one period of the clock input.

The period from one output pulse to the next equals the number of input counts in the count

register. In the CRO observe the input at channel 1 and the output at out1.

11.3.4 Mode 3 – Square Wave Generator

It is similar to mode 2 except that the output will remain high for one half of the count

and go low for the other half for even number count. If the count is odd, the output will

remain high for (count-1)/2 counts.

11.3.5 Mode 4 – Software triggered strobe

In this method , the output is high after mode is set and also during counting. On terminal

count , the output will go low for one clock period and becomes high again. This mode is

used for interrupt generation.

SQUARE WAVE GENERATION MODE

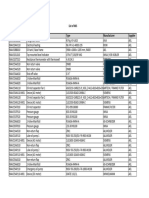

ADDRESS LABEL MNEMONICS OPCODE COMMENT

MOV DPTR,#FFCE

MOV A,#36

MOVX@DPTR,A

MOV A,#0A

MOV DPTR,#FFC8

MOVX@DPTR,A

MOV A,#00

MOVX @DPTR,A

HERE: SJMP HERE

Pre Lab:

1. Write the need of 8251 timer.

2. Explain the control word format of 8254.

3. Define Read back operation in 8254.

Post Lab:

1. Design a programmable timer using 8254 and 8086. Interface 8254 at an address

0040H for counter 0 and write the following ALPs. The 8086 and 8254 run at 6MHz

and 1.5MHz respectively.

(i) To generate a square wave of period 1ms.

(ii) To interrupt the processor after 10ms.

You might also like

- Hoist and Crane SafeyDocument60 pagesHoist and Crane SafeysergioNo ratings yet

- Cub Cadet 19hp Enforcer 44 21hp Enforcer 48 23hp Enforcer 54Document32 pagesCub Cadet 19hp Enforcer 44 21hp Enforcer 48 23hp Enforcer 54Rush WilliamsNo ratings yet

- Digital Signal Processing: Instant AccessFrom EverandDigital Signal Processing: Instant AccessRating: 3.5 out of 5 stars3.5/5 (2)

- Projects With Microcontrollers And PICCFrom EverandProjects With Microcontrollers And PICCRating: 5 out of 5 stars5/5 (1)

- SIMRAD GC80/85 Expanded: Instruction ManualDocument120 pagesSIMRAD GC80/85 Expanded: Instruction ManualnzmrsNo ratings yet

- I44v3 Parts Manual 20-09-17 PDFDocument167 pagesI44v3 Parts Manual 20-09-17 PDFTatyana100% (1)

- 2391 Revision 2000 V6.0Document118 pages2391 Revision 2000 V6.0mpendleton100% (1)

- Figure 1. Schematic - Ev-100Zx SCR Control For Traction MotorDocument43 pagesFigure 1. Schematic - Ev-100Zx SCR Control For Traction MotorMario AguirreNo ratings yet

- 8051 Microcontroller (2 Marks - Question Bank)Document13 pages8051 Microcontroller (2 Marks - Question Bank)Dr. N.Shanmugasundaram97% (34)

- 5-Machine Cycle & Delay Calculations-23-12-2022Document17 pages5-Machine Cycle & Delay Calculations-23-12-2022BRO CUBIESNo ratings yet

- Practical 2 PicDocument7 pagesPractical 2 PicPrerna Sanjivan MhatreNo ratings yet

- Mpa Question Bank1Document16 pagesMpa Question Bank1Sharon FrancisNo ratings yet

- Microcontroller and Risc ArchitectureDocument18 pagesMicrocontroller and Risc ArchitecturesridharanchandranNo ratings yet

- IV 8051manua PDFDocument56 pagesIV 8051manua PDFIrfan KhanNo ratings yet

- Microcontroller Lab ManualDocument38 pagesMicrocontroller Lab Manualharshitha100% (1)

- Updated Emb Sys & Comm Lab ManualDocument25 pagesUpdated Emb Sys & Comm Lab Manualkuzzzdmh3bNo ratings yet

- Microcontroller Lab ManualDocument38 pagesMicrocontroller Lab ManualAkash Kumar58% (12)

- Microcontroler LabmanualDocument47 pagesMicrocontroler LabmanualMonu SNo ratings yet

- 354 39 Solutions Instructor Manual 11 Hardware Features 8051 Chapter 11Document8 pages354 39 Solutions Instructor Manual 11 Hardware Features 8051 Chapter 11Saravanan JayabalanNo ratings yet

- 2marks MC FullDocument15 pages2marks MC FullSid VibhorNo ratings yet

- Micro Controllers Lab Final - DSCEDocument37 pagesMicro Controllers Lab Final - DSCESreeda PerikamanaNo ratings yet

- Serial PortDocument27 pagesSerial PortGantulga PurevdorjNo ratings yet

- Ac Motor Speed Control Using PWM TechniqueDocument63 pagesAc Motor Speed Control Using PWM TechniqueSaravanan Viswakarma100% (1)

- Microprocessor Systems Lab Experiment 4 BodyDocument6 pagesMicroprocessor Systems Lab Experiment 4 BodyRuth Abegail de VeraNo ratings yet

- Micro Controller Lab Manual 1Document38 pagesMicro Controller Lab Manual 1Suresh KumarNo ratings yet

- Microprocessor and MicrocontrollerDocument35 pagesMicroprocessor and MicrocontrollerPRABHVaB100% (1)

- Unit 4 - Microprocessor & Its Application - WWW - Rgpvnotes.inDocument9 pagesUnit 4 - Microprocessor & Its Application - WWW - Rgpvnotes.inJayesh JoshiNo ratings yet

- Experiment #6 Input / Output DesignDocument11 pagesExperiment #6 Input / Output DesignFelipe DiasNo ratings yet

- A4.8051 Communication Protocols - UART, RS232Document5 pagesA4.8051 Communication Protocols - UART, RS232sneha singhNo ratings yet

- Lecture - 9 & 10pin Diagram 8085Document24 pagesLecture - 9 & 10pin Diagram 8085no fake NewsNo ratings yet

- Microcontrollers LabDocument19 pagesMicrocontrollers LabAMARNATHNAIDU77No ratings yet

- MPMC AnswersDocument10 pagesMPMC AnswersMuralicheenuNo ratings yet

- Sns College of Engineering: Kurumbapalayam (Po), Coimbatore - 641 107Document19 pagesSns College of Engineering: Kurumbapalayam (Po), Coimbatore - 641 107Afkir Al-HusaineNo ratings yet

- Module3 - 8051 Stack, IO Port Interfacing and Programming - UpdatedDocument10 pagesModule3 - 8051 Stack, IO Port Interfacing and Programming - UpdatedPraveen G MNo ratings yet

- IA2 - Scheme & Sol MC - by TauseefDocument6 pagesIA2 - Scheme & Sol MC - by Tauseefjvgirish74No ratings yet

- Advance Microcontroler MicroDocument5 pagesAdvance Microcontroler Micromd mamnunNo ratings yet

- Cellphone Operated Robotic ArmDocument55 pagesCellphone Operated Robotic ArmVinay ReddyNo ratings yet

- The 8253Document29 pagesThe 8253Soumya Ranjan PandaNo ratings yet

- Micro Task 4 - Merged - CompressedDocument32 pagesMicro Task 4 - Merged - Compresseddipak6541.6615No ratings yet

- Unit 5Document52 pagesUnit 5mir xahidNo ratings yet

- 8 MPLAB ICD & PIC 16F877 Tutorial: CY CY OSC OSCDocument9 pages8 MPLAB ICD & PIC 16F877 Tutorial: CY CY OSC OSCrobotbusterNo ratings yet

- Unit III MPMC MaterialDocument33 pagesUnit III MPMC Materialsree2728No ratings yet

- Microprocessor 2 Marks V+Document24 pagesMicroprocessor 2 Marks V+mekalajesiNo ratings yet

- ON Microcontroller-8051 and Applications: BY G N V Ratna Kishor M.Sc.,M.Tech. Asst. ProfessorDocument66 pagesON Microcontroller-8051 and Applications: BY G N V Ratna Kishor M.Sc.,M.Tech. Asst. ProfessorbhavanimaddulaNo ratings yet

- Microcontrollers Lab ManualDocument37 pagesMicrocontrollers Lab ManualArati DazNo ratings yet

- 8254 MICROPROCESSOR (Driste)Document13 pages8254 MICROPROCESSOR (Driste)CSE7 NDUBNo ratings yet

- Microcontroller Lab ManualDocument26 pagesMicrocontroller Lab Manualssmtejani2No ratings yet

- Mod 3 Timer DMAcontrDocument55 pagesMod 3 Timer DMAcontrNicky SanthoshNo ratings yet

- Lecture 12 8051 Timer Programing v2Document22 pagesLecture 12 8051 Timer Programing v2Faisal Bin Abdur Rahman 1912038642No ratings yet

- 8051 Lab ManualDocument35 pages8051 Lab ManualVenkat BalajiNo ratings yet

- Automatic Load SharingDocument41 pagesAutomatic Load SharingSaravanan ViswakarmaNo ratings yet

- 8155 Is An Integrated RamDocument22 pages8155 Is An Integrated RamVipan SharmaNo ratings yet

- Amm Cheet PrintDocument7 pagesAmm Cheet PrintjokerNo ratings yet

- LAB7Document5 pagesLAB7REHAM DEE CAMAMANo ratings yet

- Unit 3Document27 pagesUnit 3Jyotirmayee PandaNo ratings yet

- Unit 1Document41 pagesUnit 1kaustubhNo ratings yet

- Electrical Engineering Department Academic SessionDocument17 pagesElectrical Engineering Department Academic SessionShavitra 30No ratings yet

- Department of Technical Education Andhra Pradesh: 9CM405.7TO8 1 1Document19 pagesDepartment of Technical Education Andhra Pradesh: 9CM405.7TO8 1 1Y. S.V.Ramana raoNo ratings yet

- WAN TECHNOLOGY FRAME-RELAY: An Expert's Handbook of Navigating Frame Relay NetworksFrom EverandWAN TECHNOLOGY FRAME-RELAY: An Expert's Handbook of Navigating Frame Relay NetworksNo ratings yet

- Product GuideDocument85 pagesProduct GuidePaBenavidesNo ratings yet

- P 1690 TBWDocument104 pagesP 1690 TBWShoaib JadoonNo ratings yet

- Iq8Tal With Isolator, 1 Contact In/1 Out: Part-No.: 804868 Approval: VdsDocument1 pageIq8Tal With Isolator, 1 Contact In/1 Out: Part-No.: 804868 Approval: VdstomNo ratings yet

- Equipment TP MAV AEL Oil Supply UnitDocument1,392 pagesEquipment TP MAV AEL Oil Supply UnitMuhammad Hasbi AsidiqiNo ratings yet

- Textile Fabrics & Clothing: 1. Abduselam AbdulkadirDocument5 pagesTextile Fabrics & Clothing: 1. Abduselam AbdulkadirCE CERTIFICATENo ratings yet

- Virador Fub 30Document2 pagesVirador Fub 30herlin.velasquezaNo ratings yet

- Comparison Between RISC and CISCDocument1 pageComparison Between RISC and CISCShubham BagalNo ratings yet

- Sae J96-2019Document3 pagesSae J96-2019Marcos RosenbergNo ratings yet

- Adaptor Plate: Size 06/04, 10/06 (D03/D02, D05/D03) P 350 Bar (5800 PSI)Document2 pagesAdaptor Plate: Size 06/04, 10/06 (D03/D02, D05/D03) P 350 Bar (5800 PSI)Ramiro Di PintoNo ratings yet

- Slide 7Document40 pagesSlide 7Paul StarkNo ratings yet

- Manual Il NT Mrs19vautodetect 1.0Document84 pagesManual Il NT Mrs19vautodetect 1.0Miguel Angel Pavon CarbonellNo ratings yet

- 2 PDFDocument40 pages2 PDFCerasela GeorgescuNo ratings yet

- AN-739 rs232 Cop800Document12 pagesAN-739 rs232 Cop800api-3725139No ratings yet

- 1966 Ford Mustang Breaker Points and Condenser Removal and InstallationDocument4 pages1966 Ford Mustang Breaker Points and Condenser Removal and InstallationOxgardNo ratings yet

- General Engine Info Aircraft Information Limiting Part InformationDocument1 pageGeneral Engine Info Aircraft Information Limiting Part InformationAHAMEDNo ratings yet

- Light Emiting Polymers Seminar ReportDocument23 pagesLight Emiting Polymers Seminar ReportitsmemonuNo ratings yet

- C1361 PDFDocument5 pagesC1361 PDFLucas CamposNo ratings yet

- N ® DT-466E D E: Avistar Iesel NgineDocument1 pageN ® DT-466E D E: Avistar Iesel NgineJUAN ERNESTO BETANCUR OSORIONo ratings yet

- EXPLORER II 75-85-95 Special 1 Section 40Document25 pagesEXPLORER II 75-85-95 Special 1 Section 40dimos KARAMATZIARISNo ratings yet

- Projeto Antena Direcional PXDocument4 pagesProjeto Antena Direcional PXalissonalexNo ratings yet

- SEL-TBD-I-DS-021 - R0 - Data Sheet For MSAI Flow Transmitter - SignDocument4 pagesSEL-TBD-I-DS-021 - R0 - Data Sheet For MSAI Flow Transmitter - SignhadiNo ratings yet

- EIE Lecture Notes (6th Semester Electrical)Document84 pagesEIE Lecture Notes (6th Semester Electrical)asli almu0% (1)

- Winner Hydraulics - Price List: Index and Part Number Interchange ListDocument23 pagesWinner Hydraulics - Price List: Index and Part Number Interchange ListSHANENo ratings yet

- Man-1200 Elite RS Installation and Operation Manual Apollo Protocol PDFDocument156 pagesMan-1200 Elite RS Installation and Operation Manual Apollo Protocol PDFMostafa Ali100% (1)