Professional Documents

Culture Documents

Cordic (Coordinate Rotation Digital Computer) : For VLSI Signal Processing Course

Uploaded by

AnandiacrOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Cordic (Coordinate Rotation Digital Computer) : For VLSI Signal Processing Course

Uploaded by

AnandiacrCopyright:

Available Formats

VLSI Signal Processing

1

CORDIC

(Coordinate rotation digital computer)

For VLSI Signal Processing Course

Ref: Y. H. Hu, CORDIC based VLSI architecture for

digital signal processing, IEEE Signal Processing Mag.,

pp.16-35, July 1992.

2001/4/30

VLSI Signal Processing

2

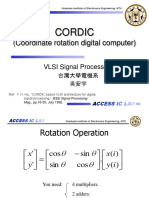

Rotation Operation

(

=

(

) (

) (

.

cos sin

sin cos

'

'

i y

i x

y

x

u u

u u

You need: 4 multipliers.

2 adders.

or ROM for Table Look-up

VLSI Signal Processing

3

What is CORDIC ?

COordinate Rotation DIgital Computer

Why do we use CORDIC ?

MAC dominates the implementational

cost in some DSP functions.

The DSP approach, CORDIC, helps to

save the hardware cost.

VLSI Signal Processing

4

Basic Concept of The CORDIC

To decompose the desired rotation angle ()

into the weighted sum of a set of predefined

elementary rotation angles (am(i))

Such that the rotation through each of them

can be accomplished with simple shift-and-

add operation.

VLSI Signal Processing

5

Behavior of CORDIC

V(0)

V(1)

V(3)

1

2 2

= + y x

VLSI Signal Processing

6

(

=

(

+

+

) (

) (

.

cos sin

sin cos

) 1 (

) 1 (

i y

i x

a a

a a

i y

i x

m m

m m

In General Case:

(

(

(

=

(

+

+

) (

) (

.

1

1

) 1 (

) 1 (

2

2

i y

i x

i

i

i y

i x

i

i

In CORDIC Algorithm:

(

=

(

+

+

) (

) (

1 tan

tan 1

cos

) 1 (

) 1 (

i y

i x

a

a

a

i y

i x

m

m

m

VLSI Signal Processing

7

CORDIC Algorithm

(i) am i

1 - n

0

1 - n

0

= =

= =

i i

i

u u

) 2 ( tan a

1

m

i

=

2 a tan ) (

1

m

i

=

)......... 2 ( tan ) 2 ( tan ) 2 ( tan

2 1 1 1 0 1

=

.........

4 3 2 1 1

u u u u u u =

VLSI Signal Processing

8

Initiation:Given x(0),y(0),z(0)

For i=0 to n-1 ,Do

/*CORDIC iteration equation */

/*Angle updating equation*/

(i) a - m i z(i) 1) z(i = +

/*Scaling Operation (required for m=1 only)*/

End i loop

(

=

(

) (

) (

) (

1

n y

n x

n K y

x

m f

f

(

(

(

=

(

+

+

) (

) (

.

1

1

) 1 (

) 1 (

2

2

i y

i x

i

i

i y

i x

i

i

m

n

i

m

a

n K

cos

1

) (

1

0

H

=

=

VLSI Signal Processing

9

X(i) Y(i)

X-Reg Y-Reg

+/- +/-

Barrel

shifter

Barrel

shifter

X(i+1) Y(i+1)

a(n-1)

a(1)

a(0)

Z-reg

i

Z(i+1)

Basic

processor for

CORDIC

VLSI Signal Processing

10

Modes of Operations

Vector rotation mode ( is given) :

determined by the set of

) (

i

z(n) - z(n) - z(0)

1

0

i

m

n

i

a

=

= = u

The objective is to compute the final

vector (Usually, we set z(0)= .)

= sign of z(i)

VLSI Signal Processing

11

Modes of Operations (contd)

Angle accumulation mode ( is

not given)

The objective is to rotate the given initial

vector back to x-axis ,and the angle can

be accrued.(Now, we let z(0)=0.)

= - sign of x(i)y(i)

V(0)

V(1)

X-axis

VLSI Signal Processing

12

Scaling Operation

b

q p

Q

q

q

i

q

m

P

p

i

p

m

n

i

i m s

i m

k k

k

n K

Type

k

n K

Type

m K

q

p

< = =

+ + =

=

+ =

[

[

2 ; 1 ; 1

) 2 1 (

) (

1

: 2 .

2

) (

1

: 1 .

2 1

1

1

1

0

) , ( 2 2

c

c

VLSI Signal Processing

13

X(n) Y(n)

X(n) Y(n)

+/- +/-

Barrel

shifter

Barrel

shifter

X-Reg Y-Reg

) ( ' 2 ) ( ' ) 1 ( '

) ( ' 2 ) ( ' ) 1 ( '

: 2

) ( 2 ) ( ' ) 1 ( '

) ( 2 ) ( ' ) 1 ( '

: 1

n y i y i y

n x i x i x

Type

n y i y i y

n x i x i x

Type

q

q

p

p

i

i

i

i

+ = +

+ = +

+ = +

+ = +

f f

y x

Scaling Stage

VLSI Signal Processing

14

Advantages and disadvantages

Simple Shift-and-add Operation.

(2 adders+2 shifters v.s. 4 mul.+2 adder)

-It needs n iterations to obtain n-bit

precision.

-Slow carry-propagate addition.

-Low throughput rate

-Area consuming shifting operations.

VLSI Signal Processing

15

How to improve CORDIC ?

Use Pipelined Architecture

Improve the Performance of the Adders

(redundant arithmetic, CSA)

Reduce Iteration Number

High radix CORDIC. (e.g., Radix-4, Radix-8)

Find a optimized shift sequence (e.g., AR-CORDIC)

Improve the Scaling Operation

Canonical multiplier recoding

Force Km to 2.

=

P

p

i

p

m

p

k

n K

1

2

) (

1

1 =

p

k

VLSI Signal Processing

16

Parallel and Pipelined Arrays

Basic

CORDIC

Processor

1

Basic

CORDIC

Processor

2

Basic

CORDIC

Processor

n+s

x(0)

y(0)

f

f

y

x

Basic

CORDIC

Processor

1

Basic

CORDIC

Processor

2

Basic

CORDIC

Processor

n+s

L

A

T

C

H

L

A

T

C

H

L

A

T

C

H

f

f

y

x

) 0 (

) 0 (

1

1

+ +

+ +

s n

s n

y

x

) 1 (

s n

v

+ ) 1 (

2

+ s n v

) (

1

s n v +

) 2 (

1 +s n

v

) 0 (

1 + +s n

v

VLSI Signal Processing

17

(

=

(

+

+

) (

) (

.

cos sin

sin cos

) 1 (

) 1 (

i y

i x

a a

a a

i y

i x

m m

m m

In General Case:

(

(

(

=

(

+

+

) (

) (

.

1

) , (

) , (

1

) 1 (

) 1 (

2

2

i y

i x

i m s

i m s

m

i y

i x

i

i

In CORDIC Algorithm:

(

=

(

+

+

) (

) (

1 tan

tan 1

cos

) 1 (

) 1 (

i y

i x

a

a

a

i y

i x

m

m

m

VLSI Signal Processing

18

Generalized CORDIC Algorithm

(i) am i

1 - n

0

=

=

i

u

] 2 [ tan

m

1

a

) , (

1

m = =

i m s

m

1 2 tanh

1 2 tan

0

) , 1 (

1

) , 1 (

1

) 1 , 0 (

2

=

=

m

m

m

i s

i s

s

m0 , linear system ;

m=1 , circular system ;

m=-1 , hyperbolic system.

VLSI Signal Processing

19

Circular

Linear

V(2)

V(4)

V(0)

V(1)

V(3)

1

2 2

= + y x

V(0)

V(2)

V(1)

V(3)

Hyperbolic

V(0)

V(1)

V(2)

V(3)

Different

coordinates

VLSI Signal Processing

20

Initiation: Given x(0),y(0),z(0)

For i=0 to n-1 ,Do

/*CORDIC iteration equation */

/*Angle updating equation*/

(i) a - m i z(i) 1) z(i = +

/*Scaling Operation (required for m=1 only)*/

End i loop

(

=

(

) (

) (

) (

1

n y

n x

n K y

x

m f

f

(

(

(

=

(

+

+

) (

) (

.

1

) , (

) , (

1

) 1 (

) 1 (

2

2

i y

i x

i m s

i m s

m

i y

i x

i

i

VLSI Signal Processing

21

Shift Sequence

{s(m,i); 0-i-n-1}

) 1 (

- ) (

1

0

) (

=

s

=

n a

a

m

i

m

n

i

i

o

u o

Determine the convergence of the CORDIC

iteration, as well as the magnitude of the scaling

factor Km(n).

m=0 or 1 , s=(m,i)=i

m=-1 , s(-1,i)=1,2,3,4,4,5,.,12,13,14,14,..

An angle approximation

error:

VLSI Signal Processing

22

Application to DSP Algorithms

Linear transformation:

- DFT, Chirp-Z transform, DHT, and FFT.

Digital filters:

- Orthogonal digital filters, and adaptive lattice filters.

Matrix based digital signal processing

algorithms:

- QR factorization, with applications to Kalman

filtering

- Linear system solvers, such as Toeplitz and

covariance system solvers,,etc.

VLSI Signal Processing

23

FFT application

N nk j

e

t 2

N nk j

e b a a

t 2

'

+ =

-1

' a

' b

a

b

N nk j

e b a b

t 2

'

=

VLSI Signal Processing

24

Butterfly unit

+

+

-

-

CORDIC

processor

R

a

I

a

R

b

I

b

R

a'

I

a'

R

b'

I

b'

N nk j

e

t 2

VLSI Signal Processing

25

Conclusions

1. In some cases, CORDIC evaluates rotational

functions more efficiently than MAC units.

2. CORDIC saves more hardware cost.

3. By the regularity, the CORDIC based

architecture is very suitable for implementation

with pipelined VLSI array processors.

4. The utility of the CORDIC based architecture

lies in its generality and flexibility.

You might also like

- Cordic: (Coordinate Rotation Digital Computer)Document25 pagesCordic: (Coordinate Rotation Digital Computer)santhiyadevNo ratings yet

- Cordic: (Coordinate Rotation Digital Computer)Document25 pagesCordic: (Coordinate Rotation Digital Computer)Magdalene MilanNo ratings yet

- Lecture7 Ee689 Eq Intro TxeqDocument27 pagesLecture7 Ee689 Eq Intro TxeqdogudoguNo ratings yet

- FPGA Implementation of Sine and Cosine Generators Using The CORDIC AlgorithmDocument9 pagesFPGA Implementation of Sine and Cosine Generators Using The CORDIC AlgorithmANIL KUMAR MANNAMNo ratings yet

- ECE734 VLSI Arrays for Digital Signal Processing Chapter 4 RetimingDocument24 pagesECE734 VLSI Arrays for Digital Signal Processing Chapter 4 RetimingaravinthcpNo ratings yet

- FPGA Implementation of Sine and Cosine Generators Using The CORDIC AlgorithmDocument13 pagesFPGA Implementation of Sine and Cosine Generators Using The CORDIC AlgorithmGovind AtalNo ratings yet

- Implementation and Performance Analysis PDFDocument5 pagesImplementation and Performance Analysis PDFMohamed GanounNo ratings yet

- SSM BoostDocument8 pagesSSM BoostTrương Văn TrọngNo ratings yet

- SSM BoostDocument8 pagesSSM BoostBenish CmNo ratings yet

- Implementing Sine and Cosine Using CORDIC AlgorithmDocument6 pagesImplementing Sine and Cosine Using CORDIC AlgorithmHarsh BaghelNo ratings yet

- Custom Single Purpose Processor DesignDocument24 pagesCustom Single Purpose Processor DesignAar Kay GautamNo ratings yet

- Electrical Engineering Lab ManualDocument7 pagesElectrical Engineering Lab ManualHasnain KashifNo ratings yet

- A Survey of CORDIC Algorithms For FPGA Based Computers: Ray AndrakaDocument0 pagesA Survey of CORDIC Algorithms For FPGA Based Computers: Ray AndrakaCix XidNo ratings yet

- CH22 The CordicDocument18 pagesCH22 The CordicDavidThânNo ratings yet

- Introduction To Discrete Time Systems and The Z TransformDocument93 pagesIntroduction To Discrete Time Systems and The Z TransformRaufzha AnandaNo ratings yet

- Vlsidsp Chap4 PDFDocument33 pagesVlsidsp Chap4 PDFgaru1991No ratings yet

- An Introduction To Discrete Wavelet TransformsDocument36 pagesAn Introduction To Discrete Wavelet TransformsAtacan ÖzkanNo ratings yet

- SR 01 07Document37 pagesSR 01 07Bhavik PatelNo ratings yet

- Assignment Report On Cordic Algorithm Implementation Using VerilogDocument27 pagesAssignment Report On Cordic Algorithm Implementation Using VerilogAyanabho BanerjeeNo ratings yet

- Digital Control Analysis and DesignDocument58 pagesDigital Control Analysis and DesignTan Yong LiangNo ratings yet

- Ee6403 DTSP123Document12 pagesEe6403 DTSP123VijayNo ratings yet

- MATLAB and Its Control ToolboxDocument41 pagesMATLAB and Its Control ToolboxzkqasimNo ratings yet

- Cockrum Fall 2008 Final PaperDocument15 pagesCockrum Fall 2008 Final Papernayeem4444No ratings yet

- Chapter 4 Retiming for Digital Signal ProcessingDocument24 pagesChapter 4 Retiming for Digital Signal ProcessinggalaxystarNo ratings yet

- DSP Question Bank for Digital Signal ProcessingDocument12 pagesDSP Question Bank for Digital Signal ProcessingBizura SarumaNo ratings yet

- Custom single-purpose processor design chapterDocument30 pagesCustom single-purpose processor design chapterNaresh Ks100% (1)

- High-Efficiency and Low-Power Architectures For 2-D DCT and IDCT Based On CORDIC RotationDocument6 pagesHigh-Efficiency and Low-Power Architectures For 2-D DCT and IDCT Based On CORDIC RotationGopinathan MuthusamyNo ratings yet

- Nov/Dec 2008 CS1354 Answer Key B.E / B.Tech Degree Examination Nov/Dec 2008 R 3261 CS1354 Computer Graphics and Multimedia Part ADocument10 pagesNov/Dec 2008 CS1354 Answer Key B.E / B.Tech Degree Examination Nov/Dec 2008 R 3261 CS1354 Computer Graphics and Multimedia Part AgspriyadarshiniNo ratings yet

- Digital Signal Processing QUESTION BANKDocument5 pagesDigital Signal Processing QUESTION BANKSaran SekaranNo ratings yet

- CADDocument48 pagesCADAshwin MahenderNo ratings yet

- IC6701 May 18 With KeyDocument14 pagesIC6701 May 18 With KeyAnonymous yO7rcec6vuNo ratings yet

- Introduction To Time Domain Electromagnetic Methods: Yanjie Zhu Yinchao Chen Paul G. Huray 12/03/2004Document40 pagesIntroduction To Time Domain Electromagnetic Methods: Yanjie Zhu Yinchao Chen Paul G. Huray 12/03/2004Ashish VermaNo ratings yet

- Concepts of Fsdsdfsignal & Image ProcessingDocument6 pagesConcepts of Fsdsdfsignal & Image ProcessingPrahlad ReddyNo ratings yet

- Analysis of Simple CORDIC Algorithm Using MATLABDocument3 pagesAnalysis of Simple CORDIC Algorithm Using MATLABamit.18.singh2466No ratings yet

- MATLAB ProblemsDocument4 pagesMATLAB ProblemsPriyanka TiwariNo ratings yet

- Application of Bio-Inspired Techniques To TelecommunicationDocument21 pagesApplication of Bio-Inspired Techniques To TelecommunicationSnigdha PatnaikNo ratings yet

- LinkagesDocument29 pagesLinkagesRubén GonzálezNo ratings yet

- Introduction To Equalization: Guy Wolf Roy Ron Guy ShwartzDocument50 pagesIntroduction To Equalization: Guy Wolf Roy Ron Guy ShwartzShilpi RaiNo ratings yet

- Image Compression 2011Document52 pagesImage Compression 2011sprynavidNo ratings yet

- SOPC Implementation of Software-Defined Radio: First PrizeDocument16 pagesSOPC Implementation of Software-Defined Radio: First PrizenanostallmannNo ratings yet

- Cordic by MohitDocument19 pagesCordic by MohitNarwal MohitNo ratings yet

- Chapter 3 Parallel and Pipelined Processing: 1 ECE734 VLSI Arrays For Digital Signal ProcessingDocument13 pagesChapter 3 Parallel and Pipelined Processing: 1 ECE734 VLSI Arrays For Digital Signal ProcessingAnup0008No ratings yet

- Wemmu 001Document4 pagesWemmu 001shastryNo ratings yet

- CORDICDocument32 pagesCORDICrah0987No ratings yet

- Classical Control System Design TechniquesDocument49 pagesClassical Control System Design Techniquesजनार्धनाचारि केल्लाNo ratings yet

- Graduate Institute of Electronics Engineering CORDIC VLSIDocument25 pagesGraduate Institute of Electronics Engineering CORDIC VLSIAchuNo ratings yet

- Liquid Level Control Systems Using PID TuningDocument220 pagesLiquid Level Control Systems Using PID TuningivorNo ratings yet

- Pipelined CORDIC Design On FPGA For A Digital Sine and Cosine Waves GeneratorDocument4 pagesPipelined CORDIC Design On FPGA For A Digital Sine and Cosine Waves GeneratorMohamed GanounNo ratings yet

- CordicDocument21 pagesCordic2015mdaamir2015No ratings yet

- CFD NotesDocument68 pagesCFD NotesPraveen P JoseNo ratings yet

- CFD Course Notes OverviewDocument68 pagesCFD Course Notes OverviewPankaj GuptaNo ratings yet

- Nonlinear Control Feedback Linearization Sliding Mode ControlFrom EverandNonlinear Control Feedback Linearization Sliding Mode ControlNo ratings yet

- Inverse Trigonometric Functions (Trigonometry) Mathematics Question BankFrom EverandInverse Trigonometric Functions (Trigonometry) Mathematics Question BankNo ratings yet

- Green's Function Estimates for Lattice Schrödinger Operators and Applications. (AM-158)From EverandGreen's Function Estimates for Lattice Schrödinger Operators and Applications. (AM-158)No ratings yet

- Robot Manipulators: Modeling, Performance Analysis and ControlFrom EverandRobot Manipulators: Modeling, Performance Analysis and ControlNo ratings yet

- Bloom PolygonDocument1 pageBloom PolygonAnandiacrNo ratings yet

- Abstract Method in ClassDocument8 pagesAbstract Method in ClassAnandiacrNo ratings yet

- By: Prof. Kumar Anand SinghDocument21 pagesBy: Prof. Kumar Anand SinghAnandiacrNo ratings yet

- CommunicationDocument16 pagesCommunicationAnandiacrNo ratings yet

- EMI LAB (NTC Thermistor)Document8 pagesEMI LAB (NTC Thermistor)AnandiacrNo ratings yet

- Chapter 1 Vector AnalysisDocument9 pagesChapter 1 Vector AnalysisAnandiacrNo ratings yet

- 2000 Series Users GuideDocument278 pages2000 Series Users GuideNevzat AtaklıNo ratings yet

- Characteristics of NTC ThermistorDocument4 pagesCharacteristics of NTC ThermistorAnandiacrNo ratings yet

- Chapter 1 Vector AnalysisDocument9 pagesChapter 1 Vector AnalysisAnandiacrNo ratings yet

- Introduction To LabVIEW CompleteDocument122 pagesIntroduction To LabVIEW CompleteAlejandro ArgaezNo ratings yet

- Engineering ElectromagneticDocument2 pagesEngineering ElectromagneticAnandiacrNo ratings yet

- Vl0502-Digital Signal Processing Structures For VlsiDocument2 pagesVl0502-Digital Signal Processing Structures For VlsiAnandiacrNo ratings yet

- Joshi-VLSI Signal ProcessingDocument12 pagesJoshi-VLSI Signal ProcessingsureshgrNo ratings yet

- Elements of ElectronicsDocument2 pagesElements of ElectronicsjhpandiNo ratings yet

- Bridge Course CivilDocument7 pagesBridge Course CiviljhpandiNo ratings yet

- VL0507 PDFDocument1 pageVL0507 PDFAnandiacrNo ratings yet

- VL0502Document1 pageVL0502AnandiacrNo ratings yet

- Vl0556-Digital Signal Processing Systems - 2Document2 pagesVl0556-Digital Signal Processing Systems - 2AnandiacrNo ratings yet

- Vl0507-Digital Vlsi Design - 1Document1 pageVl0507-Digital Vlsi Design - 1AnandiacrNo ratings yet

- Vl0507-Digital Vlsi Design - 1Document1 pageVl0507-Digital Vlsi Design - 1AnandiacrNo ratings yet

- Gujarat Technological University: M.E. in VLSI System DesignDocument1 pageGujarat Technological University: M.E. in VLSI System DesignAnandiacrNo ratings yet

- Vl0507-Digital Vlsi Design - 1Document1 pageVl0507-Digital Vlsi Design - 1AnandiacrNo ratings yet

- Vl0556-Digital Signal Processing Systems - 2Document2 pagesVl0556-Digital Signal Processing Systems - 2AnandiacrNo ratings yet

- VL0507 PDFDocument1 pageVL0507 PDFAnandiacrNo ratings yet

- VL0502Document1 pageVL0502AnandiacrNo ratings yet

- Embedded System Design (Major Elective - I)Document1 pageEmbedded System Design (Major Elective - I)Kapil JoshiNo ratings yet

- RF CMOS IC Design (Major Elective-II)Document1 pageRF CMOS IC Design (Major Elective-II)AnandiacrNo ratings yet

- VLSI Signal Processing (Major Elective-II)Document2 pagesVLSI Signal Processing (Major Elective-II)Kapil JoshiNo ratings yet

- The PN Junction Diode (Open CKT)Document13 pagesThe PN Junction Diode (Open CKT)AnandiacrNo ratings yet

- CS302 Quiz Solved For MID TERM PDFDocument25 pagesCS302 Quiz Solved For MID TERM PDFattiqueNo ratings yet

- DAG - Directed Acyclic GraphDocument8 pagesDAG - Directed Acyclic GraphMs.R.Thillaikarasi CSE DepartmentNo ratings yet

- Unit - V: Branch and Bound - The MethodDocument18 pagesUnit - V: Branch and Bound - The Methodmansha99No ratings yet

- Chapter 7 Algorithms W6Document2 pagesChapter 7 Algorithms W6golchhavidhiNo ratings yet

- Compre Make-Up MFDS PDFDocument2 pagesCompre Make-Up MFDS PDFsrirams007No ratings yet

- Chapter-5-Data Flow Models - TestingDocument52 pagesChapter-5-Data Flow Models - TestingAbhilash HegdeNo ratings yet

- Math 8 2nd QRT ScaffoldDocument1 pageMath 8 2nd QRT ScaffoldSimmy DhaliwalNo ratings yet

- All INT Quizzes 3Document25 pagesAll INT Quizzes 3Tiberiu UngurianuNo ratings yet

- Program-21: To Implement A Stack and Manage DataDocument16 pagesProgram-21: To Implement A Stack and Manage DataShivam Kumar singhNo ratings yet

- CS 201 1 PDFDocument7 pagesCS 201 1 PDFMd AtharNo ratings yet

- Genetic AlgorithmDocument104 pagesGenetic AlgorithmVishnuraj Vishnu KrNo ratings yet

- Quantum ComputingDocument1 pageQuantum ComputingNikhil ShahNo ratings yet

- C Program For Binary Search TreeDocument6 pagesC Program For Binary Search TreeSaiyasodharan89% (19)

- CS40003 (Data Analytics) : Term ProjectDocument10 pagesCS40003 (Data Analytics) : Term ProjectMirnesa SalihovićNo ratings yet

- Programming and Data Structure Solved MCQs Part 2 BookDocument15 pagesProgramming and Data Structure Solved MCQs Part 2 BookRida BaigNo ratings yet

- Chapter 8: Deadlocks: Silberschatz, Galvin and Gagne ©2018 Operating System Concepts - 10 EditionDocument47 pagesChapter 8: Deadlocks: Silberschatz, Galvin and Gagne ©2018 Operating System Concepts - 10 EditionyashNo ratings yet

- AVL Tree- Self-Balancing Binary Search TreeDocument22 pagesAVL Tree- Self-Balancing Binary Search TreeVaibhav RavindraNo ratings yet

- AA Tree: Balancing RotationsDocument6 pagesAA Tree: Balancing Rotationsneoage12No ratings yet

- Neural Network Backpropagation ExplainedDocument7 pagesNeural Network Backpropagation ExplainedАндрей МаляренкоNo ratings yet

- Daniel Moune Algo Ds 2 Assignment 2Document5 pagesDaniel Moune Algo Ds 2 Assignment 2oliviertwizzNo ratings yet

- Bin Packing AlgorithmsDocument3 pagesBin Packing AlgorithmsKhairi AzmiNo ratings yet

- Query Processing & Optimization OverviewDocument38 pagesQuery Processing & Optimization OverviewJAYPALSINH GOHILNo ratings yet

- Compiler DesignDocument25 pagesCompiler DesignTrust KaguraNo ratings yet

- FFT (Fast Fourier Transformation) AlgorithmDocument4 pagesFFT (Fast Fourier Transformation) Algorithmabdullah1996No ratings yet

- Tail Lard 1993Document8 pagesTail Lard 1993LUISA FRAZAO PRIMONo ratings yet

- Vahid Butterfly Transform An Efficient FFT Based Neural Architecture Design CVPR 2020 PaperDocument10 pagesVahid Butterfly Transform An Efficient FFT Based Neural Architecture Design CVPR 2020 PaperfcojafetNo ratings yet

- LTI System Properties Example: Yn XNDocument2 pagesLTI System Properties Example: Yn XNShahbazHussainNo ratings yet

- Computer Science Practice Book IIIDocument115 pagesComputer Science Practice Book IIIRohit SallaNo ratings yet

- Questions:: School of Information Technology and Engineering M.Tech. Software Engineering (Integrated)Document3 pagesQuestions:: School of Information Technology and Engineering M.Tech. Software Engineering (Integrated)Teja SreeNo ratings yet

- Rang 3Document3 pagesRang 3ManoNo ratings yet