Professional Documents

Culture Documents

TI Stellaris CortexM4F Peripheral Overview

TI Stellaris CortexM4F Peripheral Overview

Uploaded by

Nestor JrCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

TI Stellaris CortexM4F Peripheral Overview

TI Stellaris CortexM4F Peripheral Overview

Uploaded by

Nestor JrCopyright:

Available Formats

Stellaris

ARM

Cortex-M4F Training

1

Peripheral Overview

Agenda

Stellaris LM4F General Specifications

Features of ARM

Cortex-M4F

Other System Features

Low Power Features

Watchdog Timers

Timers and GPIOs

2

Timers and GPIOs

Analog Peripherals

Connectivity

Motion Control Peripherals

Stellaris

LM4F Devices

3

Stellaris

ARM

Cortex-M4F

Connectivity features:

CAN, USB H/D/OTG, SPI, I2C, UARTs

High-performance analog integration

Two 1 MSPS 12-bit ADCs

Three analog comparators

Best-in-class power consumption

As low as 370 uA/MHz

Stellaris

LM4Fx MCU

Serial Interfaces Motion Control

ARM

Cortex-M4F

SWD/T

NVIC

JTAG

FPU

ETM

MPU

80 MHz

256 KB

Flash

Analog

Temp Sensor

3 Analog

Comparators

32 KB

SRAM

ROM

2KB EEPROM

LDO Voltage

Regulator

2 x 12-bit ADC

Up to 24 channel

1 MSPS

System

As low as 370 uA/MHz

500s wakeup from low-power modes

RTC currents as low as 1.7uA

Solid roadmap

Higher speeds

Larger memory

Ultra-low power

6 I

2

C

2 CAN

8 UARTs

USB Full Speed

Host / Device / OTG

4 SSI/SPI

2 Quadrature

Encoder Inputs

16 PWM Outputs

Comparators

PWM

Generator

Timer

Dead-Band

Generator

PWM

Generator

System

Systick Timer

Precision Oscillator

Clocks, Reset

System Control

12 Timer/PWM/CCP

6 each 32-bit or 2x16-bit

6 each 64-bit or 2x32-bit

2 Watchdog Timers

GPIOs

32ch DMA

Battery-Backed

Hibernate

R

T

C

Internal Memory

256 KB single-cycle Flash memory up to 40 MHz; a prefetch buffer

improves performance above 40 MHz

32 KB single-cycle SRAM with bit-banding

Internal ROM loaded with StellarisWare software:

Stellaris Peripheral Driver Library

Stellaris Boot Loader Stellaris Boot Loader

Advanced Encryption Standard (AES) cryptography tables

Cyclic Redundancy Check (CRC) error detection functionality

2KB EEPROM

5

Stellaris architecture

JTAG/SWD

System

Control and

Clocks

(W/ Precls. Osc.)

ARM

Cortex

tm

-M4F

(80 MHz)

FPU

MPU NVIC

ROM

Flash

(256 KB)

SRAM

(32KB)

BUS Matrix

DCode bus

System Bus

LM4F232H5QD

DMA

EEPROM

ICode bus

Watchdog

Timers (2)

Hibernation SYSTEM

A

d

v

a

n

c

e

d

P

e

r

i

p

h

e

r

a

l

B

u

s

(

A

P

B

)

EEPROM

(2K)

GPIOs

(105)

USB OTG

(FS PHY)

Ssi

(4)

Hibernation

Module

General- Purpose

Timers (12)

CAN

Controllers (2)

UART

(8)

I2C

(6)

Analog

Comparators (3)

Analog

Comparators (3)

A

d

v

a

n

c

e

d

H

i

g

h

-

P

e

r

f

o

r

m

a

n

c

e

B

u

s

(

A

H

B

)

ADC Channels

(24)

QEI

(2)

SYSTEM

PERIPHERALS

SERIAL

PERIPHERALS

ANALOG

PERIPHERALS

MOTION CONTROL

PERIPHERALS

Stellaris

LM4F System Features

Direct Memory Access, Hibernate Module, Watchdog Timers

7

Direct Memory Access, Hibernate Module, Watchdog Timers

Direct Memory Access

32 channel configurable DMA controller

Dedicated channels for supported peripherals

One channel each for receive and transmit path for bidirectional peripherals

Multiple data sizes, two levels of priority, maskable device request

Interrupt on transfer completion, with a separate interrupt per channel

Main processer is always given priority for bus access

8

Main processer is always given priority for bus access

Multiple transfer modes:

Basic

Auto

Ping-pong, for continuous data flow to/from peripherals

Scatter-gather, from a programmable list of arbitrary transfers initiated from a single

request

DMA requests supported by:

UART, Timer, USB, ADC, SSI, External Peripherals I/F, GPIO

DMA Basic Transfer and Auto Transfer

Source: A

Destination: B

Control word: Basic

PrimaryControl Struct

DMA

Request

0x8F45

Location A

0x8F45

Location B

Data

Copied

Basic Transfers move data from one location to another as long as the

request remains active, and there is still data to transfer. This works well

for peripherals which normally keep their requests active for the duration of

the transfer.

Auto Transfers work similarly, but finish the transfer, even if the request is

removed. This is typically used for software requests, so the request does

not have to remain active for the entire duration.

9

DMA Ping-Pong Transfers

A Periph

Primary Ctrl Struct

B Periph

Alternate Ctrl Struct

Periph

A B C D

Buffers

1 2

Primary control struct performs its transfer while

alternate struct is idle (or being loaded with the

next transfer).

A Periph

Primary Ctrl Struct

B Periph

Alternate Ctrl Struct

Periph

Complete

Primary control struct sends an interrupt to the

processor to declare its transfer complete.

Buffers

A B C D

10

3 4

next transfer).

C Periph

Primary Ctrl Struct

B Periph

Alternate Ctrl Struct

Periph

C Periph

Primary Ctrl Struct

B Periph

Alternate Ctrl Struct

Periph

Alternate control struct performs its transfer,

while primary control struct is loaded with the

next transfer.

Alternate control struct sends an interrupt to the

processor to declare its transfer complete, and

the cycle starts over from step 1.

Complete

A B C D

Buffers

A B C D

Buffers

Scatter-Gather

Source: A

Destination: F

S/G Struct

Source: S/G

Dest: Ctrl Struct 2

Control: S/G

Primary Ctrl Struct

Source: B

Destination: F

Source: C

Source:

Alternate Ctrl Struct

1

2

3

A

B

F

1

2

4

11

Source: C

Destination: F

Source: D

Destination: F

Source: E

Destination: F

Source:

Destination:

Control: S/G

3

4

5

C

D

E

3

4

5

The primary control structure performs DMA transfers

to put DMA tasks from the task list into the Alternate

control structure in sequence. The alternate control

structure then performs each DMA task one by one.

This allows many transfers to happen together, even if

the relevant memory is not contiguous.

Hibernation and Low Power States

Stellaris family devices offer the following three low power states:

Sleep Mode

Deep-Sleep Mode

Hibernation

12

Sleep Mode and Deep Sleep Mode

Sleep Mode

Turns off the clock for the main processor

Will wake up when a high enough priority interrupt is received

Deep Sleep Deep Sleep

Turns off the system clock, PLL, and flash memory

Enables a Wake-up Interrupt Controller (WIC), which will bring the

processor out of deep sleep if an interrupt is received

13

Hibernation Module

The Hibernation module manages removal and restoration of power as a

means for reducing power consumption. It can completely remove

power from all parts of the chip except itself.

Includes a 32-bit real-time seconds counter with 1/32,768 second

resolution for timed wake up

Dedicated pin for an external wakeup trigger Dedicated pin for an external wakeup trigger

GPIO pin state may be retained, and 16 32-bit words of non volatile

memory may store the system state during hibernation

Programmable interrupts for RTC match, external wake, and low

battery events

Runs on a separate clock and power source

14

Normal Operation

Processor

Hibernation

Module

Peripherals

15

Processor

Module

WIC

Processor and peripherals are powered; sleep, deep sleep, and

hibernate-related features are turned off.

Sleep Mode

Processor

Hibernation

Module

Peripherals

16

Processor

Module

WIC

The processor enters a low-power state, and stops executing

instructions until a sufficiently important interrupt is received.

Deep Sleep Mode

Processor

Hibernation

Module

Peripherals

17

Processor

Module

WIC

Processor enters a very low-power state, and some features (such

as Systick) are shut off completely. The Wakeup Interrupt Controller

(WIC) intercepts important interrupts, and wakes the processor if

necessary.

Hibernate

Processor

Hibernation

Module

Peripherals

18

Processor

Module

WIC

Power to the majority of the chip, including the processor and all

peripherals, is shut off. The Hibernation module continues to

operate using its own power source and clock until the wakeup

condition is met.

Watchdog Timers

Two 32-bit countdown timers, capable of generating maskable or non-

maskable interrupts on roll-over.

One Watchdog timer is clocked by the system clock. The other runs

from the PIOSC

Configuration may be locked to prevent inadvertent changes to the

watchdog settings. watchdog settings.

User-enabled stalling for software debugging.

May be used to generate a system reset when the processor fails to

clear the interrupt

Possible uses:

Recovering from software errors

Recover from external devices failing or not behaving as expected.

Reset and continue operation if the main crystal is damaged or removed.

19

Stellaris

LM4F Low Power Details

20

Run Mode

This mode provides normal operation of the processor and currently

enabled peripherals (i.e. the ones that are enabled in RCGC registers).

The microcontroller actively executes code with maximum

performance.

The system clock can be any of the available clock sources including

the PLL.

I

DD_RUN

=

32mA

21 21

Sleep Mode

Sleep mode is used to lower the overall power consumption by turning off the clock to

the processor and memory (Flash & SRAM).

The active peripherals (i.e. the ones that are enabled in SCGC/ RCGC registers) are

clocked at the same frequency as the system clock.

The system clock has the same clock source & frequency as that during run mode.

Application: This mode is used in applications where processor neednt be running

code, but peripherals are still required to function at system clock speed.

I

DD_SLEEP

=

10mA

22 22

Processor executes a Wait for Interrupt

(WFI), or Wait for Event (WFE) or Sleep-

on-Exit (upon completing execution of

exception handler if SLEEPEXIT bit in

SYSCTRL register is set)

Processor (NVIC) detects an interrupt,

or depending upon the mechanism that

caused it to enter the sleep mode i.e.

WFI/WFE/Sleep-on-Exit.

Code execution begins

Entering into Sleep Mode and waking up from Sleep Mode

SLEEP MODE

2 sys clks. (when PPL is not used)

Deep Sleep Mode

Deep Sleep mode is used to further reduce the overall power consumption by turning off the

clock to the processor and memory (Flash & SRAM) along with the following:

Main osc. (MOSC, 4 to 25MHz) can be powered off.

PLL is powered off (if active in Run Mode).

The active peripherals (enabled in DCGC register) can be clocked using internal oscillator

(IOSC, 30kHz).

Application: This mode is used in applications where processor neednt be running code,

and peripherals are required to function at a speed lower than run-mode system speed.

23 23

If SLEEPDEEP bit in SYSCTRL & processor

executes a Wait for Interrupt (WFI)/ Wait for

Event (WFE) or Sleep-on-Exit (upon

completing execution of exception handler if

SLEEPEXIT bit in SYSCTRL register is set)

Wake-Up Interrupt Controller (WIC)

wakes up the processor upon

detecting an interrupt if DEEPSLEEP

bit SCR register is set.

Code execution begins

Entering into Deep Sleep Mode and waking up from Deep Sleep Mode

DEEP SLEEP MODE

1.25 to 350 s

Hibernation Mode

Hibernation mode provides the lowest power configuration available

on Stellaris microcontrollers.

This mode allows users to completely power down the core and

peripherals while only maintaining power to the Hibernation module.

Hibernation module is a dedicated hardware that:

Allows managing removal and restoration of power to the

processor.

Can be independently powered by an external battery or an aux.

I

HIB

=

1.6 A

24

Can be independently powered by an external battery or an aux.

power supply.

Allows power to be restored upon assertion of an external signal,

or at a certain time (using RTC).

Application: Used in battery-powered/ hand-held applications where

the system can be put into a lowest-power state while saving some

state information.

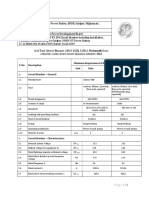

Power Mode Comparision

Mode

Run Mode Sleep Mode

Deep Sleep

Mode

Hibernate

(VDD3ON)

Hibernate

(RTC)

Hibernate

(no RTC)

Parameter

I

DD

32 mA 10 mA TBD 5 A 1.7 A 1.6 A

V

DD

3.3 V 3.3 V 3.3 V 3.3 V 0 V 0 V

25

V

BAT

N.A. N.A. N.A. 3 V 3 V 3 V

System

Clock

40 MHz with

PLL

40 MHz with

PLL

30 kHz Off Off Off

Core

Powered On Powered On Powered On

Off

Off Off

Clocked Not Clocked Not Clocked Not Clocked Not Clocked Not Clocked

Peripherals All On All Off All Off All Off All Off All Off

Code while{1} N.A. N.A. N.A. N.A. N.A.

Current Consumption in Different Power Modes

TBD

Hibernation Module Key Features

32 bit real time seconds counter (Real

time clock) with 15-bit sub seconds &

add-in trim capability

Dedicated pin for waking using an

external signal

RTC operational and hibernation

Low-battery detection, signaling, and

interrupt generation, with optional wake

on low battery

Clock source from a 32.768-kHz

external crystal or external oscillator

16 32-bit words of battery-backed

memory to save state during hibernation

26

RTC operational and hibernation

memory valid as long as V

BAT

is valid

GPIO pins state retention (VDD3ON

Mode)

Two mechanisms for power control

System Power Control

On-chip Power Control

memory to save state during hibernation

Programmable interrupts for RTC

match, external wake, and low battery

events.

Hibernation Module

Block Diagram & Signal Description

32.768 kHz

crystal, or a

single ended

clock source

External input

that brings the

processor out

of hibernation

Buffered

version of

32.768 kHz

clock

Battery

Backed

Memory

16 Words

27

of hibernation

mode

Power

source for

Hibernation

module, can

be an

external

power supply

or a battery

Output that

indicates

processor is in

hibernation mode

Functional Block Diagram of Hibernation Module

The device enters hibernation mode in following cases:

When HIBREQ bit in HIBCTL register is set, or

When V

DD

is removed with a valid V

BAT

(if properly configured).

When the device is in hibernation mode, HIB signal is asserted.

The device wakes-up from hibernation in following cases:

When WAKE pin is asserted, or

When RTC match occurs, or

When low battery is detected.

Hibernation Module Functional Description

When low battery is detected.

Upon wake up, HIB signal is de-asserted and an internal POR signal is issued.

28

HIBREQ=1, or

V

DD

removal

RTC match/ WAKE assertion/

Low battery detection

Code execution begins

t

WAKE_TO_HIB T

TPOR

Entering into hibernation and waking up from hibernation

HIBERNATION

~500 s

HIB signal is

de-asserted

t

LDO_RAMP

Dynamic power source determination

Supply voltage of Hibernation module is the higher of V

DD

or V

BAT.

2 mechanisms for power control (based on VDD3ON bit in HIBCTL register)

Power Control

Controls the power to the MCU with a control signal,

HIB is connected to EN signal of an external LDO

VDD3ON Mode: Uses internal switches to control

power to MCU while retaining power to I/O pins

29

Power control* using an External LDO Power Control* using VDD3ON Mode

GNDX GNDX

32.768 kHz 32.768 kHz

*simplified diagram to explain the concept. See datasheet for more details.

Hibernation module requires an external clock source that is independent from the main system clock.

An independent clock source is required to maintain RTC/ preserve the contents of battery-backed

memory when the main system clock is powered down due to removal of V

DD.

A 32.768-kHz crystal or an external clock source can be used to provide clock to the Hibernation

module.

If the application does not require hibernation, XOSC1 pin can remain unconnected, XOSC0 can be

connected to ground, and V

BAT

pin should be connected to V

DD

.

Hibernation Clock Source

30

Hibernation Clock Source: External Crystal Hibernation Clock Source: External Oscillator

Clock

Source

(f

EXT_OSC

)

32.768

kHz NC

32.768 kHz

GNDX

Low Battery Detection

Optionally, hibernation can be prevented during low battery condition i.e.

the module can be configured so that it does not go into hibernation mode

if the battery voltage drops below this threshold.

The module can monitor the voltage level of the external battery and

detect when the voltage drops below V

LOWBAT

(1.9V, 2.1V, 2.3V or 2.5V).

V

LOWBAT

threshold is configured using VBATSEL bit in HIBCTL register.

Battery voltage is monitored while in hibernation, and the microcontroller

Battery Management

Battery voltage is monitored while in hibernation, and the microcontroller

can also be configured to wake from hibernation if the battery voltage

goes below the threshold using the BATWKEN bit in the HIBCTL register.

31

The Hibernation module draws power from whichever

source, V

BAT

or V

DD

, has the higher voltage.

Stellaris

LM4F Timers and GPIOs

32

Timer Use

Individual Concatenated

16/32 bit

GPTM Block

32/64 bit

GPTM Block

One-Shot/Periodic Timer Mode

32-bit Timer

64-bit Timer

16-bit Timer 16-bit Timer

8-bit Prescaler 8-bit Prescaler

32-bit Timer 32-bit Timer

16-bit Prescaler 16-bit Prescaler

Count up or down Count up or down

Wait-for-Trigger mode

DMA trigger

One-Shot timer mode

The timer stops counting and clears the bit

Periodic timer mode

Count up from 0x0 to loaded value & reloads with 0x0

Count down from its preloaded value & reloads with the preloaded value

Snap-shot mode- the actual free-running value of the timer at the time-out event is

loaded and the free-running value of the prescaler is loaded

33

Timer Use

Individual Concatenated

16/32 bit

GPTM Block

N/A

32/64 bit

GPTM Block

N/A

32-bit Timer

64-bit Timer

Real-Time Clock Timer Mode

Count up only Count up only

After reset, the counter is loaded with a value of 0x1

Input clock is required to be 32.768 KHz & it is then divided down to a 1-Hz

When count value matches the preloaded value, GPTM asserts and continues

counting until either a hardware reset, or it is disabled by software.

When the timer value reaches the terminal count, the timer rolls over and

continues counting up from 0x0.

34

Timer Use

Individual Concatenated

16/32 bit

GPTM Block

N/A

32/64 bit

GPTM Block

N/A

Input Edge-Count Mode

24-bit Timer Optional Prescaler

The maximum input frequency is of the system frequency

48-bit Timer Optional Prescaler

The maximum input frequency is of the system frequency

The timer is configured as a 24-bit or 48-bit up- or down-counting including the

optional prescaler with upper count value

Counting down: start value is initialized

Counting up : start value is 0x0

Capable of capturing three types of events

Rising edge

Falling edge

Both

Interrupts, ADC and/or a DMA trigger can be generated

35

How Input Edge-Count mode works

Start Value 0x000A

0x0009

0x0008

0x0007

Match Value 0x0006

Count

Timer stops,

Flags

asserted

Timer reload

on next cycle

Ignored Ignored

Count

Count

Count

Count

After the match value is reached in down-count mode, the counter is then

reloaded using the start value, and stopped

Input Signal

36

Input Edge-Time Mode

The maximum input frequency is of the system frequency

The timer is configured as a 24-bit or 48-bit up- or down-counting including the

Timer Use

Individual Concatenated

16/32 bit

GPTM Block

N/A

32/64 bit

GPTM Block

N/A

24-bit Timer Optional Prescaler

48-bit Timer Optional Prescaler

The timer is configured as a 24-bit or 48-bit up- or down-counting including the

optional prescaler with upper count value

Counting down: start value is initialized

Counting up : start value is 0x0

Capable of capturing three types of events

Rising edge

Falling edge

Both

Interrupts, ADC and/or a DMA trigger can be generated

After the event has been captured, the timer doesnt stop counting

37

How Input Edge-Time Mode works

Count value

loaded

Count value

loaded

Count value

loaded

Count

Start Value 0xFFFF

Z

X

Configured to capture rising edge events

Each time a rising event is detected, the count value is loaded

Y

Time

Input Signal

38

PWM Mode

The timer is configured as a 34-bit or 48-bit down-counter with a start value (and

thus period)

Timer Use

Individual Concatenated

16/32 bit

GPTM Block

N/A

32/64 bit

GPTM Block

N/A

24-bit Timer

48-bit Timer

thus period)

PWM frequency and period are synchronous events and therefore guaranteed

to be glitch free

Counting down until it reaches the 0x0 state

Wait-for-Trigger mode

On the next counter cycle in periodic mode, the counter reloads its start value

Capable of generating interrupts based on

Rising edge

Falling edge

Both

39

How PWM Mode works

PWM Signal

Asserts

Count

Start Value

Match value

0x0

PWM Signal

Deasserts

PWM Signal

Asserts

PWM Signal

Deasserts

PWM Signal

Asserts

Time

The output PWM signal asserts when the counter is at its start state

The output PWM signal deasserts when the counter value equals the mach

value

Capability of inverting the output PWM signal

0x0

0

1

Output

Signal

Time

40

Synchronizing GP Timer Blocks

Synchronize selected Timers to begin counting at the same time.

No interruption when the Timers are synchronized.

In concatenated mode, only the bit for Timer A must be set.

Mode Count Dir Time Out Action

32-bit One Shot - N/A

32-bit periodic Down Count value = ILR

Up Count value = 0

32-bit RTC Up Count value = 0

16-bit One Shot - N/A

16-bit Periodic Down Count value = ILR

Up Count value = 0

16-bit Edge-Count Down Count value = ILR

Up Count value = 0

16-bit Edge-Time Down Count value = ILR

Up Count value = 0

16-bit PWM Down Count value = ILR

41

General Purpose IO

Programmable pad configuration through GPIO module

Any GPIO can be an external interrupt source

GPIO banks P and Q can have individual interrupts for each pin (larger packages)

Toggle rate up to the CPU clock speed on the Advanced High-Performance

Bus

5-V-tolerant input/outputs

Programmable Drive Strength

2, 4, 8 mA or 8 mA with slew rate control, several pins have 18-mA drive strength

Programmable weak pull-up, pull-down, and open drain

Digital input enables

42

Stellaris

LM4F Analog Features

43

Analog-to-Digital Converter

Stellaris LM4F MCUs feature 2 ADC modules

(ADC0 and ADC1) that can be used to convert

continuous analog voltages to discrete digital

values

Each ADC module has 12-bit resolution

Each ADC module operates independently and

can therefore:

Execute different sample sequences

ADC

V

IN

V

OUT

V

I

N

44

Execute different sample sequences

Sample any of the 24 analog input channels

Generate different interrupts & triggers

44

Analog-to-Digital converter ADC Implementation in Stellaris LM4F MCUs

ADC0

ADC1

Input

Channels

Triggers

Interrupts/

Triggers

Interrupts/

Triggers

24

V

O

U

T

000

001

011

010

100

101

t

t

ADC Key Features

12-bit precision ADC

24 shared analog input channels

Single ended & differential input

configurations

On-chip internal temperature sensor

Flexible trigger control

Controller/ software

Timers

Analog comparators

PWM

GPIO

Hardware averaging of up to 64 samples

45

Maximum sample rate of one million

samples/second (1MSPS).

Selectable reference signals (VDDA,

GNDA or two external voltages*)

4 programmable sample conversion

sequencers

Hardware averaging of up to 64 samples

for improved accuracy

8 Digital comparators/ per ADC

Efficient transfers using DMA

Optional phase shift in sample time,

programmable from 22.5 to 337.5

*except on 64 pin packages

ADC Block Diagram

Digital readings

ADC

Trigger

Analog in

Ref. voltage

Analog

46

Analog

Comparator

The analog comparators may also be used as ADC trigger sources:

Allows the user to monitor a sensor value after it passes some

threshold voltage.

Conversions will only be triggered when the voltage is inside the

range of interest

Block Diagram & Signal Description

Reference

voltages to

specify the

voltages at

which ADC

converts to

a min/max

value

Analog Inputs

to ADC

47

Functional Block Diagram of an ADC Module

Sample Sequencers

ADCs on Stellaris LM4F devices collect and sample data using a programmable

sequence-based approach.

Each sample sequence is a fully programmable series of consecutive (back-to-back)

samples that allows the ADC module to collect data from multiple input sources without

having to be re-configured.

Each ADC module has 4 sample sequencers that control sampling and data capture.

All sample sequencers are identical except for the number of samples they can capture

48

and the depth of the FIFO.

To configure a sample sequencer, the following information is required:

Input source

Mode (single-ended, or differential)

Interrupt generation on sample completion

Indicator for the last sample in the sequence

48

ADC Sample Sequencers

Sequencer

Number of

Samples

Depth of

FIFO

SS 3 1 1

SS 2 4 4

SS 1 4 4

SS 0 8 8

DMA Operation: There is a dedicated DMA

channel for each ADC sample sequencer. Each

sample sequencer can transfer data

independently.

ADC Voltage Reference

ADC uses ADCV

REFA+

and ADCV

REFA-

reference

voltages to produce a conversion value.

Internal/ external reference voltages for ADC can

be selected using VREF bit in ADCCTL register.

V

DDA

GNDA

VREFA+

VREFA-

ADCV

REFA+

ADCV

REFA-

I

n

t

e

r

n

a

l

E

x

t

e

r

n

a

l

Resolution (in single-ended mode):

C

REF

ADC saturates in under-voltage and over-voltage

cases ( shaded region).

49 49

ADC Voltage Reference & Conversion Range

C

o

n

v

e

r

s

i

o

n

R

e

s

u

l

t

V

IN

0x000

ADCV

REFA- ADCV

REFA+

[ADCV

REFA-

+ ADCV

REFA+

]

2

0xFFF

0xC00

0x800

0x400

S

a

t

u

r

a

t

i

o

n

R

e

g

i

o

n

Range:

Differential Sampling

ADC also allows differential sampling of two analog input channels.

Differential input pair can be configured in ADCSSMUXn register.

Differential sampling can be enabled by setting Dn bit in ADCSSCTL0.

Differential input pair n samples the voltage difference (V

IN

) between consecutive

even and odd analog inputs channels.

0xFFF

S

a

t

u

r

a

t

i

o

n

R

e

g

i

o

n

50 50

ADC Conversion Range in Differential Mode

C

o

n

v

e

r

s

i

o

n

R

e

s

u

l

t

V

IN 0x000

0

0xC00

0x800

0x400

S

a

t

u

r

a

t

i

o

n

R

e

g

i

o

n

-VADCV

REF VADCV

REF

Where,

VADCV

REF

= ADCV

REFA+

- ADCV

REFA-

For conversion accuracy:

Resolution:

ADC conversions saturate in under-voltage and

over-voltage cases (shaded region).

Sample Phase Control

ADC Sample Phases shifts

ADC0 and ADC1 can be

operated from the same

trigger source.

If they are sampling data at

the same frequency, then start

of conversion can be delayed

in 15 discrete increments of

22.5from 0up to 337.5.

t

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 ADC

Sample

Clock

PH 0x0

(0)

PH 0x1

(22.5)

PH 0x1F

(337.5)

51 51

A

n

a

l

o

g

I

n

p

u

t

t

S1 S2 S3 S4 S5 S6 S7 S8

S1 S2 S3 S4 S5 S6 S7 S8

ADC1

ADC0

Skewed Sampling

Skewed Sampling

ADC0 & ADC1 can be used

out of phase of each other.

The sampled data can be

combined in the software.

This effectively doubles the

conversion bandwidth upto

2MSPS.

t

(337.5)

ADC Sample Phases

Hardware Sample Averaging Circuit

Hardware sample averaging circuit can be used to

generate higher precision results.

Up to 64 samples can be accumulated and averaged

to form a single data entry in the sequencer FIFO.

By default, hardware sample averaging circuit is off.

All the data from the converter passes through

the sequencer FIFO.

Averaging is controlled by ADCSAC register.

S

a

m

p

l

e

s

t

A+B+C+D

A

B

C

D

A

B

C

D

52

All channels are averaged equally irrespective of

their configuration (single ended or differential).

Example: if AVG value in ADCSAC register is0x02,

then 4x averaging will be done. If IE bit in

ADCSSCTL0 register is set, then an interrupt will be

generated when FIFO gets second data entry.

Tradeoff: Throughput is decreased proportionally to

the number of samples in the averaging calculation.

52

Sample Averaging Example

A+B+C+D

4

A+B+C+D

4

FIFO

INT

Internal Temperature Sensor

R

e

f

e

r

e

n

c

e

V

o

l

t

a

g

e

(

V

)

Temperature(C)

2.7

1.633

0.3

Internal temperature sensor module consists of:

Band gap reference circuit that provides

reference voltage to various analog

peripherals.

On-chip internal temperature sensor.

53 53 Internal Temperature Sensor Characteristics

125 25 -55

T

e

m

p

e

r

a

t

u

r

e

(

C

)

ADC Output

147.5

91.2

-77

0xFFF 0x800 0x0 0xC00 0x400

34.9

-21.3

Internal temperature sensor serves following key

purposes:

Senses die temperature for reliable system

operation.

Provides temperature measurements in order to

calibrate hibernation modules RTC trim value.

The temperature can be sampled by setting TSn

bit in ADCSSCTLn register.

Digital Comparator Unit

A digital comparator compares the ADC modules output

with user programmable limits. Depending on the result of

the comparison, a processor interrupt or a trigger to the

PWM module can be generated.

Each ADC module contains 8 digital comparators.

Operational Modes:

Always Mode

Once Mode

Hysteresis Mode

M

i

d

B

a

n

d

COMP1

H

i

g

h

B

a

n

d

V

IN

54

Hysteresis Always Mode

Modes can be selected using CIM or CTM bit in ADCCTLn

register.

Functional Ranges:

Low Band

Mid Band

High Band

Functional Ranges can be selected using COMP0 and

COMP1 bits in ADCDCCMPn register.

Always, COMP1 COMP0.

54

Digital Comparator Functional Ranges

M

i

d

B

a

n

d

COMP0

t

L

o

w

B

a

n

d

Analog Comparator Key Features

Analog comparator compares two analog

voltages and provides a logical output

depending upon the result of the comparison.

3 analog comparators integrated in Stellaris

MCUs can be independently used to:

Compare two analog signals and replace an

external/discrete analog comparator to save

board space and system cost.

V

IN-

V

IN-

(external)

V

IN+

(internal

ref. or external)

V

OUT

55

Drive an external pin

Trigger an ADC

Signal an application using interrupts

55

V

IN+

V

OUT

1 1

0 0 0

Using Analog Comparators Independently

Generate an interrupt Trigger an ADC

Any Signal

Analog Comparator: Inputs & Output

t

t

Block Diagram & Signal Description

Analog Comparator

Ns positive input

Analog Comparator

Ns negative input

C1o

C2o

Analog Comparator

Ns output

C1o

Output to trigger

an ADC

56

Functional Block Diagram of Analog Comparator Module

C0o

Stellaris

LM4F Communications

57

Synchronous Serial Interface (SSI)

Up to 4 SSI modules

Programmable interface operation for Freescale SPI, MICROWIRE, and Texas

Instruments synchronous serial interfaces

Programmable clock bit rate and prescaler with SSI slave clock frequencies up

to 1/6

th

of the system clock

Separate transmit and receive FIFOs, 16 bits wide, 8 locations deep

58

Programmable data frame size from 4 to 16 bits

Internal loopback test mode for diagnostic/debug testing

Efficient transfers using Micro Direct Memory Access Controller (DMA)

Separate channels for transmit and receive

Receive single request asserted when data is in the FIFO; burst request asserted

when FIFO contains 4 entries

Transmit single request asserted when there is space in the FIFO; burst request

asserted when FIFO contains 4 entries

Inter-Integrated Circuit (I

2

C)

Up to 6 I

2

C Modules

Master and slave modes supported

Simultaneous master and slave operation

Master arbitration, clock synchronization, multi-master support, and 7-bit

addressing modes

There are a total of four I

2

C modes: There are a total of four I

2

C modes:

Master Transmit, Master Receive

Slave Transmit, Slave Receive

Standard (100 Kbps), Fast (400 Kbps), and High (3.4 Mbps) speeds supported

Master and slave interrupts support

I

2

C master generates interrupts when a transmit or receive operation completes (or

aborts).

I

2

C slave generates interrupts when data has been sent or requested by a master.

59

Universal Asynchronous Receiver/Transmitter (UART)

Up to 8 UARTs

Each UART has:

Separate transmit and receive FIFOs

Programmable FIFO length

FIFO trigger levels of 1/8, 1/4, 1/2, 3/4, and 7/8

Programmable baud-rate generator allowing rates up to speeds up to 10Mbps

Standard asynchronous communication bits for start, stop and parity

False start bit detection

Line-break generation and detection

Fully programmable serial interface characteristics: Fully programmable serial interface characteristics:

5, 6, 7, or 8 data bits

Even, odd, stick, or no-parity bit generation/detection

1 or 2 stop bit generation

IrDA serial-IR (SIR) encoder/decoder providing:

Programmable use of IrDA Serial InfraRed (SIR) or UART input/output

Support of IrDA SIR encoder/decoder functions for data rates up to 115.2 Kbps half-duplex

Support of normal 3/16 and low-power (1.41-2.23 s) bit durations

Programmable internal clock generator enabling division of reference clock by 1 to 256 for low-

power mode bit duration

ISO 7816 Support

60

Universal Asynchronous Receiver/Transmitter (UART)

LIN protocol support

EIA-485 9-bit support

Standard FIFO-level and End-of-Transmission interrupts

Efficient transfers using Micro Direct Memory Access Controller

(DMA)

Separate channels for transmit and receive Separate channels for transmit and receive

Receive single request asserted when data is in the FIFO; burst request

asserted at programmed FIFO level

Transmit single request asserted when there is space in the FIFO; burst

request asserted at programmed FIFO level

61

Universal Serial Bus (USB)

Integrated controller and PHY

USB 2.0 Full Speed (12 Mbps) operation

Devices with OTG/Host/Device

Transfer: Control, Interrupt, Bulk and Isochronous

16 Endpoints

0 and 1 hardwired for control transfers (one in, one out)

Remaining 14 may be configured by software.

2 KB Dedicated Endpoint Memory

Direct Memory Access

One endpoint may be defined for double-buffered 1023-byte isochronous packet size.

USB-IF Compliance

TI is a member of the USB Implementers Forum.

Complies with USB-IF certification standards

TIs Stellaris VID available for sublicense (with assigned PIDs).

62

Controller Area Network (CAN)

2CAN controllers

Each supports CAN protocol version 2.0 part A/B

Bit rates up to 1Mb/s

32 message objects, each with own identifier mask

Maskable interrupt Maskable interrupt

Disable automatic retransmission mode for TTCAN

Programmable loop-back mode for self test operation

63

Stellaris

LM4F Motion Control

64

Pulse Width Modulation (PWM)

2 PWM modules with 4 generators each. Each

generator contains:

One 16-bit counter

Runs in down or up/down mode

Output frequency controlled by a 16-bit load value

Load value updates can be synchronized

Produces output signals at zero and load value

Two comparators Two comparators

Comparator value updates can be synchronized

Produces output signals on match

PWM generator

Output constructed based on actions taken as a

result of the counter and comparator output signals

Produces two independent PWM signals

65

Pulse Width Modulation (PWM) cont.

Dead band generator

Produces two PWM signals with programmable dead band delays suitable

for driving a half-H bridge

Can be bypassed, leaving input PWM signals unmodified

Output control block

PWM output enable of each PWM signal

Optional output inversion of each PWM signal

Optional fault handling for each PWM signal Optional fault handling for each PWM signal

Synchronization of timers in the PWM generator blocks

Synchronization of timer/comparator updates across the PWM generator

blocks

Interrupt status summary of the PWM generator blocks

66

PWM Block Diagram

Timer

Timer

match

Preliminary PWM pair with

To PWM pins

Compare

Signal

Generation

Dead-band

Generation

Output Logic

67

match

events

Preliminary

PWM

PWM pair with

Dead-band

To PWM pins

The PWM module essentially consists of a timer, a configurable

comparison module, and three stages of signal generation and

conditioning logic.

PWM Compare Event Waveforms

Count Down Mode Count Down Mode

Asymmetrical Asymmetrical

Waveform Waveform

CMPA CMPA

CMPB CMPB

. .. .. .. .

. .. .. .. .

. .. .. .. . . .. .. .. .

. .. .. .. . . .. .. .. .

Match events produce signals, which can be used to drive

positive or negative edges of a PWM. Each counter may

generate up to two PWMs using different combinations of

compare events.

68

PWM Compare Event Waveforms

Count Up and Down Mode Count Up and Down Mode

Symmetrical Symmetrical

Waveform Waveform

CMPA CMPA

CMPB CMPB

. .. .. .. .

. .. .. .. .

. .. .. .. .

. .. .. .. .

. .. .. .. . . .. .. .. .

. .. .. .. . . .. .. .. .

69

Up-down mode is well suited to symmetrical, center-aligned

waveforms.

PWM Dead bands and Output Logic

PWM waveforms from the

counters may be used as is, or the

dead band and output logic can

produce a complement waveform

to one of them.

No dead band

70

The complement waveform may

optionally have dead bands

inserted, which are convenient for

some motor control applications.

Dead band

Original wave

Fault-condition Interrupts

A fault condition is one in which the controller

must be signaled to stop normal PWM function

and then sets the outputs to a safe state.

There are two basic situations where this

becomes necessary: becomes necessary:

The controller is stalled and cannot perform the

necessary computation in the time required for

motion control (Stall signal from internal debugger)

An external error or event is detected (FAULTn

pin)

71

Quadrature Encoder Interface (QEI)

Also known as a 2-channel incremental encoder, a quadrature encoder interface converts

angular displacement into a pulse signal. It is typically used in motion control applications,

and can track the position, velocity, and direction of a motor

Stellaris QEI features:

Includes two quadrature encoder interface (QEI) modules

Position integrator that tracks the encoder position Position integrator that tracks the encoder position

Programmable noise filter on the inputs

Velocity capture using built-in timer

Interrupt generation on:

Index pulse

Velocity-timer expiration

Direction change

Quadrature error detection

72

Quadrature Encoder Interface (QEI)

A digital (angular) position sensor

slots spaced deg. apart

photo sensors spaced /4 deg. apart

light source (LED)

/4

shaft rotation

Ch. A

Ch. B

Quadrature Output from Photo Sensors

Incremental Optical Encoder

73

Quadrature Encoder Interface (QEI)

(00) (11)

(10) (01)

(A,B) =

10

increment

counter

decrement

counter

Position resolution is /4 degrees

Ch. A

Ch. B

00

01

11

Quadrature Decoder

State Machine

Illegal

Transitions;

generate

phase error

interrupt

74

You might also like

- Astm D2095 PDFDocument3 pagesAstm D2095 PDFTaher Hama AmeenNo ratings yet

- Ppii Tutorial ManualDocument145 pagesPpii Tutorial ManualFabio BolivarNo ratings yet

- Engineering Specification: ESFU5A-8079-AADocument5 pagesEngineering Specification: ESFU5A-8079-AAjavier ortizNo ratings yet

- Pic 24 Data SheetDocument554 pagesPic 24 Data SheetLewis LiddellNo ratings yet

- GPS ControlerDocument20 pagesGPS ControlerDileep guptaNo ratings yet

- Minggu 4 Uc 32bitDocument41 pagesMinggu 4 Uc 32bitPahala SamosirNo ratings yet

- Datasheet Am3359Document253 pagesDatasheet Am33591jzksharkNo ratings yet

- UC ATmega328 328P SummaryfvafdvdfdfvdfDocument24 pagesUC ATmega328 328P SummaryfvafdvdfdfvdfKevin SerranoNo ratings yet

- MC9S08SH32Document328 pagesMC9S08SH32jahenNo ratings yet

- Infineon-Traveo II CYT2B7 Series-DataSheet-v11Document167 pagesInfineon-Traveo II CYT2B7 Series-DataSheet-v11umesh.joshitataautoNo ratings yet

- Es Unit1Document83 pagesEs Unit1venneti kiranNo ratings yet

- Automatic Temperature ControllerDocument24 pagesAutomatic Temperature Controllerarunbera00792% (12)

- New Chapter 2 Micro ArchitectureDocument25 pagesNew Chapter 2 Micro ArchitectureAmzar ShukriNo ratings yet

- WPC 8769 LDGDocument5 pagesWPC 8769 LDGOsman EfendiNo ratings yet

- ATM Terminal Design Based On Figure Print Recognition DocuDocument115 pagesATM Terminal Design Based On Figure Print Recognition DocuPraveen NaiduNo ratings yet

- 1 02 - Embedded Hardware Units and Devices in A SysteDocument23 pages1 02 - Embedded Hardware Units and Devices in A SysteChristy PollyNo ratings yet

- Microcontroller: Micro-ControllerDocument14 pagesMicrocontroller: Micro-ControllerGarima JainNo ratings yet

- AT91 Sam 7 X 256Document687 pagesAT91 Sam 7 X 256anhminh81No ratings yet

- MC9S08QE128RMDocument346 pagesMC9S08QE128RMSergio ContrerasNo ratings yet

- Embedded System Architecture SlidesDocument40 pagesEmbedded System Architecture SlidesKiran Tk100% (1)

- ZW 0301Document25 pagesZW 0301jojo325No ratings yet

- Atxmega16 128a4uDocument121 pagesAtxmega16 128a4udiegoquindioNo ratings yet

- Es Unit1Document83 pagesEs Unit1venneti kiranNo ratings yet

- ATxmega 128 A3 UDocument141 pagesATxmega 128 A3 UsanapashokNo ratings yet

- Infineon-TRAVEO T2G CYT2B9 Series-DataSheet-v11 00-ENDocument171 pagesInfineon-TRAVEO T2G CYT2B9 Series-DataSheet-v11 00-ENumesh.joshitataautoNo ratings yet

- 3 Embedded Systems - Raj KamalDocument37 pages3 Embedded Systems - Raj KamalAshokkumar ManickamNo ratings yet

- At 90 Can 128Document428 pagesAt 90 Can 128Mahmoud AlNo ratings yet

- MC9S08JM60Document373 pagesMC9S08JM60Mohamed SaadNo ratings yet

- 5-En - stm32l4 System RCCDocument25 pages5-En - stm32l4 System RCCYohanes ErwinNo ratings yet

- Module 1 - 411Document43 pagesModule 1 - 411رفال الجهنيNo ratings yet

- AM335x DatasheetDocument197 pagesAM335x DatasheetsitasinanNo ratings yet

- Pic Microcontroller Block DiagramDocument15 pagesPic Microcontroller Block DiagramNandaKiranNo ratings yet

- Lpc1343 IntroductionDocument11 pagesLpc1343 Introductionshahbazalam4a5No ratings yet

- Semiconductor MPC565/MPC566 MPC565/MPC566 RISC MCU With Code Compression OptionDocument12 pagesSemiconductor MPC565/MPC566 MPC565/MPC566 RISC MCU With Code Compression OptionVicente AlvarezNo ratings yet

- 24 FJ 128 Ga 306Document406 pages24 FJ 128 Ga 306Kyaw Htet LuNo ratings yet

- 20 Pagini - 16F877.UnlockedDocument13 pages20 Pagini - 16F877.UnlockedMariusNastaseNo ratings yet

- ATmega324PB DTEDocument19 pagesATmega324PB DTEAhmad MaulanaNo ratings yet

- PIC24FJ128GA606 Microchip PDFDocument470 pagesPIC24FJ128GA606 Microchip PDFSoro FoxNo ratings yet

- Atmel - ATTINY PDFDocument497 pagesAtmel - ATTINY PDFKishore GurramNo ratings yet

- Reset Circuitry & Watchdog TimersDocument51 pagesReset Circuitry & Watchdog TimersSangeeta RanjanNo ratings yet

- 4.2 Features of Pic MicrocontrollerDocument7 pages4.2 Features of Pic MicrocontrollerratheeshbrNo ratings yet

- MPC5200CVR400BDocument78 pagesMPC5200CVR400BLiubomir MilanoffNo ratings yet

- C8051F326Document140 pagesC8051F326jpserafiniNo ratings yet

- KTU - CST202 - Computer Organization and Architecture: Ontrol Ogic EsignDocument17 pagesKTU - CST202 - Computer Organization and Architecture: Ontrol Ogic EsignJoel K SanthoshNo ratings yet

- Intel 80586 (Pentium)Document24 pagesIntel 80586 (Pentium)Soumya Ranjan PandaNo ratings yet

- Self Study: Atmel Atmega128 Architecture: Anupama KR & Meetha.V.Shenoy Embedded System Design 8051Document5 pagesSelf Study: Atmel Atmega128 Architecture: Anupama KR & Meetha.V.Shenoy Embedded System Design 8051Shivam ShuklaNo ratings yet

- At Mega 64Document392 pagesAt Mega 64Jackson Manrique GutierrezNo ratings yet

- Compact DeviceDocument57 pagesCompact Devicesriram kantipudiNo ratings yet

- Unit 4Document51 pagesUnit 4Vyshnavi Challa ObullaNo ratings yet

- Pic 16F877Document115 pagesPic 16F877narendramaharana39100% (1)

- COA Module 4 FinalDocument22 pagesCOA Module 4 FinalAkhil KrishnaNo ratings yet

- Embedded ARM Starter KitDocument3 pagesEmbedded ARM Starter KitEmblitz Rajajinagar100% (2)

- Msp430 Training ManualDocument106 pagesMsp430 Training ManualOhm PrakashNo ratings yet

- Datasheet PDFDocument12 pagesDatasheet PDFThong ChanNo ratings yet

- (EN) MG32F02A128 064 DataSheet V1.20Document111 pages(EN) MG32F02A128 064 DataSheet V1.20Super ManNo ratings yet

- 02 AVR-Micro ControllerDocument59 pages02 AVR-Micro ControllerPriscillaNo ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- 8051 Microcontroller: An Applications Based IntroductionFrom Everand8051 Microcontroller: An Applications Based IntroductionRating: 5 out of 5 stars5/5 (6)

- PlayStation 2 Architecture: Architecture of Consoles: A Practical Analysis, #12From EverandPlayStation 2 Architecture: Architecture of Consoles: A Practical Analysis, #12No ratings yet

- Practical Data Acquisition for Instrumentation and Control SystemsFrom EverandPractical Data Acquisition for Instrumentation and Control SystemsNo ratings yet

- K ServerDocument11 pagesK Serveraryatel26No ratings yet

- Group1 OB Ward-Case StudyDocument10 pagesGroup1 OB Ward-Case StudyAnthony Seth AguilandoNo ratings yet

- EYE Emergency Manual An Illustrated Guide: Second EditionDocument51 pagesEYE Emergency Manual An Illustrated Guide: Second EditionMin MawNo ratings yet

- 13.8KV Unit Substation-InstallationDocument1 page13.8KV Unit Substation-InstallationMuhammad IrfanNo ratings yet

- PMLS 2 Midterm 1Document14 pagesPMLS 2 Midterm 1ematias230000001830No ratings yet

- TTSL CatalogDocument3 pagesTTSL CatalogNguyen CuongNo ratings yet

- Nuccore ResultDocument2,189 pagesNuccore ResultJohanS.Acebedo0% (1)

- Aujeszky's DiseaseDocument30 pagesAujeszky's DiseaseFrances ChewNo ratings yet

- Optimization of Component of Excavator BucketDocument3 pagesOptimization of Component of Excavator BucketijsretNo ratings yet

- Cybernetic Tradition 1Document15 pagesCybernetic Tradition 1Jenina CuevasNo ratings yet

- CVDocument1 pageCVSiddharth ChauhanNo ratings yet

- Chloropene Rubber-CRDocument9 pagesChloropene Rubber-CRreilyshawnNo ratings yet

- Horn AntennasDocument29 pagesHorn AntennasAbderrahmane BadisNo ratings yet

- Electrochemistry FR Worksheet Answers Key PDFDocument22 pagesElectrochemistry FR Worksheet Answers Key PDFEmily toaNo ratings yet

- Industrial Pressure and Vacuum Switches: 9012G, 9016G, and XMLA, B, C, DDocument104 pagesIndustrial Pressure and Vacuum Switches: 9012G, 9016G, and XMLA, B, C, DJohn KingNo ratings yet

- RoboticsbasicDocument52 pagesRoboticsbasicdanvicNo ratings yet

- Technical Information and Configuration: Progressive Safety Gear G01Document16 pagesTechnical Information and Configuration: Progressive Safety Gear G01Ali DiabNo ratings yet

- IDFT & CONVOLUTIONS - PROBLEMS Part 6Document19 pagesIDFT & CONVOLUTIONS - PROBLEMS Part 6Abishek RajeshNo ratings yet

- Curriculum Vitae: Personal InformationDocument10 pagesCurriculum Vitae: Personal InformationBehairy AhmedNo ratings yet

- Cadôr - Books About Nothing PDFDocument4 pagesCadôr - Books About Nothing PDFFelipeCussen100% (1)

- Unit 3Document90 pagesUnit 3ranNo ratings yet

- 145kV GTP BPDBDocument4 pages145kV GTP BPDBJRC TestingNo ratings yet

- Halal Cosmetics NewDocument2 pagesHalal Cosmetics Newahmad100% (1)

- Simple Annuities FinalDocument95 pagesSimple Annuities FinalMae Ann KongNo ratings yet

- Amanita MuscariaDocument16 pagesAmanita MuscariaPedro Rodrigues100% (1)

- Biotechnology & Biochemical Engineering: ObjectivesDocument9 pagesBiotechnology & Biochemical Engineering: ObjectivesSusmit NimjeNo ratings yet

- Lec4 - Shear of Thin Walled BeamsDocument52 pagesLec4 - Shear of Thin Walled Beamsamber batoolNo ratings yet