Professional Documents

Culture Documents

VHDL Lab File

Uploaded by

Vishal PathakOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

VHDL Lab File

Uploaded by

Vishal PathakCopyright:

Available Formats

VHDL

Lab File

SUBMITTED BY

Giric Goyal

A2305208361

Roll No 51!

5"S3 #Y$

BTE"H #"SE$

SESSI%N& 2008'2012

INDE(

SNo DES"RI)TI%N Da*+ Si,-a*.r+

E()ERIMENT N% 2

AIM& To implement HALF ADDER in VHDL using dataflow, behavioral

and structural stle of modeling!

T/+ory&

Half adder is the most basic digital arithmetic circuit! "t is a logical circuit that

performs an addition operation on two binar digits! "t is a combinational circuit

which produces a sum and a carr value, which are both binar digits!

A half adder has two inputs, generall labeled A and #, and two outputs, the $sum% &

and $carr flag% '!

& is the two(bit $)*R gate% of A and #, and ' is the $A+D gate% of A and #!

&, A -or #

',A and #

Following is the truth table for a half adder is .

A B S "

/ / / /

/ 0 0 /

0 / 0 /

0 0 / 0

Da*a0lo1 co2+ 0or Hal0 A22+r

"%DE& librar ieee1

use ieee!std2logic20034!all1

entit half2adder is

port 5a,b6in bit1

sum,carr6out bit71

end half2adder1

architecture E of half2adder is

begin

sum8, a -or b1

carr8,a and b1

end E1

*9T:9T ;AVEF*R<6

B+/a3ioral co2+ 0or Hal0 A22+r

"%DE& librar ieee1

use ieee!std2logic20034!all1

entit half2adder is

port 5a,b6 in bit1

sum,carr6out bit71

end half2adder1

architecture E of half2adder is

begin

process5a,b7

variable =6 bit2vector5/ to 071

begin

= 6,a > b1

case = is

when ?//?,@ sum8,A/A1

carr8,A/A1

when ?/0?,@ sum8,A0A1

carr8,A/A1

when ?0/?,@ sum8,A0A1

carr8,A/A1

when ?00?,@ sum8,A/A1

carr8,A0A1

end case1

end process 1

end E1

*9T:9T ;AVEF*R<6

S*r.c*.ral co2+ 0or Hal0 A22+r

"%DE& librar ieee1

use ieee!std2logic20034!all1

entit -org is

port 5a,b6 in bit1

B6out bit71

end -org1

architecture E of -org is

begin

B8, a -or b1

end E1

entit andg is

port 5a,b6 in bit1

B6 out bit71

end andg1

architecture E0 of andg is

begin

B8, a and b1

end E01

entit half2adderg is

port 5a0,b6in bit1

sum,carr6out bit71

end half2adderg1

architecture EC of half2adderg is

component -org

port 5a,b6in bit1

B6out bit71

end component1

component andg

port 5a,b6 in bit1

B6 out bit71

end component1

begin

AD6 -org port map 5a0,b,sum71

AC6 andg port map 5a0,b,carr71

end EC1

*9T:9T ;AVEF*R<6

E()ERIMENT N% 3

AIM& To implement F9LL ADDER in VHDL using dataflow, behavioral

and structural stle of modeling!

T/+ory&

Full adder is a combinational circuit that performs an addition operation on three

binar digits! "t produces a sum and a carr value, which are both binar digits!

A half adder has three inputs, generall labelled A, #, and 'in, and two outputs, the

$sum% & and $carr flag% 'out!

& is the two(bit $)*R gate% of A, #, and 'in!

&, A -or # -or 'in

'out,A!#E 5A -or #7 'in

Following is the truth table for a full adder is(

A B "i- S "o.*

/ / / / /

/ / 0 0 /

/ 0 / 0 /

/ 0 0 / 0

0 / / 0 /

0 / 0 / 0

0 0 / / 0

0 0 0 0 0

Da*a0lo1 co2+ 0or 4.ll A22+r

"%DE

librar ieee1

use ieee!std2logic20034!all1

entit full2adder0 is

port 5a,b,c6in bit1

sum,carr6out bit71

end full2adder01

architecture e0 of full2adder0 is

begin

carr8,5a and b7 or 5b and c7 or 5c and a71

sum8,a -or b -or c1

end e01

*9T:9T ;AVEF*R<6

B+/a3ioral co2+ 0or 0.ll a22+r

"%DE&

librar ieee1

use ieee!std2logic20034!all1

entit fulladder is

port5a6in bit2vector5/ to C71

sum,carr6out bit71

end fulladder1

architecture e0 of fulladder is

begin

:06process5a7

begin

case a is

when ?///?,@sum8,A/A1carr8,A/A1

when ?//0?,@sum8,A0A1carr8,A/A1

when ?/0/?,@sum8,A0A1carr8,A/A1

when ?/00?,@sum8,A/A1carr8,A0A1

when ?0//?,@sum8,A0A1carr8,A/A1

when ?0/0?,@sum8,A/A1carr8,A0A1

when ?00/?,@sum8,A/A1carr8,A0A1

when ?000?,@sum8,A0A1carr8,A0A1

end case1

end process p01

*9T:9T ;AVEF*R<6

S*r.c*.ral co2+ 0or 0.ll a22+r

'*DE6

librar ieee1

use ieee!std2logic20034!all1

entit andg is

port 5a,b6in bit1

B6out bit71

end andg1

architecture E of andg is

begin

B8, a and b1

end E1

entit org is

port 5a,b,c6 in bit1

B6 out bit71

end org1

architecture E0 of org is

begin

B8,a or b or c1

end E01

entit -org is

port5a,b,c6in bit1

B6out bit71

end -org1

architecture EC of -org is

begin

B8,a -or b -or c1

end EC1

entit full2adderg is

port 5a0,b,c6in bit1

sum,carr6out bit71

end full2adderg1

architecture ED of full2adderg is

component andg

port 5a,b6in bit1

B6out bit71

end component1

component org

port 5a,b,c6 in bit1

B6 out bit71

end component1

component -org

port5a,b,c6in bit1

B6out bit71

end component1

signal -0,-C,-D6bit1

begin

A46 andg port map 5a0,b,-071

AC6 andg port map 5b,c,-C71

AD6 andg port map 5a0,c,-D71

*R06 org port map 5-0,-C,-D,sum71

)*R06 -org port map 5a0,b,c,carr71

end ED1

*9T:9T ;AVEF*R<6

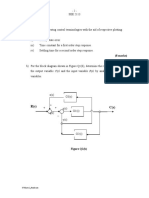

E()ERIMENT N% !

AIM& To implement a 4)0 multiple-er in VHDL using dataflow,

behavioral and structural stle of modeling!

Da*a0llo1 co2+ 0or ! *o 1 5.l*i6l+7+r&

F9+'T"*+6F,55d/ and 5not s/7 and 5not s077 or

5d0 and 5not s07 and s/7 or

5dC and s0 and 5not s/77 or

5dD and s/ and s077

'*DE6

librar ieee1

use ieee!std2logic20034!all1

entit mu-40 is

port 5a,b,c,d,s0,sC6in bit1

B6out bit71

end mu-401

architecture e0 of mu-40 is

begin

B8,555not s07 and 5not sC7 and a7 or 55not s07 and 5sC7 and b7 or 55s07 and 5not sC7 and c7 or 55s07 and

5sC7 and d771

end e01

*9T:9T ;AVEF*R<

B+/a3ioral co2+ 0or ! *o 1 5.l*i6l+7+r

TR9TH TA#LE6

"G: *G:

&/ &0 F

/ / D/

/ 0 D0

0 / DC

0 0 DD

'*DE6

librar ieee1

use ieee!std2logic20034!all1

entit mu-4 is

port5a,b,c,d,s0,sC6in bit1

B6out bit71

end mu-41

architecture e0 of mu-4 is

begin

process5a,b,c,d,s0,sC7

begin

if s0>sC,?//?

then B8,a1

elsif s0>sC,?/0?

then B8,b1

elsif s0>sC,?0/?

then B8,c1

else B8,d1

end if1

end process1

end e01

*9T:9T ;AVEF*R<6

S*r.c*.ral co2+ 0or !(1 5.l*i6l+7+r&

'*DE6 librar ieee1

use ieee!std2logic20034!all1

entit mu-4str is

port5d/,d0,dC,dD,s/,s06in std2logic16out std2logic71

end mu-4str1

architecture gate of mu-4str is

component not0

port5a6in std2logic16out std2logic71

end component1

component andD

port5a,b,c6in std2logic16out std2logic71

end component1

component or4

port5a,b,c,d6in std2logic16out std2logic71

end component1

signal -0,-C,-D,-4,-H,-36std2logic1

begin

u/6not0 port map5s/,-071

u06not0 port map5s0,-C71

uC6andD port map5-0,-C,d/,-D71

uD6andD port map5-0,s0,d0,-471

u46andD port map5-C,s/,dC,-H71

uH6andD port map5s/,s0,dD,-371

u36or4 port map5-D,-4,-H,-3,71

end gate1

*9T:9T ;AVEF*R<6

E()ERIMENT N% 5

AIM& To implement a D)I decoder in VHDL using dataflow, behavioral

and structural stle of modeling!

T/+ory&

A 2+co2+r is a device which does the reverse of an encoder, undoing the encoding so

that the original information can be retrieved! The same method used to encode is

usuall Just reversed in order to decode!

"n digital electronics, a decoder can taKe the form of a multiple(input, multiple(

output logic circuit that converts coded inputs into coded outputs, where the input

and output codes are different! e!g! n(to(C

n

, binar(coded decimal decoders! Enable

inputs must be on for the decoder to function, otherwise its outputs assume a single

?disabled? output code word! Decoding is necessar in applications such as

data multiple-ing, L segment displa and memor address decoding!

Da*a0lo1 co2+ 0or 3&8 2+co2+r&

'*DE6 librar ieee1

use ieee!std2logic20034!all1

entit decoder is

port5-,,B,enable6in bit1a,b,c,d,e,f,g,h6out bit71

end decoder1

architecture deco0 of decoder is

begin

a8,55not -7and 5not 7and 5not B771

b8,55not -7and 5not 7and B71

c8,55not -7and and 5not B771

d8,55not -7and and B71

e8,5- and 5not 7and 5not B771

f8,5- and 5not 7and B71

g8,5- and and 5not B771

h8,5- and and B71

end deco01

*9T:9T ;AVEF*R<

S*r.c*.ral co2+ 0or 3&8 2+co2+r&

'*DE6 librar ieee1

use ieee!std2logic20034!all1

entit notg is

port5a6in bit1

b6 out bit71

end notg1

architecture e0 of notg is

begin

b8, not a1

end architecture1

entit andg is

port5a,b,c6in bit1

d6 out bit71

end andg1

architecture eC of andg is

begin

d8, a and b and c1

end architecture1

entit main is

port5 a6 in bit2vector5/ to C71

d6 out bit2vector5/ to L771

end main1

architecture main of main is

component notg is

port5a6in bit1

b6 out bit71

end component1

component andg is

port5a,b,c6in bit1

d6 out bit71

end component1

signal -,,B6bit1

begin

-06notg port map5a5/7,-71

-C6notg port map5a507,71

-D6notg port map5a5C7,B71

-46andg port map5-,,B,d5/771

-H6andg port map5-,,a5C7,d50771

-36andg port map5-,a507,B,d5C771

-L6andg port map5-,a507,a5C7,d5D771

-I6andg port map5a5/7,,B,d54771

-M6andg port map5a5/7,,a5C7,d5H771

-0/6andg port map5a5/7,a507,B,d53771

-006andg port map5a5/7,a507,a5C7,d5L771

end architecture1

*9T:9T ;AVEF*R<

B+/a3ioral co2+ 0or 3&8 2+co2+r&

'*DE6 librar ieee1

use ieee!std2logic20034!all1

entit decoder is

port 5s6out bit2vector5/ to L71

a6in bit2vector5/ to C771

end decoder1

architecture behaviour of decoder is

begin

process5a7

begin

case a is

when ?///? ,@ s8,?0///////?1

when ?//0? ,@ s8,?/0//////?1

when ?/0/? ,@ s8,?//0/////?1

when ?/00? ,@ s8,?///0////?1

when ?0//? ,@ s8,?////0///?1

when ?0/0? ,@ s8,?/////0//?1

when ?00/? ,@ s8,?//////0/?1

when ?000? ,@ s8,?///////0?1

end case1

end process1

end behaviour1

*9T:9T ;AVEF*R<

E()ERIMENT N% 6

AIM& To implement a D, T, &(R, N(O Flip Flop using behavioural stle of

modeling!

T/+ory&

D 4LI) 4L%) & The P output alwas taKes on the state of the D input at the moment

of a rising clocK edge 5or falling edge if the clocK input is active low7!

QLR

"t is called

the D flip(flop for this reason, since the output taKes the value of

the D input or Data input, and Delays it b one clocK count! The D flip(flop can be

interpreted as a primitive memor cell, Bero(order hold, or dela line!

Truth table6

"loc8 D 9 9

6r+3

Rising

edge

/ / )

Rising

edge

0 0 )

+on(Rising ) P

prev

B+/a3ioral co2+ 0or D 0li6 0lo6&

'*DE6 librar ieee1

use ieee!std2logic20034!all1

librar ieee1

use ieee!std2logic20034!all1

entit diff is

port5d,clK6in bit1

=,=bar6inout bit71

end diff1

architecture behav of diff is

begin

process5d,clK7

begin

if clK,A0A and clKA event

then

=8, d1

=bar8, not d1

end if1

end process1

end behav1

*9T:9T ;AVEF*R<

T 4LI) 4L%) &

"f the T input is high, the T flip(flop changes state 5?toggles?7 whenever the clocK

input is strobed! "f the T input is low, the flip(flop holds the previous value! This

behavior is described b the characteristic e=uation6

5or, without benefit of the )*R operator, the

e=uivalent6 7

and can be described in a truth table6

T 4li6'4lo6 o6+ra*io-

Q3R

"/arac*+ri:*ic *a;l+ E7ci*a*io- *a;l+

T Q Q

next

"o55+-* Q Q

next

T "o55+-*

/ / / hold state 5no clK7 / / / +o change

/ 0 0 hold state 5no clK7 0 0 / +o change

0 / 0 toggle / 0 0 'omplement

0 0 / toggle 0 / 0 'omplement

B+/a3ioral co2+ 0or T 0li6 0lo6&

'*DE6 librar ieee1

use ieee!std2logic20034!all1

entit tiff is

port5t,clK6in bit1

=,=bar6inout bit71

end tiff1

architecture behav of tiff is

begin

process5t,clK7

begin

if clK,A0A and clKA event

then

=8,not t1

=bar8,t1

end if1

end process1

end behav1

*9T:9T ;AVEF*R<

SR 4LI) 4L%) &

The fundamental latch is the simple SR flip-flop, where & and R stand

for set and reset, respectivel! "t can be constructed from a pair of cross(

coupled +A+D or +*R logic gates! The stored bit is present on the output marKed P!

+ormall, in storage mode, the & and R inputs are both low, and feedbacK maintains

the P and P outputs in a constant state, with P the complement of P! "f & is

pulsed high while R is held low, then the P output is forced high, and stas high even

after & returns low1 similarl, if R is pulsed high while & is held low, then the P

output is forced low, and stas low even after R returns low!

5A)A denotes a DonAt care condition1 meaning the signal is irrelevant7

SR 4li6'4lo6 o6+ra*io- #BUILT <ITH N%R GATES$

Q3R

"/arac*+ri:*ic *a;l+ E7ci*a*io- *a;l+

S R Ac*io- 9#*$ 9#*=1$ S R Ac*io-

/ / Oeep state / / / ) +o change

/ 0 P , / / 0 0 / reset

0 / P , 0 0 / / 0 set

0 0 9nstable combination 0 0 ) / race condition

B+/a3ioral co2+ 0or SR 0li6 0lo6&

'*DE6 librar ieee1

use ieee!std2logic20034!all1

entit srff is

port5s,r,clK6in bit1

=,=bar6inout bit71

end srff1

architecture behav of srff is

begin

process5s,r,clK7

variable g6 bit2vector5/ to 071

begin

g6, s>r1

if clK,A0A and clKA event

then

case g is

when ?//?,@ null1

when ?/0?,@ =8,A/A1 =bar8,A0A1

when ?0/?,@ =8,A0A1 =bar8,A/A1

when ?00?,@ assert rG,A0A and sG,A0Areport ?invalid condition? severit error1

end case1

end if1

end process1

end behav1

*9T:9T ;AVEF*R<

>? 4LI) 4L%) &

The NO flip(flop augments the behavior of the &R flip(flop 5N,&et, O,Reset7 b

interpreting the & , R , 0 condition as a ?flip? or toggle command! &pecificall, the

combination N , 0, O , / is a command to set the flip(flop1 the combination N , /, O

, 0 is a command to reset the flip(flop1 and the combination N , O , 0 is a command

to toggle the flip(flop, i!e!, change its output to the logical complement of its current

value! &etting N , O , / does +*T result in a D flip(flop, but rather, will hold the

current state! To snthesiBe a D flip(flop, simpl set O e=ual to the complement of N!

The NO flip(flop is therefore a universal flip(flop, because it can be configured to

worK as an &R flip(flop, a D flip(flop, or a T flip(flop!

The characteristic e=uation of the NO flip(flop is6

and the corresponding truth table is6

>? 4li6 4lo6 o6+ra*io-

"/arac*+ri:*ic *a;l+ E7ci*a*io- *a;l+

> ? 9

-+7*

"o55+-* 9 9

-+7*

> ? "o55+-*

/ / P

prev

hold state / / / ) +o change

/ 0 / reset / 0 0 ) &et

0 / 0 set 0 / ) 0 Reset

0 0 P

prev

toggle 0 0 ) / +o change

B+/a3ioral co2+ 0or >? 0li6 0lo6&

'*DE6 librar ieee1

use ieee!std2logic20034!all1

entit JKff is

port5J,K,clK6in bit1

=,=bar6inout bit71

end JKff1

architecture behav of JKff is

begin

process5J,K,clK7

variable s6 bit2vector5/ to 071

begin

s6, J>K1

if clK,A0A and clKA event

then

case s is

when ?//?,@ null1

when ?/0?,@ =8,A/A1 =bar8,A0A1

when ?0/?,@ =8,A0A1 =bar8,A/A1

when ?00?,@ =8,not =1 =bar8,=1

end case1

end if1

end process1

end behav1

*9T:9T ;AVEF*R<

E()ERIMENT N% @

AIM& To design shift registers in VHDL using structural!

T/+ory&

These are the simplest Kind of shift registers! The data string is presented at AData "nA,

and is shifted right one stage each time AData AdvanceA is brought high! At

each advance, the bit on the far left 5i!e! AData "nA7 is shifted into the

first flip(flopAs output! The bit on the far right 5i!e! AData *utA7 is shifted out

and lost!

The data are stored after each flip(flop on the APA output, so there are four

storage AslotsA available in this arrangement, hence it is a 4(#it Register! To

give an idea of the shifting pattern, imagine that the register holds //// 5so

all storage slots are empt7! As AData "nA presents 0,/,0,0,/,/,/,/ 5in that

order, with a pulse at AData AdvanceA each time! This is called clocKing or

strobing7 to the register, this is the result! The left hand column corresponds

to the left(most flip(flopAs output pin, and so on!

&o the serial output of the entire register is 0/00//// 57! As ou can see if

we were to continue to input data, we would get e-actl what was put in, but offset

b four AData AdvanceA ccles! This arrangement is the hardware e=uivalent of

a =ueue! Also, at an time, the whole register can be set to Bero b bringing the reset

5R7 pins high!

This arrangement performs destructive readout ( each datum is lost once it been

shifted out of the right(most bit!

/ / / /

0 / / /

/ 0 / /

0 / 0 /

0 0 / 0

/ 0 0 /

/ / 0 0

/ / / 0

/ / / /

S*r.c*.ral co2+ 0or SIS%&

'*DE6 librar ieee1

use ieee!std2logic20034!all1

entit dff is

port5d,clK6in bit1

=6out bit71

end dff1

architecture e0 of dff is

begin

process5d, clK7

begin

if clK,A0A and clKAevent then

=8,d1

end if1

end process1

end e01

entit siso is

port5 input,clK6in bit1

=out6out bit71

end siso1

architecture e0 of siso is

component dff

port5d,clK6in bit1

=6out bit71

end component1

signal =/,=0,=C6bit1

begin

n06dff port map5input,clK,=/71

nC6dff port map5=/,clK,=071

nD6dff port map5=0,clK,=C71

n46dff port map5=C,clK,=out71

end e01

*9T:9T ;AVEF*R<

)I)%&

The :ARALLEL "+G:ARALLEL *9T shift register is loaded with four bits

simultaneousl, in parallel!The are also clocKed out simultaneousl, in parallel!

S*r.c*.ral co2+ 0or )I)%&

'*DE6 librar ieee1

use ieee!std2logic20034!all1

entit dff is

port 5d,clK6in bit1

=,=bar6out bit71

end dff1

architecture behav of dff is

begin

process 5d,clK7

begin

if clK , A0A and clKAevent then

=8,d1

=bar8,not d1

end if1

end process1

end behav1

entit pipo is

port 5a,b,c,d,clK6in bit1

=/,=0,=C,=D6out bit71

end pipo1

architecture e0 of pipo is

component dff

port 5d,clK6in bit1

=,=bar6out bit71

end component1

begin

+06 dff port map 5a,clK,=/71

+C6 dff port map 5b,clK,=071

+D6 dff port map 5c,clK,=C71

+46 dff port map 5d,clK,=D71

end e01

*9T:9T ;AVEF*R<

)IS%&

This configuration has the data input on lines D0 through D4 in parallel format! To

write the data to the register, the ;riteG&hift control line must be held L*;! To shift

the data, the ;G& control line is brought H"SH and the registers are clocKed! The

arrangement now acts as a &"&* shift register, with D0 as the Data "nput! However,

as long as the number of clocK ccles is not more than the length of the data(string,

the Data *utput, P, will be the parallel data read off in order!

S*r.c*.ral co2+ 0or )I)%&

'*DE6 librar ieee1

use ieee!std2logic20034!all1

entit ctrl is

port5outf0,-,control6in bit1

inpfC6out bit71

end ctrl1

architecture e0 of ctrl is

begin

process5-,control,outf07

begin

if control,A0A then

inpfC8,-1

else

inpfC8,outf01

end if1

end process1

end e01

entit dff is

port 5d,clK6in bit1

=,=bar6out bit71

end dff1

architecture behav of dff is

begin

process 5d,clK7

begin

if clK , A0A and clKAevent then

=8,d1

=bar8,not d1

end if1

end process1

end behav1

entit piso is

port5a,b,c,d,d/,d0,dC,dD6inout bit1

=/,=0,=C,=D6inout bit1

control,clK6in bit71

end piso1

architecture eC of piso is

component dff

port 5d,clK6in bit1

=,=bar6out bit71

end component1

component ctrl

port5outf0,-,control6in bit1

inpfC6out bit71

end component1

begin

d/8,a1

+06 dff port map 5a,clK,=/71

+C6 ctrl port map 5=/,b,control,d071

+D6 dff port map 5d0,clK,=071

+46 ctrl port map 5=0,c,control,dC71

+H6 dff port map 5dC,clK,=C71

+36 ctrl port map 5=C,c,control,dD71

+L6 dff port map 5dD,clK,=D71

end eC1

*9T:9T ;AVEF*R<

SI)%&

This configuration allows conversion from serial to parallel format! Data is input

seriall, as described in the &"&* section above! *nce the data has been input, it ma

be either read off at each output simultaneousl, or it can be shifted out and replaced!

S*r.c*.ral co2+ 0or )I)%&

'*DE6 librar ieee1

use ieee!std2logic20034!all1

entit dff is

port 5d,clK6in bit1

=,=bar6out bit71

end dff1

architecture behav of dff is

begin

process 5d,clK7

begin

if clK , A0A and clKAevent then

=8,d1

=bar8,not d1

end if1

end process1

end behav1

entit sipo is

port 5input,clK6in bit1

=/,=0,=C,=D6inout bit71

end sipo1

architecture e0 of sipo is

component dff

port 5d,clK6in bit1

=,=bar6out bit71

end component1

begin

+06 dff port map 5input,clK,=/71

+C6 dff port map 5=/,clK,=071

+D6 dff port map 5=0,clK,=C71

+46 dff port map 5=C,clK,=D71

end e01

*9T:9T ;AVEF*R<

E()ERIMENT N% A

AIM& Design a mod H counter

T/+ory&

"n digital logic and computing, a co.-*+r is a device which stores 5and sometimes

displas7 the number of times a particular event or process has occurred, often in

relationship to a clocK signal! "n practice, there are two tpes of counters6

9p counters, which increase 5increment7 in value

Down counters, which decrease 5decrement7 in value

A mod H counter counts till binar four and in fifth clocK pulse it counts bacK to Bero!

B+/a3ioral co2+ 0or 5o2 5 co.-*+r&

'*DE6 librar ieee1

use ieee!std2logic20034!all1

9&E ieee!std2logic2arith!all1

9&E ieee!std2logic2unsigned!all1

E+T"TF binar2counter "&

port5 clK, reset6in bit1 count6out std2logic2vector5 / to C771

E+D E+T"TF binar2counter1

AR'H"TE'T9RE binar *F binar2counter "&

signal temp6 std2logic2vector5 / to C76,?///?1

#ES"+

process 5 clK, reset7

begin

if reset,A0A then temp8,?///?1

else if clK,A0A and clKAevent then

temp8, tempE 01

end if1

end if1

end process1

count8, temp1

E+D AR'H"TE'T9RE binar;

*9T:9T ;AVEF*R<

E()ERIMENT N% 8

AIM& Design a binar counter

T/+ory&

"n digital logic and computing, a co.-*+r is a device which stores 5and sometimes

displas7 the number of times a particular event or process has occurred, often in

relationship to a clocK signal! "n practice, there are two tpes of counters6

9p counters, which increase 5increment7 in value

Down counters, which decrease 5decrement7 in value

binar counter is a machine 5liKe a computer7 which counts in binar!

B+/a3ioral co2+ 0or ;i-ary co.-*+r&

'*DE6 librar ieee1

use ieee!std2logic20034!all1

9&E ieee!std2logic2arith!all1

9&E ieee!std2logic2unsigned!all1

E+T"TF binar2counter "&

port5 clK, reset6in bit1 count6out std2logic2vector5 / to C771

E+D E+T"TF binar2counter1

AR'H"TE'T9RE binar *F binar2counter "&

signal temp6 std2logic2vector5 / to C76,?///?1

#ES"+

process 5 clK, reset7

begin

if reset,A0A then temp8,?///?1

else if clK,A0A and clKAevent then

temp8, tempE 01

end if1

end if1

end process1

count8, temp1

E+D AR'H"TE'T9RE binar;

*9T:9T ;AVEF*R<

E()ERIMENT N% 10

AIM& Design simple AL9

T/+ory&

An arithmetic logic unit 5AL97 is a digital circuit that performs arithmetic and

logical operations! The AL9 is a fundamental building blocK of the central

processing unit 5':97 of a computer, and even the simplest microprocessors contain

one for purposes such as maintaining timers! The processors found inside modern

':9s and graphics processing units accommodate ver powerful and ver comple-

AL9s1 a single component ma contain a number of AL9s!

B+/a3ioral co2+ 0orALU&

'*DE6 librar ieee1

use ieee!std2logic20034!all1

9&E ieee!std2logic2arith!all1

9&E ieee!std2logic2unsigned!all1

E+T"TF alu "&

port5 a,b6in std2logic2vector5C downto /71

sel6 in std2logic2vector5D downto /71

cin6 in std2logic1

6out std2logic2vector5 C downto /771

E+D E+T"TF alu1

AR'H"TE'T9RE alu *F alu "&

#ES"+

process5 a,b,sel7

begin

case sel is

((arithmetic unit

when?////?,@ 8,a1

when?///0?,@ 8,aE01

when?//0/?,@ 8,a(01

when?//00?,@ 8,b1

when?/0//?,@ 8,bE01

when?/0/0?,@ 8,b(01

when?/00/?,@ 8,aEb1

when?/000?,@ 8,aEbEcin1

(( logic unit

when?0///?,@ 8, not a1

when?0//0?,@ 8, not b1

when?0/0/?,@ 8, a and b1

when?0/00?,@ 8, a or b1

when?00//?,@ 8, a nand b1

when?00/0?,@ 8, a nor b1

when?000/?,@ 8, a -or b1

when?0000?,@ 8, not 5 a -or b71

when others,@ null1

end case1

end process1

E+D AR'H"TE'T9RE alu1

*9T:9T ;AVEF*R<

E()ERIMENT N% 1

AIM& To implement logic gates

T/+ory&

%R GATE

The *R gate is a digital logic gate that implements logical disJunction ( it behaves

according to the truth table to the right! A H"SH output 507 results if one or both the

inputs to the gate are H"SH 507! "f neither input is H"SH, a L*; output 5/7 results!

IN)UT

A #

%UT)UT

A E #

/ / /

/ 0 0

0 / 0

0 0 0

B+/a3ioral co2+ 0or %R ,a*+&

'*DE6 librar ieee1

use ieee!std2logic20034!all1

entit orgate is

port5a,b6in bit1

-6out bit71

end orgate1

architecture behav of orgate is

begin

p06process5a,b7

begin

if a,A/A and b,A/A

then -8,A/A1

elsif a,A/A and b,A0A

then -8,A0A1

elsif a,A0A and b,A/A

then -8,A0A1

else -8,A0A1

end if1

end process p01

end behav1

*9T:9T ;AVEF*R<

N%R GATE&

The +*R gate is a digital logic gate that implements logical +*R ( it behaves

according to the truth table to the right! A H"SH output 507 results if both the inputs

to the gate are L*; 5/7! "f one or both input is H"SH 507, a L*; output 5/7 results!

+*R is the result of the negation of the *R operator! +*R is a functionall complete

operation (( combinations of +*R gates can be combined to generate an other

logical function! # contrast, the *R operator is monotonic as it can onl change

L*; to H"SH but not vice versa!

IN)UT

A #

%UT)UT

A +*R #

/ / 0

/ 0 /

0 / /

0 0 /

B+/a3ioral co2+ 0or N%R ,a*+&

'*DE6 librar ieee1

use ieee!std2logic20034!all1

entit norgate is

port5a,b6in bit1

-6out bit71

end norgate1

architecture behav of norgate is

begin

p06process5a,b7

begin

if a,A/A and b,A/A

then -8,A0A1

elsif a,A/A and b,A0A

then -8,A/A1

elsif a,A0A and b,A/A

then -8,A/A1

else -8,A/A1

end if1

end process p01

end behav1

*9T:9T ;AVEF*R<

(%R GATE&

The (%R ,a*+ 5sometimes E%R ,a*+7 is a digital logic gate that implements

e-clusive disJunction ( it behaves according to the truth table above! A H"SH output

507 results if one, and onl one, of the inputs to the gate is H"SH 507! "f both inputs

are L*; 5/7 or both are H"SH 507, a L*; output 5/7 results!

)*R gate is short for e-clusive *R! This means that precisel one input must be 0

5true7 for the output to be 0 5true7! A wa to remember )*R is ?one or the other but

not both!?

IN)UT

A #

%UT)UT

A )*R #

/ / /

/ 0 0

0 / 0

0 0 /

B+/a3ioral co2+ 0or (%R ,a*+&

'*DE6 librar ieee1

use ieee!std2logic20034!all1

entit e-or is

port5 a,b6 in bit1

B6 out bit71

end e-or1

architecture -0 of e-or is

begin

process5a,b7

variable c6 bit2vector5/ to 071

begin

c6, a>b1

case c is

when ?//? ,@ B8,A/A1

when ?/0? ,@ B8,A0A1

when ?0/? ,@ B8,A0A1

when ?00? ,@ B8,A/A1

end case1

end process1

end -01

*9T:9T ;AVEF*R<

(N%R GATE&

The (N%R ,a*+ 5sometimes spelled ?e-nor? or ?enor?7 is a digital logic gate whose

function is the inverse of the e-clusive *R 5)*R7 gate! The two(input version

implements logical e=ualit, behaving according to the truth table to the right! A

H"SH output 507 results if both of the inputs to the gate are the same! "f one but not

both inputs are H"SH 507, a L*; output 5/7 results!

B+/a3ioral co2+ 0or (%R ,a*+&

'*DE6 librar ieee1

use ieee!std2logic20034!all1

entit norgate is

port5a,b6in bit1

-6out bit71

end norgate1

architecture behav of norgate is

begin

p06process5a,b7

begin

if a,A/A and b,A/A

then -8,A0A1

elsif a,A/A and b,A0A

then -8,A/A1

elsif a,A0A and b,A/A

then -8,A/A1

else -8,A/A1

end if1

end process p01

end behav1

*9T:9T ;AVEF*R<

NAND GATE&

+A+D gates are one of the two basic logic gates 5along with +*R gates7 from which

an other logic gates can be built! Due to this propert, +A+D and +*R gates are

sometimes called ?universal gates?! However, contrar to popular belief, modern

integrated circuits are not constructed e-clusivel from a single tpe of gate! "nstead,

EDA tools are used to convert the description of a logical circuit to a netlist of

comple- gates 5standard cells7!

B+/a3ioral co2+ 0or (%R ,a*+&

'*DE6 librar ieee1

use ieee!std2logic20034!all1

entit nandg is

port5a,b6in bit1B6out bit71

end nandg1

architecture a0 of nandg is

constant nandg2dela6 time 6, 0/ ns1

begin

process5a,b7

variable t6bit2vector5/ to 071

begin

t6,a > b1

case t is

when ?//?,@B8,A0A1

when ?/0?,@B8,A0A1

when ?0/?,@B8,A0A1

when ?00?,@B8,A/A1

end case1

end process1

end a01

*9T:9T ;AVEF*R<

You might also like

- Lab ManualDocument42 pagesLab ManualNaresh KumarNo ratings yet

- Project Report VHDLDocument68 pagesProject Report VHDLricha_shukla_40No ratings yet

- Arduino Modules L298N Dual H Bridge Motor ControllDocument7 pagesArduino Modules L298N Dual H Bridge Motor ControllMarius DanilaNo ratings yet

- Project Report - VHDL MUXDocument4 pagesProject Report - VHDL MUXMsdmsd Msd100% (1)

- VHDL LabmanualDocument27 pagesVHDL LabmanualAsif BashaNo ratings yet

- Xlinx - VLSI Practical Lab ManualDocument31 pagesXlinx - VLSI Practical Lab ManualSamarth J Parikh0% (1)

- VHDL ExamplesDocument28 pagesVHDL Examplesapi-3731978No ratings yet

- VHDLDocument96 pagesVHDLJeevan Bhat100% (8)

- Programming FPGAsDocument38 pagesProgramming FPGAssayuri8910No ratings yet

- DC Motor Interface With Robot Operating System ROSDocument30 pagesDC Motor Interface With Robot Operating System ROSMuhammad SaleemNo ratings yet

- Simulink Support Package For ArduinoDocument4 pagesSimulink Support Package For ArduinofredNo ratings yet

- Vga VHDLDocument18 pagesVga VHDLDaveNo ratings yet

- 4-Bit ALUDocument3 pages4-Bit ALUdipendughoshNo ratings yet

- Digital Clock in VHDLDocument2 pagesDigital Clock in VHDLTapas KolteNo ratings yet

- Processor Design From Leon3 Extension Final ReportDocument44 pagesProcessor Design From Leon3 Extension Final ReportTalal KhaliqNo ratings yet

- NI Tutorial 3115 enDocument3 pagesNI Tutorial 3115 enajith.ganesh2420No ratings yet

- Advanced Embedded System Design: Project ReportDocument7 pagesAdvanced Embedded System Design: Project ReportSyed Akhlaq100% (1)

- Assignment - Muhammad Ali Asad - 014Document39 pagesAssignment - Muhammad Ali Asad - 014mumtazNo ratings yet

- Griet-M.tech-Embedded Systems - Microcontrollers Lab Manual 2018-19 PDFDocument178 pagesGriet-M.tech-Embedded Systems - Microcontrollers Lab Manual 2018-19 PDFAnonymous P40JqxuSKNo ratings yet

- ADE Lab Viva Question and Answer 2018Document5 pagesADE Lab Viva Question and Answer 2018NITHIN NNo ratings yet

- 8 Bit ALU by XilinxDocument16 pages8 Bit ALU by XilinxDIPTANU MAJUMDERNo ratings yet

- VLSI Lab Manual - Digital Cirucit Design Using VHDLDocument82 pagesVLSI Lab Manual - Digital Cirucit Design Using VHDLSakthikumar Balasundaram100% (3)

- Vlsi Project Report Arithmetic Logical Unit Using Verilog AluDocument7 pagesVlsi Project Report Arithmetic Logical Unit Using Verilog AluAnurag KharwarNo ratings yet

- VLSI Lab Manual V Sem July16Document65 pagesVLSI Lab Manual V Sem July16Aditya RanjanNo ratings yet

- VHDL TutorialDocument86 pagesVHDL TutorialramjidrNo ratings yet

- Robotics PPT ch-1Document29 pagesRobotics PPT ch-1SileshNo ratings yet

- 15ec563 - 8051 Microcontroller - Syllabus PDFDocument2 pages15ec563 - 8051 Microcontroller - Syllabus PDFNagesh100% (1)

- Pal and PlaDocument10 pagesPal and PlaRahul Kumar67% (6)

- 7.performance Analysis of Wallace Tree Multiplier With Kogge Stone Adder Using 15-4 CompressorDocument38 pages7.performance Analysis of Wallace Tree Multiplier With Kogge Stone Adder Using 15-4 Compressoranil kumarNo ratings yet

- Shift RegisterDocument25 pagesShift RegisterdianseptyaNo ratings yet

- Digital System Design Using VHDL PaperDocument2 pagesDigital System Design Using VHDL PaperlambajituNo ratings yet

- 4 Bit Cpu ReportDocument16 pages4 Bit Cpu ReportHarshil LodhiNo ratings yet

- Frequency Divider Using VHDLDocument27 pagesFrequency Divider Using VHDLPallavi NalawadeNo ratings yet

- DSP Lab ManualDocument84 pagesDSP Lab ManualGowtham Raj100% (2)

- 8085 SimulatorDocument2 pages8085 Simulatorradke42626No ratings yet

- ECE448 Lecture7 VGA 1Document66 pagesECE448 Lecture7 VGA 1Mendbayar MbNo ratings yet

- Microprocessor FileDocument93 pagesMicroprocessor FileHarshal AmbatkarNo ratings yet

- L9 Understanding Atmega328P 2Document15 pagesL9 Understanding Atmega328P 2VIGHNESH AIYANo ratings yet

- Xzno22222222222 PDFDocument278 pagesXzno22222222222 PDFاحمد سالمNo ratings yet

- CISE414 - Unit 04 AVR Atmega PortsDocument30 pagesCISE414 - Unit 04 AVR Atmega Portsمحمد حمدNo ratings yet

- TMS320C6748 DSP BOARD Package ContentDocument22 pagesTMS320C6748 DSP BOARD Package ContentPrangya PradhanNo ratings yet

- A Complete 8-Bit Microcontroller in VHDLDocument29 pagesA Complete 8-Bit Microcontroller in VHDLSidney O. EbotNo ratings yet

- Lab 05 To Perform Signal Companding in SimulinkDocument15 pagesLab 05 To Perform Signal Companding in SimulinkArshad AliNo ratings yet

- Starfast-A Wireless Wearable EEG Biometric System Based On The ENOBIO SensorDocument8 pagesStarfast-A Wireless Wearable EEG Biometric System Based On The ENOBIO SensorMohammed Suleman Ashraf100% (2)

- Project 1 - Robotic ArmDocument19 pagesProject 1 - Robotic ArmAizzat ZackNo ratings yet

- Arm-Cortex m3Document13 pagesArm-Cortex m3vinjamurisivaNo ratings yet

- Void PPC UpdateDocument41 pagesVoid PPC UpdatePian RispianNo ratings yet

- Introduction To TMS320C6713 DSP Starter Kit DSK)Document18 pagesIntroduction To TMS320C6713 DSP Starter Kit DSK)Anup DharanguttiNo ratings yet

- Pedroni VHDL 2ed Exercise Solutions v4 PDFDocument37 pagesPedroni VHDL 2ed Exercise Solutions v4 PDFana eht50% (2)

- VHDL Project: Title: "Stop Watch"Document13 pagesVHDL Project: Title: "Stop Watch"Soriya HiteshNo ratings yet

- PBG BCI RoboticsDocument5 pagesPBG BCI Roboticsbangalore2009No ratings yet

- MPLab Tutorial v1Document45 pagesMPLab Tutorial v1ASIM RIAZNo ratings yet

- CortexM4 FPUDocument14 pagesCortexM4 FPUMohamedAliFerjaniNo ratings yet

- Introduction to 6800/6802 Microprocessor Systems: Hardware, Software and ExperimentationFrom EverandIntroduction to 6800/6802 Microprocessor Systems: Hardware, Software and ExperimentationNo ratings yet

- Application-Specific Integrated Circuit ASIC A Complete GuideFrom EverandApplication-Specific Integrated Circuit ASIC A Complete GuideNo ratings yet

- VHDL ReportDocument29 pagesVHDL ReportSalman AliNo ratings yet

- UNIT-3: Design Combinational CKT Using Architecture ModelDocument36 pagesUNIT-3: Design Combinational CKT Using Architecture Modelankit_4382No ratings yet

- CSE 1st SemesterDocument6 pagesCSE 1st SemesterkdjsajkdjkdshkjaNo ratings yet

- P9120 SyllabusDocument5 pagesP9120 SyllabusQiqi DorisNo ratings yet

- Perl Programming TutorialDocument43 pagesPerl Programming TutorialGábor ImolaiNo ratings yet

- Short-Run Behavior of Defensive Assets in The Ethiopian Commercial Banking SectorDocument25 pagesShort-Run Behavior of Defensive Assets in The Ethiopian Commercial Banking SectorEndrias EyanoNo ratings yet

- Calculas 1Document3 pagesCalculas 1Ishfaq ChohanNo ratings yet

- Sample2 PDFDocument4 pagesSample2 PDFWaseemjahangirNo ratings yet

- Dcs Project1Document13 pagesDcs Project1Sujeet KumarNo ratings yet

- Math 1030 Skittles Term ProjectDocument8 pagesMath 1030 Skittles Term Projectapi-340538273No ratings yet

- BF 03266576Document9 pagesBF 03266576Gianni FurgoneNo ratings yet

- Evaluation of Properties and FEM Model of The Friction Welded Mild Steel-Al6061-AluminaDocument15 pagesEvaluation of Properties and FEM Model of The Friction Welded Mild Steel-Al6061-AluminaKamel FedaouiNo ratings yet

- FPGA Temp SensorDocument8 pagesFPGA Temp SensorRajan BhartiNo ratings yet

- Transportation and Assignment Models in Operations ResearchDocument3 pagesTransportation and Assignment Models in Operations ResearchE5251888100% (1)

- 6 Structures in 'C'Document11 pages6 Structures in 'C'api-372813692% (12)

- S5 Course HandoutDocument135 pagesS5 Course HandoutAnil KumarNo ratings yet

- APSRTC Junior Assistant (Finance) User Guide & Instruction BookletDocument15 pagesAPSRTC Junior Assistant (Finance) User Guide & Instruction BookletTrcStaffNo ratings yet

- Study Package - Physics 11Document378 pagesStudy Package - Physics 11rebeccasanjuNo ratings yet

- Servois' 1813 Perpetual Calendar, With An English Translation - Gauss' Calculation For The Date of EasterDocument1 pageServois' 1813 Perpetual Calendar, With An English Translation - Gauss' Calculation For The Date of EasterZlatko JurkovićNo ratings yet

- Population Projection of Ethiopia For All Regions at Wereda Level From 2014 PDFDocument118 pagesPopulation Projection of Ethiopia For All Regions at Wereda Level From 2014 PDFFuad100% (1)

- SyllabusDocument4 pagesSyllabusAlysson Vany ClochetteNo ratings yet

- ACFMDocument10 pagesACFMAnson MartinNo ratings yet

- Emat 6700 May20 Project Reflection 1 GrayDocument3 pagesEmat 6700 May20 Project Reflection 1 Grayapi-286313605No ratings yet

- Lesson Plan ECS 228 November 2013 - April 2014 - IzziyantieDocument4 pagesLesson Plan ECS 228 November 2013 - April 2014 - IzziyantiesaifulsabdinNo ratings yet

- Open Sim Tutorial 3Document8 pagesOpen Sim Tutorial 3Jobin VargheseNo ratings yet

- Lec3 4Document14 pagesLec3 4mrd9991No ratings yet

- CLILDocument14 pagesCLILMiguel Rico Porter100% (2)

- Automation Expo Exhibitior List 2015Document100 pagesAutomation Expo Exhibitior List 2015Manan TyagiNo ratings yet

- R(S) C(S) : 0708sem1 - FinalexamDocument27 pagesR(S) C(S) : 0708sem1 - FinalexamAmiruddin Mohd ArifuddinNo ratings yet

- s2 1 PDFDocument3 pagess2 1 PDFkrishnaNo ratings yet

- Unit - 2 Linear Data Structures - Array & StackDocument19 pagesUnit - 2 Linear Data Structures - Array & StackDarshna SharmaNo ratings yet