Professional Documents

Culture Documents

Full Adder Using 4x1 Mux

Uploaded by

Rasigan UrOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Full Adder Using 4x1 Mux

Uploaded by

Rasigan UrCopyright:

Available Formats

FULL ADDER USING 4X1 MUX

Aim:

To design a full adder program using multiplexer by Verilog HDL program under Altera

Quartus II 9.0 web Editor tool.

Tools required:

Altera Quartus II 9.0

Design:

A

B

Sum Cout

Sum

Cout

Cin=0 Cin=1 Cin=0 Cin=1

0 0 0 1 0 0 Cin 0

0 1 1 0 0 1

Cin

1 0 1 0 0 1

Cin

1 1 0 1 1 1 Cin 1

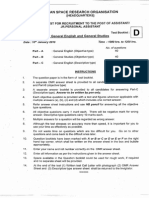

Logic Diagram:

Source Code:

module fa_mux(sum,cout,a,b,cin);

output cout,sum;

input a,b,cin;

wire cinb;

mux m1(.z(sum),.d0(cin),.d1(cinb),.d2(cinb),.d3(cin),.s0(a),.s1(b));

mux m2(.z(cout),.d0(0),.d1(cin),.d2(cin),.d3(1),.s0(a),.s1(b));

assign cinb=~cin;

endmodule

module mux(z,d0,d1,d2,d3,s0,s1);

input d0,d1,d2,d3,s0,s1;

output z;

reg z;

always @(d0 or d1 or d2 or d3 or s0 or s1)

begin

case({s0,s1})

2'b00: z<=d0;

2'b01: z<=d1;

2'b10: z<=d2;

2'b11: z<=d3;

endcase

end

endmodule

OUTPUT WAVEFORM:

RESULT:

Thus we have designed a full adder using multiplexer by Verilog HDL program under

Altera Quartus II 9.0 web Editor tool.

You might also like

- Stick Diagram & Lambda Based Design RulesDocument21 pagesStick Diagram & Lambda Based Design Rulesbaraniinst6875100% (1)

- VHDL DOCUMENTATIONDocument41 pagesVHDL DOCUMENTATIONB. MeenakshiNo ratings yet

- Digital Electronics - MCQsDocument38 pagesDigital Electronics - MCQsAbhay ShuklaNo ratings yet

- Digital Electronics (MCQ) PART-1Document7 pagesDigital Electronics (MCQ) PART-101ABHIGYAN MAJINo ratings yet

- Updated - DSDV - BEC302 - LAB MANUAL123Document54 pagesUpdated - DSDV - BEC302 - LAB MANUAL123Harish G CNo ratings yet

- DAA Lab Manual VTUDocument41 pagesDAA Lab Manual VTUManohar NV100% (2)

- DSP MCQDocument2 pagesDSP MCQBala MuruganNo ratings yet

- Digital Electronics Multiple Choice QuestionsDocument22 pagesDigital Electronics Multiple Choice QuestionsSenthilkumar KrishnamoorthyNo ratings yet

- CS8351 Digital Principles and System Design MCQDocument52 pagesCS8351 Digital Principles and System Design MCQSeekay Alais Karuppaiah C100% (2)

- HDL Model QPDocument5 pagesHDL Model QPSubramanyaAIyerNo ratings yet

- NI Tutorial 3115 enDocument3 pagesNI Tutorial 3115 enajith.ganesh2420No ratings yet

- Digital Design Lab Manual: Introduction To VerilogDocument48 pagesDigital Design Lab Manual: Introduction To VerilogKeith FernandesNo ratings yet

- Week 2 Coding Assignment Name: Priyanka Indra Roll No.: 84 Dept: CSE1 Sem:6Document18 pagesWeek 2 Coding Assignment Name: Priyanka Indra Roll No.: 84 Dept: CSE1 Sem:6Priyanka IndraNo ratings yet

- 1 Number SystemDocument14 pages1 Number SystemhemanthNo ratings yet

- Advanced Communication Lab Manual: Visvesvaraya Technological UniversityDocument46 pagesAdvanced Communication Lab Manual: Visvesvaraya Technological UniversityPunith Gowda M B100% (2)

- Verilog CodeDocument60 pagesVerilog CodePriyanka JainNo ratings yet

- MCQ's DSP 201-300Document18 pagesMCQ's DSP 201-300Rohit NegiNo ratings yet

- LCD and KEYBORD Interfacing Part 1Document25 pagesLCD and KEYBORD Interfacing Part 1Prathamesh AmateNo ratings yet

- Verilog Lab ManualDocument27 pagesVerilog Lab Manualjainatush912100% (1)

- Digital Logic Design Question PaperDocument2 pagesDigital Logic Design Question PaperMuhammad UmairNo ratings yet

- Multiplier in Vlsi PDFDocument23 pagesMultiplier in Vlsi PDFvmspraneeth100% (1)

- Assignment 1 DSDDocument2 pagesAssignment 1 DSDsarala tNo ratings yet

- Department of ECE Module Iv Finite Word Length EffectsDocument28 pagesDepartment of ECE Module Iv Finite Word Length EffectsSuraaj Sakthi KumarNo ratings yet

- HDL Manual (18ecl58)Document20 pagesHDL Manual (18ecl58)lohith sNo ratings yet

- Viva Voce Questions On Communication SystemsDocument3 pagesViva Voce Questions On Communication SystemsZealWolf100% (3)

- 8 Bit Carry Select AdderDocument6 pages8 Bit Carry Select AdderNandini Nandy50% (2)

- 2009 - Open Book Exam BITS PilaniDocument2 pages2009 - Open Book Exam BITS PilaniShivam ShuklaNo ratings yet

- CS 8351 Digital Principles and System Design MultiplexersDocument25 pagesCS 8351 Digital Principles and System Design Multiplexerspadmaa1No ratings yet

- Group - A (Short Answer Questions) : S.No Blooms Taxonomy Level Course OutcomesDocument15 pagesGroup - A (Short Answer Questions) : S.No Blooms Taxonomy Level Course OutcomesRama KrishnaNo ratings yet

- LDPC - Low Density Parity Check CodesDocument6 pagesLDPC - Low Density Parity Check CodespandyakaviNo ratings yet

- Binary To Excess 3 VHDL Code Using Structural ModelingDocument1 pageBinary To Excess 3 VHDL Code Using Structural ModelingOP2RNo ratings yet

- Pseudo Random Sequence Generator in VerilogDocument3 pagesPseudo Random Sequence Generator in VerilogAhmed AbduljabbarNo ratings yet

- Experiment No. 5: Binary Phase Shift KeyingDocument7 pagesExperiment No. 5: Binary Phase Shift KeyingGovind YadavNo ratings yet

- Ecad Lab ManualDocument55 pagesEcad Lab Manualjeravi84100% (3)

- Ade Mod5Document8 pagesAde Mod5BasNo ratings yet

- Digital Circuits & Fundamentals of MicroprocessorDocument86 pagesDigital Circuits & Fundamentals of Microprocessorfree_prog67% (6)

- Commnication Lab Manual 2021 SchemeDocument51 pagesCommnication Lab Manual 2021 Scheme29 Naib rasool shaikhNo ratings yet

- Digital Signal Processing Unit NotesDocument44 pagesDigital Signal Processing Unit NotesGowri ShankarNo ratings yet

- PLD, Logic Gates and Families Unit ReviewDocument5 pagesPLD, Logic Gates and Families Unit ReviewnithyasaviNo ratings yet

- LCDF3 Chap 03 P1Document54 pagesLCDF3 Chap 03 P1boymatterNo ratings yet

- ARM ArchitectureDocument16 pagesARM ArchitectureS S0% (1)

- Cquiz 2Document4 pagesCquiz 2simNo ratings yet

- Roth's D-Algorithm ExplainedDocument48 pagesRoth's D-Algorithm ExplainedVinod Khera100% (1)

- Project Report On Electronic Voting Machine Using Fpga VerilogDocument23 pagesProject Report On Electronic Voting Machine Using Fpga Verilogteja72452No ratings yet

- Embedded Systems Lab Manual MODDocument20 pagesEmbedded Systems Lab Manual MODHari0% (1)

- Python Multiple ChoiceDocument13 pagesPython Multiple ChoicejobyNo ratings yet

- Electronically Tunable Chaotic Oscillators Using OTA-C Derived From Jerk ModelDocument23 pagesElectronically Tunable Chaotic Oscillators Using OTA-C Derived From Jerk ModelKhunanon KarawanichNo ratings yet

- CS370-FixedFloatingDocument19 pagesCS370-FixedFloatingGasser Alaa EldienNo ratings yet

- Ca Q&aDocument129 pagesCa Q&aRavi TejaNo ratings yet

- Radar Systems - Delay Line CancellersDocument7 pagesRadar Systems - Delay Line Cancellersgajjala rakeshNo ratings yet

- Xilinx Project Navigator HDL Lab ManualDocument72 pagesXilinx Project Navigator HDL Lab Manualshubham100% (1)

- Collect and Prepare Human Activity Sensor DataDocument7 pagesCollect and Prepare Human Activity Sensor DataagamdeepNo ratings yet

- BJT Amplifier Configurations & Parameters QuizDocument9 pagesBJT Amplifier Configurations & Parameters Quizkingibzz82100% (1)

- CS 25000 Spring 2017 Final Practice SolutionsDocument13 pagesCS 25000 Spring 2017 Final Practice SolutionsTiger TangNo ratings yet

- Break and Continue MCQ AnsDocument11 pagesBreak and Continue MCQ Ansnancy_007No ratings yet

- Unit 9 - Week 7: Assignment 7Document5 pagesUnit 9 - Week 7: Assignment 7Gajalakshmi AshokNo ratings yet

- Comprehensive Assignments for DCDR (2161603) SubjectDocument4 pagesComprehensive Assignments for DCDR (2161603) SubjectShubhuNo ratings yet

- Identify The Structure Implemented in The Following Layout Diagram and Draw Its Equivalent CMOS ImplementationDocument2 pagesIdentify The Structure Implemented in The Following Layout Diagram and Draw Its Equivalent CMOS Implementationrishika chhibberNo ratings yet

- Lecture 21Document7 pagesLecture 21litoduterNo ratings yet

- Dokumen - Tips Full Adder Using 4x1 MuxDocument3 pagesDokumen - Tips Full Adder Using 4x1 MuxMr MiracleNo ratings yet

- 75 PDFsam MSDN 1C Sharp DocumentationDocument151 pages75 PDFsam MSDN 1C Sharp DocumentationRasigan UrNo ratings yet

- ReadmeDocument1 pageReadmeRasigan UrNo ratings yet

- Question BankDocument32 pagesQuestion BanknandhinidishNo ratings yet

- 5 What Is A FunctionDocument3 pages5 What Is A FunctionRasigan UrNo ratings yet

- ReadmeDocument1 pageReadmeRasigan UrNo ratings yet

- List ch01 01 Eq1Document1 pageList ch01 01 Eq1Rasigan UrNo ratings yet

- JRC MuxDocument3 pagesJRC MuxRasigan UrNo ratings yet

- Udc XorgDocument3 pagesUdc XorgRasigan UrNo ratings yet

- Question BankDocument32 pagesQuestion BanknandhinidishNo ratings yet

- Question BankDocument32 pagesQuestion BanknandhinidishNo ratings yet

- BoothDocument2 pagesBoothRasigan UrNo ratings yet

- Remembering MF Husain - Was India Deserving of A Genius Like HimDocument15 pagesRemembering MF Husain - Was India Deserving of A Genius Like HimRasigan UrNo ratings yet

- 3 Fir ComparsionDocument8 pages3 Fir ComparsionRasigan UrNo ratings yet

- TruncDocument4 pagesTruncRasigan UrNo ratings yet

- Comp 1Document3 pagesComp 1Rasigan UrNo ratings yet

- BramDocument2 pagesBramRasigan UrNo ratings yet

- FifoDocument3 pagesFifoRasigan UrNo ratings yet

- Distributed Arithmetic FIR Filter TechniqueDocument8 pagesDistributed Arithmetic FIR Filter TechniqueRasigan UrNo ratings yet

- Power Area FILTERSDocument8 pagesPower Area FILTERSRasigan UrNo ratings yet

- 2DFIR FilterDocument4 pages2DFIR FilterRasigan UrNo ratings yet

- Remembering MF Husain - Was India Deserving of A Genius Like HimDocument15 pagesRemembering MF Husain - Was India Deserving of A Genius Like HimRasigan UrNo ratings yet

- Std10 Tamil 1 PDFDocument125 pagesStd10 Tamil 1 PDFsasikumar rNo ratings yet

- PublicationDocument1 pagePublicationRasigan UrNo ratings yet

- Series FormulasDocument3 pagesSeries FormulasBachchan MishraNo ratings yet

- 2010 Paper IDocument14 pages2010 Paper IRasigan UrNo ratings yet

- New High-Speed Multi OutputDocument1 pageNew High-Speed Multi OutputRasigan UrNo ratings yet

- Testability Evaluation of Electronic DesignsDocument50 pagesTestability Evaluation of Electronic DesignsRasigan UrNo ratings yet

- Fig. 2-1: Spherical and Plane Wave FrontsDocument15 pagesFig. 2-1: Spherical and Plane Wave FrontsRasigan UrNo ratings yet

- Analytic Geometry Formulas PDFDocument4 pagesAnalytic Geometry Formulas PDFKaranbir RandhawaNo ratings yet

- Fpga Module PresDocument45 pagesFpga Module PrescatchmereddyNo ratings yet