Professional Documents

Culture Documents

FET Biasing

Uploaded by

546546587587Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

FET Biasing

Uploaded by

546546587587Copyright:

Available Formats

FET Biasing

1

Introduction

For the JFET, the relationship between input and output

quantities is nonlinear due to the squared term in

Shockleys equation.

Nonlinear functions results in curves as obtained for

transfer characteristic of a JFET.

Graphical approach will be used to examine the dc

analysis for FET because it is most popularly used rather

than mathematical approach

The input of BJT and FET controlling variables are the

current and the voltage levels respectively

2

JFETs differ from BJTs:

Nonlinear relationship between input (V

GS

) and output

(I

D

)

JFETs are voltage controlled devices, whereas BJTs are

current controlled

Introduction

3

Common FET Biasing Circuits

JFET

Fixed Bias

Self-Bias

Voltage-Divider Bias

Depletion-Type MOSFET

Self-Bias

Voltage-Divider Bias

Enhancement-Type MOSFET

Feedback Configuration

Voltage-Divider Bias

Introduction

4

General Relationships

For all FETs:

For JFETs and Depletion-Type MOSFETs:

For Enhancement-Type MOSFETs:

A I

G

0 ~

S D

I I =

2

P

GS

DSS D )

V

V

(1 I I =

2

) (

T GS D

V V k I =

5

Fixed-Bias Configuration

The configuration includes the ac levels Vi and Vo and

the coupling capacitors.

The resistor is present to ensure that Vi appears at the

input to the FET amplifier for the AC analysis.

6

Fixed-Bias Configuration

For the DC analysis,

Capacitors are open circuits

and

The zero-volt drop across R

G

permits replacing R

G

by a short-circuit

A I

G

0 ~ V R A R I V

G G G RG

0 ) 0 ( = = =

7

Fixed-Bias Configuration

Investigating the input loop

I

G

=0A, therefore

V

RG

=I

G

R

G

=0V

Applying KVL for the input loop,

-V

GG

-V

GS

=0

V

GG

= -V

GS

It is called fixed-bias configuration due to V

GG

is a fixed

power supply so V

GS

is fixed

The resulting current,

2

) 1 (

P

GS

DSS D

V

V

I I =

8

Investigating the graphical approach.

Using below tables, we

can draw the graph

V

GS

I

D

0 I

DSS

0.3V

P

I

DSS

/2

0.5 I

DSS

/4

V

P

0mA

9

The fixed level of V

GS

has been superimposed as a

vertical line at

At any point on the vertical line, the level of V

G

is -V

GG

---

the level of I

D

must simply be determined on this vertical

line.

The point where the two curves intersect is the common

solution to the configuration commonly referrers to as

the quiescent or operating point.

The quiescent level of I

D

is determine by drawing a

horizontal line from the Q-point to the vertical I

D

axis.

GG GS

V V =

10

Output loop

D D DD DS

R I V V =

V V

S

0 =

S D DS

V V V =

S DS D

V V V + = 0 =

S

V

DS D

V V =

S G GS

V V V =

S GS G

V V V + =

0 =

S

V

GS G

V V =

11

Example

Determine VGSQ, IDQ, VDS, VD, VG, VS

12

Exercise

Determine IDQ, VGSQ, VDS, VD, VG and VS

13

Self Bias Configuration

The self-bias configuration eliminates the need for two

dc supplies.

The controlling V

GS

is now determined by the voltage

across the resistor R

S

14

For the indicated input loop:

Mathematical approach:

rearrange and solve.

S D GS

R I V =

2

2

1

1

|

|

.

|

\

|

=

|

|

.

|

\

|

=

P

S D

DSS D

P

GS

DSS D

V

R I

I I

V

V

I I

15

Graphical approach

Draw the device transfer characteristic

Draw the network load line

Use to draw straight line.

First point,

Second point, any point from I

D

= 0 to I

D

= I

DSS

. Choose

the quiescent point obtained at the intersection of the

straight line plot and the device characteristic curve.

The quiescent value for I

D

and V

GS

can then be

determined and used to find the other quantities of

interest.

S D GS

R I V =

0 , 0 = =

GS D

V I

2

2

S DSS

GS

DSS

D

R I

V

then

I

I

=

=

16

17

For output loop

Apply KVL of output loop

Use I

D

= I

S

RD DD S DS D

S D S

D S D DD DS

V V V V V

R I V

R R I V V

= + =

=

+ = ) (

18

19

Example

Determine VGSQ, IDQ,VDS,VS,VG and VD.

20

Example

Determine VGSQ, IDQ, VD,VG,VS and VDS.

21

Voltage-Divider Bias

The arrangement is the same as BJT but the DC analysis is different

In BJT, IB provide link to input and output circuit, in FET VGS does

the same

22

Voltage-Divider Bias

The source V

DD

was separated into two equivalent sources to

permit a further separation of the input and output regions of the

network.

I

G

= 0A ,Kirchoffs current law requires that I

R1

= I

R2

and the series

equivalent circuit appearing to the left of the figure can be used to

find the level of V

G

.

23

2 1

DD 2

G

R R

V R

V

+

=

S D G GS

RS GS G

R I V V

V V V

=

= 0

Voltage-Divider Bias

V

G

can be found using the voltage divider rule :

Using Kirchoffs Law on the input loop:

Rearranging and using ID =IS:

Again the Q point needs to be established by

plotting a line that intersects the transfer curve.

24

Procedures for plotting

1. Plot the line: By plotting two points: V

GS

= V

G

, I

D

=0 and V

GS

= 0, I

D

= V

G

/R

S

2. Plot the transfer curve by plotting I

DSS

, V

P

and calculated values of I

D

.

3. Where the line intersects the transfer curve is the Q point for the circuit.

25

Once the quiescent values of I

DQ

and V

GSQ

are determined, the

remaining network analysis can be found.

Output loop:

2 1

2 1

R R

V

I I

DD

R R

+

= =

) (

S D D D DD DS

R I R I V V + =

D D DD D

R I V V =

S D S

R I V =

26

Effect of increasing values of R

S

27

Example

Determine IDQ, VGSQ, VD, VS, VDS and VDG.

28

Example

Determine IDQ, VGSQ, VDS, VD and VS

29

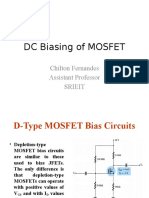

Depletion-type MOSFET bias circuits are similar to JFETs. The only difference is

that the depletion-Type MOSFETs can operate with positive values of V

GS

and with

I

D

values that exceed I

DSS

.

Depletion-Type MOSFETs

30

The DC Analysis

Same as the FET calculations

Plotting the transfer characteristics of the device

Plotting the at a point that V

GS

exceeds the 0V or more positive values

Plotting point when V

GS

=0V

and

I

D

=0A

The intersection between Shockley characteristics and linear

characteristics defined the Q-point of the MOSFET

The problem is that how long does the transfer characteristics have to

be draw?

We have to analyze the input loop parameter relationship.

As R

S

become smaller, the linear characteristics will be in narrow slope

therefore needs to consider the extend of transfer characteristics for

example of voltage divider MOSFET,

The bigger values of V

P

the more positive values we should draw for the

transfer characteristics

S D G GS

RS GS G

R I V V

V V V

=

= 0

Depletion-Type MOSFETs

31

Analyzing the MOSFET circuit for DC

analysis

How to analyze dc

analysis for the shown

network?

It is a . Type network

Find V

G

or V

GS

Draw the linear

characteristics

Draw the transfer

characteristics

Obtain V

GSQ

and I

DQ

from

the graph intersection

32

1. Plot line for V

GS

= V

G

, I

D

= 0 and I

D

= V

G

/R

S

, V

GS

= 0

2. Plot the transfer curve by plotting I

DSS

, V

P

and calculated values of I

D

.

3. Where the line intersects the transfer curve is the Q-point.

Use the I

D

at the Q-point to solve for the other variables in the voltage-divider bias

circuit. These are the same calculations as used by a JFET circuit.

33

When R

S

changethe linear characteristics will change..

1. Plot line for V

GS

= V

G

, I

D

= 0 and I

D

= V

G

/R

S

, V

GS

= 0

2. Plot the transfer curve by plotting I

DSS

, V

P

and calculated values of I

D

.

3. Where the line intersects the transfer curve is the Q-point.

Use the I

D

at the Q-point to solve for the other variables in the voltage-divider bias

circuit. These are the same calculations as used by a JFET circuit.

34

The transfer characteristic for the enhancement-type MOSFET is very different

from that of a simple JFET or the depletion-typeMOSFET.

Enhancement-Type MOSFET

35

Transfer characteristic for E-MOSFET

and

2

) (

) (

Th

GS GS D

V V k I =

2

) ( ) (

) (

) (

Th GS on GS

on D

V V

I

k

=

36

Feedback Biasing Arrangement

I

G

=0A, therefore V

RG

= 0V

Therefore: V

DS

= V

GS

Which makes

D D DD GS

R I V V =

37

1. Plot the line using V

GS

= V

DD

, I

D

= 0 and I

D

= V

DD

/ R

D

and V

GS

= 0

2. Plot the transfer curve using V

GSTh

, I

D

= 0 and V

GS(on)

, I

D(on)

; all given in the

specification sheet.

3. Where the line and the transfer curve intersect is the Q-Point.

4. Using the value of I

D

at the Q-point, solve for the other variables in the bias

circuit.

Feedback Biasing Q-Point

38

DC analysis step for Feedback Biasing

Enhancement type MOSFET

Find k using the datasheet or specification given;

ex: V

GS(ON)

,V

GS(TH)

Plot transfer characteristics using the formula

I

D

=k(V

GS

V

T

)

2

. Three point already defined that is I

D(ON)

,

V

GS(ON)

and V

GS(TH)

Plot a point that is slightly greater than V

GS

Plot the linear characteristics (network bias line)

The intersection defines the Q-point

39

Example

Determine IDQ and VDSQ for network below

40

Again plot the line and the transfer curve to find the Q-point.

Using the following equations:

2 1

DD 2

G

R R

V R

V

+

=

) (

D S D DD DS

S D G GS

R R I V V

R I V V

+ =

=

Input loop :

Output loop :

Voltage-Divider Biasing

41

1. Plot the line using V

GS

= V

G

= (R

2

V

DD

)/(R

1

+ R

2

), I

D

= 0 and I

D

= V

G

/R

S

and V

GS

= 0

2. Find k

3. Plot the transfer curve using V

GSTh

, I

D

= 0 and V

GS(on)

, I

D

(on); all given in

the specification sheet.

4. Where the line and the transfer curve intersect is the Q-Point.

5. Using the value of I

D

at the Q-point, solve for the other variables in the

bias circuit.

Voltage-Divider Bias Q-Point

42

Example

Determine IDQ and VGSQ and VDS for

network below

43

=

= -

-

=

-

=

- + ) (

=

=

-

+

= -

) (

+

=

=

-

) (

+

+ -

=

=

44

= -

=

=

= -

=

-

=

-

=

+

- =

= - +

( )

=

=

-

=

=

+

-

45

Troubleshooting

N-channel V

GSQ

will be 0V or negative if properly

checked

Level of V

DS

is ranging from 25%~75% of V

DD

. If 0V

indicated, theres problem

Check with the calculation between each terminal and

ground. There must be a reading, R

G

will be excluded

46

For p-channel FETs the same calculations and graphs are used, except

that the voltage polarities and current directions are the opposite. The

graphs will be mirrors of the n-channel graphs.

P-Channel FETs

47

Voltage-Controlled Resistor

JFET Voltmeter

Timer Network

Fiber Optic Circuitry

MOSFET Relay Driver

Practical Applications

48

JFET Voltmeter

49

Advantages

High Input impedance for isolation.

Amount of power drawn from circuit under

test is very small, so no loading effect.

Very high sensitivity.

Amplifier gain allows measurement in the

mV range.

No damage due to overload because of

amplifier saturation.

50

Single MOSFET Relay Toggle Circuit

51

You might also like

- Chap3a - FET (v1.2)Document70 pagesChap3a - FET (v1.2)Al AidenNo ratings yet

- Digital Signal Processing Systems: Implementation Techniques: Advances in Theory and ApplicationsFrom EverandDigital Signal Processing Systems: Implementation Techniques: Advances in Theory and ApplicationsNo ratings yet

- Chapter 4:jfet: Junction Field Effect TransistorDocument68 pagesChapter 4:jfet: Junction Field Effect TransistorelectricKKTMNo ratings yet

- Numerical Solution of Ordinary and Partial Differential Equations: Based on a Summer School Held in Oxford, August-September 1961From EverandNumerical Solution of Ordinary and Partial Differential Equations: Based on a Summer School Held in Oxford, August-September 1961No ratings yet

- FET BiasingDocument48 pagesFET Biasingbetteralwz100% (3)

- Unit Vii Fet AmplifiersDocument14 pagesUnit Vii Fet AmplifiersAadarsha timilsinaNo ratings yet

- BJT and JFET Frequency ResponseDocument16 pagesBJT and JFET Frequency ResponseVert WheelerNo ratings yet

- Chapter 6 - FET Biasing: Your Answer: Correct AnswerDocument6 pagesChapter 6 - FET Biasing: Your Answer: Correct AnswerXiao XiNo ratings yet

- 5.introduction To JFETDocument22 pages5.introduction To JFETGowshalya PerinbanayakamNo ratings yet

- L6 Week6 FET Biasing Chap7Document40 pagesL6 Week6 FET Biasing Chap7Amir MustakimNo ratings yet

- Chapter Two Differential Amplifiers 2nd LectureDocument35 pagesChapter Two Differential Amplifiers 2nd LectureTemesgen MekonenNo ratings yet

- L12 Voltage Transfer Characteristic, BJT Biasing 1Document17 pagesL12 Voltage Transfer Characteristic, BJT Biasing 1de_stanszaNo ratings yet

- EC Signals and SystemsDocument48 pagesEC Signals and SystemsJeeva KeshavNo ratings yet

- EDC Lab ManualDocument45 pagesEDC Lab ManualChirag Sachdeva100% (2)

- Lab 4Document15 pagesLab 4Aliqpsk AlasadyNo ratings yet

- BJT and FET Frequency Response - Lec2Document51 pagesBJT and FET Frequency Response - Lec2Toota TuttaNo ratings yet

- Unit Step Function in MatlabDocument6 pagesUnit Step Function in Matlabshaista005100% (3)

- Electronics Sample Lab ReportDocument10 pagesElectronics Sample Lab ReportLeo Marcelo VillalbaNo ratings yet

- Numerical AnalysisDocument63 pagesNumerical AnalysisMohammad AhmedNo ratings yet

- Electromagnetic Fields II-SummerDocument39 pagesElectromagnetic Fields II-SummerMINESY60% (5)

- Convergence Rates On Root Finding: Com S 477/577 Oct 5, 2004Document5 pagesConvergence Rates On Root Finding: Com S 477/577 Oct 5, 2004Mich LadycanNo ratings yet

- Chapter 15Document10 pagesChapter 15Yug VarshneyNo ratings yet

- ECE 3500 Signals and Systems Quiz Solutions Quiz 1Document2 pagesECE 3500 Signals and Systems Quiz Solutions Quiz 1skybosgNo ratings yet

- Z TransformDocument21 pagesZ Transformadil1122100% (3)

- IV Characteristic TransistorDocument7 pagesIV Characteristic TransistorNida RidzuanNo ratings yet

- Chapter 11 Part 4 Multistage Amplifier - Sem1 1617Document9 pagesChapter 11 Part 4 Multistage Amplifier - Sem1 1617Yue KaiNo ratings yet

- Electronics-2 Lab Report 7Document7 pagesElectronics-2 Lab Report 7siyal343No ratings yet

- Questions On Time-Domain Analysis of CT SystemsDocument20 pagesQuestions On Time-Domain Analysis of CT Systemskibrom atsbhaNo ratings yet

- ECE 3500 Signals and Systems Quiz Solutions Quiz 6Document1 pageECE 3500 Signals and Systems Quiz Solutions Quiz 6skybosgNo ratings yet

- Emitter FollowerDocument8 pagesEmitter FollowerjerlineprincyNo ratings yet

- III. Introduction To Bipolar-Junction Transistors: C B E CE BE BCDocument30 pagesIII. Introduction To Bipolar-Junction Transistors: C B E CE BE BCorangenarwhalNo ratings yet

- ELC 107 Post-Lab 3 (FET II JFET Current Source)Document3 pagesELC 107 Post-Lab 3 (FET II JFET Current Source)Dean Karlo BardelozaNo ratings yet

- Bjts DC BiasingDocument89 pagesBjts DC BiasingVenugopal ReddyvariNo ratings yet

- 14.4 Bode Plots: Frequency Response 589Document12 pages14.4 Bode Plots: Frequency Response 589Luis Lizana100% (1)

- Electromagnetic Waves and Transmission LinesDocument180 pagesElectromagnetic Waves and Transmission LinesGurusreenuNo ratings yet

- Ee105 Fet LectDocument61 pagesEe105 Fet LectKahMun LimNo ratings yet

- The Hybrid Pi and T Models LectureDocument6 pagesThe Hybrid Pi and T Models LecturehasnaintoahaNo ratings yet

- Transistor CharacteristicsDocument44 pagesTransistor CharacteristicsNidhi PatelNo ratings yet

- Signal Flow Graph (Diajarkan)Document57 pagesSignal Flow Graph (Diajarkan)Muhammad DienullahNo ratings yet

- Rate of ConvergenceDocument10 pagesRate of ConvergenceKhalid ShahNo ratings yet

- 2b RectifierDocument21 pages2b RectifierLove StrikeNo ratings yet

- Electrical Properties of Mos DeviceDocument28 pagesElectrical Properties of Mos Devicemayamohan7250% (1)

- DC and AC BridgesDocument55 pagesDC and AC Bridgessaikarthick023100% (1)

- Trapezoidal RuleDocument10 pagesTrapezoidal RuleRicardo Wan Aguero0% (1)

- Digital Systems I EC 381: Mohamed ElgalhudDocument19 pagesDigital Systems I EC 381: Mohamed ElgalhudCorazon corazonNo ratings yet

- Differential AmplifierDocument15 pagesDifferential AmplifierrppvchNo ratings yet

- Frequency Response of FETDocument24 pagesFrequency Response of FETLai Yon Peng100% (2)

- Fourier Series ExercisesDocument1 pageFourier Series ExercisesKarim Karim100% (1)

- BJT Diff AmplifierDocument15 pagesBJT Diff AmplifierAdrià Amézaga SàrriesNo ratings yet

- UNIT 3-2marks-FET PDFDocument9 pagesUNIT 3-2marks-FET PDFpriyanka236No ratings yet

- Nyquist Stability CriterionDocument20 pagesNyquist Stability CriterionmoosuhaibNo ratings yet

- Multistage Transistor AmplifiersDocument8 pagesMultistage Transistor Amplifiersbree789No ratings yet

- MATLAB Programming Tutorial - Version 05-: Electromagnetic Fields Theory (BEE3113)Document32 pagesMATLAB Programming Tutorial - Version 05-: Electromagnetic Fields Theory (BEE3113)Johnjoseph Vera100% (1)

- EDC Question BankDocument6 pagesEDC Question BankSudershan DolliNo ratings yet

- 4 Phasor Diagrams and Phasor AlgebraDocument9 pages4 Phasor Diagrams and Phasor AlgebraIan HughesNo ratings yet

- Electronics 1 Lab Manual PDFDocument30 pagesElectronics 1 Lab Manual PDFAnonymous 7y7TeR0% (1)

- MOD1Document24 pagesMOD1Chilton Fernandes100% (1)

- CH06 FET BiasingDocument39 pagesCH06 FET BiasingRANA RAMEEZNo ratings yet

- DC Biasing of MOSFETDocument13 pagesDC Biasing of MOSFETChilton FernandesNo ratings yet

- CBSE Class11 Maths Notes 13 Limits and DerivativesDocument7 pagesCBSE Class11 Maths Notes 13 Limits and DerivativesRoy0% (1)

- Mech302hw5s 2Document11 pagesMech302hw5s 2priyadarshini212007No ratings yet

- Heart Rate Variability - Wikipedia PDFDocument30 pagesHeart Rate Variability - Wikipedia PDFLevon HovhannisyanNo ratings yet

- Monograph SeismicSafetyDocument63 pagesMonograph SeismicSafetyAlket DhamiNo ratings yet

- PANIC Origin Story (Part 1)Document6 pagesPANIC Origin Story (Part 1)EpicReads100% (3)

- Impact of E-Banking in India: Presented By-Shouvik Maji PGDM - 75Document11 pagesImpact of E-Banking in India: Presented By-Shouvik Maji PGDM - 75Nilanjan GhoshNo ratings yet

- You Are Loved PDFDocument4 pagesYou Are Loved PDFAbrielle Angeli DeticioNo ratings yet

- 2009-Journal of Pharmacy and PharmacologyDocument37 pages2009-Journal of Pharmacy and PharmacologyLeticia Bonancio CerqueiraNo ratings yet

- A Review of Cassiterite Beneficiation PraticesDocument23 pagesA Review of Cassiterite Beneficiation PraticesLevent ErgunNo ratings yet

- Magtajas vs. PryceDocument3 pagesMagtajas vs. PryceRoyce PedemonteNo ratings yet

- Theory of Interpersonal RelationsDocument2 pagesTheory of Interpersonal RelationsAra Gayares Gallo100% (1)

- Sample Opposition To Motion To Alter or Amend Judgment in United States District CourtDocument3 pagesSample Opposition To Motion To Alter or Amend Judgment in United States District CourtStan BurmanNo ratings yet

- A Complete List of Greek Underworld GodsDocument3 pagesA Complete List of Greek Underworld GodsTimothy James M. Madrid100% (1)

- Baath Arab Socialist Party - Constitution (Approved in 1947)Document9 pagesBaath Arab Socialist Party - Constitution (Approved in 1947)Antonio de OdilonNo ratings yet

- Week 4 CasesDocument38 pagesWeek 4 CasesJANNNo ratings yet

- NCLEX 20QUESTIONS 20safety 20and 20infection 20controlDocument8 pagesNCLEX 20QUESTIONS 20safety 20and 20infection 20controlCassey MillanNo ratings yet

- RARC Letter To Tan Seri Razali Ismail July 26-2013Document4 pagesRARC Letter To Tan Seri Razali Ismail July 26-2013Rohingya VisionNo ratings yet

- Ocr Graphics Gcse CourseworkDocument6 pagesOcr Graphics Gcse Courseworkzys0vemap0m3100% (2)

- PPH CasestudyDocument45 pagesPPH CasestudyRona Mae PangilinanNo ratings yet

- Makalsh CMDDocument22 pagesMakalsh CMDMaudy Rahmi HasniawatiNo ratings yet

- G12 PR1 AsDocument34 pagesG12 PR1 Asjaina rose yambao-panerNo ratings yet

- Adobe Voice Assessment Tool-FinalDocument1 pageAdobe Voice Assessment Tool-Finalapi-268484302No ratings yet

- Network Firewall SecurityDocument133 pagesNetwork Firewall Securitysagar323No ratings yet

- Dermatome, Myotome, SclerotomeDocument4 pagesDermatome, Myotome, SclerotomeElka Rifqah100% (3)

- Mil CompiledDocument62 pagesMil CompiledDan VegaNo ratings yet

- History Paper 2 IB Study GuideDocument6 pagesHistory Paper 2 IB Study Guidersuresh1995100% (4)

- Chapter (1) The Accounting EquationDocument46 pagesChapter (1) The Accounting Equationtunlinoo.067433100% (3)

- FR-A800 Plus For Roll To RollDocument40 pagesFR-A800 Plus For Roll To RollCORTOCIRCUITANTENo ratings yet

- Proff Ethi PDFDocument12 pagesProff Ethi PDFgeethammani100% (1)

- Teaching Philosophy StatementDocument25 pagesTeaching Philosophy Statementtchrdale27No ratings yet