Professional Documents

Culture Documents

Short Channel Effects

Short Channel Effects

Uploaded by

Basheer V.PCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Short Channel Effects

Short Channel Effects

Uploaded by

Basheer V.PCopyright:

Available Formats

3.

Short Channel Effects on MOS

Transistors.

Institute of

Microelectronic

Systems

Overview.

Short Channel

Devices.

Velocity Saturation

Effect.

Threshold Voltage

Variations.

Hot Carrier Effects.

Process Variations.

(Source: Jan M. Rabaey, Digital Integrated Circuits)

3: Short Channel Effects

Institute of

Microelectronic

Systems

Short Channel Devices.

As the technology scaling

reaches channel lengths less

than a micron (L<1), second

order effects, that were ignored in

devices with long channel length

(L>1), become very important.

MOSFETs owning those

dimensions are called short

channel devices.

The main second order effects

are: Velocity Saturation,

Threshold Voltage Variations and

Hot Carrier Effects.

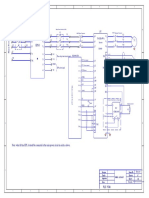

Gate Oxyde

Gate

Source

n+

Polysilicon

Field-Oxyde

Drain

(SiO2)

n+

L<1

p+ stopper

p-substrate

Bulk Contact

CROSS-SECTION of NMOS Transistor

Institute of

Microelectronic

Systems

3: Short Channel Effects

Velocity Saturation Effect (I)

Review of the Classical

Derivation of the Drain Current:

VGS>VT

VDS<<VGS

Induced channel charge at V(x):

Qi(x)=-COX[VGS-V(x)-VT]

VGS

VDS

G

n+

V(x)

n+

+

L

(1)

ID

p-substrate

The current is given as a product

of the drift velocity of the carriers

vn and the available charge:

ID=-vn(x)Qi(x)W

3: Short Channel Effects

MOS transistor and its bias conditions

(2)

Institute of

Microelectronic

Systems

Velocity Saturation Effect (II)

The electron velocity is related

to the electric field through the

mobility:

vn = n ( x ) = n

dV

dx

(3)

Combining (1) and (3) in (2):

IDdx=nCOXW(VGS-V(x)-VT)dV

(4)

Integrating (4) from 0 to L yields

the voltage-current relation of the

transistor:

3: Short Channel Effects

I D = n COX

W

L

VDS

(

)

V

V

V

T

DS

GS

(5)

2

The behavior of the short channel

devices deviates considerably

from this model.

Eq. (3) assumes the mobility n

as a constant independent of the

value of the electric field .

At high electric field carriers fail to

follow this linear model.

This is due to the velocity

saturation effect.

Institute of

Microelectronic

Systems

Velocity Saturation Effect (III)

vn (m/s)

When the electric field reaches a

critical value C, (1.5106 V/m for

p-type silicon) the velocity of the

carriers tends to saturate (105 m/s

for silicon) due to scattering

effects.

vsat=105

constant

velocity

constant mobility

(slope=)

E (V/m)

Ec=1.5

3: Short Channel Effects

Institute of

Microelectronic

Systems

Velocity Saturation Effect (IV)

The impact of this effect over the

drain current of a MOSFET

operating in the linear region is

obtained as follows:

The velocity as a function of the

electric field, plotted in the last

figure can be approximated by:

v=

for C

1 + C

v = vsat

(6)

for C

Reevaluating (1) and (2) using (6):

I D = (VDS ) n COX

W

L

VDS

(

)

V

V

V

T

DS

GS

(7)

with:

(VDS ) =

1 + (VDS C L )

For large values of L or small

values of VDS, approaches 1

and (7) reduces to (5).

For short channel devices <1

and the current is smaller than

what would be expected.

Institute of

Microelectronic

Systems

3: Short Channel Effects

Velocity Saturation Effect (V)

When increasing the drain-source

voltage, the electric field reaches

the value C, and the carriers at

the drain become velocitiy

saturated. Assuming that the drift

velocity is saturated, from (4) with

ndV=vsat the drain current is:

IDSAT=vsatCOXW(VG-VT-VDSAT)

3: Short Channel Effects

Equating (8) and (9) and solving

for VDSAT:

VDSAT = (VGT )VGT

(10)

(8)

Evaluating (7) with VDS=VDSAT

I DSAT = (VDSAT ) n COX

Where VGT is a short notation for

VGS-VT.

VDSAT

W

VGT VDSAT

L

2

For a short channel device and

large enough values of VGT,

(VGT) is smaller than 1, hence

the device enters saturation

before VDS reaches VGS-VT.

Institute of

Microelectronic

Systems

Velocity Saturation Effect (VI)

ID

Long-channel device

VGS=VDD

Short-channel device

VDSAT

VDS

VGS-VT

Short channel devices display an extended saturation

region due to velocity-saturation

Institute of

Microelectronic

Systems

3: Short Channel Effects

Simplificated model for hand calculations (I)

A substantially simpler model can be obtained by making two

assumptions:

Velocity saturates abruptly at C and is approximated by:

=n

for C

=sat= nC

for C

VDSAT at which C is reached is constant and has a value:

VDSAT = L C =

L sat

(11)

Under these conditions the equation for the current in the linear

region remains unchanged from the long channel model. The

value for IDSAT is found by substituting eq. (11) in (5).

3: Short Channel Effects

Institute of

Microelectronic

Systems

10

Simplificated model for hand calculations (II)

I DSAT = n COX

W

L

VDSAT

(VGS VT )VDSAT

I DSAT = vsat COX W (VGS VT ) DSAT

2

(12)

This model is truly first order and empirical and causes

substantial deviations in the transition zone between linear and

velocity saturated regions. However it shows a linear

dependence of the saturation current with respect to VGS for the

short channel devices.

3: Short Channel Effects

Institute of

Microelectronic

Systems

11

I-V characteristics of long- and shortchannel MOS transistors both with W/L=1.5

3: Short Channel Effects

Institute of

Microelectronic

Systems

12

ID-VGS characteristic for long- and short

channel devices both with W/L=1.5

Institute of

Microelectronic

Systems

3: Short Channel Effects

13

Threshold Voltage Variations (I)

For a long channel N-MOS transistor the threshold Voltage is

given for:

VT = VT 0 +

2 F + VSB 2 F

(11)

Eq. (11) states that the threshold Voltage is only a function of the

technology and applied body bias VSB

For short channel devices this model becomes inaccurate and

threshold voltage becomes function of L, W and VDS.

3: Short Channel Effects

Institute of

Microelectronic

Systems

14

Threshold Voltage Variations (II)

VT

VT

Long-channel threshold

Low VDS threshold

VDS

L

Threshold as a function of

the length (for low VDS)

3: Short Channel Effects

Drain-induced barrier lowering

(for low L)

Institute of

Microelectronic

Systems

15

Hot Carrier Effects (I)

During the last decades transistors dimensions were scaled

down, but not the power supply.

The resulting increase in the electric field strength causes an

increasing energy of the electrons.

Some electrons are able to leave the silicon and tunnel into the

gate oxide.

Such electrons are called Hot carriers.

Electrons trapped in the oxide change the VT of the transistors.

This leads to a long term reliabilty problem.

For an electron to become hot an electric field of 104 V/cm is

necessary.

This condition is easily met with channel lengths below 1m.

3: Short Channel Effects

Institute of

Microelectronic

Systems

16

Hot Carrier Effects (II)

Hot carrier effects cause the I-V characteristics of an NMOS transistor to

degrade from extensive usage.

3: Short Channel Effects

Institute of

Microelectronic

Systems

17

Process Variations.

Devices parameters vary between runs and even on

the same die!

Variations in the process parameters , such as impurity concentration densities, oxide thicknesses, and diffusion depths. These are caused by nonuniform conditions during the deposition and/or the diffusion of the

impurities. This introduces variations in the sheet resistances and transistor parameters such as the threshold voltage.

Variations in the dimensions of the devices, mainly resulting from the

limited resolution of the photolithographic process. This causes ( W/L)

variations in MOS transistors and mismatches in the emitter areas of

bipolar devices.

3: Short Channel Effects

Institute of

Microelectronic

Systems

18

Impact of Device Variations.

2.10

2.10

Delay (nsec)

Delay (nsec)

1.90

1.90

1.70

1.70

1.50

1.10 1.20 1.30 1.40 1.50 1.60

1.50

0.90

Leff (in mm)

0.80

0.70

0.60 0.50

VTp (V)

Delay of Adder circuit as a function of variations in L and VT

Institute of

Microelectronic

Systems

3: Short Channel Effects

19

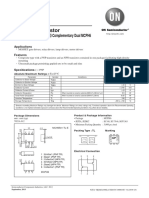

Parameter values for a 0.25m CMOS

process. (minimum length devices).

NMOS

PMOS

VTO (V)

0.43

-0.4

3: Short Channel Effects

(V0.5)

0.4

-0.4

VDSAT (V)

0.63

-1

Institute of

Microelectronic

Systems

K (A/V2)

115 10-6

-30 10-6

(V-1)

0.06

-0.1

20

You might also like

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (540)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5813)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (844)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (822)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (348)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1092)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Mosfet 01Document56 pagesMosfet 01Edward Allan MangubatNo ratings yet

- Embedded CDocument111 pagesEmbedded CMohammed El-Adawy100% (7)

- IGBTDocument22 pagesIGBTumeshgangwar100% (1)

- R0 - Electrical Drawing OC 2030290Document17 pagesR0 - Electrical Drawing OC 2030290Vivekananda Mal100% (2)

- DC Load CalculationsDocument20 pagesDC Load Calculationsraghavendran raghuNo ratings yet

- Timing PathsDocument44 pagesTiming PathsMohammed El-Adawy100% (2)

- Electric Drawing-FR2000Document19 pagesElectric Drawing-FR2000MuMoMa100% (1)

- Buchholz Relay in Transformers (Working Principle) - Electrical4UDocument5 pagesBuchholz Relay in Transformers (Working Principle) - Electrical4UHarsh PatelNo ratings yet

- Final NEO 16Document49 pagesFinal NEO 16Shiva Bhasker ReddyNo ratings yet

- Mips VHDLDocument22 pagesMips VHDLMohammed El-AdawyNo ratings yet

- Color Slides SOCE 3 3Document184 pagesColor Slides SOCE 3 3Mohammed El-AdawyNo ratings yet

- Xilinx Tutorial Spartan3 Home PCDocument50 pagesXilinx Tutorial Spartan3 Home PCCruise_IceNo ratings yet

- Eetop - CN FPR 10 1.labDocument162 pagesEetop - CN FPR 10 1.labMohammed El-AdawyNo ratings yet

- Module 1. Introduction To ASIC DesignDocument2 pagesModule 1. Introduction To ASIC DesignMohammed El-AdawyNo ratings yet

- Introduction To ASIC Design: Dr. Paul D. Franzon Genreal OutlineDocument54 pagesIntroduction To ASIC Design: Dr. Paul D. Franzon Genreal OutlineMohammed El-AdawyNo ratings yet

- ECE465 Lecture Notes # 11 Clocking Methodologies: Shantanu Dutt UICDocument21 pagesECE465 Lecture Notes # 11 Clocking Methodologies: Shantanu Dutt UICMohammed El-AdawyNo ratings yet

- ELC609F12 Lec0 IntroductionDocument16 pagesELC609F12 Lec0 IntroductionMohammed El-AdawyNo ratings yet

- Uvm Users Guide 1.1Document198 pagesUvm Users Guide 1.1boojahNo ratings yet

- Valeo Exam CafcDocument17 pagesValeo Exam CafcMohammed El-Adawy100% (1)

- Electrical Material ListDocument2 pagesElectrical Material Listravindrakumar sataoNo ratings yet

- Unit 3: MOS Electrostatics: The Mobile Charge vs. Gate VoltageDocument22 pagesUnit 3: MOS Electrostatics: The Mobile Charge vs. Gate VoltagealNo ratings yet

- ABD OL 108 A3.pdf.9Document1 pageABD OL 108 A3.pdf.9Berkah Jaya PanelNo ratings yet

- Nema 2 SDDocument3 pagesNema 2 SDJean Charles GaramNo ratings yet

- Eletromagnetic - William HaytDocument11 pagesEletromagnetic - William HaytshubhNo ratings yet

- 3TW42 DOL StarterDocument26 pages3TW42 DOL StarterluvlijNo ratings yet

- AF-E-06-16 - 0 - 132kV Bus Section E09 - Schematic DiagramDocument42 pagesAF-E-06-16 - 0 - 132kV Bus Section E09 - Schematic DiagramAdetunji Babatunde TaiwoNo ratings yet

- 01 Logic DesignDocument53 pages01 Logic DesignShouvik MusavvirNo ratings yet

- MCH6541 Dual 700ma 30V 500MhzDocument9 pagesMCH6541 Dual 700ma 30V 500MhzRaduNo ratings yet

- Ref615 Ansi v2.0 Hmi Led Labels Template 0Document6 pagesRef615 Ansi v2.0 Hmi Led Labels Template 0Shigue París WagataNo ratings yet

- Corner Effect in Double and Triple GateDocument4 pagesCorner Effect in Double and Triple GateIELTS 2021.10No ratings yet

- SCS, Lascr, Diac and TriacDocument16 pagesSCS, Lascr, Diac and TriacRyan Paul RiwarinNo ratings yet

- Color PlatesDocument4 pagesColor PlatesChaitanya KumarNo ratings yet

- Push Button FlyerDocument2 pagesPush Button FlyerskodgeNo ratings yet

- DET40073 Topic 1Document54 pagesDET40073 Topic 1HAAVINESHNo ratings yet

- Multi 9 Catalogue Ƒinal PDFDocument195 pagesMulti 9 Catalogue Ƒinal PDFms100% (1)

- A#5 G4 Romero Bsee1fDocument25 pagesA#5 G4 Romero Bsee1fRomero, Ken Angelo B.No ratings yet

- ATS O-SungDocument28 pagesATS O-Sungba sonNo ratings yet

- Power TransistorDocument37 pagesPower Transistorsaikarthick023No ratings yet

- ?M4 - Formative Assessment - Electronics Devices & CircuitsDocument5 pages?M4 - Formative Assessment - Electronics Devices & CircuitsRoan ChuaNo ratings yet

- BJT الترانزستور ثنائي القطبية ـ موقع الفريد في الفيزياءDocument24 pagesBJT الترانزستور ثنائي القطبية ـ موقع الفريد في الفيزياءOssama BohamdNo ratings yet

- Junction Field Effect TransistorDocument27 pagesJunction Field Effect Transistorsanthosh100% (1)

- Transistors ProductsDocument2 pagesTransistors ProductsJose GuerreroNo ratings yet