Professional Documents

Culture Documents

Arithmetic / Logic Unit - ALU Design

Arithmetic / Logic Unit - ALU Design

Uploaded by

Mihir GajjarOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Arithmetic / Logic Unit - ALU Design

Arithmetic / Logic Unit - ALU Design

Uploaded by

Mihir GajjarCopyright:

Available Formats

Arithmetic / Logic Unit

ALU

Design

Dr. Arjan Durresi

Louisiana State University

Baton Rouge, LA 70810

Durresi@Csc.LSU.Edu

These slides are available at:

http://www.csc.lsu.edu/~durresi/CSC3501_07/

Louisiana State University

7- Arithmetic / Logic Unit ALU Design - 1

CSC3501 S07

Overview

1-Bit ALU

Full Adder

32-Bit ALU

Louisiana State University

7- Arithmetic / Logic Unit ALU Design - 2

CSC3501 S07

Different Implementations

Not easy to decide the best way to build something

Don't want too many inputs to a single gate

Dont want to have to go through too many gates

for our purposes, ease of comprehension is important

Let's look at a 1-bit ALU for addition:

CarryIn

a

Sum

b

cout = a b + a cin + b cin

sum = a xor b xor cin

CarryOut

How could we build a 1-bit ALU for add, and, and or?

How could we build a 32-bit ALU?

Louisiana State University

7- Arithmetic / Logic Unit ALU Design - 3

CSC3501 S07

32-bit ALU

Our ALU should be able to perform functions:

logical and function

logical or function

arithmetic add function

arithmetic subtract function

arithmetic slt (set-less-then) function

logical nor function

ALU control lines define a function to be performed on A and B.

Louisiana State University

7- Arithmetic / Logic Unit ALU Design - 4

CSC3501 S07

A 1-Bit ALU

The 1-bit logical unit for AND and OR

Louisiana State University

7- Arithmetic / Logic Unit ALU Design - 5

CSC3501 S07

A Full Adder

Louisiana State University

7- Arithmetic / Logic Unit ALU Design - 6

CSC3501 S07

A Full Adder

CarryOut=( b*CarryIn)+( a*CarryIn)+( a*b)+(a*b*CarryIn)

CarryOut=( b*CarryIn)+( a*CarryIn)+( a*b)

Louisiana State University

7- Arithmetic / Logic Unit ALU Design - 7

CSC3501 S07

A Full Adder

Sum=(abCarryIn)+(abCarryIn)+(abCarryIn)+(abCarryIn)

Louisiana State University

7- Arithmetic / Logic Unit ALU Design - 8

CSC3501 S07

Functioning of 32-bit ALU

Result lines provide result of the chosen function applied to

values of A and B Since this ALU operates on 32-bit operands, it

is called 32-bit ALU

Zero output indicates if all Result lines have value 0

Overflow indicates a sign integer overflow of add and subtract

functions; for unsigned integers, this overflow indicator does not

provide any useful information

Carry out indicates carry out and unsigned integer overflow

Louisiana State University

7- Arithmetic / Logic Unit ALU Design - 9

CSC3501 S07

Designing 32-bit ALU: Beginning

Louisiana State University

7- Arithmetic / Logic Unit ALU Design - 10

CSC3501 S07

Designing 32-bit ALU: Principles

Louisiana State University

7- Arithmetic / Logic Unit ALU Design - 11

CSC3501 S07

32-bit Adder

Louisiana State University

This is a ripple carry adder.

The key to speeding up addition

is determining carry out in the

higher order bits sooner.

Result: Carry look-ahead

adder.

7- Arithmetic / Logic Unit ALU Design - 12

CSC3501 S07

32-bit ALU With 3 Functions

CarryOut

Louisiana State University

7- Arithmetic / Logic Unit ALU Design - 13

CSC3501 S07

32-bit Subtractor

Louisiana State University

7- Arithmetic / Logic Unit ALU Design - 14

CSC3501 S07

32-bit Adder / Subtractor

Louisiana State University

7- Arithmetic / Logic Unit ALU Design - 15

CSC3501 S07

32-bit ALU With 4 Functions

Louisiana State University

7- Arithmetic / Logic Unit ALU Design - 16

CSC3501 S07

2s Complement Overflow

Louisiana State University

7- Arithmetic / Logic Unit ALU Design - 17

CSC3501 S07

32-bit ALU With 4 Functions

and Overflow

Louisiana State University

7- Arithmetic / Logic Unit ALU Design - 18

CSC3501 S07

Set Less Than (slt) Function

Louisiana State University

7- Arithmetic / Logic Unit ALU Design - 19

CSC3501 S07

32-bit ALU With 5 Functions

Louisiana State University

7- Arithmetic / Logic Unit ALU Design - 20

CSC3501 S07

Zero

AB=0 A=B

To test fore Zero:

Zero = (Result31+Result30+ . . . Result2+ Result1+ Result0)

Louisiana State University

7- Arithmetic / Logic Unit ALU Design - 21

CSC3501 S07

32-bit ALU with 5 Functions

and Zero

Louisiana State University

7- Arithmetic / Logic Unit ALU Design - 22

CSC3501 S07

Faster Addition: Carry Lookahead

The key to speeding up addition is determining the

carry in to the high-order bits sooner.

Fast Carry Using Infinite Hardware

CarryIn2 = (b1CarryIn1)+(a1CarryIn1)+ (a1b1)

CarryIn1=(b0CarryIn0)+(a0CarryIn0)+ (a0b0)

And

C2=(a1a0b0)+(a1a0c0)+(a1b0c0) +

+(b1a0b0)+(b1a0c0)+(b1b0c0)+(a1b1)

Louisiana State University

7- Arithmetic / Logic Unit ALU Design - 23

CSC3501 S07

Carry-lookahead Adder

ci+1 = (bici) + (aici) + (aibi) =

= (aibi) + (ai+ bi) ci

Generate (gi) and propagate (pi)

gi = ai bi

pi = ai + bi

ci+1 = gi + pi ci

If gi = 1. That is, the adder generates a CarryOut (ci+1)

independent of the value of CarryIn (ci)

ci+1 = gi + pi ci = 1

If gi = 0 and pi = 1

ci+1 = gi + pi ci = 0 + 1 ci = ci

The adder propagates CarryIn to a CarryOut.

CarryIni+1 is a 1 if either gi is 1 or both pi is 1 and CarryIni is 1.

Louisiana State University

7- Arithmetic / Logic Unit ALU Design - 24

CSC3501 S07

Carry-lookahead Adder

Louisiana State University

7- Arithmetic / Logic Unit ALU Design - 25

CSC3501 S07

Carry-lookahead Adder

A plumbing analogy for

carry lookahead for 1

bit, 2 bits, and 4 bits

using water pipes and

valves.

Louisiana State University

7- Arithmetic / Logic Unit ALU Design - 26

CSC3501 S07

Fast Carry Using the Second

Level of Abstraction

To go faster, well need carry lookahead at a higher level.

For the four 4-bit adder blocks:

That is, the super propagate signal for the 4-bit abstraction

(Pi) is true only if each of the bits in the group will propagate a

carry.

Louisiana State University

7- Arithmetic / Logic Unit ALU Design - 27

CSC3501 S07

Fast Carry Using the Second

Level of Abstraction

For the super generate signal (Gi), we care only if there is a

carry out of the most significant bit of the 4-bit group.

This obviously occurs if generate is true for that most

significant bit; it also occurs if an earlier generate is true and all

the intermediate propagates, including that of the most

significant bit, are also true:

Louisiana State University

7- Arithmetic / Logic Unit ALU Design - 28

CSC3501 S07

Fast Carry Using the Second

Level of Abstraction

A plumbing analogy for the nextlevel carry-lookahead signals P0

and G0.

P0 is open only if all four

propagates (pi) are open, while

water flows in G0 only if at least

one generate (gi) is open and all

the propagates downstream from

that generate are open.

Louisiana State University

7- Arithmetic / Logic Unit ALU Design - 29

CSC3501 S07

Example: Speed of Ripple Carry

versus Carry Lookahead

Time is estimated by simply counting the number of gates along

the path through a piece of logic. Compare the number of gate

delays for paths of two 16-bit adders, one using ripple carry and

one using two-level carry lookahead.

the carry out signal takes two gate delays per bit. Then the

number of gate delays between a carry in to the least significant

bit and the carry out of the most significant is 16 2 = 32.

Louisiana State University

7- Arithmetic / Logic Unit ALU Design - 30

CSC3501 S07

Example

For carry lookahead, the carry out of the most

significant bit is just C4, defined in the example. It

takes two levels of logic to specify C4 in terms of Pi

and Gi (the OR of several AND terms). Pi is specified

in one level of logic (AND) using pi, and Gi is specified

in two levels using pi and gi, so the worst case for this

next level of abstraction is two levels of logic. pi and

gi are each one level of logic, defined in terms of ai

and bi. If we assume one gate delay for each level of

logic in these equations, the worst case is 2 + 2 + 1 = 5

gate delays.

Louisiana State University

7- Arithmetic / Logic Unit ALU Design - 31

CSC3501 S07

NOR

Louisiana State University

7- Arithmetic / Logic Unit ALU Design - 32

CSC3501 S07

32-bit ALU with 6 Functions

Louisiana State University

7- Arithmetic / Logic Unit ALU Design - 33

CSC3501 S07

32-bit ALU Elaboration

We have now accounted for all but one of the

arithmetic and logic functions for the core MIPS

instruction set. 32-bit ALU with 6 functions omits

support for shift instructions.

It would be possible to widen 1-bit ALU multiplexer to

include 1-bit shift left and/or 1-bit shift right.

Hardware designers created the circuit called a barrel

shifter, which can shift from 1 to 31 bits in no more

time than it takes to add two 32-bit numbers. Thus,

shifting is normally done outside the ALU.

Louisiana State University

7- Arithmetic / Logic Unit ALU Design - 34

CSC3501 S07

Summary

1-Bit ALU

Full Adder

32-Bit ALU

Louisiana State University

7- Arithmetic / Logic Unit ALU Design - 35

CSC3501 S07

You might also like

- OpenMPCoursework2Document5 pagesOpenMPCoursework2Jaokd100% (1)

- Running Errands #2: Lesson 16Document14 pagesRunning Errands #2: Lesson 16Camila ReyesNo ratings yet

- Lec 1 - Number Systems and Digital LogicDocument38 pagesLec 1 - Number Systems and Digital LogicSAVILASH A/L RAVINDRANNo ratings yet

- Student Marks AnalysisDocument24 pagesStudent Marks AnalysisjayNo ratings yet

- DanielDocument67 pagesDanielMercy EmmansonNo ratings yet

- Computer Science Capstone Project: Course DescriptionDocument7 pagesComputer Science Capstone Project: Course DescriptionGrantham UniversityNo ratings yet

- Software Requirement Specification (SRS) : Online Photo GalleryDocument5 pagesSoftware Requirement Specification (SRS) : Online Photo Galleryklint0% (1)

- Assignment 3.solutionDocument2 pagesAssignment 3.solutionMohammad SharifNo ratings yet

- 04 - 05-AI-Knowledge and ReasoningDocument61 pages04 - 05-AI-Knowledge and ReasoningderbewNo ratings yet

- CH 1Document29 pagesCH 1himaws72No ratings yet

- Computer Network - CS610 Power Point Slides Lecture 01Document19 pagesComputer Network - CS610 Power Point Slides Lecture 01Ibrahim ChoudaryNo ratings yet

- Parallel Processing Assignment 1Document14 pagesParallel Processing Assignment 1RobelNo ratings yet

- Lab Manual 14 - GUI-1Document15 pagesLab Manual 14 - GUI-1saif habibNo ratings yet

- R7411503-Performance Evalution of Computer SystemsDocument4 pagesR7411503-Performance Evalution of Computer SystemssivabharathamurthyNo ratings yet

- CMP 103 3 Programming in C 3 0 3Document2 pagesCMP 103 3 Programming in C 3 0 3Dinesh PudasainiNo ratings yet

- 1 - 1 - Fundamentals - Algorithm - Problem - SlovingDocument24 pages1 - 1 - Fundamentals - Algorithm - Problem - SlovingKarthikeyan RVNo ratings yet

- Chapter 2 - Database System Model and ArchitectureDocument22 pagesChapter 2 - Database System Model and ArchitecturesfdNo ratings yet

- Object Oriented SAD-3 Requirement ElicitationDocument50 pagesObject Oriented SAD-3 Requirement ElicitationBiruk BelaynehNo ratings yet

- Adama Science and Technology University: School of Electrical Engineering and ComputingDocument10 pagesAdama Science and Technology University: School of Electrical Engineering and ComputingDechasa ShimelsNo ratings yet

- Comprehensive 1 PDFDocument154 pagesComprehensive 1 PDFSrinithy SaravananNo ratings yet

- Introduction To ComputingDocument270 pagesIntroduction To ComputingNadaNo ratings yet

- Es 4 SolutionDocument7 pagesEs 4 SolutionshimelisNo ratings yet

- Expert System DevelopmentDocument7 pagesExpert System DevelopmentbabaNo ratings yet

- Software Tools: Human Computer InteractionDocument7 pagesSoftware Tools: Human Computer InteractionWangNo ratings yet

- Oltp VS OlapDocument9 pagesOltp VS OlapSikkandar Sha100% (1)

- Practical 1: Aim: To Study and Create Use-Case Diagram Theory: Use-Case DiagramDocument35 pagesPractical 1: Aim: To Study and Create Use-Case Diagram Theory: Use-Case DiagramVaishali Amol KorgaonkarNo ratings yet

- Introduction To Data Management: Chapter 1, Pratt & AdamskiDocument25 pagesIntroduction To Data Management: Chapter 1, Pratt & Adamskiahmad100% (1)

- SE Task 1Document2 pagesSE Task 1Em ShabirinNo ratings yet

- Class 12 Computer Notes by Binod RijalDocument31 pagesClass 12 Computer Notes by Binod Rijalसन्दिप तिम्ल्सिना100% (1)

- Solution To Assi1Document8 pagesSolution To Assi1Yogesh GandhiNo ratings yet

- Laboratory Activitity #1 - NewDocument10 pagesLaboratory Activitity #1 - NewCharian Andojar PendicaNo ratings yet

- Uml ElevatorDocument29 pagesUml ElevatorLaveesh AgrawalNo ratings yet

- Presentation Abstraction ControlDocument5 pagesPresentation Abstraction ControlVishy AnandNo ratings yet

- CS504MCQs - Final - Bydr - TariqHanif PDFDocument21 pagesCS504MCQs - Final - Bydr - TariqHanif PDFAmjad Ali0% (1)

- Data Structure Midterm Exam Ay 2023-2024Document7 pagesData Structure Midterm Exam Ay 2023-2024arjeanetteNo ratings yet

- DFD ExampleDocument4 pagesDFD ExamplePauline Bogador MayordomoNo ratings yet

- SE351-Software Construction and Development: Semester 5Document21 pagesSE351-Software Construction and Development: Semester 5Ali RAZA100% (1)

- Practice Quiz AnswersDocument40 pagesPractice Quiz AnswersReddy Freddy75% (4)

- Electronics and Communication Engineering CurriculamDocument6 pagesElectronics and Communication Engineering Curriculamraghucp141No ratings yet

- Library Book CirculationDocument89 pagesLibrary Book CirculationAmritaSinghNo ratings yet

- Python Video Lectures ListDocument5 pagesPython Video Lectures ListSana ArshadNo ratings yet

- Computer ScienceDocument5 pagesComputer ScienceMehari KirosNo ratings yet

- Implementation of Student Attendance Management SystemDocument7 pagesImplementation of Student Attendance Management SystemIJIRSTNo ratings yet

- ComEng22 Syllabus RevisedDocument111 pagesComEng22 Syllabus RevisedHope LeeNo ratings yet

- Srms ProjectDocument70 pagesSrms Projectsai prasad reddyNo ratings yet

- Second Generation ComputersDocument4 pagesSecond Generation ComputersJohn James AntipoloNo ratings yet

- Unity University: Blood Bank Management SystemDocument96 pagesUnity University: Blood Bank Management Systembethlehem kebedeNo ratings yet

- Student Information System System DesignDocument15 pagesStudent Information System System DesignKUSHAL HNo ratings yet

- Hostel Management SystemDocument26 pagesHostel Management SystemVickram Jain50% (2)

- sOFTWARE REUSEDocument48 pagessOFTWARE REUSENaresh KumarNo ratings yet

- A Movie Recommender System: MOVREC: Manoj Kumar D.K. Yadav Ankur Singh Vijay Kr. GuptaDocument5 pagesA Movie Recommender System: MOVREC: Manoj Kumar D.K. Yadav Ankur Singh Vijay Kr. GuptaDeepak JainNo ratings yet

- Se Practical FileDocument38 pagesSe Practical FileChirag VadhavanaNo ratings yet

- Unit-III-Loader & Linker - Sri EshwarDocument91 pagesUnit-III-Loader & Linker - Sri EshwarVeningstonk AgeeshNo ratings yet

- CS352H: Computer Systems Architecture: Lecture 5: MIPS Integer ALU September 10, 2009Document27 pagesCS352H: Computer Systems Architecture: Lecture 5: MIPS Integer ALU September 10, 2009farah_nishuNo ratings yet

- CH 02Document48 pagesCH 02Hemant RajakNo ratings yet

- Unit 04 English Sentence To Boolean EquationsDocument30 pagesUnit 04 English Sentence To Boolean EquationsJhill-Jhill Jimenez Dela PeñaNo ratings yet

- Vlsi Lab7 F 13 V1Document9 pagesVlsi Lab7 F 13 V1Shannan WeberNo ratings yet

- CH 02Document47 pagesCH 02Praveen KumarNo ratings yet

- 1 PBDocument21 pages1 PBahmedmamdouhelnajjarNo ratings yet

- Vlsi Implementation For High Speed AddersDocument6 pagesVlsi Implementation For High Speed AddersPardha Saradhi Damarla100% (1)

- BCE-UNIT-2 Components of BuilDocument84 pagesBCE-UNIT-2 Components of Builviveksp99No ratings yet

- Boletin FS 1035MFPDocument19 pagesBoletin FS 1035MFPDarkEnganNo ratings yet

- Making Symbian Development Easier With FShell: A Console Environment For The Symbian PlatformDocument13 pagesMaking Symbian Development Easier With FShell: A Console Environment For The Symbian PlatformSEE2010 Platform Developer TrackNo ratings yet

- Weavelink 1 2V 3R LP R1Document33 pagesWeavelink 1 2V 3R LP R1tery100% (1)

- Knowledge Sharing 2014 Book of Abstracts: An EMC Proven Professional PublicationDocument60 pagesKnowledge Sharing 2014 Book of Abstracts: An EMC Proven Professional PublicationAbhishekBhauNo ratings yet

- Eduroam Installation in ZambiaDocument11 pagesEduroam Installation in ZambiaThomas YobeNo ratings yet

- Intercollegiate Halls: Introducing Eleanor Rosa HouseDocument9 pagesIntercollegiate Halls: Introducing Eleanor Rosa HouseSandra VucevicNo ratings yet

- Impressions of GuanajuatoDocument5 pagesImpressions of Guanajuatodsalamon330No ratings yet

- Huntsman Tooling BoardDocument3 pagesHuntsman Tooling BoardGaurav GuptaNo ratings yet

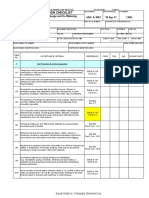

- Saudi Aramco Inspection ChecklistDocument4 pagesSaudi Aramco Inspection Checklistkarthi51289No ratings yet

- Space Frame Structures: AR - 302 Building Construction & Materials VDocument9 pagesSpace Frame Structures: AR - 302 Building Construction & Materials Vkushagra agrawalNo ratings yet

- PDP 424MV DatasheetDocument12 pagesPDP 424MV DatasheetJose BenavidesNo ratings yet

- Final Bill SEBIDocument138 pagesFinal Bill SEBISarvagya UpadhyayNo ratings yet

- ps0315 PDFDocument229 pagesps0315 PDFerrosNo ratings yet

- Kitchen Basket ss304 Undermount SeriesDocument2 pagesKitchen Basket ss304 Undermount SeriesbarizaNo ratings yet

- PESU - 5th Sem Course InformationDocument28 pagesPESU - 5th Sem Course InformationJuthik BVNo ratings yet

- Speech 1 TranscriptDocument5 pagesSpeech 1 TranscriptAli LaodeNo ratings yet

- Manual Dell Poweredge 2850 2Document25 pagesManual Dell Poweredge 2850 2BrenardcrespoNo ratings yet

- RRC Connection ReDocument3 pagesRRC Connection ReSumitNo ratings yet

- Renaissance and Baroques Art Styles-TechniquesDocument64 pagesRenaissance and Baroques Art Styles-TechniquesDONNALYN TORRESNo ratings yet

- Fortios Handbook 54 PDFDocument3,366 pagesFortios Handbook 54 PDFcalad03No ratings yet

- Katalog Zao Belzarubezhstroy enDocument39 pagesKatalog Zao Belzarubezhstroy enGustavoDosRamosNo ratings yet

- Nomenclature (Peb)Document4 pagesNomenclature (Peb)Santhosh ChandramNo ratings yet

- Drawing List - BMSDocument2 pagesDrawing List - BMShannaNo ratings yet

- Xiaomi Redmi Note TD&WCDMA Schematic PDFDocument17 pagesXiaomi Redmi Note TD&WCDMA Schematic PDFwongpeihung0% (1)

- NV10Document39 pagesNV10Marian BaciuNo ratings yet

- Roof Rainwater Harvesting: Questions AnsweredDocument2 pagesRoof Rainwater Harvesting: Questions AnsweredGreen Action Sustainable Technology GroupNo ratings yet

- Genetic EpistemologyDocument9 pagesGenetic EpistemologyNorlyn ValeraNo ratings yet

- NGCP Laspinas AccomplishmentDocument12 pagesNGCP Laspinas AccomplishmentNAIRASECNo ratings yet

- Book Review Towards A New Engineering ReDocument1 pageBook Review Towards A New Engineering ReMentor LlunjiNo ratings yet