Professional Documents

Culture Documents

Arithmetic Instructions Mnemonics Description Bytes Instruction Cycles

Arithmetic Instructions Mnemonics Description Bytes Instruction Cycles

Uploaded by

Deepak AcharOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Arithmetic Instructions Mnemonics Description Bytes Instruction Cycles

Arithmetic Instructions Mnemonics Description Bytes Instruction Cycles

Uploaded by

Deepak AcharCopyright:

Available Formats

8051 has about 111 instructions.

These can be grouped into the following categories

1. Arithmetic Instructions

2. Logical Instructions

3. Data Transfer instructions

4. Boolean Variable Instructions

5. Program Branching Instructions

The following nomenclatures for register, data, address and variables are used while write instructions.

A: Accumulator

B: "B" register

C: Carry bit

Rn: Register R0 - R7 of the currently selected register bank

Direct: 8-bit internal direct address for data. The data could be in lower 128bytes of RAM (00 - 7FH) or it could be in

the special function register (80 - FFH).

@Ri: 8-bit external or internal RAM address available in register R0 or R1. This is used for indirect addressing mode.

#data8: Immediate 8-bit data available in the instruction.

#data16: Immediate 16-bit data available in the instruction.

Addr11: 11-bit destination address for short absolute jump. Used by instructions AJMP & ACALL. Jump range is 2 kbyte

(one page).

Addr16: 16-bit destination address for long call or long jump.

Rel: 2's complement 8-bit offset (one - byte) used for short jump (SJMP) and all conditional jumps.

bit: Directly addressed bit in internal RAM or SFR

Arithmetic Instructions

Mnemonics

Description

Bytes

Instruction Cycles

ADD A, Rn

A + Rn

ADD A, direct

A + (direct)

ADD A, @Ri

A + @Ri

ADD A, #data

A + data

ADDC A, Rn

A + Rn + C

ADDC A, direct

A + (direct) + C

ADDC A, @Ri

A + @Ri + C

ADDC A, #data

A + data + C

DA A

Decimal adjust accumulator

DIV AB

Divide A by B

A

quotient

B

remainder

DEC A

DEC Rn

Rn

DEC direct

(direct)

DEC @Ri

@Ri

INC A

INC Rn

Rn

INC direct

(direct)

INC @Ri

@Ri

INC DPTR

DPTR

DPTR +1

MUL AB

Multiply A by B

A

low byte (A*B)

A -1

Rn - 1

(direct) - 1

@Ri - 1

A+1

Rn + 1

(direct) + 1

@Ri +1

high byte (A* B)

SUBB A, Rn

A - Rn - C

SUBB A, direct

A - (direct) - C

SUBB A, @Ri

A - @Ri - C

SUBB A, #data

A - data - C

Logical Instructions

Mnemonics

Description

Bytes

Instruction Cycles

ANL A, Rn

A AND Rn

ANL A, direct

A AND (direct)

ANL A, @Ri

A AND @Ri

ANL A, #data

A AND data

ANL direct, A

(direct)

(direct) AND A

ANL direct, #data

(direct)

(direct) AND data

CLR A

00H

CPL A

ORL A, Rn

A OR Rn

ORL A, direct

A OR (direct)

ORL A, @Ri

A OR @Ri

ORL A, #data

A OR data

ORL direct, A

(direct)

(direct) OR A

ORL direct, #data

(direct)

(direct) OR data

RL A

Rotate accumulator left

RLC A

Rotate accumulator left through carry 1

RR A

Rotate accumulator right

RRC A

Rotate accumulator right through carry 1

SWAP A

Swap nibbles within Acumulator

XRL A, Rn

A EXOR Rn

XRL A, direct

A EXOR (direct)

XRL A, @Ri

A EXOR @Ri

XRL A, #data

A EXOR data

XRL direct, A

(direct)

(direct) EXOR A

XRL direct, #data

(direct)

(direct) EXOR data

Data Transfer Instructions

Mnemonics

Description

Bytes

Instruction Cycles

MOV A, Rn

Rn

MOV A, direct

(direct)

MOV A, @Ri

@Ri

MOV A, #data

data

MOV Rn, A

Rn

MOV Rn, direct

Rn

(direct)

MOV Rn, #data

Rn

data

MOV direct, A

(direct)

MOV direct, Rn

(direct)

Rn

MOV direct1, direct2 (direct1)

(direct2)

MOV direct, @Ri

(direct)

@Ri

MOV direct, #data

(direct)

#data

MOV @Ri, A

@Ri

MOV @Ri, direct

@Ri

(direct)

MOV @Ri, #data

@Ri

data

MOV DPTR, #data16 DPTR

data16

MOVC A, @A+DPTR A

Code byte pointed by A + DPTR

MOVC A, @A+PC

Code byte pointed by A + PC

MOVC A, @Ri

Code byte pointed by Ri 8-bit address)

MOVX A, @DPTR

External data pointed by DPTR

MOVX @Ri, A

@Ri

MOVX @DPTR, A

@DPTR

PUSH direct

(SP)

POP direct

(direct)

XCH Rn

A (External data - 8bit address)

(direct)

(SP)

Exchange A with Rn

XCH direct

Exchange A with direct byte

XCH @Ri

Exchange A with indirect RAM

XCHD A, @Ri

Exchange least significant nibble of A with that of 1

indirect RAM

A(External data - 16bit address)

Boolean Variable Instructions

Mnemonics

Description

Bytes

Instruction Cycles

CLR C

C-bit

CLR bit

bit

SET C

SET bit

bit

CPL C

CPL bit

bit

ANL C, /bit

C.

ANL C, bit

C. bit

ORL C, /bit

C+

ORL C, bit

C + bit

MOV C, bit

bit

MOV bit, C

bit

Program Branching Instructions

Mnemonics

Description

Bytes

Instruction Cycles

ACALL addr11

PC + 2

(SP) ; addr 11

AJMP addr11

Addr11

PC

CJNE A, direct, rel

Compare with A, jump (PC + rel) if not equal

CJNE A, #data, rel

Compare with A, jump (PC + rel) if not equal

CJNE Rn, #data, rel

Compare with Rn, jump (PC + rel) if not equal

CJNE @Ri, #data, rel

Compare with @Ri A, jump (PC + rel) if not equal

DJNZ Rn, rel

Decrement Rn, jump if not zero

DJNZ direct, rel

Decrement (direct), jump if not zero

JC rel

Jump (PC + rel) if C bit = 1

JNC rel

Jump (PC + rel) if C bit = 0

JB bit, rel

Jump (PC + rel) if bit = 1

JNB bit, rel

Jump (PC + rel) if bit = 0

PC

JBC bit, rel

Jump (PC + rel) if bit = 1

JMP @A+DPTR

A+DPTR

JZ rel

If A=0, jump to PC + rel

JNZ rel

If A 0 , jump to PC + rel

LCALL addr16

PC + 3

(SP), addr16

LJMP addr 16

Addr16

PC

NOP

No operation

RET

(SP)

PC

RETI

(SP)

PC, Enable Interrupt

SJMP rel

PC + 2 + rel

JMP @A+DPTR

JZ rel

JNZ rel

NOP

A+DPTR

PC

If A = 0. jump PC+ rel

If A 0, jump PC + rel

No operation

1

2

2

1

2

2

2

1

PC

PC

PC

You might also like

- a拉扎维模拟CMOS集成电路第二版最新答案Document1,603 pagesa拉扎维模拟CMOS集成电路第二版最新答案就爱吃饭团No ratings yet

- Control Transfer Instructions and Programming Using 8051 MicrocontrolleDocument72 pagesControl Transfer Instructions and Programming Using 8051 MicrocontrollePujaChaudhuryNo ratings yet

- 8051 Instruction Set Summary - AtmelDocument4 pages8051 Instruction Set Summary - AtmelRaissan ChedidNo ratings yet

- 8051 Instruction Set SlidesDocument72 pages8051 Instruction Set SlidesNaWin NKNo ratings yet

- Microcontroller Instruction SetDocument73 pagesMicrocontroller Instruction Set4SI21EC037 MONOJ S BNo ratings yet

- 8051 Addressing ModesDocument73 pages8051 Addressing ModesKUSHAGRA GUPTA 13BEE0102No ratings yet

- Microprocessor and Microcontrroller Module 1 - Calicut UniversityDocument32 pagesMicroprocessor and Microcontrroller Module 1 - Calicut UniversityAshwin GopinathNo ratings yet

- Module - 2: 8051 Instruction SetDocument39 pagesModule - 2: 8051 Instruction SetPramod PatilNo ratings yet

- 8051 Instruction SetDocument73 pages8051 Instruction SettbijleNo ratings yet

- Asembbly Operation & Sintax Program Arithmetic Operations Mnemonic Description Bytes CyclesDocument6 pagesAsembbly Operation & Sintax Program Arithmetic Operations Mnemonic Description Bytes CyclesArief HamidNo ratings yet

- 8051 Notes 3rd Unit PDFDocument36 pages8051 Notes 3rd Unit PDFfwefNo ratings yet

- 8051 Instruction Set SummaryDocument2 pages8051 Instruction Set SummaryBertold Van den BerghNo ratings yet

- Question & Answers For Microcontrollers and Its Applications Btech Iv-I Semester (Ece A & B)Document13 pagesQuestion & Answers For Microcontrollers and Its Applications Btech Iv-I Semester (Ece A & B)Krapa Sai PraveenNo ratings yet

- Instruction Format 8051Document26 pagesInstruction Format 8051alex24arulNo ratings yet

- 8051 Instruction SetDocument50 pages8051 Instruction Setkapil singhNo ratings yet

- Microprocessors (Bcst601)Document61 pagesMicroprocessors (Bcst601)surbhiNo ratings yet

- Instruction Set of 8051 MicrocontrollerDocument5 pagesInstruction Set of 8051 MicrocontrollerSubhajit Chakraborty50% (2)

- Architecture and Programming of 8051 MCU's: Chapter 3: The 8051 Instruction SetDocument90 pagesArchitecture and Programming of 8051 MCU's: Chapter 3: The 8051 Instruction SetebinNo ratings yet

- CJ Instrucoes 8051Document6 pagesCJ Instrucoes 8051Luz Do Mundo PijamasNo ratings yet

- 3.1 Addressing Modes: ECP2036 Microprocessors System and Interfacing Chapter 3: The 8051 Instruction SetDocument6 pages3.1 Addressing Modes: ECP2036 Microprocessors System and Interfacing Chapter 3: The 8051 Instruction SetSwetha ChinnikannuNo ratings yet

- Fundamentals of Microcontroller & Its Application: Unit-IiDocument10 pagesFundamentals of Microcontroller & Its Application: Unit-IiRajan PatelNo ratings yet

- 8051 Architecture FullDocument39 pages8051 Architecture FullRaja RajNo ratings yet

- Opcodes 80537Document57 pagesOpcodes 80537Sebas EuNo ratings yet

- Microcontroller Instruction Set - 3Document73 pagesMicrocontroller Instruction Set - 3savisuNo ratings yet

- Programming Model of 8051Document45 pagesProgramming Model of 8051Mayuri ChebleNo ratings yet

- Microcontroller Instruction Set: Subject: Microcontroller and Embeded System Class: 5, Ece Presented byDocument73 pagesMicrocontroller Instruction Set: Subject: Microcontroller and Embeded System Class: 5, Ece Presented byLavanya VallbhareddyNo ratings yet

- Atmel 8051 MCU Instruction SetDocument3 pagesAtmel 8051 MCU Instruction SetBlack DragonNo ratings yet

- 8080 Assembly Language MnemonicsDocument3 pages8080 Assembly Language MnemonicsDavid StaudacherNo ratings yet

- 2.2 Microcontroller Instruction SetDocument51 pages2.2 Microcontroller Instruction Setcory kurdapyaNo ratings yet

- Instruction Set 8051 - v1Document10 pagesInstruction Set 8051 - v1avinashNo ratings yet

- Instruction Groups: The 8051 Has 255 Instructions - Every 8-Bit Opcode From 00 To FF Is Used Except For A5.Document30 pagesInstruction Groups: The 8051 Has 255 Instructions - Every 8-Bit Opcode From 00 To FF Is Used Except For A5.VLC350ZNo ratings yet

- Iv Semester B.Tech (Electrical & Electronics Engineering) Grade Improvement Examinations, August 2021Document5 pagesIv Semester B.Tech (Electrical & Electronics Engineering) Grade Improvement Examinations, August 2021DuoDrenchNo ratings yet

- Chapters of Assembly Language 2Document178 pagesChapters of Assembly Language 2ezerobert56_86874258No ratings yet

- Bank Addressing (Or) Register AddressingDocument4 pagesBank Addressing (Or) Register AddressingDr. Gollapalli NareshNo ratings yet

- InstructionsDocument70 pagesInstructionsAkshay AjayNo ratings yet

- 8051 Instruction SetDocument2 pages8051 Instruction SetMaheswari VijayakumarNo ratings yet

- Week 04Document68 pagesWeek 04aroosa naheedNo ratings yet

- MPMC IV UnitDocument33 pagesMPMC IV UnitVenkatasamy EEENo ratings yet

- 5 Instruction SetDocument41 pages5 Instruction SetElectroalumni NietNo ratings yet

- 8051 Instruction Set and ProgrammingDocument95 pages8051 Instruction Set and Programmingprabhabathi deviNo ratings yet

- Ec522 8051 04Document125 pagesEc522 8051 04Anurag BansalNo ratings yet

- BGK MPMC Unit-4 Q and ADocument9 pagesBGK MPMC Unit-4 Q and AMallesh ArjaNo ratings yet

- Instruction SetDocument18 pagesInstruction SetGirl OnFireNo ratings yet

- Instruction Sap 2Document3 pagesInstruction Sap 2Ian RobisoNo ratings yet

- M @-51 Instruction Set: Programmer'SDocument7 pagesM @-51 Instruction Set: Programmer'Swen_galsNo ratings yet

- Unit 2Document21 pagesUnit 2mrunal1729No ratings yet

- Instruction Set Summary: (I. Scott Mackenzie)Document12 pagesInstruction Set Summary: (I. Scott Mackenzie)saravanan_KLUNo ratings yet

- 1 Microcontroller Instruction SetDocument72 pages1 Microcontroller Instruction SetjaigodaraNo ratings yet

- Data Transfer and Arithmetic InstructionsDocument6 pagesData Transfer and Arithmetic InstructionsAkshaya ThirumalairajNo ratings yet

- Intel 8051 Instruction SetDocument55 pagesIntel 8051 Instruction SetRakesh GangwarNo ratings yet

- 8051 Assembly LanguageDocument39 pages8051 Assembly LanguagemanvithbNo ratings yet

- 02.addressing ModesDocument10 pages02.addressing Modessasi_kar_1No ratings yet

- ARM Instruction Set PDFDocument124 pagesARM Instruction Set PDFhod elnNo ratings yet

- Unit2 CODDocument70 pagesUnit2 CODzazhasnainNo ratings yet

- Md. Iftekharul Islam Sakib Lecturer Cse, BuetDocument45 pagesMd. Iftekharul Islam Sakib Lecturer Cse, BuetMd. Moniruzzaman100% (1)

- 8051 - Micro ControllersDocument33 pages8051 - Micro ControllersRijo Jackson TomNo ratings yet

- 8051 InstructionDocument28 pages8051 Instruction125- PRIYADHARSHINI VNo ratings yet

- 8051 Arithmetic InstDocument59 pages8051 Arithmetic InstNilesh DesaiNo ratings yet

- Combinatorial Algorithms: For Computers and CalculatorsFrom EverandCombinatorial Algorithms: For Computers and CalculatorsRating: 4 out of 5 stars4/5 (2)

- Digital Signal Processing: Instant AccessFrom EverandDigital Signal Processing: Instant AccessRating: 3.5 out of 5 stars3.5/5 (2)

- Power Oroject Z&FDocument24 pagesPower Oroject Z&FzigijuNo ratings yet

- Data Sheet: BGY135 BGY136Document10 pagesData Sheet: BGY135 BGY136wijakesumaNo ratings yet

- Solution:: Fig. 2 Shows The Required Common Base ConnectionDocument9 pagesSolution:: Fig. 2 Shows The Required Common Base ConnectionSwathi Gudivada100% (1)

- Summer Internship Presentation On Embedded Systems Through RaspberryDocument44 pagesSummer Internship Presentation On Embedded Systems Through Raspberryayush.agarwal9325360% (1)

- Pages From RFP - 18607 - Supply - of - LB1 - TransformerDocument73 pagesPages From RFP - 18607 - Supply - of - LB1 - TransformerAnaNo ratings yet

- Netzer DS-25 SpecsheetDocument8 pagesNetzer DS-25 SpecsheetElectromateNo ratings yet

- Digital Logic Design 6 CountersDocument37 pagesDigital Logic Design 6 CountersMurad QəhramanovNo ratings yet

- cc6d Brochure Nueva PDFDocument2 pagescc6d Brochure Nueva PDFjuliocanalesNo ratings yet

- Answer Key PDFDocument48 pagesAnswer Key PDFDanishNo ratings yet

- Atria 3000 Service Manual PDFDocument40 pagesAtria 3000 Service Manual PDFPamela Zavala100% (1)

- Ixfa22N65X2 Ixfp22N65X2 Ixfh22N65X2: V 650V I 22A X2-Class Hiperfet Power MosfetDocument7 pagesIxfa22N65X2 Ixfp22N65X2 Ixfh22N65X2: V 650V I 22A X2-Class Hiperfet Power MosfetjaluadiNo ratings yet

- VHF Low Loss Band-Pass Helical Filter For 145 MHZ - English NewDocument33 pagesVHF Low Loss Band-Pass Helical Filter For 145 MHZ - English NewSharbel AounNo ratings yet

- SAILOR 77 Fleet+ Installation Manual PDFDocument61 pagesSAILOR 77 Fleet+ Installation Manual PDFAnonymous nC9gpUWPNo ratings yet

- Ece104 Lab Report 6Document4 pagesEce104 Lab Report 6cent carinoNo ratings yet

- GSM Based Automatic Electricity Billing SystemDocument6 pagesGSM Based Automatic Electricity Billing SystemIJARTETNo ratings yet

- Optoisolation and Optical Sensor Products: Selection GuideDocument64 pagesOptoisolation and Optical Sensor Products: Selection GuidetorinomgNo ratings yet

- MOSFET Transistor Pragya Kushwaha KIT S1Document17 pagesMOSFET Transistor Pragya Kushwaha KIT S1pragya kushwahaNo ratings yet

- EE 100A SyllabusDocument3 pagesEE 100A SyllabusjedNo ratings yet

- Combined Transformers Oil-Paper InsulationDocument8 pagesCombined Transformers Oil-Paper InsulationFelipe GarciaNo ratings yet

- Digital Signal Processing-1703074Document12 pagesDigital Signal Processing-1703074Sourabh KapoørNo ratings yet

- Carrier Current Receiver PDFDocument5 pagesCarrier Current Receiver PDFTEDY-RNo ratings yet

- Introduction To Pic Programming: Programming Baseline Pics in CDocument19 pagesIntroduction To Pic Programming: Programming Baseline Pics in CAndre Fernandes da SilvaNo ratings yet

- Coil Craft - Selecting InductorsDocument5 pagesCoil Craft - Selecting InductorsklangrobNo ratings yet

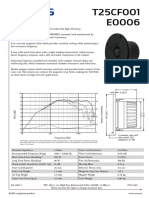

- Seas Excel E0006 t25cf001-2Document1 pageSeas Excel E0006 t25cf001-2Laura CampbellNo ratings yet

- D L C Question BankDocument11 pagesD L C Question BankLeka AmuNo ratings yet

- Basic ElectronicsDocument30 pagesBasic ElectronicsMd. Mahamudul Hasan100% (1)

- AL81GDocument1 pageAL81Gjunkmail_12000No ratings yet

- Implementation of A Pid Controller Embedded in A Fpga For Positioning A DC MotorDocument6 pagesImplementation of A Pid Controller Embedded in A Fpga For Positioning A DC MotorJuan Pablo RosalesNo ratings yet

- LQ150X1LW71NDocument22 pagesLQ150X1LW71Nhome madeNo ratings yet